### **General Description**

The MAX8702/MAX8703 dual-phase noninverting MOSFET drivers are designed to work with PWM controller ICs, such as the MAX8705/MAX8707, in notebook CPU core and other multiphase regulators. Applications can either step down directly from the battery voltage to create the core voltage, or step down from a low-voltage system supply. The single-stage conversion method allows the highest possible efficiency, while the 2-stage conversion at higher switching frequency provides the minimum possible physical size.

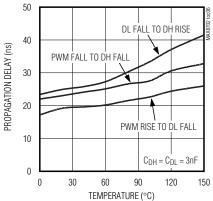

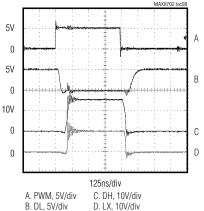

Each MOSFET driver is capable of driving 3nF capacitive loads with only 19ns propagation delay and 8ns typical rise and fall times. Larger capacitive loads are allowable but result in longer propagation and transition times. Adaptive dead-time control helps prevent shootthrough currents and maximizes converter efficiency.

The MAX8702/MAX8703 feature zero-crossing comparators on each channel. When enabled, these comparators permit the drivers to be used in pulse-skipping operation, thereby saving power at light loads. A separate shutdown control is also included that disables all functions, drops quiescent current to  $2\mu$ A, and sets DH low and DL high.

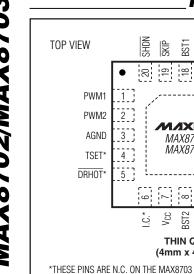

The MAX8702 integrates a resistor-programmable temperature sensor. An open-drain output (DRHOT) signals to the system when the local die temperature exceeds the set temperature. The MAX8702/MAX8703 are available in a thermally-enhanced 20-pin thin QFN package.

Multiphase High-Current Power Supplies 2- to 4-Cell Li+ Battery to CPU Core Supplies Notebook and Desktop Computers Servers and Workstations

**Applications**

#### Features

- Dual-Phase MOSFET Driver

- ♦ 0.35Ω (typ) On-Resistance and 5A (typ) Drive Current

- Drives Large Synchronous-Rectifier MOSFETs

- Integrated Temperature Sensor (MAX8702 Only) Resistor Programmable Open-Drain Driver Hot Indicator (DRHOT)

- ♦ Adaptive Dead Time Prevents Shoot-Through

- Selectable Pulse-Skipping Mode

- ♦ 4.5V to 28V Input Voltage Range

- Thermally Enhanced Low-Profile Thin QFN Package

### **Ordering Information**

| PART       | TEMP RANGE      | PIN-<br>PACKAGE          | DESCRIPTION                                  |

|------------|-----------------|--------------------------|----------------------------------------------|

| MAX8702ETP | -40°C to +100°C | 20 Thin QFN<br>4mm x 4mm | Dual-Phase<br>Driver with<br>Temp. Sensor    |

| MAX8703ETP | -40°C to +100°C | 20 Thin QFN<br>4mm x 4mm | Dual-Phase<br>Driver without<br>Temp. Sensor |

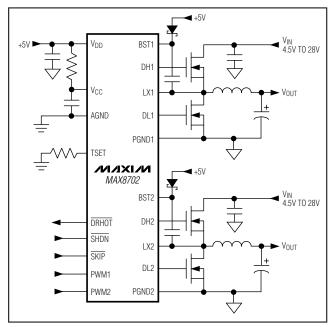

### \_Minimal Operating Circuit

Pin Configuration appears at end of data sheet.

####

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> to AGND         | 0.3V to +6V                         |

|---------------------------------|-------------------------------------|

| V <sub>DD</sub> to AGND         | 0.3V to +6V                         |

| PGND_ to AGND                   | 0.3V to +0.3V                       |

| SKIP, SHDN, DRHOT, TSET to AGND | 0.3V to +6V                         |

| PWM_ to AGND                    | 0.3V to +6V                         |

| DL_ to PGND                     | 0.3V to (V <sub>DD</sub> + 0.3V)    |

| LX_ to AGND                     | 2V to +30V                          |

| DH_ to LX                       | 0.3V to (V <sub>BST</sub> _ + 0.3V) |

| BST_ to LX                                            | 0.3V to +6V    |

|-------------------------------------------------------|----------------|

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |                |

| 20-Pin 4mm x 4mm Thin QFN                             |                |

| (derate 16.9mW/°C above +70°C)                        | 1349mW         |

| Operating Temperature Range                           | 40°C to +100°C |

| Junction Temperature                                  | +150°C         |

| Storage Temperature Range                             |                |

| Lead Temperature (soldering, 10s)                     | +300°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

(Circuit of Figure 2. V<sub>CC</sub> = V<sub>DD</sub> = V<sub>SHDN</sub> = V<sub>SKIP</sub> = 5V, **T<sub>A</sub>** = 0°C to +85°C. Typical values are at T<sub>A</sub> = +25°C, unless otherwise noted.)

| PARAMETER                            | SYMBOL               | CONDITIONS                                                                 |                         | MIN  | ТҮР  | MAX | UNITS |  |

|--------------------------------------|----------------------|----------------------------------------------------------------------------|-------------------------|------|------|-----|-------|--|

| Input Voltage Range                  | Vcc                  |                                                                            |                         | 4.5  |      | 5.5 | V     |  |

| V <sub>CC</sub> Undervoltage-Lockout |                      | 85mV typical                                                               | V <sub>CC</sub> rising  | 3.4  | 3.85 | 4.1 | V     |  |

| Threshold                            | V <sub>UVLO</sub>    | hysteresis                                                                 | V <sub>CC</sub> falling | 3.3  | 3.75 | 4.0 | v     |  |

| V <sub>CC</sub> Quiescent Current    |                      | SKIP = AGND, I                                                             | PWM_ = AGND             |      | 200  | 400 | μA    |  |

| (Note 1)                             | lcc                  | SKIP = AGND, I                                                             | PWM_ = V <sub>CC</sub>  |      | 2    | 3   | mA    |  |

| V <sub>DD</sub> Quiescent Current    | IDD                  | SKIP = AGND, I                                                             | PWM_ = AGND             |      | 1    | 5   | μΑ    |  |

| V <sub>CC</sub> Shutdown Current     |                      | $\overline{\text{SHDN}} = \overline{\text{SKIP}} =$                        | AGND                    |      | 2    | 5   | μΑ    |  |

| V <sub>DD</sub> Shutdown Current     |                      | $\overline{\text{SHDN}} = \overline{\text{SKIP}} =$                        | AGND                    |      | 1    | 5   | μA    |  |

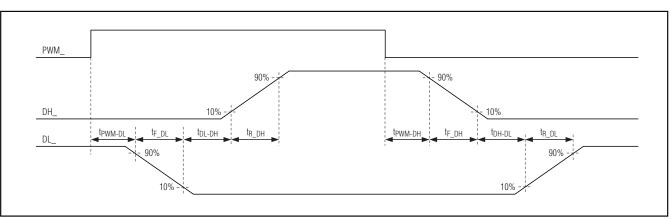

| GATE DRIVERS AND DEAD-T              | IME CONTRO           | L (Figure 1)                                                               |                         |      |      |     |       |  |

| DL_ Propagation Delay                | tpwm-dl              | PWM_ high to D                                                             | L_ low                  |      | 19   |     | ns    |  |

| DL_ FTOPAYALIOIT Delay               | tDH-DL               | DH_ low to DL_                                                             | high                    | 36   |      |     |       |  |

| DH_ Propagation Delay                | tdl-dh               | DL_ low to DH_                                                             | high                    |      | 25   |     | ns    |  |

| DH_ FTOPAgation Delay                | tpwm-dh              | PWM_ low to DH                                                             | PWM_ low to DH_ low     |      |      |     | 115   |  |

| DL_ Transition Time                  | tF_DL                | DL_ falling, 3nF                                                           | load                    |      | 11   |     | ns    |  |

|                                      | t <sub>R_DL</sub>    | DL_ rising, 3nF                                                            |                         | 8    |      |     |       |  |

| DH Transition Time                   |                      | DH_ falling, 3nF                                                           |                         | 14   |      |     |       |  |

| DH_ Transition Time                  | tr_DH                | DH_ rising, 3nF                                                            | load                    |      | 16   |     | ns    |  |

| DH_ On-Resistance (Note 2)           | R <sub>DH</sub>      | $V_{BST_{-}} - V_{LX_{-}} = 1$                                             | 5V                      |      | 1.0  | 4.5 | Ω     |  |

| DL_ On-Resistance (Note 2)           | R <sub>DL_HIGH</sub> | High state (pullup) 1.0                                                    |                         | 4.5  | Ω    |     |       |  |

| DL_ ON-NESISIANCE (NOIE 2)           | R <sub>DL_LOW</sub>  | Low state (pulld                                                           |                         | 0.35 | 2.0  | 52  |       |  |

| DH_ Source/Sink Current              | IDH                  | $V_{DH_{-}} = 2.5V, V_{E}$                                                 | $BST V_LX_ = 5V$        |      | 1.5  |     | Α     |  |

| DL_Source Current                    | IDL_SOURCE           | $V_{DL_} = 2.5V$                                                           |                         |      | 1.5  |     | А     |  |

| DL_Sink Current                      | I <sub>DL_SINK</sub> | $V_{DL_{-}} = 5V$                                                          |                         |      | 5    |     | А     |  |

| Zero-Crossing Threshold              |                      | VPGND VLX_,                                                                | SKIP = AGND             |      | 2.5  |     | mV    |  |

| TEMPERATURE SENSOR                   |                      |                                                                            |                         |      |      |     |       |  |

| Temperature Threshold<br>Accuracy    |                      | $T_A = +85^{\circ}C$ to $+125^{\circ}C$ , $10^{\circ}C$ falling hysteresis |                         | -5   |      | +5  | °C    |  |

| DRHOT Output Low Voltage             |                      | I <sub>SINK</sub> = 3mA                                                    |                         |      |      | 0.4 | V     |  |

| DRHOT Leakage Current                |                      | High state, VDR                                                            | HOT = 5.5V              |      |      | 1   | μA    |  |

//IXI//I

### **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 2.  $V_{CC} = V_{DD} = V_{\overline{SHDN}} = V_{\overline{SKIP}} = 5V$ , **T<sub>A</sub> = 0°C to +85°C**. Typical values are at T<sub>A</sub> = +25°C, unless otherwise noted.)

| PARAMETER                  | SYMBOL | CONDITIONS             | MIN | ТҮР  | MAX | UNITS |

|----------------------------|--------|------------------------|-----|------|-----|-------|

| Thermal-Shutdown Threshold |        | 10°C hysteresis        |     | +160 |     | °C    |

| LOGIC CONTROL SIGNALS      |        |                        |     |      |     |       |

| Logic Input High Voltage   |        | SHDN, SKIP, PWM1, PWM2 | 2.4 |      |     | V     |

| Logic Input Low Voltage    |        | SHDN, SKIP, PWM1, PWM2 |     |      | 0.8 | V     |

| Logic Input Current        |        | SHDN, SKIP, PWM1, PWM2 | -1  |      | +1  | μΑ    |

### **ELECTRICAL CHARACTERISTICS**

(Circuit of Figure 2. V<sub>CC</sub> = V<sub>DD</sub> = V<sub>SHDN</sub> = V<sub>SKIP</sub> = 5V, **T<sub>A</sub>** = -40°C to +100°C, unless otherwise noted.) (Note 3)

| PARAMETER                            | SYMBOL               | CONDITIONS                                                            |                                      | MIN | ТҮР  | MAX | UNITS |

|--------------------------------------|----------------------|-----------------------------------------------------------------------|--------------------------------------|-----|------|-----|-------|

| Input Voltage Range                  | Vcc                  |                                                                       |                                      | 4.5 |      | 5.5 | V     |

| V <sub>CC</sub> Undervoltage-Lockout |                      | 85mV typical                                                          | V <sub>CC</sub> rising               | 3.4 |      | 4.1 | V     |

| Threshold                            | Vuvlo                | hysteresis                                                            | V <sub>CC</sub> falling              | 3.3 |      | 4.0 | V     |

| Vac Ouissaant Ourrant                |                      | SKIP = AGND, PW                                                       | /M_ = PGND_                          |     |      | 450 | μA    |

| V <sub>CC</sub> Quiescent Current    | Icc                  | SKIP = AGND, PW                                                       | $/M_{=} V_{CC}$                      |     |      | 3   | mA    |

| V <sub>DD</sub> Quiescent Current    | IDD                  | $\overline{\text{SKIP}}$ = AGND, PW<br>T <sub>A</sub> = -40°C to +85° |                                      |     | 5    | μA  |       |

| V <sub>CC</sub> Shutdown Current     |                      | $\overline{\text{SHDN}} = \overline{\text{SKIP}} = A$                 | GND, T <sub>A</sub> = -40°C to +85°C |     |      | 5   | μA    |

| V <sub>DD</sub> Shutdown Current     |                      | $\overline{SHDN} = \overline{SKIP} = A$                               | GND, T <sub>A</sub> = -40°C to +85°C |     |      | 5   | μA    |

| GATE DRIVERS AND DEAD-T              | IME CONTRO           | L                                                                     |                                      |     |      |     |       |

| DH_ On-Resistance (Note 2)           | R <sub>DH</sub>      | $V_{BST_} - V_{LX_} = 5V$                                             |                                      |     | 1.0  | 4.5 | Ω     |

| DL On Desistance (Note 2)            | R <sub>DL_HIGH</sub> | High state (pullup)                                                   |                                      |     | 1.0  | 4.5 | Ω     |

| DL_ On-Resistance (Note 2)           | R <sub>DL_LOW</sub>  | Low state (pulldow                                                    | vn)                                  |     | 0.35 | 2.0 | 52    |

| TEMPERATURE SENSOR                   |                      |                                                                       |                                      |     |      |     |       |

| DRHOT Output Low Voltage             |                      | I <sub>SINK</sub> = 3mA                                               |                                      |     |      | 0.4 | V     |

| LOGIC CONTROL SIGNALS                |                      |                                                                       |                                      |     |      |     |       |

| Logic Input High Voltage             |                      | SHDN, SKIP, PWM                                                       | 11, PWM2                             | 2.4 |      |     | V     |

| Logic Input Low Voltage              |                      | SHDN, SKIP, PWM                                                       | 11, PWM2                             |     |      | 0.8 | V     |

Note 1: Static drivers instead of pulsed-level translators.

Note 2: Production testing limitations due to package handling require relaxed maximum on-resistance specifications for the thin QFN package.

Note 3: Specifications from -40°C to +100°C are guaranteed by design, not production tested.

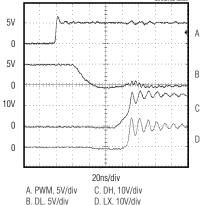

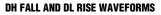

Figure 1. Timing Definitions Used in the Electrical Characteristics

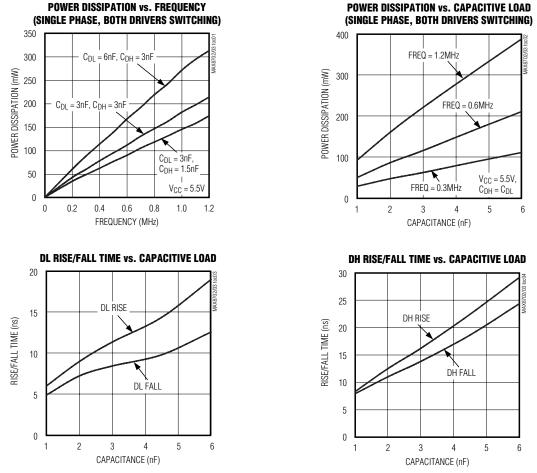

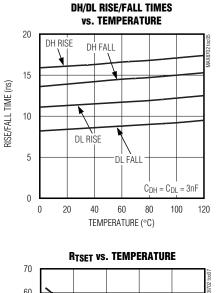

### **Typical Operating Characteristics**

(Circuit of Figure 2.  $V_{IN}$  = 12V,  $V_{DD}$  =  $V_{CC}$  =  $V_{\overline{SHDN}}$  =  $V_{\overline{SKIP}}$  = 5V,  $T_A$  = +25°C unless otherwise noted.)

### **Typical Operating Characteristics (continued)**

(Circuit of Figure 2.  $V_{IN}$  = 12V,  $V_{DD}$  =  $V_{CC}$  =  $V_{\overline{SHDN}}$  =  $V_{\overline{SKIP}}$  = 5V,  $T_A$  = +25°C unless otherwise noted.)

DH RISE AND DL FALL WAVEFORMS

PROPAGATION DELAY vs. TEMPERATURE

TYPICAL SWITCHING WAVEFORMS

5

## **Pin Description**

| Р       | N       |                 |                                                                                                                                                                                                                                                                   |

|---------|---------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX8702 | MAX8703 | NAME            | FUNCTION                                                                                                                                                                                                                                                          |

| 1       | 1       | PWM1            | Phase 1 PWM Logic Input. DH1 is high when PWM1 is high; DL1 is high when PWM1 is low.                                                                                                                                                                             |

| 2       | 2       | PWM2            | Phase 2 PWM Logic Input. DH2 is high when PWM2 is high; DL2 is high when PWM2 is low.                                                                                                                                                                             |

| 3       | 3       | AGND            | Analog Ground. The AGND and PGND_ pins must be connected externally at one point close to the IC. Connect the device's exposed backside pad to AGND.                                                                                                              |

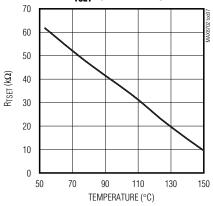

| 4       | _       | TSET            | Temperature-Set Input. Connect an external 1% resistor from TSET to AGND to set the trip point.<br>$R_{TSET} = 85,210 / T - 745,200 / T^2 - 195$ , where $R_{TSET}$ is the temperature-setting resistor in k $\Omega$<br>and T is the trip temperature in Kelvin. |

| 5       | _       | DRHOT           | Driver-Hot-Indicator Output. DRHOT is an open-drain output. Pull up with an external resistor.<br>When the device's temperature exceeds the programmed set point, DRHOT is pulled low.                                                                            |

| 6       | —       | I.C.            | Internally Connected. Connect to AGND.                                                                                                                                                                                                                            |

| 7       | 7       | V <sub>CC</sub> | Internal Control Circuitry Supply Input. The input voltage range is from 4.5V to 5.5V. Bypass V <sub>CC</sub> to AGND with a 1µF ceramic capacitor. The maximum resistance between V <sub>CC</sub> and V <sub>DD</sub> should be 10 $\Omega$ .                    |

| 8       | 8       | BST2            | Phase 2 Bootstrap Flying-Capacitor Connection. An optional resistor in series with BST2 allows the DH2 pullup current to be adjusted.                                                                                                                             |

| 9       | 9       | DH2             | Phase 2 High-Side Gate-Driver Output. DH2 swings between LX2 and BST2.                                                                                                                                                                                            |

| 10      | 10      | LX2             | Phase 2 Inductor Switching Node Connection. LX2 is the internal lower supply rail for the DH2 high-side gate driver. LX2 is also the input to the skip-mode zero-crossing comparator.                                                                             |

| 11      | 11      | PGND2           | Phase 2 Power Ground. PGND2 is the internal lower supply rail for the DL2 low-side gate driver.                                                                                                                                                                   |

| 12      | 12      | DL2             | Phase 2 Low-Side Gate-Driver Output. DL2 swings between PGND2 and $V_{DD}$ . DL2 is high in shutdown.                                                                                                                                                             |

| 13      | 13      | V <sub>DD</sub> | DL_ Gate-Driver Supply Input. The input voltage range is from 4.5V to 5.5V. Bypass $V_{DD}$ to the power ground with a 2.2µF ceramic capacitor.                                                                                                                   |

| 14      | 14      | DL1             | Phase 1 Low-Side Gate-Driver Output. DL1 swings between PGND1 and V <sub>DD</sub> . DL1 is high in shutdown.                                                                                                                                                      |

| 15      | 15      | PGND1           | Phase 1 Power Ground. PGND1 is the internal lower supply rail for the DL1 low-side gate driver.                                                                                                                                                                   |

| 16      | 16      | LX1             | Phase 1 Inductor Switching Node Connection. LX1 is the internal lower supply rail for the DH1 high-side gate driver. LX1 is also the input to the skip-mode zero-crossing comparator.                                                                             |

| 17      | 17      | DH1             | Phase 1 High-Side Gate-Driver Output. DH1 swings between LX1 and BST1.                                                                                                                                                                                            |

| 18      | 18      | BST1            | Phase 1 Bootstrap Flying-Capacitor Connection. An optional resistor in series with BST1 allows the DH1 pullup current to be adjusted.                                                                                                                             |

| 19      | 19      | SKIP            | Pulse-Skipping-Mode Control Input. The pulse-skipping mode is enabled when SKIP is low.<br>When SKIP is high, both drivers operate in PWM mode (i.e., except during dead times, DL_ is the complement of DH_).                                                    |

| 20      | 20      | SHDN            | Shutdown Control Input. When SHDN and SKIP are low, DH_ is forced low, DL_ forced high, and the device enters into a low-power shutdown state. Temperature sensing is disabled in shutdown.                                                                       |

| _       | 4, 5, 6 | N. C.           | No Connection. Not internally connected.                                                                                                                                                                                                                          |

## **Typical Operating Circuit**

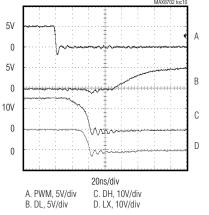

The typical operating circuit of the MAX8702 (Figure 2) shows the power-stage and gate-driver circuitry of a dualphase CPU core supply operating at 300kHz, with each phase capable of supplying 20A of load current. Table 1 lists recommended component options, and Table 2 lists the component suppliers' contact information.

## **Detailed Description**

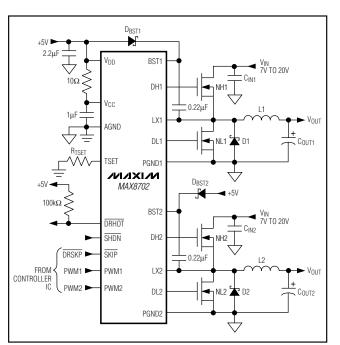

The MAX8702/MAX8703 dual-phase noninverting MOSFET drivers are intended to work with PWM controller ICs in CPU core and other multiphase switching

### Table 1. Component List

| DESIGNATION                                     | DESCRIPTION                                                                     |

|-------------------------------------------------|---------------------------------------------------------------------------------|

| Total Input<br>Capacitance (C <sub>IN</sub> )   | (4) 10µF, 25V<br>Taiyo Yuden TMK432BJ106KM or<br>TDK C4532X5R1E106M             |

| Total Output<br>Capacitance (C <sub>OUT</sub> ) | (4) 330μF, 2.5V, 9mΩ low-ESR polymer<br>capacitor (D case)<br>Sanyo 2R5TPE330M9 |

| Schottky Diode<br>(per phase)                   | 3A Schottky diode<br>Central Semiconductor<br>CMSH3-40                          |

| Inductor (per phase)                            | 0.6µH<br>Panasonic ETQP1H0R6BFA or<br>Sumida CDEP134H-0R6                       |

| High-Side MOSFET<br>(NH, per phase)             | Siliconix (1) Si7892DP or<br>International Rectifier (2) IRF6604                |

| Low-Side MOSFET<br>(NL, per phase)              | Siliconix (2) Si7442DP or<br>International Rectifier (2) IRF6603                |

### Table 2. Component Suppliers

| SUPPLIER                | WEBSITE               |

|-------------------------|-----------------------|

| Central Semiconductor   | www.centralsemi.com   |

| Fairchild Semiconductor | www.fairchildsemi.com |

| International Rectifier | www.irf.com           |

| Panasonic               | www.panasonic.com     |

| Sanyo                   | www.secc.co.jp        |

| Siliconix (Vishay)      | www.vishay.com        |

| Sumida                  | www.sumida.com        |

| Taiyo Yuden             | www.t-yuden.com       |

| TDK                     | www.component.tdk.com |

regulators. Each MOSFET driver is capable of driving 3nF capacitive loads with only 19ns propagation delay and 8ns typical rise and fall times. Larger capacitive loads are allowable but result in longer propagation and transition times. Adaptive dead-time control prevents shoot-through currents and maximizes converter

Figure 3. MAX8702 Functional Diagram

MAX8702/MAX8703

. . . . . .

Figure 2. MAX8702 Typical Operating Circuit

7

efficiency while allowing operation with a variety of MOSFETs and PWM controllers. A UVLO circuit allows proper power-on sequencing. The PWM control inputs are both TTL and CMOS compatible.

The MAX8702 integrates a resistor-programmable temperature sensor. An open-drain output (DRHOT) signals to the system when the die temperature of the driver exceeds the set temperature. See the *Temperature Sensor* section.

#### **MOSFET Gate Drivers (DH, DL)**

The DH and DL drivers are optimized for driving moderately sized high-side and larger low-side power MOSFETs. This is consistent with the low duty factor seen in the notebook CPU environment, where a large V<sub>IN</sub> - V<sub>OUT</sub> differential exists. Two adaptive dead-time circuits monitor the DH and DL outputs and prevent the opposite-side FET from turning on until DH or DL is fully off. There must be a low-resistance, low-inductance path from the DH and DL drivers to the MOSFET gates for the adaptive dead-time circuits to work properly. Otherwise, the sense circuitry interprets the MOSFET gate as "off" while there is actually still charge left on the gate. Use very short, wide traces measuring 10 to 20 squares (50 to 100 mils wide if the MOSFET is 1in from the device).

The internal pulldown transistor that drives DL low is robust, with a 0.35 $\Omega$  (typ) on-resistance. This helps prevent DL from being pulled up due to capacitive coupling from the drain-to-gate capacitance of the low-side synchronous-rectifier MOSFETs when LX switches from ground to V<sub>IN</sub>. Applications with high input voltages and long, inductive DL traces may require additional gate-to-source capacitance to ensure fast-rising LX edges do not pull up the low-side MOSFET's gate voltage, causing shoot-through currents. The capacitive coupling between LX and DL created by the MOSFET's gate-to-drain capacitance (C<sub>RSS</sub>), gate-to-source capacitance (C<sub>ISS</sub> - C<sub>RSS</sub>), and additional board parasitics should not exceed the minimum threshold voltage:

$$V_{GS(TH)} < V_{IN} \left( \frac{C_{RSS}}{C_{ISS}} \right)$$

Lot-to-lot variation of the threshold voltage can cause problems in marginal designs. Typically, adding a 4700pF capacitor between DL and power ground, close to the low-side MOSFETs, greatly reduces coupling. To prevent excessive turn-off delays, do not exceed 22nF of total gate capacitance.

Alternatively, shoot-through currents may be caused by a combination of fast high-side MOSFETs and slow low-

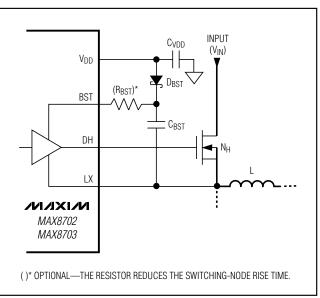

Figure 4. High-Side Gate-Driver Boost Circuitry

side MOSFETs. If the turn-off delay time of the low-side MOSFETs is too long, the high-side MOSFETs can turn on before the low-side MOSFETs have actually turned off. Adding a resistor of less than 5 $\Omega$  in series with BST slows down the high-side MOSFET turn-on time, eliminating the shoot-through currents without degrading the turn-off time (R<sub>BST</sub> in Figure 4). Slowing down the high-side MOSFETs also reduces the LX node rise time, thereby reducing the EMI and high-frequency coupling responsible for switching noise.

#### **Boost Capacitor Selection**

The MAX8702/MAX8703 use a bootstrap circuit to generate the floating supply voltages for the high-side drivers (DH). The boost capacitors (C<sub>BST</sub>) selected must be large enough to handle the gate-charging requirements of the high-side MOSFETs. Typically,  $0.1\mu$ F ceramic capacitors work well for low-power applications driving medium-sized MOSFETs. However, high-current applications driving large, high-side MOSFETs require boost capacitors larger than  $0.1\mu$ F. For these applications, select the boost capacitors to avoid discharging the capacitor more than 200mV while charging the high-side MOSFET's gates:

$$C_{BST} = \frac{N \times Q_{GATE}}{200mV}$$

where N is the number of high-side MOSFETs used for one phase and  $Q_{GATE}$  is the total gate charge specified in the MOSFET's data sheet. For example, assume

(2) IRF7811W n-channel MOSFETs are used on the high side. According to the manufacturer's data sheet, a single IRF7811W has a maximum gate charge of 24nC ( $V_{GS} = 5V$ ). Using the above equation, the required boost capacitance is:

$$C_{BST} = \frac{2 \times 24nC}{200mV} = 0.24 \mu F$$

Selecting the closest standard value, this example requires a 0.22µF ceramic capacitor.

#### 5V Bias Supply (VCC and VDD)

V<sub>DD</sub> provides the supply voltages for the low-side drivers (DL). The decoupling capacitor at V<sub>DD</sub> also charges the BST capacitors during the time period when DL is high. Therefore, the V<sub>DD</sub> capacitor should be large enough to minimize the ripple voltage during switching transitions. C<sub>VDD</sub> should be chosen according to the following equation:

#### CVDD = 10 x CBST

In the example above, a 0.22  $\mu F$  capacitor is used for CBST, so the VDD capacitor should be 2.2  $\mu F.$

$V_{CC}$  provides the supply voltage for the internal logic circuit and temperature sensor. To avoid switching noise from coupling into the sensitive internal circuit, an RC filter is recommended for the  $V_{CC}$  pin. Place a  $10\Omega$  resistor from the supply voltage to the  $V_{CC}$  pin and a  $1\mu\text{F}$  capacitor from the  $V_{CC}$  pin to AGND.

The total bias current  $\mathsf{I}_{\mathsf{BIAS}}$  from the 5V supply can be calculated using the following equation:

#### $I_{BIAS} = I_{DD} + I_{CC}$

$IDD = n_{PHASE} \times f_{SW} \times (n_{NH} \times Q_G(NH) + n_{NL} \times Q_G(NL))$

where npHASE is the number of phases, fSW is the switching frequency,  $Q_G(NH)$  and  $Q_G(NL)$  are the MOSFET data sheet's total gate-charge specification limits at V<sub>GS</sub> = 5V, n<sub>N</sub>H is the total number of high-side MOSFETs in parallel, n<sub>NL</sub> is the total number of low-side MOSFETs in parallel, and I<sub>CC</sub> is the V<sub>CC</sub> supply current.

#### **Undervoltage Lockout (UVLO)**

When V<sub>CC</sub> is below the UVLO threshold (3.85V typ) and SHDN and SKIP are low, DL is kept high and DH is held low. This provides output overvoltage protection as soon as the supply voltage is applied. Once V<sub>CC</sub> is above the UVLO threshold and SHDN is high, DL and DH levels depend on the PWM signal applied. If V<sub>CC</sub> falls below the UVLO threshold while SHDN is high, both DL and DH are immediately forced low. This prevents negative undershoots on the output when the

system power is removed without going through the proper shutdown sequence.

#### Low-Power Pulse Skipping

The MAX8702/MAX8703 enter into low-power pulseskipping mode when SKIP is pulled low. In skip mode, an inherent automatic switchover to pulse frequency modulation (PFM) takes place at light loads. A zerocrossing comparator truncates the low-side switch ontime at the inductor current's zero-crossing. The comparator senses the voltage across LX and PGND. Once VLX - VPGND drops below the zero-crossing comparator threshold (see the *Electrical Characteristics*), the comparator forces DL low. This mechanism causes the threshold between pulse-skipping PFM and nonskipping PWM operation to coincide with the boundary between continuous and discontinuous inductor-current operation. The PFM/PWM crossover occurs when the load current of each phase is equal to 1/2 the peakto-peak ripple current, which is a function of the inductor value. For a battery input range of 7V to 20V, this threshold is relatively constant, with only a minor dependence on the input voltage due to the typically low duty cycles. The switching waveforms may appear noisy and asynchronous when light loading activates the pulse-skipping operation, but this is a normal operating condition that results in high light-load efficiency.

#### Shutdown

The MAX8702/MAX8703 feature a low-power shutdown mode that reduces the V<sub>CC</sub> quiescent current drawn to  $2\mu$ A (typ). Driving SHDN and SKIP low sets DH low and DL high. Temperature sensing is disabled in shutdown.

#### Temperature Sensor (MAX8702 Only)

The MAX8702 includes a fully integrated resistor-programmable temperature sensor. The sensor incorporates two temperature-dependent reference signals and one comparator. One signal exhibits a characteristic that is proportional to temperature, and the other is complementary to temperature. The temperature at which the two signals are equal determines the thermal trip point. When the temperature of the device exceeds the trip point, the open-drain output DRHOT pulls low.

### **Table 3. Modes of Operation**

| SHDN | SKIP | MODE OF OPERATION                                         |

|------|------|-----------------------------------------------------------|

| L    | L    | Low-power shutdown state;<br>temperature sensing disabled |

| L    | Н    | PWM operation                                             |

| Н    | L    | Pulse-skipping operation                                  |

| Н    | Н    | PWM operation                                             |

A 10°C hysteresis keeps the output from oscillating when the temperature is close to the threshold. The thermal trip point is programmable up to +160°C through an external resistor between TSET and AGND. Use the following equation to determine the value of the resistor:

$R_{TSET} = (85,210 / T) - (745,200 / T^2) - 195$

where  $R_{TSET}$  is the value of the set-point resistor in  $k\Omega$  and T is the trip-point temperature in Kelvin.

The MAX8702 and MAX8703 include a thermal-shutdown circuit that is independent of the temperature sensor. The thermal shutdown has a fixed threshold of  $+160^{\circ}$ C (typ) with 10°C of thermal hysteresis. When the die temperature exceeds  $+160^{\circ}$ C, DH is pulled low and DL is pulled high. The driver automatically resets when the die temperature drops by  $+10^{\circ}$ C.

### Applications Information

#### **Power MOSFET Selection**

Most of the following MOSFET guidelines focus on the challenge of obtaining high load-current capability when using high-voltage (>20V) AC adapters. Low-current applications usually require less attention.

The high-side MOSFET (N<sub>H</sub>) must be able to dissipate the resistive losses plus the switching losses at both VIN(MIN) and VIN(MAX). Calculate both of these sums. Ideally, the losses at VIN(MIN) should be roughly equal to losses at VIN(MAX), with lower losses in between. If the losses at VIN(MIN) are significantly higher than the losses at VIN(MAX), consider increasing the size of N<sub>H</sub> (reducing RDS(ON) but increasing CGATE). Conversely, if the losses at VIN(MAX) are significantly higher than the losses at VIN(MIN), consider reducing the size of N<sub>H</sub> (increasing RDS(ON) but reducing CGATE). If VIN does not vary over a wide range, the minimum power dissipation occurs where the resistive losses equal the switching losses.

Choose a low-side MOSFET that has the lowest possible on-resistance ( $R_{DS(ON)}$ ), comes in a moderatesized package (i.e., one or two SO-8s, DPAK, or D<sup>2</sup>PAK), and is reasonably priced. Ensure that the DL gate driver can supply sufficient current to support the gate charge and the current injected into the parasitic gate-to-drain capacitor caused by the high-side MOS-FET turning on; otherwise, cross-conduction problems can occur.

#### **MOSFET** Power Dissipation

Worst-case conduction losses occur at the duty factor extremes. For the high-side MOSFET (N<sub>H</sub>), the worst-

case power dissipation due to resistance occurs at the minimum input voltage:

$$PD(N_{H}RESISTIVE) = \left(\frac{V_{OUT}}{V_{IN}}\right) \left(\frac{I_{LOAD}}{n_{TOTAL}}\right)^{2} R_{DS(ON)}$$

where  $n_{TOTAL}$  is the total number of phases.

Generally, a small high-side MOSFET is desired to reduce switching losses at high input voltages. However, the  $R_{DS(ON)}$  required to stay within package power dissipation often limits how small the MOSFETs can be. Again, the optimum occurs when the switching losses equal the conduction ( $R_{DS(ON)}$ ) losses. High-side switching losses do not usually become an issue until the input is greater than approximately 15V.

Calculating the power dissipation in high-side MOSFETs (N<sub>H</sub>) due to switching losses is difficult since it must allow for difficult quantifying factors that influence the turn-on and turn-off times. These factors include the internal gate resistance, gate charge, threshold voltage, source inductance, and PC board layout characteristics. The following switching-loss calculation provides only a very rough estimate and is no substitute for breadboard evaluation, preferably including verification using a thermocouple mounted on N<sub>H</sub>:

$$PD(N_{H}SWITCHING) = (V_{IN(MAX)})^{2} \left(\frac{C_{RSS}f_{SW}}{I_{GATE}}\right) \left(\frac{I_{LOAD}}{n_{TOTAL}}\right)$$

where  $C_{RSS}$  is the reverse transfer capacitance of  $N_{H}$  and  $I_{GATE}$  is the peak gate-drive source/sink current (5A typ).

Switching losses in the high-side MOSFET can become an insidious heat problem when maximum AC adapter voltages are applied, due to the squared term in the C  $\times$  VIN<sup>2</sup>  $\times$  fsw switching-loss equation. If the high-side MOSFET chosen for adequate RDS(ON) at low battery voltages becomes extraordinarily hot when biased from VIN(MAX), consider choosing another MOSFET with lower parasitic capacitance.

For the low-side MOSFET (NL), the worst-case power dissipation always occurs at the maximum input voltage:

$$PD(N_{L}RESISTIVE) = \left[1 - \left(\frac{V_{OUT}}{V_{IN(MAX)}}\right)\right] \left(\frac{I_{LOAD}}{n_{TOTAL}}\right)^{2} R_{DS(ON)}$$

The worst case for MOSFET power dissipation occurs under heavy overloads that are greater than  $I_{LOAD(MAX)}$  but are not quite high enough to exceed

the current limit and cause the fault latch to trip. The MOSFETs must have a good-sized heatsink to handle the overload power dissipation. The heat sink can be a large copper field on the PC board or an externally mounted device.

The Schottky diode only conducts during the dead time when both the high-side and low-side MOSFETs are off. Choose a Schottky diode with a forward voltage low enough to prevent the low-side MOSFET body diode from turning on during the dead time, and a peak current rating higher than the peak inductor current. The Schottky diode must be rated to handle the average power dissipation per switching cycle. This diode is optional and can be removed if efficiency is not critical.

#### IC Power Dissipation and Thermal Considerations

Power dissipation in the IC package comes mainly from driving the MOSFETs. Therefore, it is a function of both switching frequency and the total gate charge of the selected MOSFETs. The total power dissipation when both drivers are switching is given by:

$$PD(IC) = I_{BIAS} \times 5V$$

where I<sub>BIAS</sub> is the bias current of the 5V supply calculated in the *5V Bias Supply (V<sub>DD</sub> and V<sub>CC</sub>)* section .

The rise in die temperature due to self-heating is given by the following formula:

#### $\Delta T_J = PD(IC) \times \theta_{JA}$

where PD(IC) is the power dissipated by the device, and  $\theta_{JA}$  is the package's thermal resistance. The typical thermal resistance is 59.3°C/W for the 4mm x 4mm thin QFN package. For example, if the MAX8702 dissipates 500mW of power within the IC, this corresponds to a 30°C shift in the die temperature in the thin QFN package.

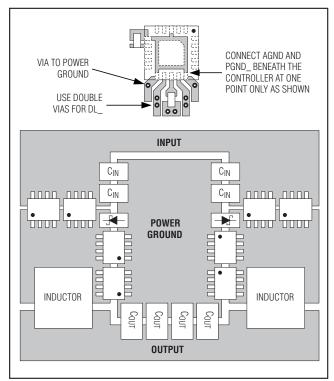

#### **PC Board Layout Considerations**

The MAX8702/MAX8703 MOSFET drivers source and sink large currents to drive MOSFETs at high switching speeds. The high di/dt can cause unacceptable ringing if the trace lengths and impedances are not well controlled. The following PC board layout guidelines are recommended when designing with the device:

1) Place V<sub>CC</sub> and V<sub>DD</sub> decoupling capacitors as close to their respective pins as possible.

- Minimize the high-current loops from the input capacitor, upper-switching MOSFET, and low-side MOSFET back to the input capacitor negative terminal.

- Provide enough copper area at and around the switching MOSFETs and inductors to aid in thermal dissipation.

- 4) Connect the PGND1 and PGND2 pins as close as possible to the source of the low-side MOSFETs.

- 5) Keep LX traces away from sensitive analog components and nodes. Place the IC and analog components on the opposite side of the board from the power-switching node if possible.

- 6) Use two or more vias for DL and DH traces when changing layers to reduce via inductance.

Figure 5 shows a PC board layout example.

Figure 5. PC Board Layout Example

LX1

15

14 DL1

13

12 DL2

[11]

19 17 16

MAXIM

MAX8702 MAX8703

∞ 6 <del>0</del>

DH2 LX2

SHDN

20

9

<u>ن</u>\* 200 3ST2 THIN QFN (4mm x 4mm)

1

2

3

4

5

SKIP BST1

## **Pin Configuration**

PGND1

$V_{DD}$

PGND2

**Chip Information**

TRANSISTOR COUNT: 1100 PROCESS: BICMOS

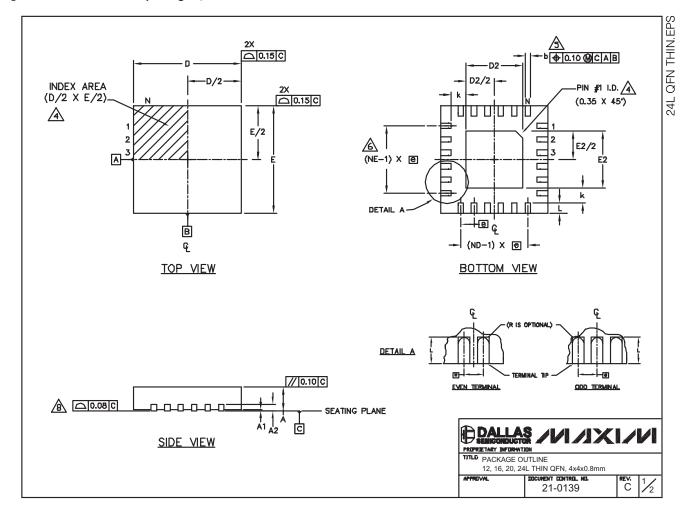

### Package Information

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to **www.maxim-ic.com/packages**.)

## \_Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to **www.maxim-ic.com/packages**.)

|               | COMMON DIMENSIONS |         |      |      |           |      |           |             |           |        |       |      |

|---------------|-------------------|---------|------|------|-----------|------|-----------|-------------|-----------|--------|-------|------|

| PKG           | 12                | 2L 4×   | :4   | 16   | 5L 4x     | 4    | 50        | )L 4×       | 4         | 24     | 4L 4× | :4   |

| REF.          | MIN.              | NDM.    | MAX. | MIN. | NDM.      | MAX. | MIN.      | NDM.        | MAX.      | MIN.   | NDM.  | MAX. |

| A             | 0.70              | 0,75    | 0.80 | 0.70 | 0.75      | 0.80 | 0.70      | 0.75        | 0.80      | 0.70   | 0.75  | 0.80 |

| A1            | 0.0               | 0.02    | 0.05 | 0.0  | 0.02      | 0.05 | 0.0       | <b>20.0</b> | 0.05      | 0.0    | 0.02  | 0.05 |

| A2            | 0                 | .20 RE  | F    | 0    | .20 RE    | F    | 0         | 20 RE       | F         | 0      | 20 RE | F    |

| ю             | 0.25              | 0.30    | 0.35 | 0.25 | 0.30      | 0.35 | 0.20      | 0.25        | 0.30      | 0.18   | 0.23  | 0.30 |

| D             | 3.90              | 4.00    | 4.10 | 3.90 | 4.00      | 4.10 | 3.90      | 4.00        | 4.10      | 3.90   | 4.00  | 4.10 |

| E             | 3.90              | 4.00    | 4.10 | 3.90 | 4.00      | 4.10 | 3.90      | 4.00        | 4.10      | 3.90   | 4.00  | 4.10 |

| e             | (                 | ).80 BS | C.   | 0    | 0.65 BSC. |      | 0.50 BSC. |             | 0.50 BSC. |        |       |      |

| ĸ             | 0.25              | -       | -    | 0.25 | -         | -    | 0.25      | -           | -         | 0.25   | -     | -    |

| L             | 0.45              | 0.55    | 0.65 | 0.45 | 0.55      | 0.65 | 0.45      | 0.55        | 0.65      | 0.30   | 0.40  | 0.50 |

| N             |                   | 12      |      |      | 16        |      | 20        |             |           | 24     |       |      |

| ND            |                   | 3       |      | 4    |           | 5    |           |             | 6         |        |       |      |

| NE            |                   | 3       |      | 4    |           | 5    |           | 6           |           |        |       |      |

| Jedec<br>Var. |                   | WGGB    |      |      | WGGC      |      | VGGD-1    |             |           | WGGD-2 |       |      |

| E       | XPDS | ED   | PAD  | VAR  | IATI | DNS  |         |

|---------|------|------|------|------|------|------|---------|

| PKG.    |      | DS   |      |      | E2   |      |         |

| CODES   | MIN. | NDM. | MAX. | MIN. | NDM. | MAX. | ALLOVED |

| T1244-2 | 1.95 | 2.10 | 2.25 | 1.95 | 2.10 | 2.25 | ND      |

| T1244-3 | 1.95 | 2.10 | 2,25 | 1.95 | 2.10 | 2.25 | YES     |

| T1244-4 | 1.95 | 2.10 | 2.25 | 1.95 | 2.10 | 2.25 | ND      |

| T1644-2 | 1.95 | 2.10 | 2,25 | 1.95 | 2.10 | 2.25 | ND      |

| T1644-3 | 1.95 | 2.10 | 2.25 | 1.95 | 2.10 | 2.25 | YES     |

| T1644-4 | 1.95 | 2.10 | 2,25 | 1.95 | 2.10 | 2.25 | ND      |

| T2044-1 | 1.95 | 2.10 | 2.25 | 1.95 | 2.10 | 2.25 | ND      |

| T2044-2 | 1.95 | 2.10 | 2,25 | 1.95 | 2.10 | 2.25 | YES     |

| T2044-3 | 1.95 | 2.10 | 2.25 | 1.95 | 2.10 | 2.25 | ND      |

| T2444-1 | 2.45 | 2.60 | 2.63 | 2.45 | 2.60 | 2.63 | ND      |

| T2444-2 | 1.95 | 2.10 | 2.25 | 1.95 | 2.10 | 2.25 | YES     |

| T2444-3 | 2.45 | 2.60 | 2.63 | 2.45 | 2.60 | 2.63 | YES     |

| T2444-4 | 2.45 | 2.60 | 2.63 | 2.45 | 2.60 | 2.63 | ND      |

NOTES:

- 1. DIMENSIONING & TOLERANCING CONFORM TO ASME Y14.5M-1994.

- 2. ALL DIMENSIONS ARE IN MILLIMETERS. ANGLES ARE IN DEGREES.

- 3. N IS THE TOTAL NUMBER OF TERMINALS.

- A THE TERNINAL #1 IDENTIFIER AND TERMINAL NUMBERING CONVENTION SHALL CONFORM TO JESD 95-1 SPF-012. DETAILS OF TERMINAL #1 IDENTIFIER ARE OPTIONAL, BUT MUST BE LOCATED WITHIN THE ZONE INDICATED. THE TERMINAL #1 IDENTIFIER MAY BE EITHER A MOLD OR MARKED FEATURE.

- A DIMENSION & APPLIES TO METALLIZED TERMINAL AND IS MEASURED BETWEEN 0.25 mm AND 0.30 mm FROM TERMINAL TIP.

- A ND AND NE REFER TO THE NUMBER OF TERMINALS ON EACH D AND E SIDE RESPECTIVELY.

- 7. DEPOPULATION IS POSSIBLE IN A SYMMETRICAL FASHION.

- & COPLANARITY APPLIES TO THE EXPOSED HEAT SINK SLUG AS WELL AS THE TERMINALS.

- 9. DRAWING CONFORMS TO JEDEC MO220, EXCEPT FOR T2444-1, T2444-3 AND T2444-4.

| 12, 16, 20, 24L THIN QFN, 4x4x0.8mm |         |           |     |

|-------------------------------------|---------|-----------|-----|

| approval                            | 21-0139 | rev.<br>C | 2/2 |

|                                     |         |           |     |

ETARY INFORMATION

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

#### 14

\_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 2004 Maxim Integrated Products

Printed USA

is a registered trademark of Maxim Integrated Products.