September 26, 2012 Ver 0.6

4-BIT SINGLE CHIP MICROCOMPUTERS

# ADAM41P272X USER`S MANUAL

- ADAM41P2727 (Including I.R. LED Drive Tr.)

- ADAM41P2723 (Including I.R. LED Drive Tr.).)

- ADAM41P2721 (Including I.R. LED Drive Tr.)

- ADAM41P2728 (Excluding I.R. LED Drive Tr.)

- ADAM41P2724 (Excluding I.R. LED Drive Tr.)

- ADAM41P2720 (Excluding I.R. LED Drive Tr.)

# 1. OVERVIEW

The ADAM41P272X is the high speed and low voltage operating 4-bit single chip microcomputer. This chip contains ADAM41 core, ROM, RAM, input/output ports , two timer/counters, etc. The ADAM41P272X is MTP version.

## 1.1. Features

- Instruction Execution Time

- 1us @ fosc=4MHz

- Program Memory (MTP)

- 48K Bytes (24,576 x 16bit)

- [ Multi-programmable by 16K-Byte or 24K-Byte ]

- Data Memory (RAM)

256 pibble (256 x 4b)

- 256 nibble (256 x 4bit)

16-Bit Table read Instruction.

- 8-Level Stack (Including Interrupts)

- Timer

- Timer / Counter : 8Bit \* 2ch

- Carrier Generator : 6Bit \* 1ch

- Watch Dog Timer : 19Bit \* 1ch

- Oscillator Type

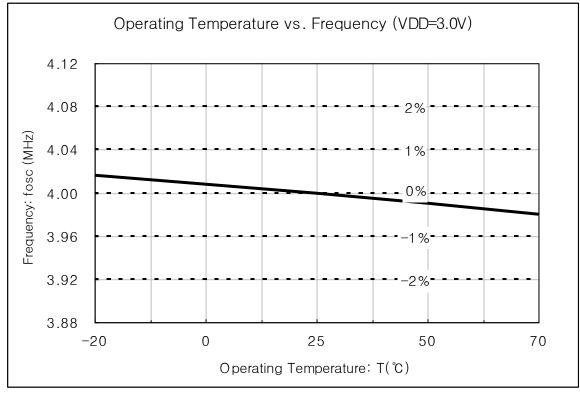

- Calibrated Internal RCOSC Only : typ. 4MHz (±2%)

- Built in Tr. for I.R. LED Drive in the ADAM41P2727/2723/2721

IOL = 250mA at VDD=3V and VO=0.3V

- Power On Reset

- Power Saving Operation Modes

STOP

- 3 Interrupt source

- Operating Voltage Range

- 1.8V ~ 3.6V @4MHz

- Low Voltage Detection Circuit

- Voltage Detection Indicator Circuit : 2-Level [ 2.5V(±0.2V) / 2.1V(±0.2V) ]

- Package

- 20SOP/ 24SOP / 28SOP / 28TSSOP

| Series         | ADAM41P2727<br>ADAM41P2728 | ADAM41P2723<br>ADAM41P2724 | ADAM41P2721<br>ADAM41P2720 |

|----------------|----------------------------|----------------------------|----------------------------|

| Program memory | 24,576 x 16                | 24,576 x 16                | 24,576 x 16                |

| Data memory    | 256 x 4                    | 256 x 4                    | 256 x 4                    |

| I/O ports      | 8                          | 8                          | 7                          |

| Input ports    | 4                          | 4                          | 4                          |

| Output ports   | 14                         | 10                         | 7                          |

| Package        | 28SOP/TSSOP                | 24SOP                      | 20SOP                      |

## Table 1.1 ADAM41P272X series members

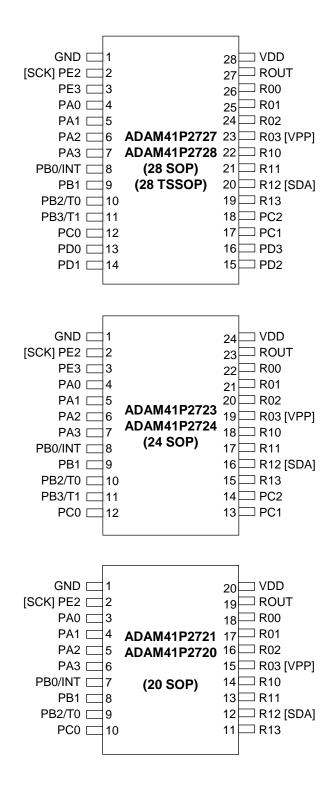

## 1.2. Pin Assignments ( top view )

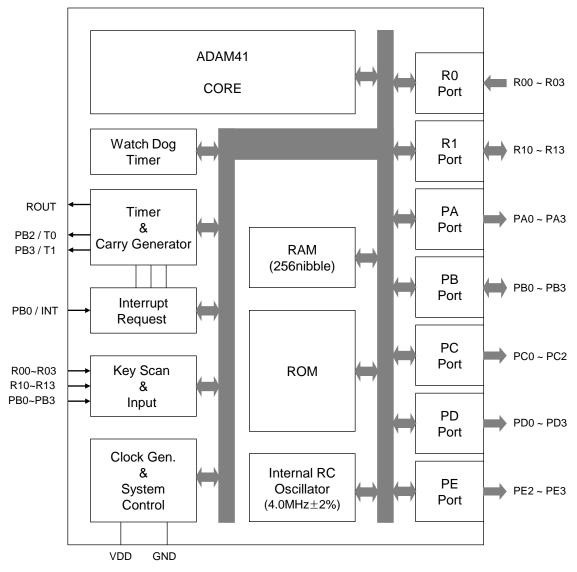

## 1.3. Block Diagram

NOTE1> PD0~PD3 ports are not available in ADAM41P2724 and ADAM41P2723 NOTE2> PD0~PD3, PE3, PB3, PC1~PC2 ports are not available in ADAM41P2720 and ADAM41P2721

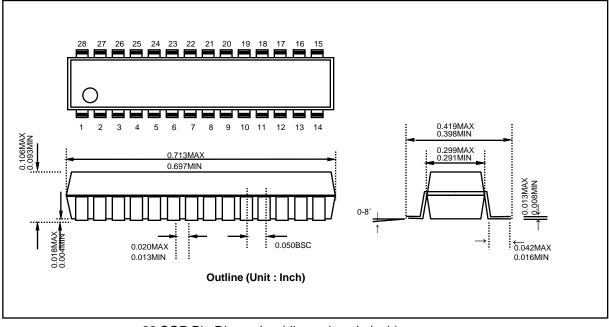

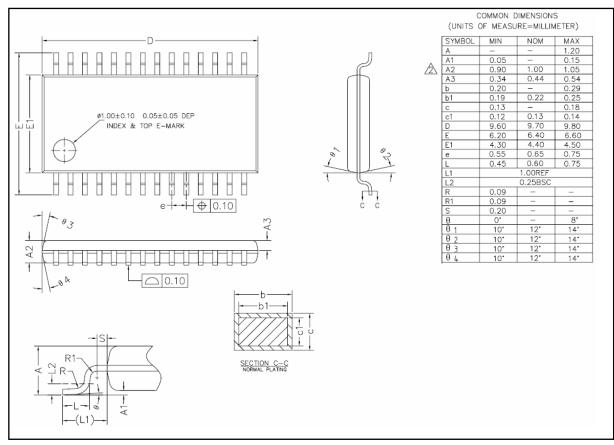

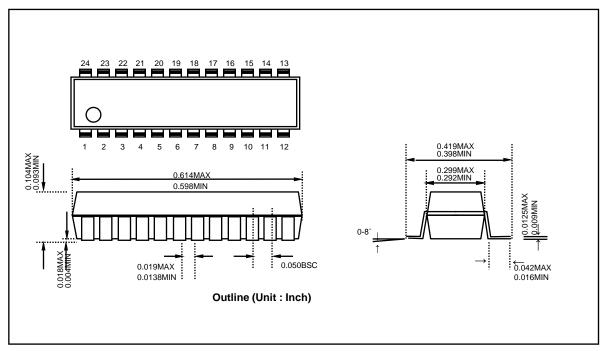

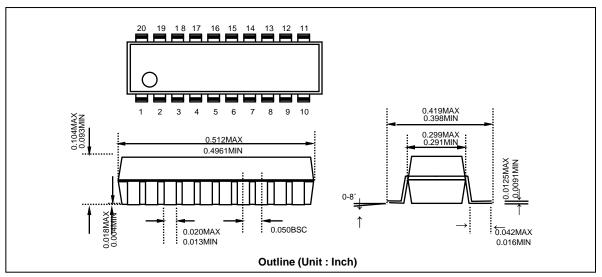

## 1.4. Package Dimension

28 SOP Pin Dimension (dimensions in inch)

28 TSSOP Pin Dimension (dimensions in millimeter)

24 SOP Pin Dimension (dimensions in inch)

20 SOP Pin Dimension (dimensions in inch)

## 1.5. Pin Function

| PIN<br>NAME                                          | INPUT<br>OUTPUT                                          | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | @RESET                  | @STOP                      |

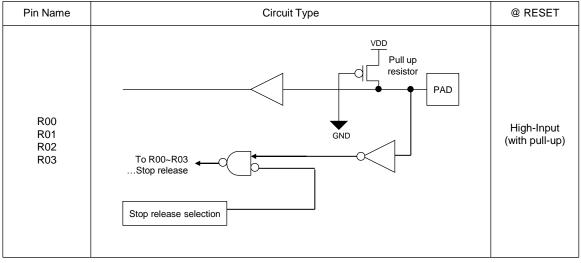

|------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|----------------------------|

| R00<br>R01<br>R02<br>R03                             | INPUT<br>INPUT<br>INPUT<br>INPUT                         | <ul> <li>- 4-bit input Port.</li> <li>- CMOS input with pull-up resistor.</li> <li>- Can be selectable as STOP release Input pin individually by user program.</li> <li>(It is released by "L" input at STOP mode)</li> </ul>                                                                                                                                                                                                                                                                | Input<br>(with Pull-up) | -                          |

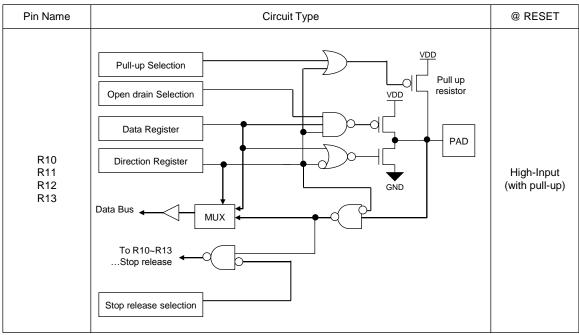

| R10<br>R11<br>R12<br>R13                             | 1/0<br>1/0<br>1/0<br>1/0                                 | <ul> <li>4-bit I/O Port.</li> <li>CMOS input with pull-up resistor.</li> <li>Pull-ups can be disabled by user Program.</li> <li>Can be selectable as STOP release Input<br/>pin individually by user program.</li> <li>(It is released by "L" input at STOP mode)</li> <li>N-ch open drain output.</li> <li>Can be programmable as Push-pull<br/>output individually.</li> <li>Each pin can be set and reset<br/>by R1 Data register value.</li> </ul>                                       | Input<br>(with Pull-up) | State<br>of before<br>STOP |

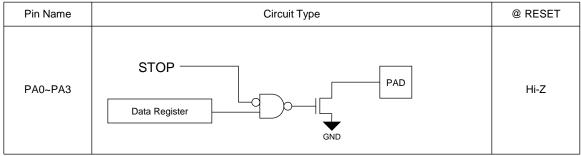

| PA0<br>PA1<br>PA2<br>PA3                             | OUTPUT<br>OUTPUT<br>OUTPUT<br>OUTPUT                     | <ul> <li>N-ch open drain output.</li> <li>Each pin can be set and reset<br/>by PA Data register value.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                            | Hi-Z                    | "L" level<br>output        |

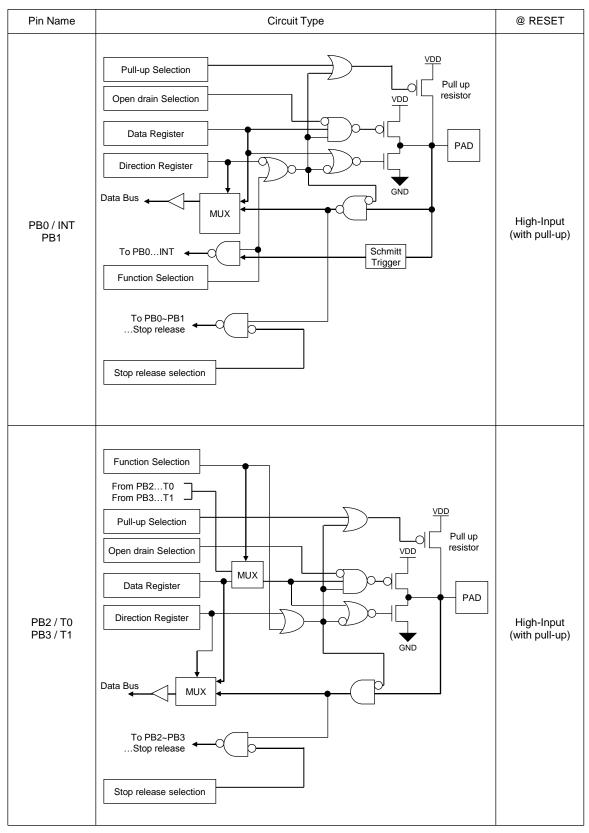

| PB0/INT<br>PB1<br>PB2/T0<br>PB3/T1                   | 1/0<br>1/0<br>1/0<br>1/0                                 | <ul> <li>4-bit I/O Port.</li> <li>CMOS input with pull-up resistor.</li> <li>Pull-ups can be disabled by user Program.</li> <li>Can be selectable as STOP release Input<br/>pin individually by user program.</li> <li>(It is released by "L" input at STOP mode)</li> <li>N-ch open drain output.</li> <li>Can be programmable as Push-pull<br/>output individually.</li> <li>Direct Driving of LED(N-TR).</li> <li>Each pin can be set and reset<br/>by PB Data register value.</li> </ul> | Input<br>(with Pull-up) | State<br>of before<br>STOP |

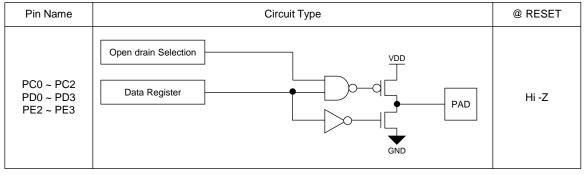

| PC0<br>PC1<br>PC2<br>PD0<br>PD1<br>PD2<br>PD3<br>PE2 | OUTPUT<br>OUTPUT<br>OUTPUT<br>OUTPUT<br>OUTPUT<br>OUTPUT | <ul> <li>N-ch open drain output.</li> <li>Can be programmable as Push-pull<br/>output individually.</li> <li>Direct Driving of LED(N-TR).</li> <li>Each pin can be set and reset<br/>by PC, PD and PE Data register value.</li> </ul>                                                                                                                                                                                                                                                        | Hi-Z                    | State<br>of before<br>STOP |

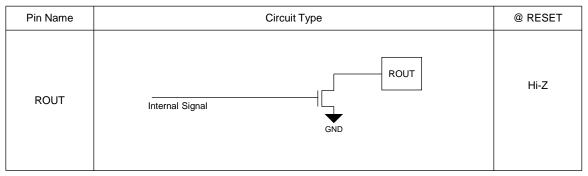

| PE3                                                  | OUTPUT                                                   | - High Current Output with built-in Tr.                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Hi-Z                    | Hi-Z                       |

| ROUT                                                 | OUTPUT                                                   | ( for ADAM41P2727/2723/2721 )<br>- High Current Output<br>( for ADAM41P2728/2724/2720 )                                                                                                                                                                                                                                                                                                                                                                                                      | "L" output              | "L" output                 |

| VDD                                                  | POWER                                                    | - Positive power supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -                       | -                          |

| GND                                                  | POWER                                                    | - Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -                       | _                          |

## 1.6. Port Structure

#### 1.6.2. R1 Ports

#### 1.6.3. PA Ports

#### 1.6.4. PB Ports

NOTE > PB3 ports is not available in ADAM41P2720 and ADAM41P2721

#### 1.6.5. PC/ PD/ PE Ports

NOTE > PD0~PD3 ports are not available in ADAM41P2724 and ADAM41P2723 NOTE2 > PC1, PC2, PD0~PD3, PE3 ports are not available in ADAM41P2720 and ADAM41P2721

#### 1.6.6. ROUT Port for ADAM41P2727, ADAM41P2723 and ADAM41P2721

#### 1.6.7. ROUT Port for ADAM41P2728, ADAM41P2724 and ADAM41P2720

| Pin Name | Circuit Type    | @ RESET   |

|----------|-----------------|-----------|

| ROUT     | Internal Signal | Low Level |

## 1.7. Electrical Characteristics

| PARAMETER           | SYMBOL | RATINGS          | UNIT |

|---------------------|--------|------------------|------|

| Supply Voltage      | Vdd    | -0.3 ~ +6.0      | V    |

| Input Voltage       | Vı     | -0.3 ~ Vdd + 0.3 | V    |

| Output Voltage      | Vo     | -0.3 ~ Vdd + 0.3 | V    |

| Storage Temperature | Тѕтс   | -65 ~ 150        | Ĉ    |

| Power Dissipation   | PD     | 700              | mW   |

\* Thermal derating above 25  $^\circ\!\!{\rm C}$  : 6mW per degree  $^\circ\!\!{\rm C}$  rise in temperature.

| PARAMETER             | SYMBOL | CONDITION                                                           | MIN. | TYP. | MAX. | UNIT |

|-----------------------|--------|---------------------------------------------------------------------|------|------|------|------|

| Supply Voltage        | )/     | fosc = 4MHz<br>(Temp = 25℃)                                         | 1.8  |      | 3.6  | V    |

| Supply Voltage        | VD     | fosc = 4MHz<br>(Temp = -20 ~ 70 ℃)                                  | 2.0  |      | 3.6  | V    |

| Oscillation Frequency | fosc   | Internal RC Oscillator<br>(VDD = 1.8 ~ 3.6V)<br>(Temp = -20 ~ 70 ℃) | 3.92 | 4.0  | 4.08 | MHz  |

| Operating Temperature | Topr   |                                                                     | -20  |      | 70   | Ĉ    |

| 1.7.3. DC Characteristics | (VDD = 1.8V~3.6V) | GND = 0V. Ta = 25℃)      |

|---------------------------|-------------------|--------------------------|

|                           |                   | <b>ee</b> ., <b>e</b> ., |

|                                      |        |                             | •                      |                        | s       | Specification |        |      |  |  |

|--------------------------------------|--------|-----------------------------|------------------------|------------------------|---------|---------------|--------|------|--|--|

| PARAMETER                            | Symbol | Condition                   |                        |                        | MIN.    | TYP.          | MAX.   | UNIT |  |  |

| High level                           | VIH1   | INT                         | INT                    |                        |         |               | VDD    | V    |  |  |

| input voltage                        | VIH2   | R0, R1, PB                  |                        |                        | 0.7VDD  |               | VDD    | V    |  |  |

| Low level                            | VIL1   | INT                         |                        |                        | 0       |               | 0.2VDD | V    |  |  |

| input voltage                        | VIL2   | R0, R1, PB                  |                        |                        | 0       |               | 0.3VDD | V    |  |  |

| High level input<br>leakage current  | ШН     | R0, R1, PB                  |                        | VIH = VDD              |         |               | 1      | μA   |  |  |

| Low level input leakage current      | IIL    | R0, R1, PB<br>( without Pul | l-up)                  | VIL = 0V               |         |               | -1     | μA   |  |  |

| High level<br>output voltage         | VOH1   | R1, PB, PC,                 | R1, PB, PC, PD, PE     |                        | VDD-0.4 |               |        | V    |  |  |

| Low level                            | VOL1   | R1, PA                      | R1, PA                 |                        |         |               | 0.8    | V    |  |  |

| output voltage                       | VOL2   | PB, PC, PD,                 | PB, PC, PD, PE         |                        |         |               | 0.8    | V    |  |  |

| High level output<br>leakage current | IOHL   | R1, PA, PB, PC, PD, PE      |                        | VOH = VDD              |         |               | 1      | μA   |  |  |

| Low level output leakage current     | IOLL   | R1, PA, PB,                 | R1, PA, PB, PC, PD, PE |                        |         |               | -1     | μA   |  |  |

| High level<br>output current         | юн     | ROUT<br>(for ADAM41         | 1P2728/24/20)          | VDD = 3V<br>VOH = 2V   | -30     | -12           | -5     | mA   |  |  |

| Low level                            | IOL1   | ROUT<br>(for ADAM41         | 1P2728/24/20)          | VDD = 3V<br>VOL = 1V   | 0.5     |               | 5      | mA   |  |  |

| output current                       | IOL2   | ROUT<br>(for ADAM41         | 1P2727/23/21)          | VDD = 3V<br>VOL = 0.3V |         | 250           |        | mA   |  |  |

| Input Pull-up<br>current             | IP     | R0, R1, PB                  |                        | VDD =3V                | 10      | 30            | 60     | μA   |  |  |

|                                      |        | Operating                   | £ 40.41.1-             | VDD = 3.6V             |         | 0.8           | 2.4    | mA   |  |  |

| Power                                | IDD    | current                     | fosc = 4MHz            | VDD = 1.8V             |         | 0.5           | 1.5    | mA   |  |  |

| supply<br>current                    | ISTOP  | Stop mode                   | Oscillator             | VDD = 3.6V             |         | 2.5           | 8      | μA   |  |  |

|                                      | 1310P  | current                     | stop                   | VDD = 1.8V             |         | 0.5           | 1.5    | μA   |  |  |

| RAM retention supply voltage         | VRET   |                             |                        |                        | 0.7     |               |        | V    |  |  |

| No. | Devenueter                      | Symbol | Pin | s    | UNIT |      |      |

|-----|---------------------------------|--------|-----|------|------|------|------|

|     | Parameter                       |        |     | MIN. | TYP. | MAX. | UNIT |

| 1   | Internal RCOSC clock cycle time | tcp    | -   | -    | 250  | -    | ns   |

| 2   | System clock cycle time         | tsys   | -   | -    | 1000 | -    | NS   |

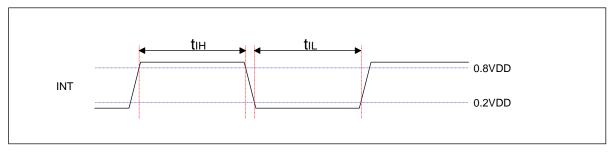

| 3   | Interrupt pulse width High      | tıн    | INT | 2    |      |      | tsys |

| 4   | Interrupt pulse width Low       | tı∟    | INT | 2    |      |      | tsys |

1.7.4. AC Characteristics (VDD =  $1.8V \sim 3.6V$ , GND = 0V, Ta =  $25^{\circ}C$ )

Fig. 1.1 Timing Chart

#### \* Internal RC Oscillator Characteristics Graphs (for reference only)

# 2. FUNCTION DESCRIPTION

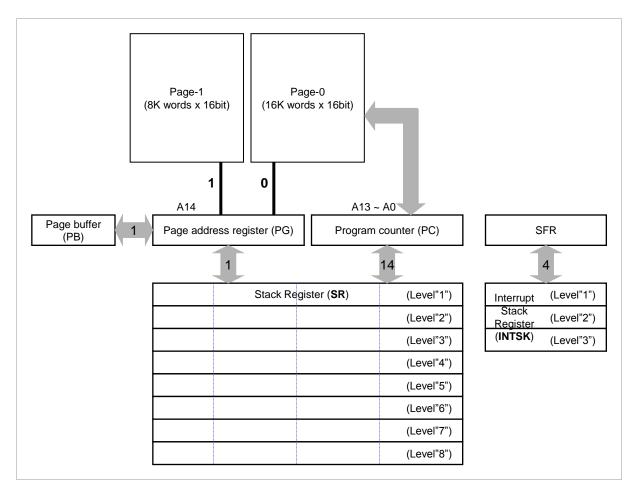

## 2.1. Program Memory

The ADAM41P272X can incorporate maximum 48K bytes  $(24K \times 16bits)$  for program memory. Program counter PC (A0~A13) and page address register(A14) are used to address the whole area of program memory having an instruction (16bits) to be executed.

The program memory consists of 16K words on 0-page and 8K words on 1-page.

The program memory is composed as shown below.

Fig. 2.1 Configuration of Program Memory

## 2.2. Address Register

The following registers are used to address the ROM.

- Page address register (PG) : Holds ROM's page number (0page, 1page) to be addressed.

- Page buffer register (PB) :

Value of PB is loaded by an LPG command when newly addressing a page. Then it is shifted into the PG when rightly executing a branch instruction (BR) and a subroutine call (CAL).

- Program counter (PC) : Available for addressing word on each page.

- Stack register (SR) : Stores returned-word address in the subroutine call mode.

- 2.2.1. Page address register (PG) and page buffer register (PB)

Address one of 0 page to 1 page in the ROM by the 1-bit page address register. Unlike the program counter, the page address register is usually unchanged so that the program will repeat on the same page unless a page changing command is issued. To change the page address, take two steps such as (1) writing in the page buffer what page to jump (execution of LPG) and (2) execution of BR or CAL, because instruction code is of eight bits so that page and word can not be specified at the same time.

In case a return instruction (RET) is executed within the subroutine that has been called in the other page, the page address will be changed at the same time.

#### 2.2.2. Program counter (PC)

This 14-bit binary counter increments is for fetching a word to be addressed in the currently addressed page having an instruction to be next executed.

For easier programming, at turning on the power, the program counter is reset to the zero location(0000H). The PG is also set to "0". Then the program counter specifies the next address.

When BR, CAL or RET instructions are decoded, the switches on each step are turned off not to update the address.

Then, for BR or CAL, address data are taken in from the instruction operands (A0 to A13), or for RET, and address including page address is fetched from stack register No. 1.

#### 2.2.3. Stack register (SR)

The stack register provides two stages each for the program counter (14bits) and the page address register (1bit) so that subroutine nesting can be made on eight levels.

The address stack register (ADS) stores a return address when the subroutine call instruction is executed or interrupt is acknowledged.

If subroutine or interrupts are nested to more than 8 levels, internal reset is occurred.

The interrupt stack register(INTSK) saves the contents of Status Flag Register (SFR) when an interrupt is acknowledged.

The saved contents are restored when an interrupt return(RETI) instruction is executed.

INTSK saves data each time an interrupt is acknowledged.

The programmer must keep in mind that the level of INTSK is only 3. So, if more over 3 levels of interrupt occur, the first stored data is lost. There is different result between Stack overflow and interrupt stack overflow.

When clearing SP (Stack Pointer) with using "SPC" instruction, interrupt processing must be inhibited before "SPC".

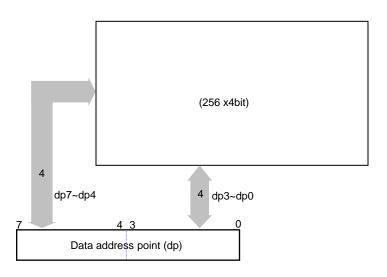

## 2.3. Data Memory (RAM)

256 nibbles (256  $\times$  4bits) is incorporated for storing data.

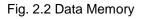

#### 2.3.1. Data memory (RAM) addressing method

The whole data memory area is directly addressed by 8-bit ram data address point (dp). Index data memory addressing is available using X-register and Y-register. In this case, X-register is added upper 4bit of data point and Y-register is added lower 4bit of data point.

Fig. 2.3 Data Memory Map

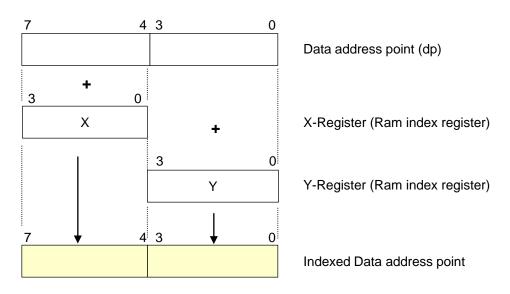

Below program example is guidance for understanding the flow of index data memory addressing.

| MEM0 EQU                                      | 033h                                    | ; Defining RAM Address                                                                                                                                                                |

|-----------------------------------------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LDM<br>LDY<br>LDX<br>LDA<br>EIX<br>LDM<br>DIX | MEM0,#0Ah<br>#7<br>#1<br>MEM0<br>MEM0,A | ; [33h] = #0Ah<br>; Setting Y register as #07h<br>; Setting X register as #01h<br>; A = #0Ah == [MEM0]<br>; Index Enable<br>; [4Ah] == [Indexed Addressed Ram] = A<br>; Index Disable |

Result after executing is MEM0 = #0Ah[MEM0 + X + Y] = = [4Ah] = #0Ah

## 2.4. General Function Registers

#### 2.4.1. X-register (X)

X-register consist of 4 bits. It can be used for a general-purpose register and also for data memory indexing register.

#### 2.4.2. Y-register (Y)

Y-register consist of 4 bits. It can be used for a general-purpose register and also for data memory indexing register.

#### 2.4.3. Accumulator (ACC)

The 4-bit register for holding data and calculation results.

#### 2.4.4. Peripheral Address Register (PAR)

The 6-bit address register for addressing peripheral registers including address buffer register (ABR), data buffer register (DBR).

#### 2.4.5. Address Buffer Register (ABR)

The 15-bit register for address buffer.

It is composed of 3 registers(ABR0, ABR1, ABR2) x 4bit and 1 register(ABR3) x 3bit.

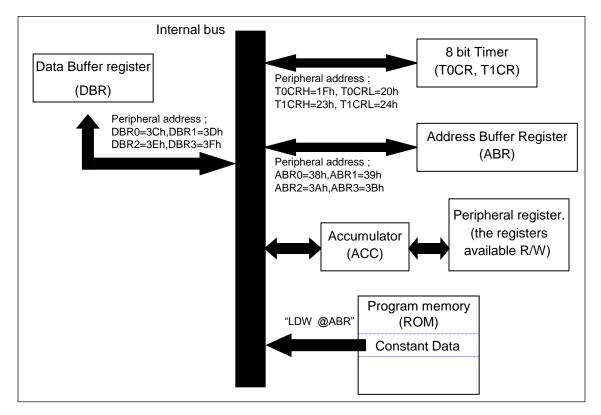

## 2.5. Buffer Registers (DBR,ABR)

Buffer registers are two types of 16 bit registers composed of 4 nibble registers. One is Data Buffer Register (DBR) and the other is Address Buffer Register (ABR). The address of Data Buffer Register (DBR) is 3Ch ~ 3Fh and the address of Address Buffer Register (ABR) is 38h ~ 3Bh on the peripheral register.

These buffers are mainly used for Data transferring between ROM and buffer or peripheral registers and buffer. They are also used for general purpose register for data manipulation, data storage and intermediate buffer.

2.5.1. Function of Data Buffer Register(DBR)

The most important function of DBR is intermediate (window) buffer for transferring data between peripheral registers and reading data from ROM.

When the data of ROM is read by "LDW @ABR", one word of ROM is fetched to DBR. The MSB of ROM data is written to DBR3 and LSB to DBR0.

If the data of pointed ROM is 1234h, each DBR has the data as DBR0 = 4h, DBR1 = 3h, DBR2 = 2h and DBR3 = 1h.

DBR is also used for reading some peripheral register data by 8bit unit. The peripheral registers are T0CR and T1CR.

Note > HEX. File maps the data as big endian type. Be careful to read the ROM data. When the programmer assigns the data like below, the ROM data is mapped as below DB 12h,34h → ROM data = 1234h

2.5.2. Function of Address Buffer Register (ABR)

The most important function of ABR is ROM address pointer.

ABR must be used for reading data from ROM. The data pointed by ABR is read to DBR. ABR value is varied through peripheral control instruction and "INC ABR".

Fig. 2.4 The internal Data flow among DBR, ABR , registers and ROM

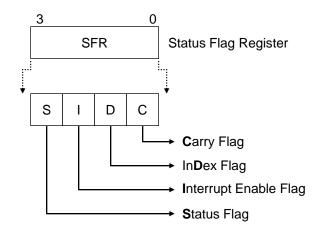

## 2.6. Status Flag Register (SFR)

Status Flag Register (SFR) consists of 4-bit register.

Each of the flags show the post state of operation and the flags determining the CPU operation, initialized as 0h in reset state.

When an interrupt is occurred, the value of SFR keep the value of pre- interrupt except for I flag. So, be careful to initialize the SFR status for getting reliable result in Interrupt sub-routine.

2.6.1. **C**arry flag (**C**)

- Carry flag bit is set when there is carry or borrow After executing ADDC / SUBC / ARRC / ARLC instructions.

- Set by SETC and clear by CLRC.

2.6.2. In**D**ex flag (**D**)

- The control bit of ram data address point indexed or not.

- X-register and Y-register is used for index addressing.

- Set and cleared by EIX, DIX.

2.6.3. Interrupt enable flag (I)

- Master enable flag of interrupt.

- Set and cleared by EI, DI

- This flag immediately becomes "0" when an interrupt is served.

2.6.4. Status flag (S)

- According to the condition after executing an instruction , set or clear.

- Can not be set or clear by any instruction.

- This flag decides whether operation of BR and CALL would be done or not.

## 2.7. Peripheral Registers

| Peripheral | Eurotica Devictora                      | Read  | Querrahal | RI | ESE | T Va  | lue |

|------------|-----------------------------------------|-------|-----------|----|-----|-------|-----|

| Address    | Function Registers                      | Write | Symbol    | 3  | 2   | 1     | 0   |

| 00 h       | PORT R0 STOP RELEASE SELECTION REG.     | W     | R0ST      |    |     | 0     |     |

| 00 h       | PORT R0 DATA REG.                       | R     | R0        | F  |     |       |     |

| 01 h       | PORT R1 STOP RELEASE SELECTION REG.     | W     | R1ST      |    | 0   |       |     |

| 02 h       | PORT R1 PULL UP RESISTOR SELECTION REG. | W     | R1PU      |    |     | 0     |     |

| 03 h       | PORT R1 OPEN DRAIN SELECTION REG.       | W     | R10D      |    |     | 0     |     |

| 04 h       | PORT R1 DATA REG.                       | R/W   | R1        |    |     | F     |     |

| 05 h       | PORT R1 DIRECTION REG.                  | W     | R1DD      |    |     | 0     |     |

| 06 h       | Reserved                                |       |           |    |     |       |     |

| 07 h       | PORT PA DATA REG.                       | R/W   | PA        |    |     | F     |     |

| 08 h       | PORT PB STOP RELEASE SELECTION REG.     | W     | PBST      |    |     | F     |     |

| 09 h       | PORT PB PULL UP RESISTOR SELECTION REG. | W     | PBPU      |    |     | 0     |     |

| 0A h       | PORT PB OPEN DRAIN SELECTION REG.       | W     | PBOD      |    |     | 0     |     |

| 0B h       | PORT PB DATA REG.                       | R/W   | PB        |    |     | F     |     |

| 0C h       | PORT PB FUNCTION SELECTION REG.         | W     | PBFN      | 0  | 0   | -     | 0   |

| 0D h       | PORT PB DIRECTION REG.                  | W     | PBDD      |    |     | 0     |     |

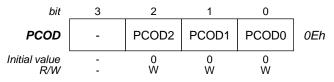

| 0E h       | PORT PC OPEN DRAIN SELECTION REG.       | W     | PCOD      |    | 0   |       |     |

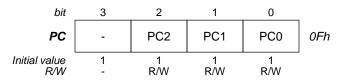

| 0F h       | PORT PC DATA REG.                       | R/W   | PC        |    |     | F     |     |

| 10 h       | PORT PD OPEN DRAIN SELECTION REG.       | W     | PDOD      |    |     | 0     |     |

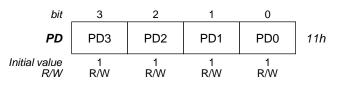

| 11 h       | PORT PD DATA REG.                       | R/W   | PD        |    |     | F     |     |

| 12 h       | Reserved                                |       |           |    |     |       |     |

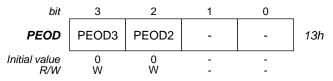

| 13 h       | PORT PE OPEN DRAIN SELECTION REG.       | W     | PEOD      |    |     | 0     |     |

| 14 h       | PORT PE DATA REG.                       | R/W   | PE        |    |     | F     |     |

| 15 h       | Reserved                                |       |           |    |     |       |     |

| 16 h       | Reserved                                |       |           |    |     |       |     |

| 17 h       | EXTERNAL INT. EDGE SELECTION REG.       | W     | IEDS      | -  | -   | 0     | 0   |

| 18 h       | INT. ENABLE REG.                        | R/W   | IENR      | 0  | 0   | 0     | 0   |

| 19 h       | INT. REQUEST FLAG REG.                  | R/W   | IRQR      | 0  | 0   | 0     | 0   |

| 1A h       | TIMER0 MODE REG.                        | R/W   | TOMR      |    | 0   |       |     |

| 1B h       | VOLTAGE DETECTION INDICATOR REGISTER    | R     | VDIR      | -  | -   | 0     | 0   |

| 1C h       | TIMER1 MODE REG.                        | R/W   | T1MR      |    |     | 0     |     |

| 1D h       | ROUT CONTROL REG .                      | R/W   | RCR       |    |     | 0     |     |

| 1E h       | CARRY MODE REG.                         | R/W   | CGMR      |    | 0   |       |     |

|            | TIMER 0 DATA0 HIGH REG.                 | W     | TODOH     |    | und | efine | d   |

| 1F h       | TIMER 0 COUNT REG. HIGH.                | R     | T0CRH     |    | und | efine | d   |

Note1> '-' is reserved bit , it must be read to "0".

| Peripheral | Eurotion Dedictors                   | Read  | Symbol | RESET Value |

|------------|--------------------------------------|-------|--------|-------------|

| Address    | Function Registers                   | Write | Symbol | 3 2 1 0     |

| 20 h       | TIMER 0 DATA 0 LOW REG.              | W     | TODOL  | undefined   |

| 20 h       | TIMER 0 COUNT REG. LOW.              | R     | TOCRL  | undefined   |

| 21 h       | TIMER 0 DATA 1 HIGH REG. W T0D1H und |       |        |             |

| 22 h       | TIMER 0 DATA 1 LOW REG.              | W     | T0D1L  | undefined   |

| 22 h       | TIMER 1 HIGH DATA REG.               | W     | T1HD   | undefined   |

| 23 h       | TIMER 1 COUNT REG. HIGH.             | R     | T1CRH  | undefined   |

| 24 h       | TIMER 1 LOW DATA REG.                | W     | T1LD   | undefined   |

| 24 h       | TIMER 1 COUNT REG LOW.               | R     | T1CRL  | undefined   |

| 25 h       | CARRY GENERATOR HIGH-MSB DATA REG.   | W     | CGHMD  | undefined   |

| 26 h       | CARRY GENERATOR HIGH-LSB DATA REG.   | W     | CGHLD  | undefined   |

| 27 h       | CARRY GENERATOR LOW-MSB DATA REG.    | W     | CGLMD  | undefined   |

| 28 h       | CARRY GENERATOR LOW-LSB DATA REG.    | W     | CGLLD  | undefined   |

| 29 h       | Reserved                             |       |        |             |

| 2A h       | Reserved                             |       |        |             |

| 2B h       | Reserved                             |       |        |             |

| 2C h       | Reserved                             |       |        |             |

| 2D h       | Reserved                             |       |        |             |

| 2E h       | Reserved                             |       |        |             |

| 2F h       | Reserved                             |       |        |             |

| 30 h       | Reserved                             |       |        |             |

| 31 h       | Reserved                             |       |        |             |

| 32 h       | Reserved                             |       |        |             |

| 33 h       | Reserved                             |       |        |             |

| 34 h       | Reserved                             |       |        |             |

| 35 h       | Reserved                             |       |        |             |

| 36 h       | Reserved                             |       |        |             |

| 37 h       | Reserved                             |       |        |             |

| 38 h       | ADDRESS BUFF REGISTER 0              | R/W   | ABR0   | undefined   |

| 39 h       | ADDRESS BUFF REGISTER 1              | R/W   | ABR1   | undefined   |

| 3A h       | ADDRESS BUFF REGISTER 2              | R/W   | ABR2   | undefined   |

| 3B h       | ADDRESS BUFF REGISTER 3              | R/W   | ABR3   | - x x x     |

| 3C h       | DATA BUFF REGISTER 0                 | R/W   | DBR0   | undefined   |

| 3D h       | DATA BUFF REGISTER 1                 | R/W   | DBR1   | undefined   |

| 3E h       | DATA BUFF REGISTER 2                 | R/W   | DBR2   | undefined   |

| 3F h       | DATA BUFF REGISTER 3                 | R/W   | DBR3   | undefined   |

Note1> '-' is reserved bit , it must be read to "0". 'x' is undefined bit.

# 3. I/O Ports

The ADAM41P272X has maximum 25 Input or output ports which are R0 (4 Input), R1 (4 I/O), PA (4 Output), PB (4 I/O), PC (3 Output), PD (4 Output), PE(2 Output).

R0, R1 and PB input Port have Stop Release selection register.

Pull-up resistors of R1 and PB port can be selectable by program. R1 and PB port contains data direction register which controls I/O and data register which stores port data.

R1, PA, PB, PC, PD, PE Ports have Open Drain output selection register.

## 3.1. Port R0

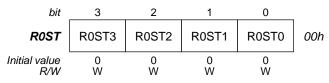

3.1.1. R0 Stop Release Selection Register (R0ST)

R0 Stop Release Selection Register (R0ST) is 4-bit register and can assign stop release pin or not.

If R0ST is selected as "0", stop release function is enabled and if selected as "1", it is disabled. R0ST is write-only register and initialized as "0h" in reset state.

#### 3.1.1. R0 DATA Register (R0)

| bit                  | 3      | 2      | 1      | 0      |     |

|----------------------|--------|--------|--------|--------|-----|

| R0                   | R03    | R02    | R01    | R00    | 00h |

| Initial value<br>R/W | 1<br>R | 1<br>R | 1<br>R | 1<br>R |     |

R0 data register (R0) is 4-bit register to store data of port R0. Since R0 port is input only port, input state of pin is read. The initial value of R0 is "Fh" in reset state.

## 3.2. Port R1

3.2.1. R1 Stop Release Selection Register (R1ST)

| bit                  | 3      | 2      | 1      | 0      |     |

|----------------------|--------|--------|--------|--------|-----|

| R1ST                 | R1ST3  | R1ST2  | R1ST1  | R1ST0  | 01h |

| Initial value<br>R/W | 0<br>W | 0<br>W | 0<br>W | 0<br>W |     |

R1 Stop Release Selection Register (R1ST) is 4-bit register and can assign stop release pin or not.

If R1ST is selected as "0", stop release function is enabled and if selected as "1", it is disabled. R1ST is write-only register and initialized as "0h" in reset state.

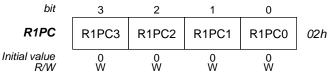

#### 3.2.2. R1 Pull-up Resistor Control Register (R1PC)

R1 pull-up resistor control register (R1PC) is 4-bit register and can control pull-up on or off each port, if corresponding port is selected as input. If R1PC is selected as "0", pull-up is enabled and if selected as "1", it is disabled. R1PC is write-only register and initialized as "0h" in reset state.

The pull-up is automatically disabled, if corresponding port is selected as output.

3.2.3. R1 Open Drain Assign Register (R1OD)

| bit                  | 3      | 2      | 1      | 0      |     |

|----------------------|--------|--------|--------|--------|-----|

| R10D                 | R1OD3  | R1OD2  | R1OD1  | R1OD0  | 03h |

| Initial value<br>R/W | 0<br>W | 0<br>W | 0<br>W | 0<br>W |     |

R1 Open Drain Assign Register (R1OD) is 4-bit register, and can assign R1 port as open drain output port for each bit. If R1OD is selected as "0", port R1 is open drain output, and if selected as "1", it is push-pull output. R1OD is write-only register and initialized as "0h" in reset state.

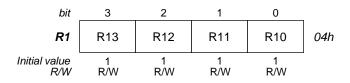

3.2.4. R1 Data Register (R1)

R1 data register (R1) is 4-bit register to store data of port R1. When set as the output state by R1DD, written data in R1 is outputted through R1 pin. When set as the input state, input state of pin is read to R1. The initial value of R1 is "Fh" in reset state.

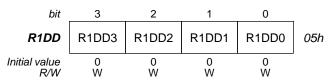

3.2.5. R1 I/O Data Direction Register (R1DD)

R1 I/O Data Direction Register (R1DD) is 4-bit register, and can assign input state or output state to each bit. If R1DD is "0", port R1 is in the input state, and if "1", it is in the output state. R1DD is write-only register. Since R1DD is initialized as "0h" in reset state, the whole port R1 becomes input state.

## 3.3. Port PA

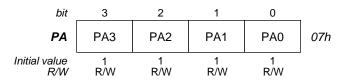

3.3.1. PA Data Register (PA)

PA data register (PA) is 4-bit register to store data of port PA. The initial value of PA is "Fh" in reset state.

## 3.4. Port PB

| Pin Name  | Port Selection | Function Selection |

|-----------|----------------|--------------------|

| PB0 / INT | PB0 (I/O)      | INT input          |

| PB1       | PB1 (I/O)      | -                  |

| PB2 / T0  | PB2 (I/O)      | Timer 0 output     |

| PB3 / T1  | PB3 (I/O)      | Timer 1 output     |

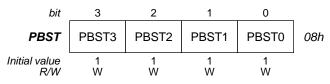

3.4.1. PB Stop Release Selection Register (PBST)

PB Stop Release Selection Register (PBST) is 4-bit register,

and can assign stop release pin or not.

If PBST is selected as "0", stop release function is enabled and if selected as "1", it is disabled. PBST is write-only register and initialized as "Fh" in reset state.

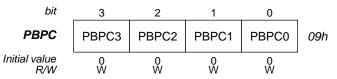

3.4.2. PB Pull-up Resistor Control Register (PBPC)

PB pull-up resistor control register (PBPC) is 4-bit register and can control pull-up on or off each bit, if corresponding port is selected as input. If PBPC is selected as "0", pull-up is enabled and if selected as "1", it is disabled. PBPC is write-only register and initialized as "0h" in reset state.

The pull-up is automatically disabled, if corresponding port is selected as output.

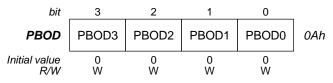

3.4.3. PB Open Drain Assign Register (PBOD)

PB Open Drain Assign Register (PBOD) is 4-bit register, and can assign PB port as open drain output port for each bit. If PBOD is selected as "0", port PB is open drain output, and if selected as "1", it is push-pull output. PBOD is write-only register and initialized as "0h" in reset state.

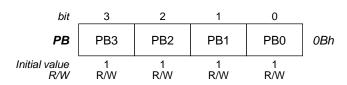

3.4.4. PB Data Register (PB)

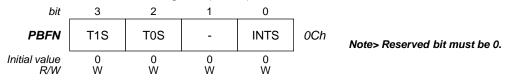

PB data register (PB) is 4-bit register to store data of port PB. The initial value of PB is "Fh" in reset state. 3.4.5. PB Function selection Register (PBFN)

PB Function selection Register (PBFN) is 4-bit register, and can assign the Function mode for each bit.

When set as "0", corresponding bit of PBFN acts as port PB selection mode, and when set as "1", it becomes function selection mode.

#### Selection Mode of PBFN

| Bit Name | PMR1 | Selection Mode                    | Remarks                                                                    |

|----------|------|-----------------------------------|----------------------------------------------------------------------------|

| 740      | 0    | PB3 select (I/O)                  | -                                                                          |

| T1S      | 1    | Timer1 output select (output)     | The output status is toggled (L<>H)<br>every T1 Output (refer to Fig. 4.5) |

| TOO      | 0    | PB2 select (I/O)                  | -                                                                          |

| TOS      | 1    | Timer0 output select (output)     | The output status is same as T0 Output (refer to Fig. 4.4)                 |

|          |      |                                   | -                                                                          |

| -        |      |                                   | -                                                                          |

| INTS     | 0    | PB0 select (I/O)                  | -                                                                          |

| 1115     | 1    | External Interrupt select (input) | -                                                                          |

PBFN is write-only register and initialized as "0h" in reset state. Therefore, becomes I/O Port mode.

3.4.6. PB I/O Data Direction Register (PBDD)

| bit                  | 3      | 2      | 1      | 0      |     |

|----------------------|--------|--------|--------|--------|-----|

| PBDD                 | PBDD3  | PBDD2  | PBDD1  | PBDD0  | 0Dh |

| Initial value<br>R/W | 0<br>W | 0<br>W | 0<br>W | 0<br>W |     |

PB I/O Data Direction Register (PBDD) is 4-bit register, and can assign input state or output state to each bit. If PBDD is "0", port PB is in the input state, and if "1", it is in the output state. PBDD is write-only register. Since PBDD is initialized as "0h" in reset state, the whole port PB becomes input state.

## 3.5. Port PC

3.5.1. PC Open Drain Assign Register (PCOD)

PC Open Drain Assign Register (PCOD) is 3-bit register, and can assign PC port as open drain output port for each bit. If PCOD is selected as "0", port PC is open drain output, and if selected as "1", it is push-pull output. PCOD is write-only register and initialized as "0h" in reset state.

3.5.2. PC Data Register (PC)

PC data register (PC) is 3-bit register to store data of port PC. The initial value of PC is "Fh" in reset state.

## 3.6. Port PD

3.6.1. PD Open Drain Assign Register (PDOD)

| bit                  | 3      | 2      | 1      | 0      |     |

|----------------------|--------|--------|--------|--------|-----|

| PDOD                 | PDOD3  | PDOD2  | PDOD1  | PDOD0  | 10h |

| Initial value<br>R/W | 0<br>W | 0<br>W | 0<br>W | 0<br>W |     |

PD Open Drain Assign Register (PDOD) is 4-bit register, and can assign PD port as open drain output port for each bit. If PDOD is selected as "0", port PD is open drain output, and if selected as "1", it is push-pull output. PDOD is write-only register and initialized as "0h" in reset state.

3.6.2. PD Data Register (PD)

PD data register (PD) is 4-bit register to store data of port PD. The initial value of PD is "Fh" in reset state.

## 3.7. Port PE

3.7.1. PE Open Drain Assign Register (PEOD)

PE Open Drain Assign Register (PEOD) is 2-bit register, and can assign PE port as open drain output port for each bit. If PEOD is selected as "0", port PE is open drain output, and if selected as "1", it is push-pull output. PEOD is write-only register and initialized as "0h" in reset state.

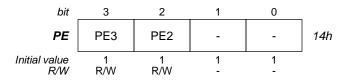

3.7.2. PE Data Register (PE)

PE data register (PE) is 2-bit register to store data of port PE. The initial value of PE is "Fh" in reset state.

# 4. PERIPHERAL HARDWARE

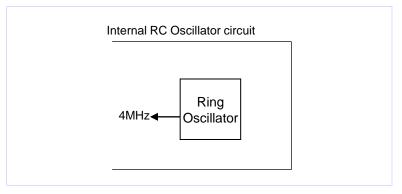

## 4.1. Oscillation Circuit

There is only 1 type of Oscillation circuit.

It is Internal RC Oscillator circuit. The Internal Oscillator is calibrated in the OTP Writer. In STOP mode, Internal RC oscillator is stopped.

Clock from oscillation circuit makes CPU clock via clock pulse generator, and then provide peripheral hardware clock.

Fig. 4.1 Oscillator configurations

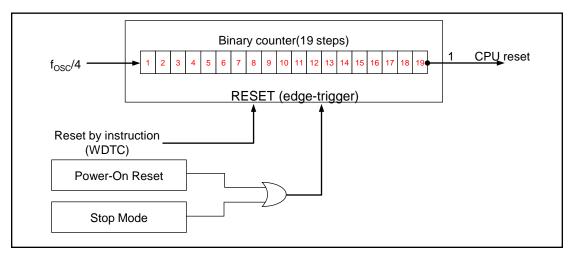

## 4.2. Watch Dog Timer (WDT)

Watch Dog Timer (WDT) is organized binary of 19 steps. The signal of fosc/4 cycle comes in the first step of WDT after WDT reset. If the last step would be "1", reset signal automatically comes out and internal circuit is initialized.

The overflow time is  $2^{18} \times 4/f_{OSC}$  (262.144ms at fosc = 4.0MHz).

Normally, the binary counter must be reset before the overflow by using reset instruction (WDTC), Power-on reset pulse or Low VDD detection pulse.

\* It is constantly reset in STOP mode. When STOP is released, counting is restarted.

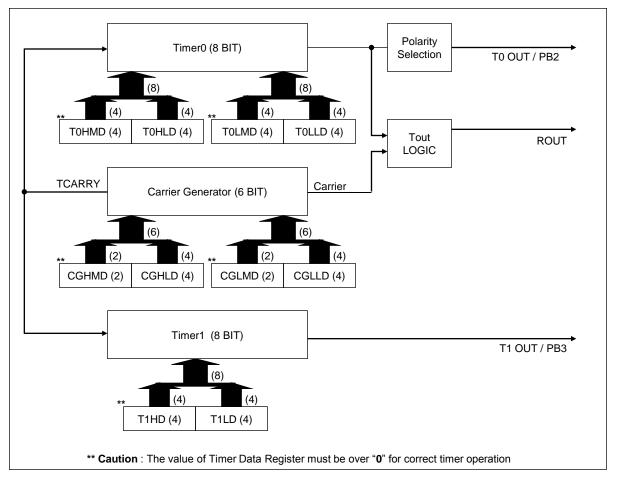

## 4.3. Timer

4.3.1. Timer operation mode

Timer is basically made of Timer Data Register, Timer Mode Register and control circuit. The types of Timer are 8bit binary counter Timer0 (T0), 8bit binary counter Timer1 (T1), Carrier Generator (CG).

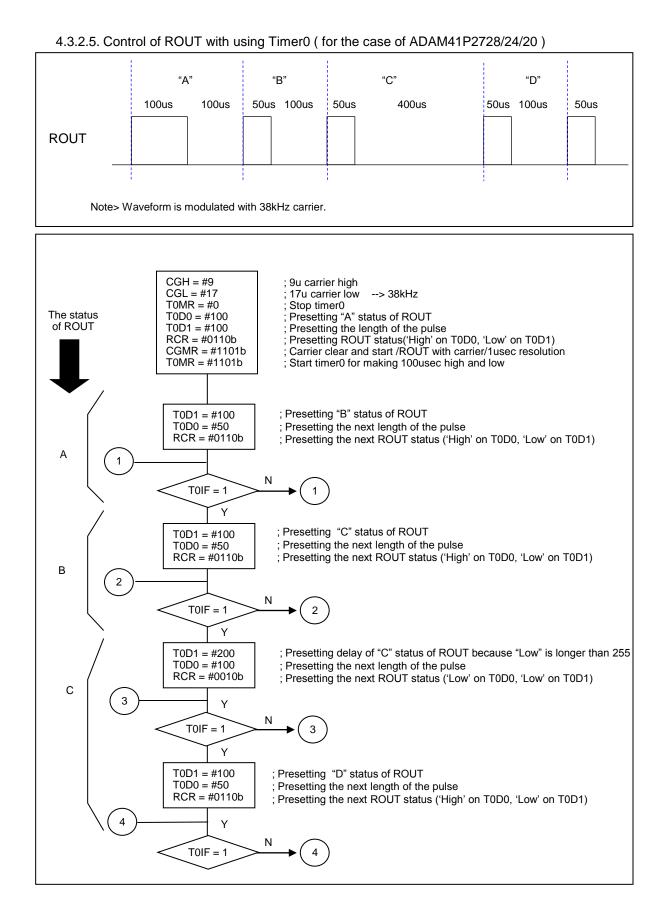

**Timer0 Data Register** consists of Timer0 Data 0 High Register (T0D0H), Timer0 Data 0 Low Register (T0D0L), Timer0 Data 1 High Register (T0D1H) and Timer0 Data 1 Low Register (T0D1L).

**Timer1 Data Register** consists of Timer1 Low Data Register (T1LD), Timer1 High Data Register (T1HD).

**Carrier Generator** consists of Carrier Generator High MSB Data Register (CGHMD), Carrier Generator High LSB Data Register (CGHLD), Carrier Generator Low MSB Data Register (CGLMD) and Carrier Generator Low LSB Data Register (CGLLD).

| Timer0               | - 8-bit Interval Timer<br>- 8-bit rectangular-wave output |

|----------------------|-----------------------------------------------------------|

| Timer1               | - 8-bit Interval Timer<br>- 8-bit rectangular-wave output |

| Carrier<br>Generator | - 6-bit up-Counter<br>- 6-bit rectangular-wave output     |

Fig. 4.3 Timer / Counter Block diagram

| 4.3.2. Function of | Timer & Counter |

|--------------------|-----------------|

|--------------------|-----------------|

|                 |            |                     |            |                        | fosc = 4MHz |

|-----------------|------------|---------------------|------------|------------------------|-------------|

| 8bit Timer (    | Timer0)    | 8bit Timer (Timer1) |            | Carrier Generator (CG) |             |

| Resolution (CK) | Max. Count | Resolution (CK)     | Max. Count | Resolution (CK)        | Max. Count  |

| TCK1 : 0. 5 us  | 128 us     | TCK1:0.5 us         | 128 us     | TCK1 : 0. 5 us         | 32 us       |

| TCK2 : 1 us     | 256 us     | TCK2 : 1 us         | 256 us     | TCK2 : 1 us            | 64 us       |

| TCK3 : 2 us     | 512 us     | TCK3 : 2 us         | 512 us     | TCK3 : 2 us            | 128 us      |

| TCARRY(*)       |            | TCARRY(*)           |            | TCK4:4 us              | 256 us      |

|                 |            |                     |            |                        |             |

(\*) Resolution & Max. count of TCARRY clock is decided by output of Carrier Generator

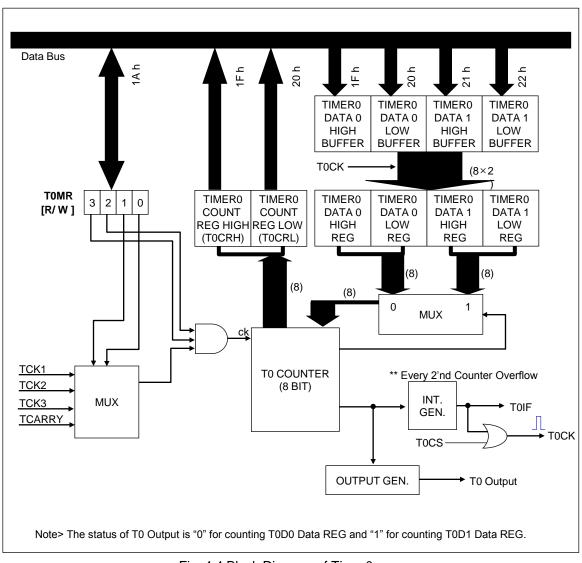

Fig. 4.4 Block Diagram of Timer0

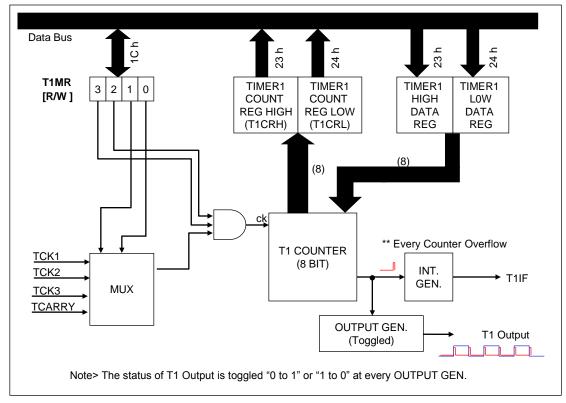

Fig. 4.5 Block Diagram of Timer1

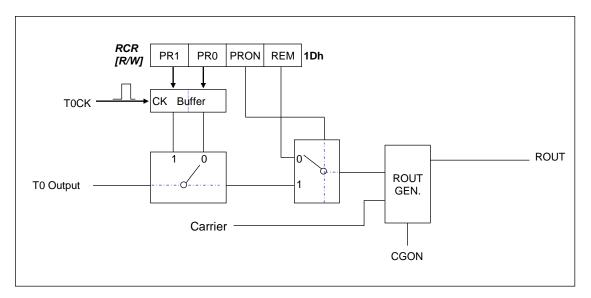

Fig. 4.6 Block Diagram of Carrier Generator

#### 4.3.2.1. Timer0 Mode Register

| bit                                                                                   | 3                                | 2                     | 1        | 0        |                               |

|---------------------------------------------------------------------------------------|----------------------------------|-----------------------|----------|----------|-------------------------------|

| Т0MR<br>[R/W]                                                                         | TOCS                             | TOCN                  | T0CK1    | T0CK0    | 1Ah                           |

| Initial value<br>R/W                                                                  | 0<br>R/W                         | 0<br>R/W              | 0<br>R/W | 0<br>R/W |                               |

|                                                                                       |                                  |                       | 00       | TCK1 (   | 500ns)                        |

| T0CK1                                                                                 | Input do                         | ak a clastian         | 01       | TCK2 (   | lus)                          |

| TOCK0                                                                                 | input cio                        | Input clock selection |          | TCK3 (2  | 2us)                          |

|                                                                                       |                                  |                       | 11       | TCARRY   | (output of Carrier Generator) |

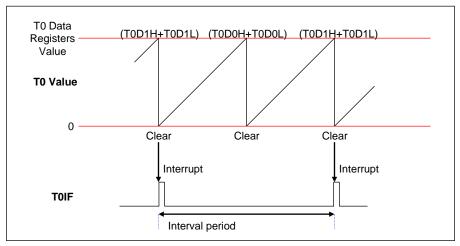

| TOCN                                                                                  | Timer0 Pause / Continue          |                       | e 0      | Timer0 F | ause                          |

| TUCIN                                                                                 | Control                          | Control               |          | Timer0 c | ontinue                       |

| TOCS                                                                                  | Timer0 Clear / start             |                       | 0        | Timer0 S | top                           |

| 1005                                                                                  | Control 1 Timer0 Clear and Start |                       |          |          |                               |

| * Timer 0 counts with 'T0D0H+T0D0L' first, after overflowed counts with 'T0D1H+T0D1L' |                                  |                       |          |          |                               |

#### 4.3.2.2. Timer1 Mode Register

| bit                  | 3                                  | 2        | 1        | 0         |                               |

|----------------------|------------------------------------|----------|----------|-----------|-------------------------------|

| T1MR<br>[R/W ]       | T1CS                               | T1CN     | T1CK1    | T1CK0     | 1Ch                           |

| Initial value<br>R/W | 0<br>R/W                           | 0<br>R/W | 0<br>R/W | 0<br>R/W  |                               |

| TION                 | Input clock selection              |          | 00       | TCK1 (5   | 00ns)                         |

| T1CK1<br>&<br>T1CK0  |                                    |          | 01       | TCK2 (1   | us)                           |

|                      |                                    |          | 10       | TCK3 (2   | us)                           |

|                      |                                    |          | 11       | TCARRY    | (output of Carrier Generator) |

| T1CN                 | Timer1 Pause / Continue<br>Control |          | e 0      | Timer1 Pa | ause                          |

|                      |                                    |          | 1        | Timer1 co | ontinue                       |

| T1CS                 | Timer1 Clear / start<br>Control    |          | 0        | Timer1 St | ор                            |

|                      |                                    |          | 1        | Timer1 Cl | ear and Start                 |

## 4.3.2.3. Carrier Generator Mode Register

| CGMR<br>[R/W ]       | CGCS                                       | CGON     | CGCK1    | CGCK0                                | 1Eh |

|----------------------|--------------------------------------------|----------|----------|--------------------------------------|-----|

| Initial value<br>R/W | 0<br>R/W                                   | 0<br>R/W | 0<br>R/W | 0<br>R/W                             |     |

| CGCK1<br>&<br>CGCK0  | Input clock selection                      |          | 00       | TCK1 (500ns)                         |     |

|                      |                                            |          | 01       | TCK2 (1us)                           |     |

|                      |                                            |          | 10       | TCK3 (2us)                           |     |

|                      |                                            |          | 11       | TCK4 (4                              | us) |

| CGON                 | Carrier Generator Output<br>Control        |          | Jt 0     | Output of ROUT without Carrier Pulse |     |

|                      |                                            |          | 1        | Output of ROUT with Carrier Pulse    |     |

| CGCS                 | Carrier Generator<br>Clear / start Control |          | 0        | Carrier Generator Stop               |     |

|                      |                                            |          | 1        | Carrier Generator Clear and Start    |     |

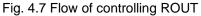

4.3.2.4. ROUT Control Register

| bit                  | 3        | 2        | 1        | 0        |     |

|----------------------|----------|----------|----------|----------|-----|

| RCR<br>[R/W ]        | PR1      | PR0      | PRON     | REM      | 1Dh |

| Initial value<br>R/W | 0<br>R/W | 0<br>R/W | 0<br>R/W | 0<br>R/W |     |

\* [ ] for ADAM41P2728/24/20

| REM Output of ROUT Bit Control<br>(When PRON=0) | 0                          | ROUT output Hi-Z<br>[ ROUT output low ]                                                                   |                                                                                                          |

|-------------------------------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

|                                                 | 1                          | ROUT output low [ROUT output high]                                                                        |                                                                                                          |

| PRON PR0 / PR1 Function<br>Control              | 0                          | PR0 / PR1 Function Disable ("REM" bit active)                                                             |                                                                                                          |

|                                                 | 1                          | PR0 / PR1 Function Enable ("REM" bit inactive)                                                            |                                                                                                          |

| PR0 Preset of ROUT Bit Control<br>(When PRON=1) | Preset of ROUT Bit Control | 0                                                                                                         | ROUT "H" on counting Timer0 DATA0 (T0D0H + T0D0L)<br>[ROUT "L" on counting Timer0 DATA0 (T0D0H + T0D0L)] |

|                                                 | 1                          | ROUT "L" on counting Timer0 DATA0 (T0D0H + T0D0L)<br>[ROUT "H" on counting Timer0 DATA0 (T0D0H + T0D0L) ] |                                                                                                          |

| PR1 Preset of ROUT Bit<br>(When PRON=1)         | Preset of ROUT Bit Control | 0                                                                                                         | ROUT "H" on counting Timer0 DATA1 (T0D1H + T0D1L)<br>[ROUT "L" on counting Timer0 DATA1 (T0D1H + T0D1L)] |

|                                                 | (When PRON=1)              | 1                                                                                                         | ROUT "L" on counting Timer0 DATA1 (T0D1H + T0D1L)<br>[ROUT "H" on counting Timer0 DATA1 (T0D1H + T0D1L)] |

\* ROUT Pin is Controlled by REM when PRON bit =0

\* ROUT Pin is Controlled by PR0, PR1 when PRON bit =1

Because Timer0 counts with Data0 (T0D0H+T0D0L) first , ROUT pin is controlled by PR0 initially.

4.3.3. Timer0

TIMER0 operates as a up-counter with two-8bit data register (T0D0H+T0D0L, T0D1H+T0D1L). When the value of the up-counter reaches the content of Timer Data Register, the up-counter is cleared to ``00 h``, and interrupt (T0IF) is occurred at the next clock.

Internal clock (TCK) and the output of Carrier Generator (TCARRY) is used as counter clock.

The counter execution is controlled by T0CS, T0CN, of T0MR.

TOCN is used to stop and start Timer0 without clearing the counter and TOCS does to clear and start the counter. During counting-up, value of counter can be read.

Timer execution is stopped by the reset signal.

Fig. 4.8 Operation of Timer0

Fig. 4.9 Start / Stop operation of Timer0

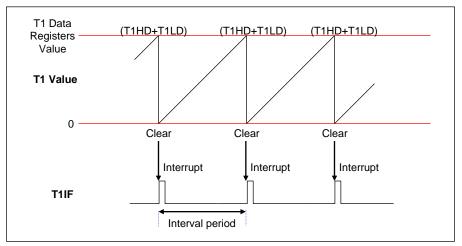

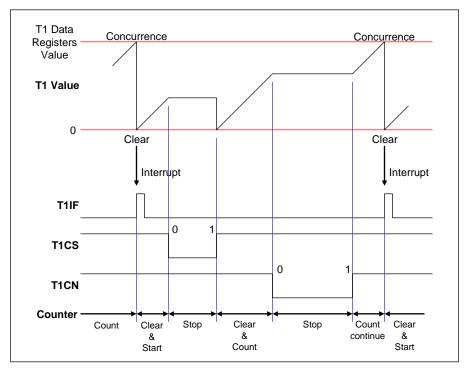

4.3.4. Timer1

TIMER1 operates as a up-counter. Timer1 has 8bit data register (T1HD+T1LD). When the value of the up-counter reaches the content of Timer Data Register, the up-counter is cleared to "00h", and interrupt (T1IF) is occurred at the next clock. Internal clock (TCK) and the output of Carrier Generator (TCARRY) is used as counter clock.

The counter execution is controlled by T1CS, T1CN, of T1MR. T1CN is used to stop and start Timer1 without clearing the counter and T1CS does to clear and start the counter. During counting-up, value of counter can be read. Timer execution is stopped by the reset signal.

Fig. 4.10 Operation of Timer1

Fig. 4.11 Start / Stop operation of Timer1

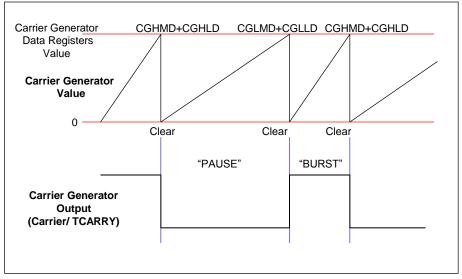

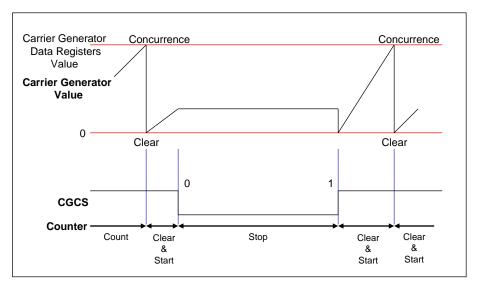

4.3.5. Carrier Generator

Carrier Generator operates as a up-counter. Carrier Generator has two 6bit-data register(CGHMD+CGHLD, CGLMD+CGLLD). The execution of Carrier generator is controlled by CGF0,CGF1,CGON,CGCS of Carrier Generator Mode Register (CGMR).

When CGCS is set to ``1``, count value of Carrier Generator is cleared and starts counting-up. Carrier Generator first counts CGLMD+CGLLD and next CGHMD+CGHLD.

CGLMD+CGLLD are for the pulse of the carrier (BURST) and CGLMD+CGLLD are for the low of the carrier (PAUSE).

Fig. 4.12 Operation of Carrier Generator

Fig. 4.13 Start/Stop of Carrier Generator

# 5. INTERRUPT

The ADAM41P272X contains 3 interrupt sources; 1 externals and 2 internals. Nested interrupt services with priority control is also possible.

- ▶ 3 interrupt source (1Ext, 2Timer)

- 3 interrupt vector

- ▶ 3 level nested interrupt control is possible.

- Read of interrupt request flag are possible.

- ▶ In interrupt accept, request flag is automatically cleared.

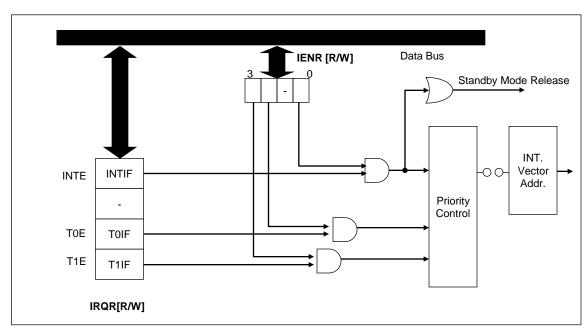

Interrupt Enable Register (IENR), Interrupt Request Register (IRQR) and priority circuit. Interrupt function block diagram is shown in Fig. 5.1.

Fig. 5.1 Interrupt Source

## 5.1. Interrupt Source

Each interrupt vector is independent and has its own priority.

|                       | Mask         | Priority | Interrupt Source          | INT Vector Addr. |

|-----------------------|--------------|----------|---------------------------|------------------|

| Hardware<br>Interrupt | Non-maskable | -        | Reset                     | 0000H            |

|                       | maskable     | 1        | INTE (External Interrupt) | 0002H            |

|                       |              | 2        | T0E (Timer0)              | 0006H            |

|                       |              | 3        | T1E (Timer1)              | 0008H            |

Table 5.1 Interrupt Source

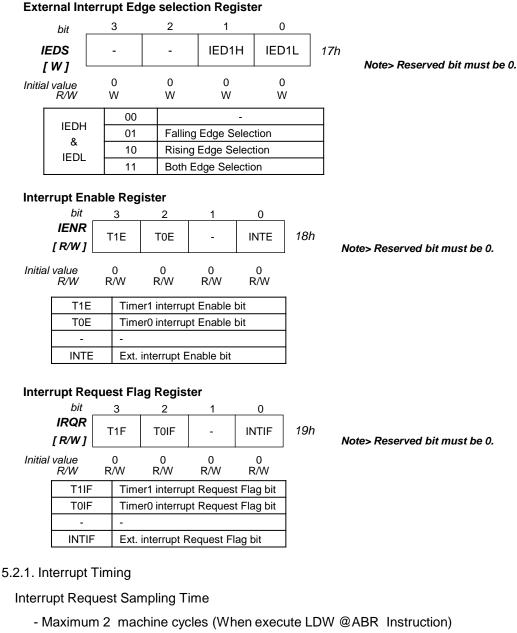

### 5.2. Interrupt Control Register

I flag of SFR is a interrupt mask enable flag. When I flag = "0", all interrupts become disable. When I flag = "1", interrupts can be selectively enabled and disabled by contents of corresponding Interrupt Enable Register(IENR).

When interrupt is occurred, interrupt request flag is set, and Interrupt request is detected at the edge of interrupt signal. The accepted interrupt request flag is automatically cleared during interrupt cycle process. The interrupt request flag maintains "1" until the interrupt is accepted or is cleared in program. In reset state, interrupt request flag register (IRQR) is cleared to "0". It is possible to read the state of interrupt register and to manipulate the contents of register.

- Minimum 0 machine cycle

Interrupt preprocess step is 1 machine cycle.

5.2.2. The valid timing after executing Interrupt control instructions

I flag is valid just after executing of EI/DI on the contrary.

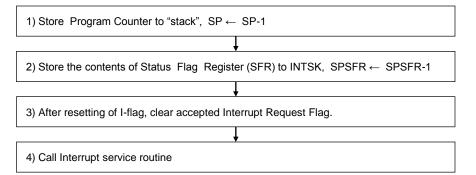

### 5.3. Interrupt Processing Sequence

When an interrupt is accepted, the on-going process is stopped and the interrupt service routine is executed. After the interrupt service routine is completed it is necessary to restore everything to the state before the interrupt occurred.

As soon as an interrupt is accepted, the content of the program counter is saved in the stack register and the contents of status flag register (SFR) is saved into the interrupt stack register (INTSK) which is 3 level stack area.

At the same time, the content of the vector address corresponding to the accepted interrupt, which is in the interrupt vector table, enters into the program counter and interrupt service is executed. In order to execute the interrupt service routine, it is necessary to write the jump addresses in the vector table (0002 h ~ 0008 h) corresponding to each interrupt.

#### Interrupt Processing Step

| System CK1            System CK2             |    | ſ |        |           |

|----------------------------------------------|----|---|--------|-----------|

| System CK3                                   |    |   |        | _         |

| PC PC-1                                      | PC |   | NEW PC | $\rangle$ |

| Interrupt                                    |    |   |        | _         |

| Interrup                                     |    |   |        |           |

| ເ<br>Interfrû <del>p</del> pt<br>Vector Addr |    |   |        | _         |

| Interrup                                     |    |   |        |           |

| Control                                      |    |   |        | _         |

| Stack<br>Pointer                             | SP |   | SP-1   | $\rangle$ |

|                                              |    |   |        |           |

#### 5.4. Multiple Interrupt

If there is an interrupt, Interrupt Mask Enable Flag is automatically cleared before entering the Interrupt Service Routine. After then, no interrupt is accepted. If El instruction is executed, interrupt mask enable bit becomes ``1``, and each enable bit can accept interrupt request. When two or more interrupts are generated simultaneously, the highest priority interrupt is accepted.

## 6. STOP FUNCTION

### 6.1. Stop Mode

STOP mode can be entered by STOP instruction during program.

In STOP mode, oscillator is stopped to make all clocks stop, which leads to less power consumption. All registers and RAM data are preserved.

"NOP" instruction should be follows STOP instruction for pre-charge time of Data Bus line.

|            | Internal circuit        | STOP mode                         |  |  |

|------------|-------------------------|-----------------------------------|--|--|

| Oscillator |                         | Stop                              |  |  |

| Internal   | CPU clock               | Stop                              |  |  |

| Registe    | r                       | Retained                          |  |  |

| RAM        |                         | Retained                          |  |  |

|            | R1,PB,PC,PD,PE<br>ports | Retained                          |  |  |

| Ports      | PA port                 | Low                               |  |  |

|            | POUT part               | Hi-Z (for ADAM41P2727/23/21)      |  |  |

|            | ROUT port               | Low (for ADAM41P2728/24/20)       |  |  |

| Timer      | -                       | Stop                              |  |  |

| Voltage    | Detection Indicator     | Stop                              |  |  |

| Watch      | log Timer               | Reset and restart at stop release |  |  |

| Address    | s Bus, Data Bus         | Retained                          |  |  |

ex) STOP : STOP instruction execution NOP : NOP instruction

Table 6.1 Operation State in Stop Mode

### 6.2. Stop Mode Release

Release of STOP mode is executed by Power on reset, inputting Low to Key input Port (one of R0, R1, PB) which is selected by R0ST, R1ST and PBST register for stop release, external interrupt and Low Voltage Detection (LVD) mode release.

When there is a release signal of STOP mode, the instruction execution starts after oscillation stabilization time( $2^{14} \times 4/f_{OSC} = 16.384$ ms at  $f_{OSC} = 4.0$ MHz)

| Release Factor                 | Release Method                                                                  |

|--------------------------------|---------------------------------------------------------------------------------|

| Power on reset                 | By Power on reset, Stop mode is release and system is initialized               |

| R0, R1, PB Port<br>(key input) | Stop mode is released by low input of pin selected by R0ST, R1ST, PBST register |

| External interrupt             | Stop mode is released by external interrupt input                               |

| Release from<br>LVD detection  | Stop mode is released by LVD detection.                                         |

#### Table 6.2 Stop Mode Release

# 7. RESET FUNCTION

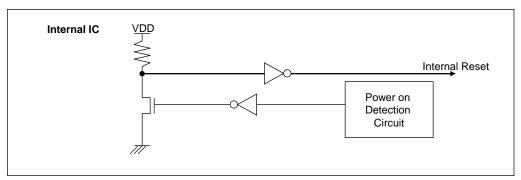

### 7.1. Power on RESET

Power On Reset circuit automatically detects the rise of power voltage (the rising time should be within 50ms). Until the power voltage reaches a certain voltage level, internal reset signal is maintained at "L" Level until internal oscillator is stable.

After power applies and starting of oscillation, this reset state is maintained for about oscillation stabilization time of  $2^{16} \times 4$ /fosc (about 65.536ms : at 4MHz).

Fig. 7.1 Block Diagram of Power On Reset Circuit

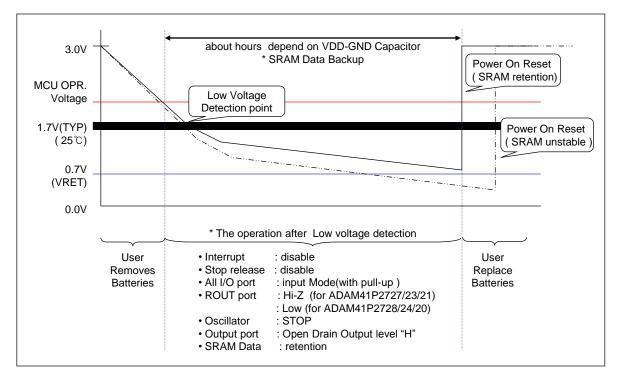

# 8. LVD (Low Voltage Detection) Mode

### 8.1. Low Voltage Detection Condition

An on-board voltage comparator checks that  $V_{DD}$  is at the required level to ensure correct operation of the device. If  $V_{DD}$  is below a certain level, Low voltage detector forces the device into low voltage detection mode.

### 8.2. Low Voltage Detection Mode

There is no power consumption except stop current, stop mode release function is disabled. I/O port is configured as input mode(with pull-up resistor) and Data memory is retained until Voltage through external capacitor is worn out.

In this mode, output ports( PA, PC, PD, PE) are configured open drain "H" output (PC, PD Ports have Push-pull "H" output by Option) and I/O ports( R1, PB) are fixed input with pull-up enabled (Pull-up disable is option in LVD mode).

### 8.3. Release of Low Voltage Detection Mode

Reset signal result from new battery (normally 3V) wakes the low voltage detection mode and come into normal reset state. It depends on user whether to execute RAM clear routine or not.

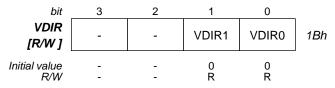

#### 8.4. Voltage Detection Indicator Register

Voltage indication can be checked by reading of the Voltage Detection Indicator Data Register (VDIR). It is useful to display the consumption of Batteries.

If VDD power level is low and higher than low voltage detection (LVD) level (refer to Fig 9.1), the bit of VDIR register could be set according to the VDD level sequentially.

The VDD detection levels for indication are two, that is, VDIR0, VDIR1 of VDIR register. The detection voltage level are VDIR1 (Typ. 2.5V) and VDIR0(Typ. 2.1V).

Voltage Detection Indicator is always operating but it is stopped in the STOP Mode. In the in-circuit emulator, Voltage Detection Indicator function is not implemented and user can not experiment with it. Therefore after final development of user program, this function may be experimented or evaluated.

8.4.1. Voltage Detection Indicator Data Register (VDIR)

Voltage Detection Indicator Data Register (VDIR) is 2-bit register to store data of low voltage level. VDIR is read only register and initialized as "0h" in reset state.

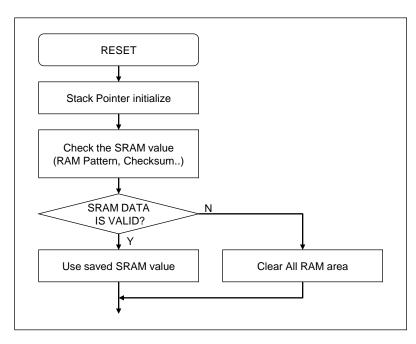

## 9. SRAM DATA BACK-UP

### 9.1. SRAM DATA BACK-UP after Low Voltage Detection

Fig. 9.1 Low Voltage Detection and Protection

#### 9.2. S/W flow chart example after Reset using SRAM DATA Back-up

Fig. 9.2 S/W Flow Chart Example for SRAM Back-up

# **10. MTP PROGRAMMING**

## 10.1. PIN Assignment

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$ | EPROM Mode ⇔ | User Mode                                                                                                              | User Mo                 | User Mode $\Leftrightarrow$ <b>EPROM Mode</b>                                                                                                                                                                                                        |  |                              |  |

|------------------------------------------------------|--------------|------------------------------------------------------------------------------------------------------------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|------------------------------|--|

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$ |              | PE2 2<br>PE3 3<br>PA0 4<br>PA1 5<br>PA2 6<br>PA3 7<br>PB0/INT 8<br>PB1 9<br>PB2/T0 10<br>PB3/T1 11<br>PC0 12<br>PD0 13 | ADAM41P2728<br>(28 SOP) | 27       ROUT         26       R00         25       R01         24       R02         23       R03         22       R10         21       R11         20       R12         19       R13         18       PC2         17       PC1         16       PD3 |  | -<br>-<br>-<br>-<br>VPP<br>- |  |

| $\textbf{EPROM Mode} \Leftrightarrow$                                       | User Mode                                                                                                             | User Mode ⇔ <b>E</b> F                 | User Mode $\Leftrightarrow$ <b>EPROM Mode</b>                                                                         |                                                           |  |

|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|--|

| GND<br>SCK<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>- | GND 1<br>PE2 2<br>PE3 3<br>PA0 4<br>PA1 5<br>PA2 6<br>PA3 7<br>PB0/INT 8<br>PB1 9<br>PB2/T0 10<br>PB3/T1 11<br>PC0 12 | ADAM41P2723<br>ADAM41P2724<br>(24 SOP) | 24 VDD<br>23 ROUT<br>22 RO0<br>21 R01<br>20 R02<br>19 R03<br>18 R10<br>17 R11<br>16 R12<br>15 R13<br>14 PC2<br>13 PC1 | VDD<br>-<br>-<br>-<br>VPP<br>-<br>-<br>SDA<br>-<br>-<br>- |  |

| EPROM Mode ⇔                                                      | User Mode                                                                                      | User Mode $\Leftrightarrow$ <b>EPROM Mode</b> |                                                                                                                             |                                                                          |  |  |

|-------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|--|--|

| GND<br>SCK<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>- | GND 1<br>PE2 2<br>PA0 3<br>PA1 4<br>PA2 5<br>PA3 6<br>PB0/INT 7<br>PB1 8<br>PB2/T0 9<br>PC0 10 | ADAM41P2721<br>ADAM41P2720<br>(20 SOP)        | 20 □ VDD ←<br>19 □ ROUT<br>18 □ R00<br>17 □ R01<br>16 □ R02<br>15 □ R03 ←<br>14 □ R10<br>13 □ R11<br>12 □ R12 ←<br>11 □ R13 | VDD<br>-<br>-<br>-<br>-<br>VPP<br>-<br>-<br>-<br>SDA<br>-<br>-<br>-<br>- |  |  |

## 10.2. PIN Function

| SYMBOL | User Mode | EPROM Mode                                     |

|--------|-----------|------------------------------------------------|

| VDD    | Power     | VDD Power (typ. 5V)                            |

| GND    | Ground    | Ground (0V)                                    |

| VPP    | R03       | Program/Verify Power (typ. 11.5V)              |

| SCK    | OSC1      | Serial Clock Input                             |

| SDA    | R12       | Serial Data Input / Output (Open-Drain Output) |

### **10.3. Configuration Option Description**

10.3.1. Port Status Option at LVD Mode

- 15 Bit for Option bit are available.

- R1, PB Ports have Pull-up Resistor or not at LVD Mode

- PC, PD Ports are Push-Pull "high" output or High-Z(High- impedance output) at LVD Mode.

#### • Configuration Option Bit mapping List [Address : 8400h]

| bit                           | 15 | 14   | 13   | 12   | 11   | 10   | 9    | 8    | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |       |

|-------------------------------|----|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|-------|

|                               | -  | PD3L | PD2L | PD1L | PD0L | PC2L | PC1L | PC0L | PB3L | PB2L | PB1L | PB0L | R13L | R12L | R11L | R10L | 8400h |

| Initial <sup>L</sup><br>value | 1  | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |       |

| Bit Name | Option<br>Description                                 | Initial<br>Value              | Code<br>Write Value | Option Result                            |

|----------|-------------------------------------------------------|-------------------------------|---------------------|------------------------------------------|

| _        | -                                                     | 1<br>(No Writing              | -                   | -                                        |

|          |                                                       | =default)                     | -                   | -                                        |

| PD3L     | PD3 is Push-Pull<br>"High" or "High-Z"                | 1<br>(No Writing              | 0                   | PD3 Port is Push-Pull "High" at LVD Mode |

| I DOL    | at LVD MÕDE                                           | =default)                     | 1                   | PD3 Port is "High-Z" at LVD Mode         |

| וכחם     | PD2 is Push-Pull<br>"High" or "High-Z"                |                               | 0                   | PD2 Port is Push-Pull "High" at LVD Mode |

| I DZL    | at LVD MODE                                           | (No Writing<br>=default)      | 1                   | PD2 Port is "High-Z" at LVD Mode         |

| PD1L     | PD1 is Push-Pull<br>"High" or "High-Z"                | 1<br>(No Writing              | 0                   | PD1 Port is Push-Pull "High" at LVD Mode |

| IDIL     | ať LVD MŎDE                                           | =default)                     | 1                   | PD1 Port is "High-Z" at LVD Mode         |

| PD0L     | PD0 is Push-Pull<br>"Hiah" or "Hiah-Z"                | 1<br>(No Writing              | 0                   | PD0 Port is Push-Pull "High" at LVD Mode |

| FDUL     | at LVD MODE                                           | =default)                     | 1                   | PD0 Port is "High-Z" at LVD Mode         |

| PC2L     | PC2 is Push-Pull<br>"High" or "High-Z"                | 1<br>(No Writing              | 0                   | PC2 Port is Push-Pull "High" at LVD Mode |

| FUZL     | at LVD MODE                                           | =default)                     | 1                   | PC2 Port is "High-Z" at LVD Mode         |

| PC1L     | PC1 is Push-Pull<br>"High" or "High-Z"                | 1<br>(No Writing              | 0                   | PC1 Port is Push-Pull "High" at LVD Mode |

| PUIL     | at LVD MODE                                           | =default)                     | 1                   | PC1 Port is "High-Z" at LVD Mode         |

| DCOL     | PC0 is Push-Pull<br>"High" or "High-Z"<br>at LVD MODE | 1<br>(No Writing<br>=default) | 0                   | PC0 Port is Push-Pull "High" at LVD Mode |

| PC0L     |                                                       |                               | 1                   | PC0 Port is "High-Z" at LVD Mode         |

| DDOI     | PB3 has Pull-up                                       | 1                             | 0                   | PB3 has no Pull-up resistor at LVD Mode  |

| PB3L     | Resistor or not<br>at LVD MODE                        | (No Writing<br>=default)      | 1                   | PB3 has Pull-up resistor at LVD Mode     |

|          | PB2 has Pull-up<br>Resistor or not                    | 1<br>(No Writing              | 0                   | PB2 has no Pull-up resistor at LVD Mode  |

| PB2L     | at LVD MODE                                           | =default)                     | 1                   | PB2 has Pull-up resistor at LVD Mode     |

|          | PB1 has Pull-up<br>Resistor or not                    | 1<br>(No Writing              | 0                   | PB1 has no Pull-up resistor at LVD Mode  |

| PB1L     | at LVD MODE                                           | =default)                     | 1                   | PB1 has Pull-up resistor at LVD Mode     |