#### SUN MICROELECTRONICS

July 1997

# UltraSPARC™-Ili

DATA SHEET

Highly Integrated 64-Bit RISC Processor, PCI Interface

### **FUNCTIONAL DESCRIPTION**

UltraSPARC-IIi (SME1040) is a highly-integrated 64-bit SPARC V9 superscalar processor. An optional APB™ (Advanced PCI Bridge -- SME2411) is available to increase connectivity and support demand for PCI I/O bandwidth. The UltraSPARC-IIi interfaces have been optimized to the "sweet spot" of typical uniprocessor system requirements. This means a balanced price-performance solution delivering the power and features that a majority of high-end applications need, optimizing power utilization and supporting manufacturability and ease-of-use.

UltraSPARC-IIi and the Advanced PCI Bridge allow designers to add UltraSPARC price-performance levels to a broad range of embedded and desktop designs. This CPU-Bridge combination not only optimizes embedded designs that require maximum processing power — such as telecommunications devices, set-top boxes, high-end printers and photocopiers — but the UltraSPARC-IIi also drives desktop applications, supporting connection to a wide array of PCI-compatible devices up to 66 MHz (directly) and 33 MHz (across the bridge).

#### Features

- SPARC V9 Architecture Compliant

- · Binary Compatible with all SPARC Application Code

- VIS Instruction Set (Extended V9 Instructions)

- · 4-way SuperScalar Design with 9 Execution Units

- 4 Integer Execution Units

- 3 Floating-Point Execution Units

- 2 Graphics Execution Units

- · Directly Addresses Little- or Big-Endian Data

- 64-Bit Address Pointers

- 16-Kilobyte Non-blocking Data Cache

- · 16-Kilobyte Instruction Cache

- In-Cache 2-bit Branch Prediction

- Single Cycle Branch Following

- Integrated Second Level (E-Cache) Controller

- Supports 0.25- to 2- Megabyte Cache Sizes

- Integrated Control of 400 Megabyte/sec EDO Dram Memory Subsystem

#### Benefits

- · 64-Byte Block Load and Block Store Instructions

- · Supports Software Data Prefetch into E-Cache

- · Supports up to 3 Outstanding E-Cache Misses

- Supports UPA64S Interface

- 800 Megabyte/Sec

- 64-Bit Slave Interface for Graphics or Similar Subsystems

- Integrated Rev 2.1 PCI

- Higher Sustained PIO and DMA PCI I/O Bandwidth than Competing Solutions

- Read Prefetch and Write Gathering and Posting

- PCI DMA is Cache Coherent

- Dedicated TLB Provides Mapping and Protection

- JTAG Boundary Scan

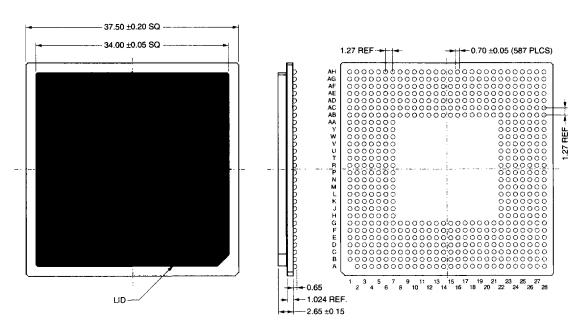

- Technology/Packaging

- 0.35 um 5-Layer Metal CMOS Process

- 2.6 V & 3.3 V (IO Only) Power Supplies

- 266 Mhz and 300 Mhz processor clock hardware options

The UltraSPARC-IIi (with a 0.5 Megabyte cache) achieves estimated SPECint95 and SPECfp95 benchmarks of 10 and 12, respectively. At the same time, it provides industry-leading bandwidth and latency. The UltraS-PARC-IIi has integrated a memory controller and the I/O interfaces onto the microchip.

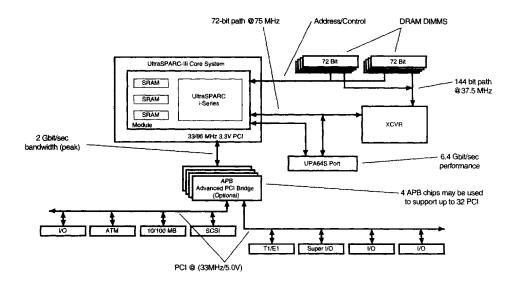

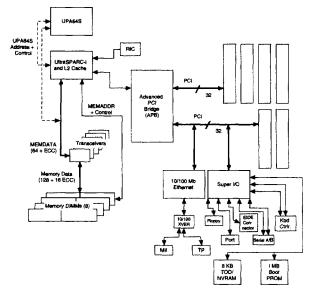

Figure 1 shows a high-level illustration of an UltraSPARC-IIi-based system. This system minimizes the memory-to-CPU bottleneck by using the following interface speeds:

| Hardware Interface            | 266 MHz CPU  | 300 MHz CPU  |

|-------------------------------|--------------|--------------|

| CPU                           | 266 MHz      | 300 MHz      |

| SRAM external cache (E-Cache) | 133 MHz      | 150 MHz      |

| DRAM data throughput          | 67 MHz       | 75 MHz       |

| PCI                           | up to 66 MHz | up to 66 MHz |

As shown in "Product System and Subsystems" beginning on page 302, this solution supports a wide array of applications.

Each functional area on the UltraSPARC-IIi maintains decentralized control, allowing many activities to overlap. Sustained performance of up to 4 instructions per cycle is supported (even in the presence of conditional branches and cache misses) by a decoupled Prefetch and Dispatch Unit. Load buffers on the input side of the Execution Unit, together with store buffers on the output side, decouple pipeline execution from data cache misses. Instructions predicted to be executed are issued in program order to multiple functional units. Such instructions are executed in parallel and may be completed out of order. The separate Memory Control and PCI I/O interface units also decouple their related key activities from the instruction pipeline.

UltraSPARC-II*i* supports the VIS extended instruction set for the V9 architecture. Use of VIS in conjunction with the four-way superscalar pipeline on the i-series processors enhances the performance for a wide range of networking applications, including TCP/IP. Use of VIS instructions also enables speed-up of I/O operations. In addition, VIS instructions support:

- H.261 real-time video compression/decompression

- one stream of MPEG-2 decompression at full broadcast quality without any additional hardware support

The UltraSPARC-IIi processor supports Sun's popular Solaris operating system and is binary-compatible with the broad array of existing applications. In addition, Sun is planning robust third-party real-time operating system (RTOS) and development tool support for embedded applications.

The UltraSPARC-IIi will be available as an individual component, on integrated cache-based modules and on industry-standard format board solutions. Please contact your Sun representative for current information on these products.

# System Illustration

Figure 1. UltraSPARC-IIi System Implementation Example

For more detailed information, see "Product System and Subsystems" beginning on page 302.

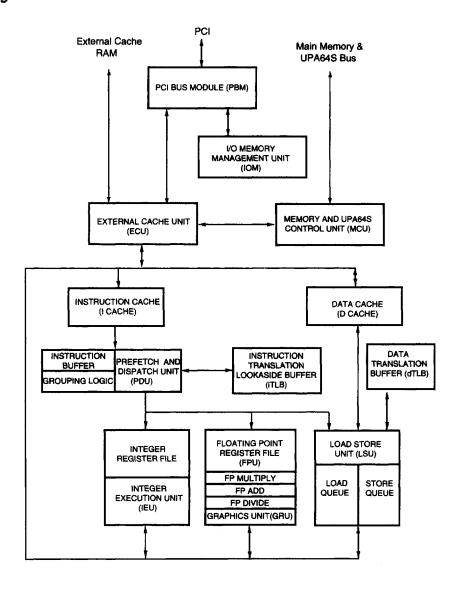

# **Block Diagram**

Figure 2. Functional Block Diagram of UltraSPARC-III

### Component Overview

In a single-chip implementation, UltraSPARC-IIi integrates the following components (see Figure 2):

- Independently clocked (132 MHz internal, 66 or 33 MHz external) PCI interfaces, fully decoupled from the main CPU

- PCI bus module (PBM)

- PCI I/O memory management unit (IOM) with 16 entries for incoming I/O to physical mapping/protection

- External (E-Cache) cache control unit (ECU)

- Memory controller unit (MCU), operates both the 144-bit-wide DRAM subsystem and the UPA64S interface

- 16-Kilobyte instruction cache (I-Cache)

- 16-Kilobyte data cache (D-Cache)

- Prefetch, branch prediction and dispatch unit (PDU) containing grouping logic and an instruction buffer

- A 64-entry instruction translation lookaside buffer (iTLB) and a 64-entry data translation lookaside buffer (dTLB)

- Integer execution unit (IEU) with two arithmetic logic units (ALUs)

- Floating-point unit (FPU) with independent add, multiply and divide/square root sub-units

- Graphics unit (GRU) composed of two independent execution pipelines

- Load buffer and store buffer unit (LSU), decoupling data accesses from the pipeline

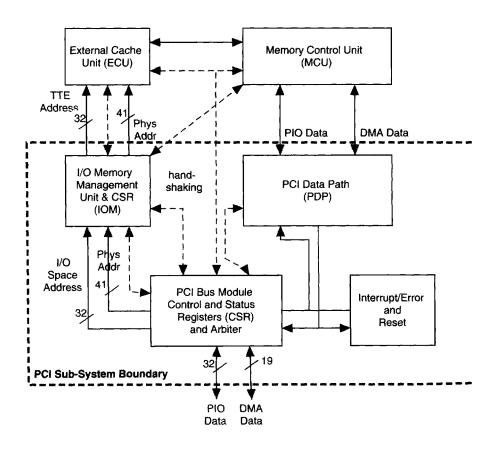

# PCI Bus Module (PBM)

The PBM interfaces UltraSPARC-IIi directly with a 32-bit PCI bus, compliant with the PCI specification, revision 2.1. The PCI bus runs at speeds up to 66MHz, typically 33 and 66 MHz. The PBM is optimized for 16-, 32-and 64-byte transfers, and can support up to four PCI bus masters. The module also queues pending interrupts received from the interrupt concentrator (or RIC-SME2210) chip. The entire PCI address space is noncacheable for CPU references but coherent DMA is supported. (This means that all writes to memory from PCI, and reads from memory, are cache coherent.) Interrupt handling is synchronized to the completion of all prior DMA writes.

# IO Memory Management Unit (IOM)

The IOM performs address translations from 32-bit DVMA to 34-bit physical addresses when UltraSPARC-IIi is a PCI target (when DVMA read/write access is required). The IOM uses a fully-associative 16-entry TLB (translation lookaside buffer). In the case of a TLB miss, the IOM performs a single-level hardware tablewalk into the large translation storage buffer (TSB) in memory.

# External Cache Control Unit (ECU)

The main role of the ECU is to handle I-Cache and D-Cache misses efficiently. The ECU can handle one access every other cycle to the external cache. Loads that miss in the D-Cache cause 16-byte D-Cache fills using two consecutive 8-byte accesses to the E-Cache. Stores are writethrough to the E-Cache and are fully pipelined. Instruction prefetches that miss the I-Cache cause 32-byte I-Cache fills using four consecutive 8-byte accesses to the E-Cache. The E-Cache is parity-protected.

In addition, the ECU supports DMA accesses which hit in the external cache and maintains data coherency between the external cache and the main memory. The size of the external cache can be 256 KB, 512 KB, 1 MB, or 2 MB (where the line size is always 64 bytes). Cache lines have only 3 states: modified, exclusive or invalid.

The combination of the load buffer and the ECU is fully pipelined. For programs with large data sets, instructions are scheduled with load latencies based on the E-Cache latency, so the E-Cache acts as a large primary cache. Floating-point applications use this feature to effectively "hide" D-Cache misses. Coherency is maintained between all caches and external PCI DMA references.

The ECU overlaps processing during load and store misses. Stores that hit the E-Cache can proceed while a load miss is being processed. The ECU is also capable of processing reads and writes without a costly turnaround penalty on the bidirectional E-Cache data bus.

Block loads and block stores (these load or store a 64-byte line of data from memory or E-Cache to the floating-point register file) provide high transfer bandwidth. By not installing into the E-Cache on miss, they avoid polluting the cache with data that is only touched once.

The ECU also provides support for multiple outstanding data transfer requests to the MCU and PBM.

# Memory Controller Unit (MCU)

All transactions to the DRAM and UPA64S subsystems are handled by the MCU. The external pins controlled by the MCU operate at divisions of the processor clock:

- UPA64S runs at 1/3 the processor clock

- data transfers to the DRAM transceivers typically occur at 1/4 of the processor clock rate (programmable)

External data transceivers allow the DRAM data to be twice as wide as data from the processor's MEMDATA pins, so the EDO CAS cycle is only 26.5 ns at 300 MHz. The MCU supports a composite DRAM specification which is a superset of 60 ns EDO DRAM specifications from all major vendors.

Use of faster DRAMs allow higher-than-quoted performance, because the various components of memory delay are programmable.

# Instruction Cache (I-Cache)

The I-Cache is a 16 Kilobyte two-way set-associative cache with 32-byte blocks. The cache is physically indexed and physically tagged. The set is predicted as part of the "next field" so that only the index bits of an address are necessary to address the cache. (This means only 13 bits, which matches the minimum page size.) The instruction cache returns up to 4 instructions from a line that is 8 instructions wide.

# Data Cache (D-Cache)

The data cache is a write-through non-allocating 16 Kilobyte direct-mapped cache with two 16-byte subblocks per line. It is virtually indexed and physically tagged. The tag array is dual-ported so that tag updates due to line fills do not collide with tag reads for incoming loads. Snoops to the D-Cache use the second tag port so that an incoming load can proceed without being held up by a snoop.

### Prefetch and Dispatch Unit (PDU)

The PDU fetches instructions before they are needed in the pipeline, so that the execution units do not starve for instructions. Instructions can be prefetched from all levels of the memory hierarchy, including the instruction cache, the external cache, and the main memory. To prefetch across conditional branches, a dynamic branch prediction scheme is implemented in hardware, based on a two-bit history of the branch. A "next field" associated with every four instructions in the I-Cache points to the next I-Cache line to be fetched. This makes it possible to follow taken branches and provides the same instruction bandwidth achieved during sequential code. Up to 12 prefetched instructions are stored in the instruction buffer sent to the rest of the pipeline.

## Translation Lookaside Buffers (iTLB and dTLB)

The Translation Lookaside Buffers provide mapping between 44-bit virtual addresses and 34-bit physical addresses. A 64-entry iTLB is used for instructions and a 64-entry dTLB for data, and both are fully associative. UltraSPARC-IIi provides hardware support for a software-based TLB miss strategy. For low-latency miss handling, a separate set of global registers is available whenever such a trap is encountered. Page sizes of 8 KB, 64 KB, and 512 KB and 4 MB are supported.

### Integer Execution Unit (IEU)

Two Arithmetic Logic Units (ALUs) form the main computational part of the IEU. An early-finish-detect multi-cycle integer multiplier and a multi-cycle integer divider are also part of the IEU. Eight register windows and four sets of global registers are provided (normal, alternate, MMU and interrupt globals). The trap registers (UltraSPARC-IIi supports five levels of traps) are part of the IEU.

# Floating-Point Unit (FPU)

The separation of the execution units in the FPU allows UltraSPARC-II*i* to issue and execute two floating-point instructions per cycle. Source data and results data are stored in the 32-entry register file, where each entry can contain a 32- or 64-bit value. Most instructions are fully pipelined (throughput of one per cycle), have a latency of three, and are not affected by the precision of the operands (same latency for single or double precision).

The divide and square-root instructions are not pipelined. These take 12 cycles to execute in single precision (22 cycles in double precision) but they do not stall the processor. Instructions, following the divide/square root can be issued, executed, and retired to the register file before the divide/square root finishes. A precise exception model is maintained by synchronizing the floating-point pipe with the integer pipe and by predicting traps for long-latency operations.

# Graphics Unit (GRU)

UltraSPARC-IIi introduces a comprehensive set of graphics instructions (VIS) that provide industry-leading support for two-dimensional and three-dimensional image and video processing, image compression, audio processing, and similar functions. Sixteen-bit and 32-bit partitioned add, boolean, and compare are provided. Eight-bit and 16-bit partitioned multiplies are supported. Single cycle pixel distance, data alignment, packing and merge operations are all supported in the GRU.

### Load/Store Unit (LSU)

The LSU is responsible for generating the virtual address of all loads and stores (including atomics and ASI loads), for accessing the data cache, for decoupling load misses from the pipeline through the load buffer, and for decoupling the stores through a store buffer. One load or one store can be issued per cycle. The store buffer can compress (or gather) multiple stores to the same 8 bytes into a single E-Cache access. The UPA64S and PCI control units can compress sequential 8-byte stores into burst transactions, to improve noncacheable store bandwidth.

### Phase Locked Loops (PLL)

To minimize the clock skew at the system level UltraSPARC-IIi has PLLs for both the processor clock and the PCI clock. The internal PCI clock runs at twice the speed of the PCI interface clock. For details, see "Quick Pin Reference - Internal, SRAM, and UPA Clock Interface" beginning on page 294 and "Quick Pin Reference - PCI Clock Interface" beginning on page 296.

### Signals

All external cache signals are of 2.6 V magnitude and exist only on the processor module. All other signals are 3.3 V LVTTL. The highest signal frequency from the module to the motherboard is 75 MHz. (unless the 100 MHz UPA64S interface is used), which allows economic motherboard design.

### **TECHNICAL CAPABILITIES**

All performance specifications are for a 300 MHz processor, with 512 kB E-Cache.

### SPEC Performance

| SPECint95 | 10 |

|-----------|----|

| SPECfp95  | 12 |

Newer compilers may improve SPECfp95 through use of software prefetch instructions.

One of the features of UltraSPARC-IIi is the superior performance of its integrated I/O, DRAM and UPA64S interfaces:

# Memory Performance

| Maximum E-Cache read bandwidth      | 1.2 GB/s |

|-------------------------------------|----------|

| Maximum E-Cache write bandwidth     | 1.2 GB/s |

| Maximum DRAM random read bandwidth  | 350 MB/s |

| Maximum DRAM random write bandwidth | 350 MB/s |

| Maximum same page read bandwidth    | 400 MB/s |

| Memcopy, from DRAM to DRAM          | 275 MB/s |

| Memcopy, from DRAM to UPA64S        | 550 MB/s |

#### FP Vector

| STREAM Copy (compiled)  | 200 MB/s |

|-------------------------|----------|

| STREAM Scale (compiled) | 210 MB/s |

| STREAM Add (compiled)   | 230 MB/s |

| STREAM Triad (compiled) | 230 MB/s |

Note that DRAM bandwidth is 1/3 to 1/4 greater than these numbers, since there is an initial DRAM read of the data locations that are used for store operations.

### PCI Bandwidth

|                                              |               | and the second of the second o | organizacji do zadli zadlenica i se<br>Tra |

|----------------------------------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| To DRAM from Processor                       | 66mhz, 32-bit | Random 64-byte Reads                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 132 MB/s                                   |

| PCI Bus (DMA)                                |               | Random 64-byte Writes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 151 MB/s                                   |

| To E-Cache from<br>Processor PCI Bus (DMA)   | 66mhz, 32-bit | Random 64-byte Reads                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 163 MB/s                                   |

|                                              |               | Random 64-byte Writes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 186 MB/s                                   |

| From Processor to<br>Processor PCI bus (PIO) | 66mhz, 32-bit | 64-byte writes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 200 MB/s                                   |

All sustained DMA numbers are for a single device. Multiple devices on separate secondary buses can cause higher sustained bandwidths. In no case is the combined bandwidth from two secondary buses less than the peak bandwidth available from one bus. This is because of efficient internal arbitration between multiple events in the bus bridge.

### **UPA64S Bandwidth**

| From Processor, to | 100mhz, 64-bit | Random 64-byte Writes    | 600 MB/s |  |  |  |

|--------------------|----------------|--------------------------|----------|--|--|--|

| UPA64S (PIO)       |                | Compressed 8-byte Writes | 800 MB/s |  |  |  |

# PCI Bandwidth with APB (33MHz Secondary Bus)

|                                               |               | A CONTRACTOR OF THE STATE OF TH |          |

|-----------------------------------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| From Processor, to<br>Secondary PCI Bus (PIO) | 33mhz, 32-bit | 64-byte Writes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 124 MB/s |

| To DRAM from Secondary                        | 33mhz, 32-bit | Random 64-byte Reads                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 78 MB/s  |

| PCI Bus (DMA)                                 |               | Random 64-byte Writes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 124 MB/s |

# SIGNAL DESCRIPTIONS [1] [2]

# Quick Pin Reference - External Cache (E-Cache) Interface

| EDATA[63:0]    | 2.6 V | 1/0 | SRAM_CLK_A/B                      | E-Cache Data Bus; Connects UltraSPARC-II/ to the E-Cache data RAMs; clocked at 1/2 the processor clock rate                                                                                                                                                            |

|----------------|-------|-----|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EDPAR[7:0]     |       | I/O |                                   | E-Cache Data Parity; odd parity is driven or checked for all EDATA transfers; MSB corresponds to the MS byte of EDATA; clocked at 1/2 the processor clock rate                                                                                                         |

| TDATA[15:0]    |       | I/O |                                   | E-Cache Tag Data. Bits 15:14 carry the MEI I state; bits[13:0] carry the physical address bits [31:18]; allows a minimum cache size of 256k bytes; all TDATA bits are used, even when the E-Cache is more than 256 kilobytes; clocked at 1/2 the processor clock rate. |

| TPAR[1:0]      |       | 1/0 |                                   | E-Cache Tag Parity; odd parity for TDATA[15:0]; TPAR[1] covers TDATA[15:8]; TPAR[0] covers TDATA[7:0]; clocked at 1/2 the processor clock rate                                                                                                                         |

| BYTEWE_L[7:0]  |       | 0   |                                   | E-Cache Byte Write Enables; active low bit [0] controls EDATA[63:56]; bit 7 controls EDATA[7:0]; clocked at 1/2 the processor clock rate                                                                                                                               |

| ECAD[17:0]     |       | 0   |                                   | E-Cache Data Address; corresponds to physical address [20:3]; allows a maximum 2 MB E-Cache; clocked at 1/2 the processor clock rate                                                                                                                                   |

| ECAT[14:0]     | ,     | 0   |                                   | E-Cache Tag Address; corresponds to physical address [20:6]; allows a maximum 2 MB E-Cache, with 64-byte lines; clocked at 1/2 the processor clock rate                                                                                                                |

| DSYN_WR_L      |       | 0   |                                   | E-Cache Data Write Enable; active low; clocked at 1/2 the processor clock rate                                                                                                                                                                                         |

| DOE_L          |       | 0   |                                   | E-Cache Data Operation Enable; active low; asserted on all SRAM operations; clocked at 1/2 the processor clock rate                                                                                                                                                    |

| TSYN_WR_L      |       | 0   |                                   | E-Cache Tag Write Enable; active low; clocked at 1/2 the processor clock rate                                                                                                                                                                                          |

| TOE_L          |       | 0   |                                   | E-Cache Tag Operation Enable; active low; clocked at 1/2 the processor clock rate                                                                                                                                                                                      |

| ECACHE_22_MODE | 3.3 V | ı   | Not Aligned<br>Static (all modes) | Selects E-Cache 22 (1-tie high) or 222 mode (0-tie low). (2 cycle read pipeline, or 3 cycle read pipeline)                                                                                                                                                             |

<sup>1.</sup> Unused inputs should be connected to the appropriate level.

<sup>2.</sup> Use approximately 10 k $\Omega$  resistors for pullups (unused) and 1 k $\Omega$  for pulldowns. Never tie a pin directly to a to a supply rail.

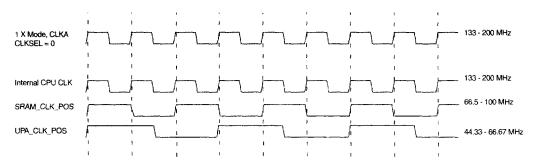

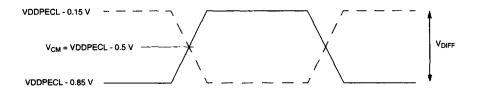

# Quick Pin Reference - Internal, SRAM, and UPA Clock Interface

| CLKA                         | PECL  | 1 | See Figure 3<br>and Figure 4 for<br>logical relation<br>of clocks | Primary positive differential clock source to<br>UltraSPARC-II; normally (in 2X mode) runs at 1/2 the internal<br>clock rate; during test, when the PLL is bypassed, the full internal<br>clock rate can be used                                                                                                                                                              |

|------------------------------|-------|---|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLKB                         |       | ı |                                                                   | Primary negative differential clock source to UltraSPARC-IIi; normally (in 2X mode) runs at 1/2 the internal clock rate; during test, when the PLL is bypassed, the full internal clock rate can be used                                                                                                                                                                      |

| UPA_CLK_POS,<br>UPA_CLK_NEG  |       | l |                                                                   | Signals run at 1/3 frequency of the internal CPU clock; also used to drive the UPA64S; when the UPA64S interface is used these signals indicate to the processor which CLKA edge corresponds to a UPA_CLK_POS edge                                                                                                                                                            |

| SRAM_CLK_POS<br>SRAM_CLK_NEG |       | 1 |                                                                   | Signals run at 1/2 the internal clock rate; also drive the SRAMs; they indicate to the processor which CLKA edges correspond to SRAM_CLK_POS clock edges                                                                                                                                                                                                                      |

| PLLBYPASS                    | 3.3 V |   | Static Signal                                                     | Used during test to bypass PLL and PLL2; clock from differential receiver is directly passed to the clock tree; during PLLBYPASS, SRAM_CLK_POS and SRAM_CLK_NEG must be 1/2 the frequency of CLKA and CLKB; also during PLLBYPASS, UPA_CLK_POS and UPA_CLK_NEG must be 1/3 the frequency of CLKA and CLKB; during PLLBYPASS mode, PCI_REF_CLK must be 2X frequency of PCI_CLK |

| L5CLK                        | 2.6 V | 0 | CLKA and CLKB                                                     | Internal level 5 clock that reflects the CPU clock; used to determine PLL lock or clock tree delay when in PLL bypass mode; may be disabled during normal operation                                                                                                                                                                                                           |

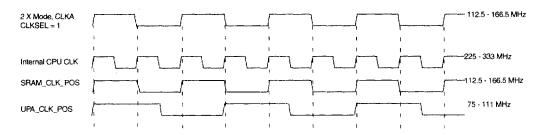

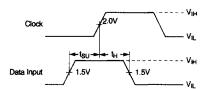

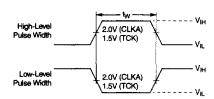

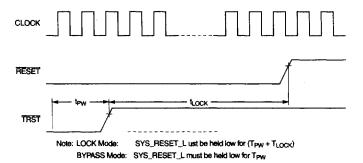

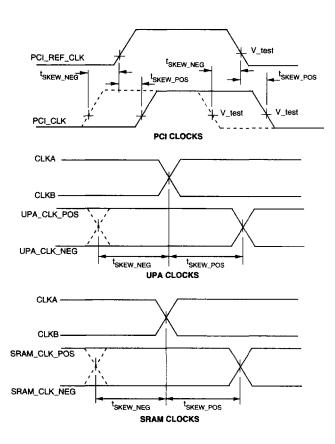

# Clock Interface Timing Detail [1] [2] [3]

Figure 3. CLKA 1X Mode: Relation of CLKA to Internal, SRAM, and UPA Clocks

Figure 4. CLKA 2X Mode: Relation of CLKA to Internal, SRAM, and UPA Clock

<sup>1.</sup> See Figure 28 and the table: Clock Skew on page 326 for skew requirements for CLKA.

<sup>2.</sup> Note that each CLK\_POS has a complementary CLK\_NEG not shown.

<sup>3.</sup> During PLLBYPASS, the Internal, SRAM, and UPA Clock relationships must be the same as in CLKA 1X Mode.

## Quick Pin Reference - PCI Clock Interface

| PCI_REF_CLK | 3.3 V | 1 | See Figure 5                        | PCI reference clock; 40-66 MHz.                                                                                                                                                                                                       |

|-------------|-------|---|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCI_CLK     | 3.3 V | ı | and Figure 6 for logical relations. | PCI clock, 66mhz; can be set to 33 MHz PCI interface if desired.                                                                                                                                                                      |

| P2L5CLK     | 2.6 V | 0 | PCI_REF_CLK                         | Disabled during normal operation; internal level 5 clock that reflects the PCI clock and is used to determine PLL lock or clock tree delay when in PLLBYPASS mode; during PLLBYPASS mode, PCI_REF_CLK must be 2X frequency of PCI_CLK |

| PLLBYPASS   |       |   |                                     | Refer to "Quick Pin Reference - Internal, SRAM, and UPA Clock Interface" on page 294                                                                                                                                                  |

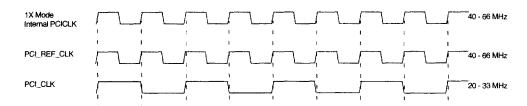

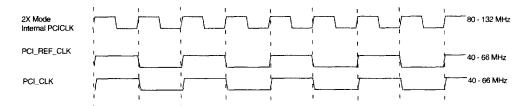

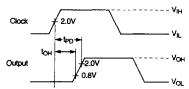

## PCI Clock Timing [1] [2]

Figure 5. Relation Between PCI (1X Mode) Clocks [3]

Figure 6. Relation Between PCI (2X Mode) Clocks [4] [5]

<sup>1.</sup> See Figure 28 and table: Clock Skew on page 326 for skew requirements for PCI\_REF\_CLK.

<sup>2.</sup> During PLLBYPASS the PCI\_CLK and PCI\_REF\_CLK relationships must be the same as for PCI 1X Mode.

<sup>3.</sup> Figure 5 applies to the PCI bus clock between 20-33 MHz, which must be in 1X mode.

<sup>4.</sup> Figure 6 (and 2X mode) applies when the bus is run from 40-66 MHz.

<sup>5.</sup> Refer to the table: Clock Skew on page 326 for permissible skew between PCI\_REF\_CLK and PCI\_CLK. It is recommended that the system designer supplies PCI\_REF\_CLK directly from the PCI\_CLK signal for 2X mode operation – see Figure 6. Skew between PCI\_CLK and PCI\_REF\_CLK must be minimized; the required setup time is: t<sub>SUeff</sub> = (3ns + t<sub>SKEW POS</sub>)

# Quick Pin Reference - JTAG/Debug Interface

| TDI           | 3.3 V | ſ   | Not aligned | IEEE 1149 test data input; pin internally pulled to logic 1 when not driven                                                  |                                                                                                              |

|---------------|-------|-----|-------------|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| TCK           |       | 1   | 1           |                                                                                                                              | IEEE 1149 test clock input; pin must always be held at logic 1 or logic 0 if not connected to a clock source |

| TMS           |       | ł   |             | IEEE 1149 test mode select input; pin internally pulled to logic 1 if not driven                                             |                                                                                                              |

| TRST_L        | 1     | 1   |             | IEEE 1149 test reset input (active low); pin internally pulled to logic 1 if not driven                                      |                                                                                                              |

| RAM_TEST      |       |     |             | When asserted this pin forces the processor into SRAM test mode allowing direct access to the cache SRAMs for memory testing |                                                                                                              |

| ITB_TEST_MODE |       | 1   | 1           | Enables a special SRAM mode for testing the ITB megacell; pull to ground using a 10.7 k $\Omega$ , 1% resistor               |                                                                                                              |

| EXT_EVENT     |       | 1 . |             | Signal used to indicate that the clock should be stopped; debug signal set inactive to logic 0 on production systems         |                                                                                                              |

| TDO           | 2.6 V | 0   | Not aligned | IEEE 1149 test data output; tri-state signal driven only when the TAP controller is in the shift-DR state                    |                                                                                                              |

| РМО           |       | 0   |             | Used for on-chip process monitors; reserved for IC manufacturing only                                                        |                                                                                                              |

| TEMP_SEN[1:0] | N/A   | 0   |             | Defines scale end points of the processor temperature sense element on the module; reserved for IC manufacturing only        |                                                                                                              |

### Quick Pin Reference - Initialization Interface

| P_RESET_L   | 3.3 V | 1 | Not Aligned | For non power-on resets (debug); asynchronous assertion and de-assertion; active low                                       |

|-------------|-------|---|-------------|----------------------------------------------------------------------------------------------------------------------------|

| X_RESET_L   |       | I |             | Driven to signal XIR traps (debug); acts as non-maskable interrupt; asynchronous assertion and de-assertion; active low    |

| SYS_RESET_L |       | ı |             | Driven for power-on resets (POR); asynchronous assertion and de-assertion; active low <sup>(1)</sup>                       |

| RST_L       |       | 0 |             | Resets PCI subsystem; Asynchronous assertion and monotonic deassertion; also used for UPA64S reset                         |

| RMTV_SEL    |       | 1 |             | Red Mode Trap Vector Select; pull up if alternate PC-compatible boot vector is required                                    |

| CLKSEL      |       | ı |             | Pullup to enable the 2x function of the CLKA/B PLL; E-Cache interface still works at 1/2 the internal processor clock rate |

| EPD         | 2.6 V | 0 |             | Asserted when UltraSPARC-II/ is in clock shutdown mode; use P_RESET_L to re-start                                          |

SYS\_RESET\_L must be a clean indication that 3.3 V, 5 V, etc. are stable and within specification. No anomalies may be present, beginning when

the power supplies are turned on and extending until the signals are within specification. When signals are within specification, the power supply

can transition monotonically to 3.3 V.

### Quick Pin Reference - PCI interface

| AD[31:0]   | 3.3 V | 1/0     | PCI_CLK | Address/Data; multiplexed on same PCI pins.                                                                                                                       |

|------------|-------|---------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CBE_L[3:0] | (All) | 1/0     |         | Bus Command and Byte Enables; multiplexed on same PCI pins                                                                                                        |

| PAR        |       | 1/0     |         | Parity; even parity across AD[31:0] and CBE_L[3:0]                                                                                                                |

| DEVSEL_L   |       | STSIII  |         | Device Select. Indicates the driving device has decoded the address of the target of the current access; as input, indicates whether any device has been selected |

| FRAME_L    |       | STS     |         | Cycle Frame; driven by current master to indicate beginning and end of an access                                                                                  |

| REQ_L[3:0] |       | ı       |         | Request; indicates to arbiter that an external device requires use of the bus                                                                                     |

| GNT_L[3:0] | 7     | T/S [2] |         | Grant; indicates to device that bus access has been granted.                                                                                                      |

| IRDY_L     |       | STS     |         | Initiator Ready; indicates the bus master's ability to complete the current data phase                                                                            |

| TRDY_L     |       | STS     |         | Target Ready; indicates the selected device's ability to complete the current data phase                                                                          |

| PERR_L     |       | STS     | 1       | Parity error; reports data parity errors                                                                                                                          |

| SERR_L     |       | O/D     |         | System Error; reports address parity errors, data parity errors on special cycles, or any other catastrophic PCI errors                                           |

| STOP_L     |       | STS     |         | Stop; indicates that the current target is requesting the master to stop the current transaction                                                                  |

<sup>1.</sup> Sustained Tri-State. STS is an active low tri -state signal owned and driven by one and only one agent at a time. The agent that drives an STS pin low must drive it high for at least one clock before letting it float. A new agent cannot start driving an STS signal any sooner than one clock after the previous owner tri-states it. A pullup is required to sustain the inactive state until another agent drives it, and must be provided by the motherboard or module.

<sup>2.</sup> Tri-State Output.

# Quick Pin Reference - Interrupt Interface

| SB_DRAIN      | 3.3 V | 0 | PCI_CLK | Store Buffer Drain. sampled at a 66 MHz PCI_CLK edge; asserted after Interrupts, or by software, to cause outstanding DMA writes to be flushed from buffers                                   |

|---------------|-------|---|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SB_EMPTY[1:0] |       | l |         | Store Buffer Empty; sampled at 66 MHz PCI_CLK edge. asserted when external APB PCI bus bridge indicates that all DMA writes queued before the assertion of SB_DRAIN have left the bus bridge; |

| INT_NUM[5:0]  |       | 1 |         | Interrupt Number; sampled at 66 MHz PCI_CLK edge; encoded interrupt request                                                                                                                   |

# Quick Pin Reference - Memory and Transceiver Interface

| MEM_WE_L          | 3.3 V | 0   | CLKA/B | Memory Write Enable; active low                                                                                                                |

|-------------------|-------|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------------|

| MEM_CAS_L[1:0]    | (All) | 0   |        | Memory Column Address Strobe; active low                                                                                                       |

| MEM_RAST_L{3:0}   |       | 0   | }      | Memory Row Address Strobe Top; active low                                                                                                      |

| MEM_RASB_L[3:0]   |       | 0   | ]      | Memory Row Address Strobe Bottom, active low                                                                                                   |

| MEM_DATA[71:0]    |       | 1/0 | ]      | Memory Data; bits [71:64] are ECC bits                                                                                                         |

| MEM_ADDR[12:0]    |       | 0   |        | Memory Address, row and column (10 and 11 bit column support)                                                                                  |

| XCVR_OEA_L        |       | 0   |        | Transceiver Output Enable A; active low                                                                                                        |

| XCVR_OEB_L        |       | 0   |        | Transceiver Output Enable B; active low                                                                                                        |

| XCVR_SEL_L        |       | 0   |        | Transceiver Select, active low; picks high or low half of read data                                                                            |

| XCVR_WR_CNTL[1:0] |       | 0   |        | Transceiver Write Control; controls lock enables on internal registers                                                                         |

| XCVR_RD_CNTL[1:0] |       | 0   |        | Transceiver Read Control; control clock enables on internal registers                                                                          |

| XCVR_CLK[2:0]     |       | 0   |        | Transceiver Clock; all data and control signals are registered by these clocks; multiple outputs to minimize loading effects of 6 transceivers |

## Quick Pin Reference - UPA64S Interface

|              |       | ·                  |                 |                                                                                                                               |

|--------------|-------|--------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------|

| S_REPLY[2:0] | 3.3 V | 0                  | UPA_CLK_POS/NEG | S Reply; encoded command indicates arrival of write data on MEM_DATA[63:0], or command to drive MEM_DATA[63:0] with read data |

| P_REPLY[1:0] |       | ł                  |                 | P Reply; encoded command that indicates ability consumption of prior write, or ability to provide read data                   |

| SYSADR[28:0] |       | I/O <sup>[1]</sup> |                 | System Address, sends 2 cycle address packet to UPA64S slave, or provides internal state debug information                    |

| ADR_VLD      |       | 0                  |                 | Address Valid; asserted during first cycle of two cycle address packet                                                        |

<sup>1.</sup> Not all of SYSADR[28:0] is bidirectional, since SYSADR[14:0] is I/O but SYSADR[28:15] is output only. SYSADR[14:0] is used as an input during RAM\_TEST.

### PRODUCT SYSTEM AND SUBSYSTEMS

#### An UltraSPARC-III Reference Platform

A reference platform has been developed to illustrate UltraSPARC-IIi operation. This platform is illustrated in the schematic block diagram of *Figure 7* and detailed in the following description:

#### Hardware

This model assumes CPU and SRAM for the E-Cache are provided on the same module, to keep the high-speed E-Cache interface in a controlled electrical environment and away from the motherboard.

This standard module uses five, 64 K x 18 register-latch SRAMs, to provide a 512-kilobyte E-Cache.

The module provides support for two standard, 33 MHz, 32-bit PCI buses, along with a 66 MHz, 32-bit PCI interface to a bus bridge ASIC, for example, the Advanced PCI Bridge (APB), SME2411.

#### Memory

- Four DIMM pairs for up to 256 Megabytes, using 168-pin JEDEC DIMMs, with 16-Megabit DRAM. Up to 1 Gigabyte, using 64-Megabit DRAM

- 144-bit DRAM data bus with 8-bit ECC on each 64 bits of data

#### Graphics

• PCI add-in card, or custom UPA64S solution

#### PCI Buses

- Three PCI buses, all compatible with the existing PCI 2.1 standard:

- Primary: One 66 MHz, 32-bit bus from UltraSPARC-IIi to APB; Note that multiple APBs can be used for multiplying PCI connectivity

- Secondary: Two 33 MHz, 32-bit busses from the APB.

- PCI clocks asynchronous with processor clock

### Block Diagram of the Reference Platform

Figure 7. Overview of UltraSPARC-III Reference Platform

#### **Transceivers**

The Texas Instruments SN74ALVC16268 is a bidirectional registered 12-bit-to-24-bit bus exchanger, with 3-state outputs.

The transceiver transfers data bidirectionally between the 72-bit UltraSPARC-IIi memory data bus, and the 144-bit DIMM memory data bus. The DIMMs cycle data in EDO mode at 37.5 MHz maximum frequency – a period of 26.5 ns.

The transceiver has bus-hold on data inputs, eliminating the need for external pullup resistors. It is available in 56-pin Plastic Shrink Small-Outline (DL) and Thin Shrink Small-Outline (DGG) packages.

The ports connected to the DIMMs include the equivalent of  $26\Omega$  series resistors, to make external series termination resistors unnecessary.

The device provides synchronous data exchange between the two ports. Data is stored in the internal registers on the low-to-high transition of the CLK input, provided that the appropriate CLKEN inputs are low. All control inputs, including the CLK inputs, are driven by UltraSPARC-IIi.

#### RIC Chip

The RIC Chip (SME2210) supports the system resets, system interrupts, system scan, and system clock control functions. It's features include:

- Support for resets from power supply, reset buttons, and scan

- Concentration of all of the interrupts; it sends interrupt numbers to the UltraSPARC-IIi

- Direction of SCAN inputs and outputs through scan chains

#### **UPA64S**

UPA64S is a custom 64-bit slave interface for graphics or similar subsystems. Transfers to and from the UPA64S interface are fully synchronous, since UPA64S receives a PECL clock that is aligned with the processor's clock. The processor transfers data on clock edges that correspond to the UPA64S clock edges. This interface runs at 1/3 of the processor clock rate, that is up to 100 MHz.

#### Memory

The following are the major features of the DRAM modules utilized in UltraSPARC-IIi memory:

- JEDEC and industry standard ECC pinout in a 168-pin, dual-in-line memory module (DIMM)

- High performance CMOS silicon gate process

- Single  $+3.3V \pm 0.3 V$  power supply

- All device pins are 3.3 V compatible

- Low power, 9 mW standby; 1,800 mW active, typical

- Refresh modes: CAS-BEFORE-RAS (CBR)

- All inputs are buffered except RAS

- 2,048-cycle refresh distributed across 32 ms

- Extended Data Out (EDO) access cycles

The UltraSPARC-II*i* memory design is built with JEDEC standard 168-pin DIMMs. The memory bus is 144 bits wide. RAS and CAS signals are provided that support a maximum of eight 8 - 128 megabyte DIMMs. A mode that supports 11-bit column addresses for 16M X 4, 64 megabit DRAMs allows a maximum of four 8 - 256 megabyte DIMMs. The memory bus width requires that the DIMMs be populated in pairs at a time. Consequently the minimum memory configuration contains 16 megabytes and the maximum memory configuration contains 1 gigabyte.

These DIMMs are available from many vendors. A composite specification was made considering typical vendor specifications. When the UltraSPARC-IIi is programmed according to the *Programmer's Reference Manual* for a particular frequency and DIMM loading combination, it generates signals that meet this composite specification, if the electrical and topological motherboard layout requirements are met.

### Memory Model for Reference Platform

Figure 8. UltraSPARC-IIi Memory: Simplified Block Diagram

Figure 8 shows how memory is connected to, and controlled by, the UltraSPARC-IIi. The memory DIMMs are arranged on a 144-bit bus to allow an entire cache line to be fetched in four CAS accesses.

UltraSPARC-IIi implements ECC, with single-bit correction and multi-bit detection of errors, for all memory data transfers.

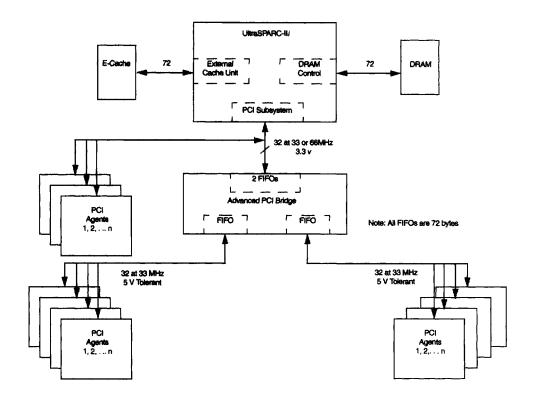

#### PCI Buses for UltraSPARC-IIi and Advanced PCI Bridge

Figure 9 shows an example of the connection of an external PCI subsystem.

The interface from UltraSPARC-IIi with its I/O subsystems is a 32-bit PCI bus, which can run at either 33 or 66 MHz. UltraSPARC-IIi internal PLLs allow slower PCI bus clock rates, down to 20 MHz or 40 MHz for each range respectively. This allows use of more PCI targets than the 2.1 specification permits for full-speed operation. However, the PCI arbiters on UltraSPARC-IIi and APB only support four master requests. The Advanced PCI Bridge (APB) allows external arbiters on the secondary buses.

The UltraSPARC-IIi PCI interface runs at 3.3 V only. To support 5 V PCI cards, the Advanced PCI Bridge (APB) must be used, which also provides expansion from one 66 MHz 32-bit PCI bus, to two 32-bit 33 MHz PCI buses. APB provides up to 64-byte write posting and data prefetching, so that the delivered throughput can be higher than a single 33 MHz bus could provide.

The secondary PCI buses have:

- 3.3 Volt operation and signalling, but are compatible with the PCI 5 V signalling environment definition.

- 32-bit data bus

- · Compatibility with the PCI Rev. 2.1 Specification

- Support for up to four master devices

Interrupts are not routed through the APB. A separate Drain/Empty protocol is used to guarantee that all DMA writes temporally complete to memory, prior to receipt of an interrupt, and thus before a potential processor trap as a result of that interrupt.

The Primary bus, which can be used with or without the Advanced PCI Bridge, has the same characteristics discussed above, except it can run in the 20-33 MHz or the 40-66 MHz range. UltraSPARC-IIi operates internally at twice the external PCI clock frequency, that is, up to 132 MHz. This helps reduce the latency involved in crossing clock domains and manipulating state machines.

Figure 9. Example of Externally-Connected PCI Subsystem

#### **UPA64S** interface (FFB)

UPA64S is a slave-only interface protocol used, for instance, by proprietary graphics boards. It can be used for any high bandwidth control or data transfers between the processor and a dedicated subsystem.

UltraSPARC-IIi drives the SYSADR (system address), ADR\_VLD (address valid) signals, the P\_REPLY and S\_REPLY handshakes, and reset (RST\_L) to the UPA64S. The data bus (64 bits out of 72) is shared with the transceiver connection to the UltraSPARC-IIi. The internal memory controller of the UltraSPARC-IIi transfers data aligned to processor clocks, but guarantees that UPA64S transfers appear aligned to the UPA64S clock. In other words, these are valid for 3 processor clock cycles, and only sampled on the UPA clock edge when UPA64S is driving.

Note that, although the transceivers only cycle the 72-bit MEMDATA at 75 MHz maximum, the FFB/UPA64S cycle this bus at up to 100 MHz.

307

Figure 10. UltraSPARC-IIi PCI Sub-System

308 Sun Microelectronics July 1997

### **TIMING DIAGRAMS**

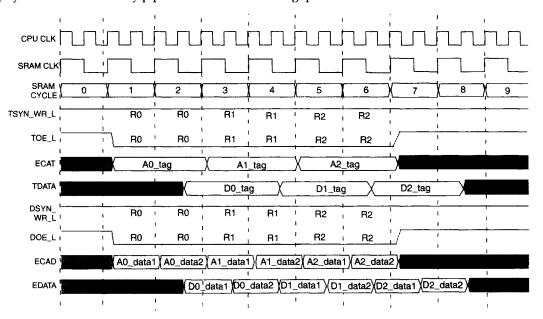

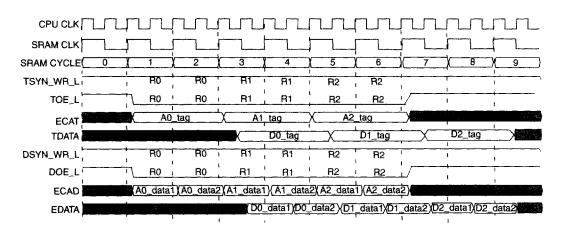

#### E-Cache Read Hit in 2-2 Mode

Three consecutive reads are shown hitting the E-Cache in Figure 11. The control signal (TOE\_L) and the address for the tag read (ECAT) are shown in transition shortly after the rising edge of the clock — along with the control signal DOE\_L and address for the data (ECAD). One cycle later, the data for both the tag read and the data read is back at the pins of the CPU. The data arrives shortly before the next rising edge, meeting the set-up time and clock skew requirements. The data bus is eight bytes wide so the data RAM is accessed twice for each data read request. The most critical eight bytes (D0\_data1) of data are returned first followed by the next eight bytes (D0\_data2) in the subsequent clock cycle. For each read request, both the tag address and the tag data are stable for 2 clock cycles, but the data address and data read changes every cycle. The reads are fully pipelined to allow full throughput.

Figure 11. Timing for E-Cache Read Hit (2-2 mode)

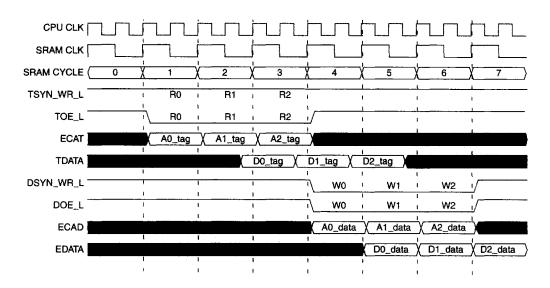

#### E-Cache Write Hit to M State Line in 2-2 Mode

Figure 12. Timing for E-Cache Write Hit to M State Line (2-2 mode)

Figure 12 shows the 2-2 timing mode for three consecutive write hits to the M state lines. Access to the first tag (D0\_tag) is started by asserting TOE\_L and by sending the tag address (A0\_tag). In the cycle after the tag data (D0\_tag) comes back, UltraSPARC-IIi determines that the access is a hit and that the line is in Modified (M) state. In the next clock, a request is made to write the data. The data address is presented on the ECAD pins in the cycle after the request (cycle 4 for W0) and the data is sent in the following cycle (cycle 5). Systems running in 2-2 mode incur no read-to-write bus turnaround penalty.

#### Read-to-Write Transition in 2-2 Mode

Figure 13 shows the read-to-write transition for 2-2 mode. Three reads are followed by two writes and two tag updates. Since the tag and data appear in the same cycle as the write, there is no turnaround penalty for reads followed by writes in 2-2 mode.

Figure 13. No Turn-Around Penalty: Read-to-Write Transition (2-2 mode)

#### E-Cache Read Hit In 2-2-2 Mode

Figure 14 shows the 2-2-2 mode timing for three consecutive reads that hit the E-cache. The control signal (TOE\_L) and the address for the tag read (ECAT) as well as the control signal (DOE\_L) and the address for the data (ECAD) are shown to change state shortly after the rising edge of clock cycle 1. Two cycles later the data from the tag RAM and the critical eight bytes (D0\_data1) from the data RAM are back at the pins of the CPU, just before the rising edge of cycle 4. One cycle later the next eight bytes of data (D0\_data2) returns from the data RAM. Note that, for each read request, the tag address and tag data are stable for two clock cycles, but the data address and data read changes every cycle. This is because the data RAM is accessed twice for each read request. Two requests are made before the data of the first read request returns.

Figure 14. Timing for E-Cache Read Hit (2-2-2 mode)

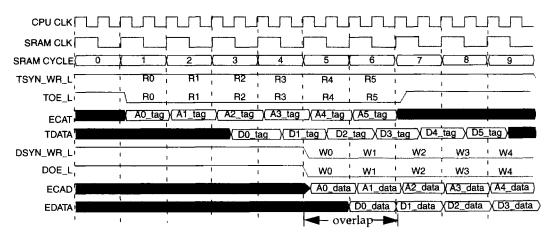

#### E-Cache Write Hits In 2-2-2 Mode

Figure 15 shows the 2-2-2 mode timing for six consecutive write hits to M state lines. Access to the first tag (D0\_tag) is started by asserting the tag address (A0\_tag) in clock cycle 1. The tag data comes back two cycles later in cycle 3. In clock cycle 4, UltraSPARC-IIi determines that the access is a hit and that the line is in Modified (M) state. In the next cycle, a request is made to write the data by asserting the data address (A0\_data). The write data (D0\_data) is sent in the next cycle. Separating the address and data by one cycle reduces the turn-around penalty when reads are immediately followed by writes (Figure 17).

If the line is in M state, then the tag port is available for the tag check of a more recent store during the data write cycle. In *Figure 15* the store buffer is empty when the first request is made, which is why there is no overlap between the tag accesses and the write accesses. In normal operation, if the line is in M state, the tag access for one write can be done in parallel with the data write step of a previous write phase. In *Figure 15*, clock cycles 5 and 6 show overlap of two previous data writes (W0, W1) and tag accesses for two more recent stores (R4 and R5).

Figure 15. Timing for E-Cache Write Hit to M State Line (2-2-2 mode)

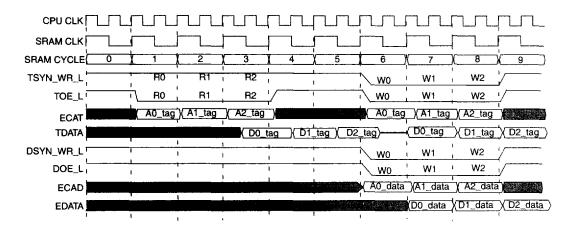

Figure 16. Timing for E-Cache Writes with E-to-M State Transition (2-2-2 mode)

Figure 16 shows the timing of E-Cache writes with E-to-M state transition. The tag checks in clock cycles 3, 4 and 5 found the line in Exclusive (E) state. The tag is updated to Modified (M) state at the same time data is written in clocks 6, 7 and 8, respectively.

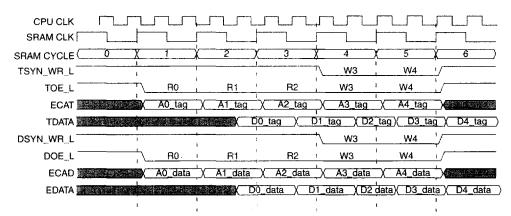

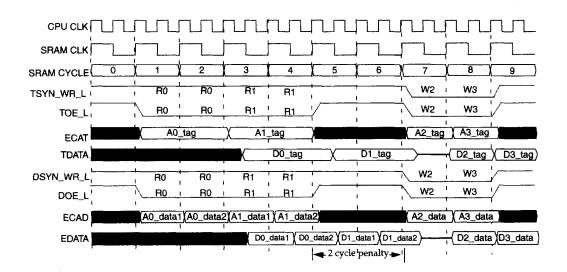

### E-Cache Read Followed by E-Cache Write In 2-2-2 Mode

Figure 17 shows the two-cycle read-to-write turnaround penalty for 2-2-2 mode. The figure shows two reads followed by two writes and two tag updates. The data for the second read (R1) is available in clock cycles 5 and 6. UltraSPARC-IIi cannot assert the write address in clock cycle 6 because electrical considerations force an extra dead cycle while the E-cache data bus driver is switched from the SRAMs to UltraSPARC-IIi. The address for the first write is asserted in clock cycle 7. This causes a two-cycle turnaround penalty. The two-cycle penalty applies to both tag accesses and data accesses because there are two stalled cycles between A1\_tag and A2\_tag, as well as between A1\_data and A2\_data.

Figure 17. Read -to-Write Turnaround Penalty (2-2-2 Mode Only) for E-Cache Read Hit (2-2-2 mode)

# **DRAM Timing**

#### Dram Write

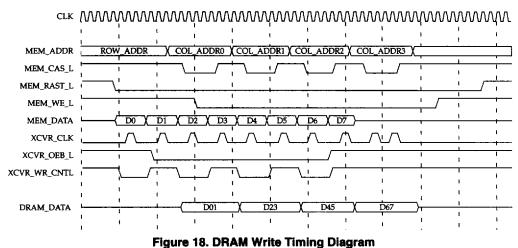

rigure to bithin title tilling blugia

Figure 18 shows the timing of a DRAM write.

#### DRAM Read

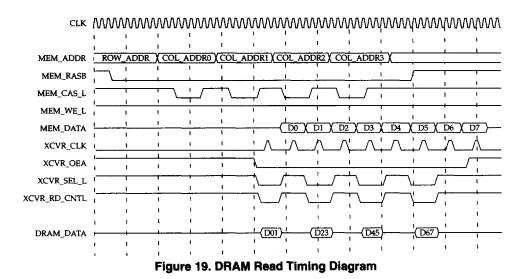

Figure 19 shows the timing diagram for a DRAM read operation.

# **PCI TIMING INFORMATION**

### PCI Read

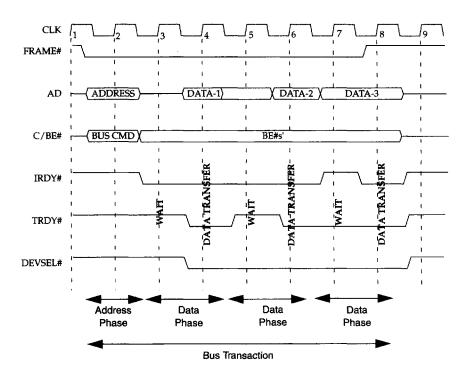

Figure 20 below illustrates a PCI read transaction. For more information, see the relevant section of the PCI Specification.

Figure 20. Basic PCI Read Operation

#### **PCI Write**

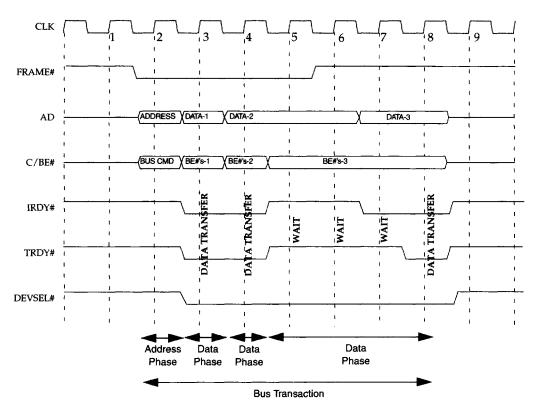

*Figure* 21 below illustrates a PCI write transaction. For more information, see the relevant section of the PCI Specification.

Figure 21. Basic PCI Write Operation

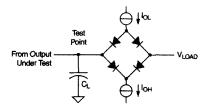

### **ELECTRICAL CHARACTERISTICS**

#### Absolute Maximum Ratings[1]