# MOTOROLA ■ SEMICONDUCTOR TECHNICAL DATA

# 16K × 4 Bit Synchronous Static RAM with Output Registers and Output Enable

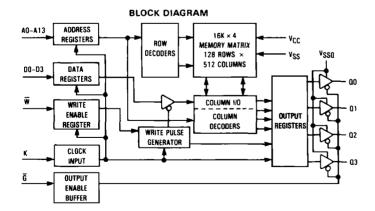

The MCM6294 is a 65,536 bit synchronous static random access memory organized as 16,384 words of 4 bits, fabricated using Motorola's second-generation high-performance silicon-gate CMOS (HCMOS III) technology. The device integrates input registers, high speed SRAM, and high-drive capability output registers onto a single monolithic circuit for reduced parts count implementation of cache data RAM and writeable control store applications. Synchronous design allows precise cycle control with the use of an external clock (k), while CMOS circuitry reduces the overall power consumption of the integrated functions for greater reliability.

The address (A0-A13), data (D0-D3), and write  $(\overline{W})$  inputs are all clock (K) controlled, positive-edge-triggered, noninverting registers.

The MCM6294 provides output register operation. At the rising edge of K, the RAM data from the previous K high cycle is presented. This function is well suited to fully pipeliried applications.

The output enable  $(\overline{\mathbf{G}})$  provides asynchronous bus control for common I/O or bank switch applications.

Write operations are internally self-timed and initiated by the rising edge of the K input. This feature eliminates complex off-chip write pulse generation and provides increased flexibility for incoming signals.

The MCM6294 is available in a 300-mil, 28-pin plastic DIP as well as a 400-mil, 28-pin plastic SOJ package.

- Single 5 V ± 10% Power Supply

- Fast Cycle Times: 20/25/30 ns Max

- Fast Clock (K) Access Times: 10/13/15 ns Max

- Address, Data Input, and W Registers On-Chip

- Output Enable for Asynchronous Bus Control

- Output Registers for Fully Pipelined Applications

- High Output Drive Capability

- Internally Self-Timed Write Pulse Generation

- Separate Data Input and Data Output Pins

- High Board Density SOJ Package Available

- Typical Applications: General-Purpose Buffer Storage, Writeable Control Store, Data Cache, or Cache Tag

# MCM6294

| PIN               | ASSIGN                 | IMI | ENT                |

|-------------------|------------------------|-----|--------------------|

| A5 [              | 1 •                    | 28  | b <sub>vcc</sub>   |

| A6 [              | 2                      | 27  | ) A4               |

| A7 [              | 3                      | 26  | ] A3               |

| A8 [              | 4                      | 25  | A2                 |

| A9 [              | 5                      | 24  | ) A1               |

| A10 [             | 6                      | 23  | D AO               |

| A11 [             | 7                      | 22  | <b>1</b> 03        |

| A12 [             | 8                      | 21  | 02                 |

| A13 [             | 9                      | 20  | <b>1</b> 03        |

| DO <b>[</b>       | 10                     | 19  | 02                 |

| D1 <b>C</b>       | 11                     | 18  | <b>1</b> 01        |

| ēd                | 12                     | 17  | իտ                 |

| κД                | 13                     | 16  | þ₩                 |

| v <sub>ss</sub> C | 14                     | 15  | o <sub>sso</sub> + |

|                   | nimum cyc<br>ions, VSS |     |                    |

| PIN NAMES                 |

|---------------------------|

| A0-A13 , Address Inputs   |

| W Write Enable            |

| G Output Enable           |

| D0-D3 Data inputs         |

| Q0-Q3 Data Outputs        |

| K Clock Input             |

| VCC +5 V Power Supply     |

| VSS Ground                |

| VSSQ Output Buffer Ground |

isolated from VSS.

#### TRUTH TABLE

| w | Operation | O0-O3            |

|---|-----------|------------------|

| L | Write     | High Z           |

| Н | Read      | D <sub>out</sub> |

NOTE: The value  $\overline{\mathbf{W}}$  is a valid input for the setup and hold times relative to the K rising edge.

# ABSOLUTE MAXIMUM RATINGS (Voltages referenced to VSS=VSSQ=0 V)

| Rating                                                 | Symbol                             | Value                        | Unit |

|--------------------------------------------------------|------------------------------------|------------------------------|------|

| Power Supply Voltage                                   | Vcc                                | -0.5 to +7.0                 | ٧    |

| Voltage Relative to VSS/VSSQ for Any<br>Pin Except VCC | V <sub>in</sub> , V <sub>out</sub> | -0.5 to V <sub>CC</sub> +0.5 | ٧    |

| Output Current (per I/O)                               | lout                               | ±20                          | mA   |

| Power Dissipation (T <sub>A</sub> = 25°C)              | PD                                 | 1.0                          | w    |

| Temperature Under Bias                                 | Tbias                              | -10 to +85                   | ۰c   |

| Operating Temperature                                  | T <sub>A</sub>                     | 0 to +70                     | ۰c   |

| Storage Temperature                                    | Tstg                               | ~55 to +125                  | °C   |

NOTE: Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to RECOMMENDED OPERATING CONDITIONS. Exposure to higher than recommended voltages for extended periods of time could affect device reliability.

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high-impedence circuit.

This is a synchronous device. All synchronous inputs must meet the specified setup and hold times with stable logic levels for ALL rising edges of clock (K) while the device is selected.

This device contains circuitry that will ensure the output devices are in High Z at power up. Care should be taken by the user to ensure that all clocks are at  $V_{\parallel L}$  or  $V_{\parallel H}$  during power up to prevent spurious read cycles from occurring.

#### DC OPERATING CONDITIONS AND CHARACTERISTICS

$(V_{CC} = 5.0 \text{ V} \pm 10\%, T_A = 0 \text{ to } 70^{\circ}\text{C}, \text{ Unless Otherwise Noted})$

# **RECOMMENDED OPERATING CONDITIONS** (Voltages referenced to $V_{SS} = V_{SSQ} = 0$ V)

| Parameter                                | Symbol | Min   | Тур | Max                  | Unit |

|------------------------------------------|--------|-------|-----|----------------------|------|

| Supply Voltage (Operating Voltage Range) | vcc    | 4.5   | 5.0 | 5.5                  | >    |

| Input High Voltage                       | VIH    | 2.0   | -   | V <sub>CC</sub> +0.3 | >    |

| Input Low Voltage                        | VIL    | -0.5* | _   | 0.8                  | >    |

$V_{IL}$  (min) = -0.5 V dc;  $V_{IL}$  (min) = -3.0 V ac (pulse width  $\leq$ 20 ns)

### DC CHARACTERISTICS

| Parameter                                                                                                    | Symbol  | Min | Max   | Unit |

|--------------------------------------------------------------------------------------------------------------|---------|-----|-------|------|

| Input Leakage Current (All Inputs, Vin = 0 to VCC)                                                           | likg(i) | -   | ± 1.0 | μA   |

| Output Leakage Current (G=V <sub>IH</sub> , V <sub>out</sub> =0 to V <sub>CC</sub> , Outputs must be high-Z) | likg(O) | _   | ±1.0  | μA   |

| AC Supply Current (G=V <sub>IL</sub> , I <sub>out</sub> =0 mA, Cycle Time=t <sub>KHKH</sub> min)             | ICCA    | ·   | 140   | mA   |

| Output Low Voltage (I <sub>OL</sub> = 12.0 mA)                                                               | VOL     | -   | 0.4   | V    |

| Output High Voltage (IOH = -10.0 mA)                                                                         | VOH     | 2.4 | _     | V    |

#### CAPACITANCE (f = 1.0 MHz, dV = 3.0 V, TA = 25°C, Periodically Sampled Rather Than 100% Tested)

| Characteristic     | Symbol | Тур | Max | Unit |

|--------------------|--------|-----|-----|------|

| Input Capacitance  | Cin    | 4   | 6   | pF   |

| Output Capacitance | Cout   | 7   | 10  | pF   |

# **AC OPERATING CONDITIONS AND CHARACTERISTICS**

( $V_{CC} = 5.0 \text{ V} \pm 10\%$ ,  $T_A = 0 \text{ to } +70^{\circ}\text{C}$ , Unless Otherwise Noted)

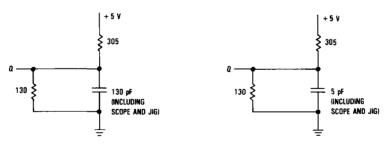

| Input Timing Measurement Reference Level 1.5 V | Output Timing Measurement Reference Level 1.5 V |

|------------------------------------------------|-------------------------------------------------|

| Input Pulse Levels                             | Output LoadSee Figure 1A Unless Otherwise Noted |

| Input Rise/Fall Time                           |                                                 |

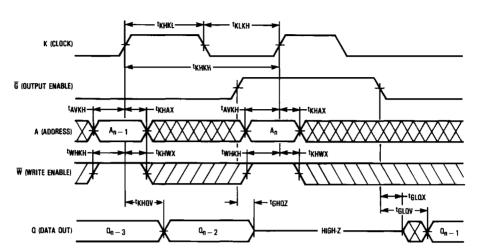

#### READ CYCLE (See Note 1)

| D                             | _      | MCM6294-20        |     | MCM6294-25 |     | MCM6294-30 |     |     |      |       |

|-------------------------------|--------|-------------------|-----|------------|-----|------------|-----|-----|------|-------|

| Parameter                     |        | Symbol            | Min | Max        | Min | Max        | Min | Max | Unit | Notes |

| Read Cycle Time               |        | tKHKH             | 20  | -          | 25  | _          | 30  | -   | ns   | 2     |

| Clock Access Time             |        | tKHQV             | -   | 10         | _   | 10         | _   | 13  | ns   | 3     |

| Output Active from Clock High |        | †KHQX             | 0   | -          | 0   | -          | 0   | -   | ns   | 4     |

| Clock Low Pulse Width         |        | tKLKH             | 5   | _          | 5   | _          | 5   | -   | ns   |       |

| Clock High Pulse Width        |        | tKHKL             | 5   |            | 5   | -          | 5   | _   | ns   |       |

| Setup Times for:              | ₩<br>W | tAVKH<br>tWHKH    | 5   | _          | 5   | _          | 5   | _   | ns   | 5     |

| Hold Times for:               | ₩      | tKHAX<br>tKHWX    | 3   | _          | 3   | _          | 3   | _   | ns   | 5     |

| G High to Q High Z            |        | <sup>‡</sup> GHQZ | -   | 10         | -   | 10         | _   | 13  | ns   | 4, 6  |

| G Low to Q Active             |        | tGLQX             | 0   | _          | 0   | _          | 0   | _   | ns   | 4, 6  |

| G Low to Q Valid              |        | tGLQV             | _   | 10         | -   | 10         | _   | 13  | ns   |       |

#### NOTES:

- 1. A read is defined by W high for the setup and hold times.

- 2. All read cycle timing is referenced from K or from G.

- 3. Valid data from K high will be the data stored at the address of the last valid read cycle.

- 4. Transition is measured ±500 mV from steady-state voltage with load of Figure 1B. This parameter is sampled not 100% tested.

- 5. This is a synchronous device. All synchronous inputs must meet the specified setup and hold times with stable logic levels for ALL rising edges of clock (K) while the device is selected.

- 6. At any given voltage and temperature, tGHOZ max is less than tGLOX min for a given device.

#### AC TEST LOADS

Figure 1A

Figure 1B

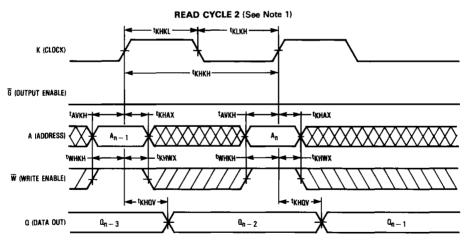

# READ CYCLE 1 (See Note 1)

NOTE:

1. The outputs  $Q_{n-3}$  and  $Q_{n-2}$  are derived from two previous read cycles, where  $\overline{W} = V_{IH}$  for those cycles.

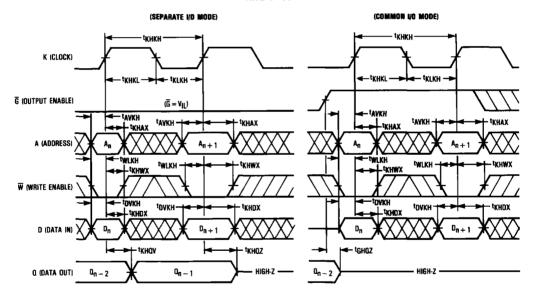

### WRITE CYCLE (W Controlled, See Note 1)

| Parameter                           |             | Symbol                  | MCM6294-20 |     | MCM6294-25 |     | MCM6294-30 |     |      | ١     |

|-------------------------------------|-------------|-------------------------|------------|-----|------------|-----|------------|-----|------|-------|

|                                     |             |                         | Min        | Max | Min        | Max | Min        | Max | Unit | Notes |

| Write Cycle Time                    |             | tKHKH                   | 20         | -   | 25         | -   | 30         | _   | ns   | 2     |

| Clock High to Output High Z (₩=VIL) |             | tKHQZ                   | _          | 10  | _          | 10  |            | 13  | ns   | 3     |

| G High to Q High Z                  |             | tGHOZ                   | _          | 10  | -          | 10  | _          | 13  | ns   | 4     |

| Setup Times for:                    | A<br>₩<br>D | tAVKH<br>tWLKH<br>tDVKH | 5          | _   | 5          | _   | 5          | _   | ns   | 5     |

| Hold Times for:                     | A<br>₩<br>D | tKHAX<br>tKHWX<br>tKHDX | 3          | _   | 3          | -   | 3          | -   | ns   | 5     |

#### NOTES:

- 1. A write is performed when  $\overline{\mathbf{W}}$  is low for the specified setup and hold times.

- 2. All write cycle timing is referenced from K or from G.

- Transition is measured ±500 mV from steady-state voltage with load of Figure 1B. At any given voltage and temperature, t<sub>KHQZ</sub> max is less than t<sub>KHQX</sub> min for a given device.

- 4. G becomes a don't care signal for successive writes after the first write cycle.

- This is a synchronous device. All synchronous inputs must meet the specified setup and hold times with stable logic levels for ALL rising edges of clock (K) while the device is selected.

#### WRITE CYCLE

#### APPLICATIONS INFORMATION

The Motorola family of synchronous SRAMs is designed to provide a performance and parts count advantage in applications such as writeable control stores, memory mapping, and cache memory. The on-board input registers eliminate the need for external latch chips in systems where addresses and data are not on the bus long enough to satisfy standard SRAM setup and hold times. Registers on the output port provide extended hold times independent of address or other device input changes to better meet system access requirements. The clock (K) input controls the operation of the input registers and output registers, and provides a direct means of synchronizing the SRAM to a system clock.

The MCM6294 offers registered output operation. On the

rising edge of the clock (K) signal, the output data for the previous cycle is latched until the next rising clock edge.

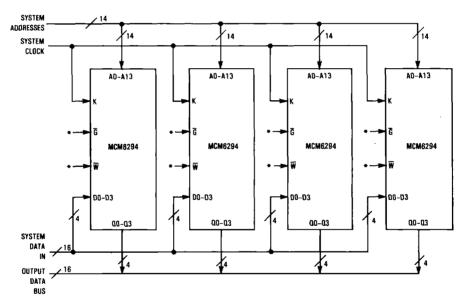

Figure 2 shows a typical system configuration using four MCM6294 chips. The system addresses are tied to the MCM6294s in parallel, while system data is distributed among the four input data ports of 4 bits each. Output data is tied to a separate output data bus to exploit the separate I/O configuration of the MCM6294. The clock (K) signal is a logical derivation of the system clock.

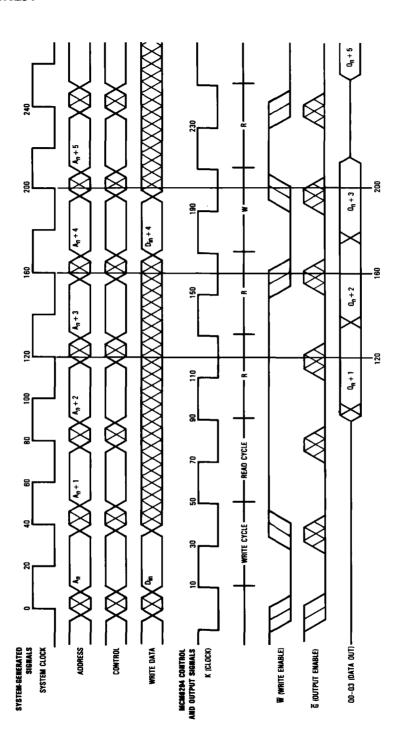

Figure 3 shows typical bus timing for the configuration of Figure 2. The system bus supplies address, data, and control signals, while accepting data from the memory on rising clock edges. In some applications, the clock (K) signal may need to be a delayed system clock to allow adequate address and data setup times.

\*From read/write controller.

Figure 2. Typical Configuration for a 16-Bit Bus

Figure 3. Pipeline System Timing

NOTES:

1. The system supplies address, data, and control information and accepts data from memory on the rising edge of the system clock.

2. The memory clock is delayed 10 ns (for this example) to allow input information to propagate to the memory chips.

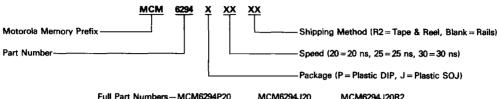

# ORDERING INFORMATION (Order by Full Part Number)

Full Part Numbers — MCM6294P20 MCM6294P25

MCM6294P30

MCM6294J20 MCM6294J25 MCM6294J30 MCM6294J20R2 MCM6294J25R2 MCM6294J30R2