#### Transil array for data protection

#### **Description:**

TY Semicondutor<sup>®</sup>

The ESDA6V8UW is 4-channel very low capacitance ESD transient voltage suppressor which provides a very high level of protection for sensitive electronic components that may be subjected to electrostatic discharge. It is particularly well-suited to protect systems with high speed communication lines from ESD, EFT, and lighting.

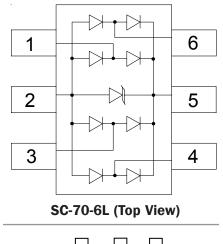

The ESDA6V8UW is consists of eight low capacitance steering diodes and a TVS diode in a SC-70-6L package. Each channel of ESDA6V8UW could safely dissipate ESD strikes of  $\pm 15$ kV air discharge as well as  $\pm 8$ kV contact discharge, meeting the requirement of the IEC 61000-4-2 international standard. Using the MIL-STD-883 (Method 3015) specification for Human Body Model (HBM) ESD, the device provides protection for contact discharges to greater than  $\pm 15$ kV.

#### **Specification Features:**

- Stand-off Voltage: 5 V

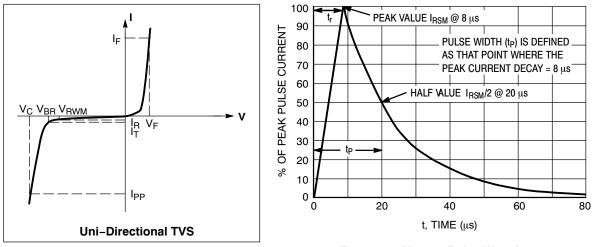

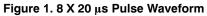

- Peak Power up to 300 Watts @ 8 x 20 us Pulse

- Low Leakage current IEC61000-4-2

- Level 4 ESD Protection IEC61000-4-4

- Level 4 EFT Protection

- Low capacitance: 0.7 pF typical

### **Mechanical Characteristics**

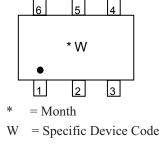

- SC-70-6L Package

- Pb–Free Packages are Available

- Molding compound flammability rating: UL 94V-0

- Packaging: Tape and Reel per EIA 481

(SC-70-6L)

#### Applications

- High Speed Communication Line Protection

- USB 2.0 Power and Data Line Protection

- Monitors and Flat Panel Displays Notebook Computers

- Video Line Protection & Base Stations

- HDSL, IDSL Secondary IC Side Protection

- Microcontroller Input Protection

- LCD and camera modules

- 10/100/1000 Ethernet

# Absolute Max Ratings (Tamb=25 C)

| Rating                                            | Symbol          | Value       | Units |

|---------------------------------------------------|-----------------|-------------|-------|

| Peak Pulse Power(tp = 8/20µs)                     | P <sub>PP</sub> | 300         | W     |

| ESD per IEC 61000-4-2 (Air)                       | Vpp             | +/-15       | KV    |

| ESD per IEC 61000-4-2 (Contact)                   |                 | +/-8        |       |

| Maximum lead temperature for soldering during 10s | TL              | 260         | °C    |

| Storage Temperature Range                         | Tstg            | -55 to +125 | °C    |

| Operating Temperature Range                       | Тор             | -55 to +125 | °C    |

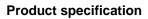

### **Electrical Parameter**

| Symbol           | Parameter                              |

|------------------|----------------------------------------|

| I <sub>PP</sub>  | Maximum Reverse Peak Pulse Current     |

| V <sub>C</sub>   | Clamping Voltage @ IPP                 |

| V <sub>RWM</sub> | Working Peak Reverse Voltage           |

| I <sub>R</sub>   | Maximum Reverse Leakage Current @ VRWM |

| I <sub>T</sub>   | Test Current                           |

| V <sub>BR</sub>  | Breakdown Voltage @ IT                 |

| I <sub>F</sub>   | Forward Current                        |

| VF               | Forward Voltage @ IF                   |

## **Electrical Characteristics**

TY Semicondutor<sup>®</sup>

#### (T=25°C, Device for 5.0V Reverse Stand-off Voltage)

|                   | Conditions                          | Minimum | Typical | Maximum | Unit |

|-------------------|-------------------------------------|---------|---------|---------|------|

| I <sub>R</sub>    | V <sub>RWM</sub> =5V, Pin5 to 2     |         |         | 5       | uA   |

| V <sub>F</sub>    | $I_F = 10 \text{mA}$                | 0.4     | 0.8     | 1.5     | V    |

| V <sub>BR</sub> , | $I_T=1mA$ , Pin5 to 2               | 6.0     | 7.0     |         | V    |

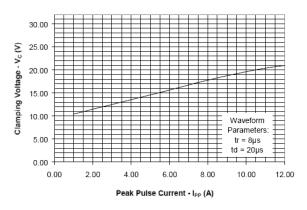

| V <sub>C</sub>    | $I_{PP}=1A$ , tp = 8/20us, note 1&2 |         |         | 12.0    | V    |

|                   | Any I/O pin to Ground               |         |         |         |      |

| Cj                | $V_R = 0V, f = 1MHz$                |         | 1.2     | 1.5     | pF   |

|                   | Any I/O pin to Ground               |         |         |         |      |

|                   | $V_R = 0V, f = 1MHz$                |         | 0.7     |         | pF   |

|                   | Between I/O pins                    |         |         |         |      |

Note 1: These parameters guaranteed by design and characterization. Note 2: These measurements performed with no external capacitor on Pin5.

## **Typical Characteristics**

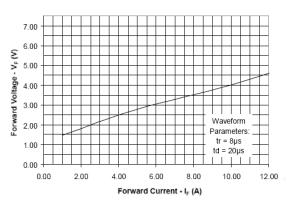

**Clamping Voltage vs. Peak Pulse Current**

Forward Voltage vs. Forward Current

## **Applications Information**

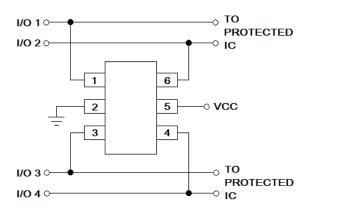

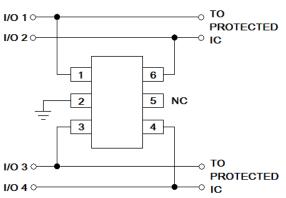

#### Device Connection Options for Protection of Four Digh-Speed Data Lines

This device is designed to protect data lines by clamping them to a fixed reference. When the voltage on the protected line exceeds the reference voltage the steering diodes are forward biased, conducting the transient current away from the sensitive circuitry. Data lines are connected at pins 1, 3, 4 and 6. Pin 2 should be connected directly to a ground plane. The path length is kept as short as possible to minimize parasitic inductance. The positive reference is connected at pin 5. The options for connecting the positive reference are as follows:

1. To protect data lines and the power line, connect pin 5 directly to the positive supply rail (VCC). In this configuration the data lines are referenced to the supply voltage. The internal TVS diode prevents over-voltage on the supply rail.

2. In applications where the supply rail does not exit the system, the internal TVS may be used as the reference. In this case, pin 5 is not connected. The steering diodes will begin to conduct when the voltage on the protected line exceeds the working voltage of the TVS (plus one diode drop).

3. In applications where complete supply isolation is desired, the internal TVS is again used as the reference and VCC is connected to one of the I/O inputs. An example of this configuration is the protection of a SIM port. The Clock, Reset, I/O, and VCC lines are connected at pins 1, 3, 4, and 6. Pin 2 is connected to ground and pin 5 is not connected.

#### **Data Line and Power Supply Protection Using Vcc as reference**

#### Data Line Protection Using Internal TVS Diode as reference

#### Matte Tin Lead Finish

Matte tin has become the industry standard lead-free replacement for SnPb lead finishes. A matte tin finish is composed of  $100\Box$  tin solder with large grains. Since the solder volume on the leads is small compared to the solder paste volume that is placed on the land pattern of the PCB, the reflow profile will be determined by the requirements of the solder paste. Therefore, these devices are compatible with both lead-free and SnPb assembly techniques. In addition, unlike other lead-free compositions, matte tin does not have any added alloys that can cause degradation of the solder joint.

## Package mechanical data

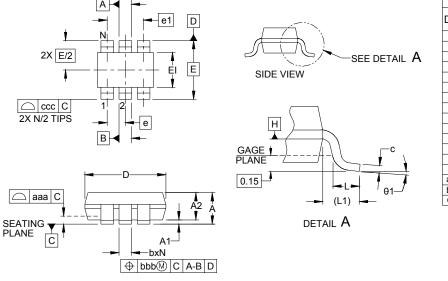

Outline drawing:

| DIMENSIONS |          |      |             |          |      |      |

|------------|----------|------|-------------|----------|------|------|

| DIM        | INCHES   |      | MILLIMETERS |          |      |      |

| ואווט      | MIN      | NOM  | MAX         | MIN      | NOM  | MAX  |

| Α          | -        | -    | .043        | -        | -    | 1.10 |

| A1         | .000     | -    | .004        | 0.00     | -    | 0.10 |

| A2         | .028     | .035 | .039        | 0.70     | 0.90 | 1.00 |

| b          | .006     | -    | .012        | 0.15     | -    | 0.30 |

| С          | .003     | -    | .009        | 0.08     | -    | 0.22 |

| D          | .075     | .079 | .083        | 1.90     | 2.00 | 2.10 |

| E1         | .045     | .049 | .053        | 1.15     | 1.25 | 1.35 |

| Е          | .083 BSC |      |             | 2.10 BSC |      |      |

| е          | .026 BSC |      | 0.65 BSC    |          |      |      |

| e1         | .051     |      | 1.30 BSC    |          |      |      |

| L          | .010     | .014 | .018        | 0.26     | 0.36 | 0.46 |

| L1         | (.017)   |      |             | (0.42)   |      |      |

| N          | 6        |      | 6           |          |      |      |

| θ1         | 0°       | -    | 8°          | 0°       | -    | 8°   |

| aaa        | .004     |      | 0.10        |          |      |      |

| bbb        | .004     |      | 0.10        |          |      |      |

| CCC        | .012     |      |             | 0.30     |      |      |

#### NOTES:

- 1. CONTROLLING DIMENSIONS ARE IN MILLIMETERS (ANGLES IN DEGREES).

- 2. DATUMS -A- AND -B- TO BE DETERMINED AT DATUM PLANE-H-

- 3. DIMENSIONS "E1" AND "D" DO NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.

- 4. REFERENCE JEDEC STD MO-203, VARIATION AB.

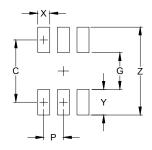

#### Land Pattern:

|     | DIMENSIONS |             |  |  |

|-----|------------|-------------|--|--|

| DIM | INCHES     | MILLIMETERS |  |  |

| С   | (.073)     | (1.85)      |  |  |

| G   | .039       | 1.00        |  |  |

| Р   | .026       | 0.65        |  |  |

| Х   | .016       | 0.40        |  |  |

| Y   | .033       | 0.85        |  |  |

| Z   | .106       | 2.70        |  |  |

NOTES:

1. THIS LAND PATTERN IS FOR REFERENCE PURPOSES ONLY. CONSULT YOUR MANUFACTURING GROUP TO ENSURE YOUR COMPANY'S MANUFACTURING GUIDELINES ARE MET.