# CCD321A/B 455/910—Bit Analog Shift Register Charge Coupled Device

### **FEATURES**

- Electrically variable analog delay line for audio and video applications.

- 1 H video delay line capability with broadcast quality performance.

- Excellent bandwidth at video and audio rates due to buried channel technology.

- Wide range of data rate: from 10 kHz to 20 MHz per 455 section.

- High signal to noise ratio Video: 58 dB, Audio: 65 dB.

- Special modifications available consult factory.

#### DESCRIPTION

The CCD321 is an electrically variable analog delay line intended to be used in analog signal processing systems that include delay and temporary storage of analog information. The CCD321 consists of two 455-bit analog shift registers, each with its own injection port, transport clock and output port allowing the device to be used as two 455 or one 910-bit analog delay line.

The CCD321 can be used in applications ranging from video frequencies to audio frequencies. A complete TV line of 63.5 µs can be stored with a sampling frequency of 14.318 MHz (four times color subcarrier frequency of 3.58 MHz). Applications in video systems include time base correction, comb filtering and signal-to-noise enhancing. Audio applications include variable delay of audio signals, reverberation effects in stereo equipment, tone delay in organs and musical instruments as well as voice scrambling applications. The CCD321 also finds applications in time base compression and expansion applications where analog data can be fed at one rate to the device, the clocks can be temporarily stopped and then data clocked out at a different rate.

The CCD321B is an improved pin-for-pin replacement for the CCD321A. The CCD321 is available in four different classes as follows:

| DEVICE       | APPLICATION         |                             |

|--------------|---------------------|-----------------------------|

| follows:     |                     |                             |

| CCU321A, THE | CCD321 IS available | IT TOUT OTHER ETT CHASSES A |

CCD321A-1 Broadcast quality video delay line

CCD321A-2/B-2 Industrial video delay line

CCD321A-3/B-3 Time base compression and expansion delay line

CCD321A-4/B-4 Audio delay line

|                                                                            | PIN NAMES                                   | PIN CONNECTION DIAGRAM   |                      |  |  |  |

|----------------------------------------------------------------------------|---------------------------------------------|--------------------------|----------------------|--|--|--|

| φ <sub>1A</sub> .φ <sub>1B</sub> Analog Shift Register<br>Transport Clocks |                                             | 16-PIN DIP<br>(TOP VIEW) |                      |  |  |  |

| $\phi_{SA}.\phi_{SB}$                                                      | Input Sampling Clocks                       |                          |                      |  |  |  |

| $\phi_{RA}.\phi_{RB}$                                                      | Output Sample and                           | VOA □ 1 `                | 16 <b>□</b> ∨DD      |  |  |  |

|                                                                            | Hold Clocks                                 | V <sub>GG</sub> □ 2      | 15 ☐ V <sub>OB</sub> |  |  |  |

| v <sub>2</sub>                                                             | Analog Shift Register<br>DC Transport Phase | VIA                      | 14 🗖 V2              |  |  |  |

| V <sub>IA</sub> ,V <sub>IB</sub>                                           | Analog Inputs                               | VRA □ 4                  | 13 V1B               |  |  |  |

| V <sub>RA</sub> .V <sub>RB</sub>                                           | Analog Reference Inputs                     | ØSA <b>□</b> 5           | 12 VRB               |  |  |  |

| $v_{OA}, v_{OB}$                                                           | Analog Outputs                              | ₽1A <b>□</b> 6           | 11 <b>□</b>          |  |  |  |

| V <sub>DD</sub>                                                            | Output Drain                                | <b>Ф</b> ВА <b>□</b> 7   | 10 <b>□</b> #18      |  |  |  |

| $v_{GG}$                                                                   | Signal Ground                               | ∨ss 🗖 <sup>в</sup>       | 9                    |  |  |  |

| v <sub>ss</sub>                                                            | Substrate Ground                            |                          |                      |  |  |  |

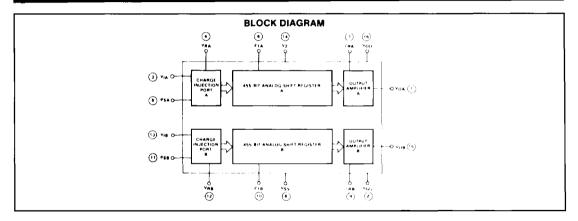

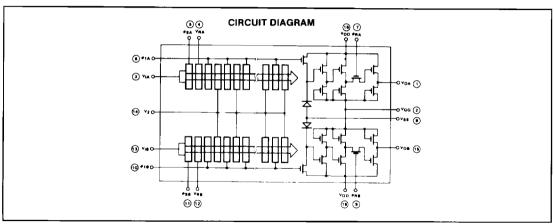

**FUNCTIONAL DESCRIPTION** — The CCD321 consists of the following elements illustrated in the Block Diagram:

Two Charge Injection Ports — The analog information in voltage form is applied to two input ports at  $V_{IA}$  (or  $V_{IB}$ ). Upon the activation of the analog sample clocks  $\phi_{SA}$  (or  $\phi_{SB}$ ) a charge packet linearly dependent on the voltage difference between  $V_{IA}$  and  $V_{RA}$  (or  $V_{IB}$  and  $V_{RB}$ ) is injected into analog shift register A [or B].

Two 455-Bit Analog Shift Registers — Each register transports the charge packets from the charge injection port to its corresponding output amplifier. Both registers are operated in the 1-1/2 phase mode where one phase  $(\phi_{1A} \text{ or } \phi_{1B})$  is a clock and the other phase  $(V_2)$  is an intermediate dc potential. Phases  $\phi_{1A}$  and  $\phi_{1B}$  are completely independent.  $V_2$  is a dc voltage common to both registers.

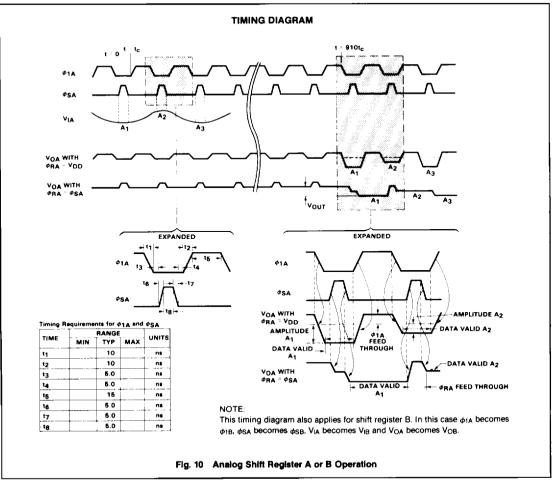

Two Output Amplifiers — Charge packets from each analog shift register are delivered to their corresponding output amplifier as shown in the circuit diagram. Each output amplifier consists of three source follower stages with constant current source bias. A sample and hold transistor is located between the second and third stage of the amplifier. When the gate of the sample and hold transistor is clocked  $|\phi_{RA}\rangle$  a continuous output waveform is obtained as shown in the timing diagrams. The sample and hold transistor can be defeated by connecting  $\phi_{RA}$  and/or  $\phi_{RB}$  to  $V_{DD}$ . In this case the output is a pulse modulated waveform as shown in the timing diagram.

**MODES OF OPERATION** — The CCD321 can be operated in four different modes:

**455-Bit Analog Delay** — Either 455-bit analog shift register can be operated independently as a 455-bit delay line. The driving waveforms to operate shift register A is shown in Fig. 10. The input voltage signal is applied directly to  $V_{IA}$ . The input sampling clock  $\phi_{SA}$  samples this input voltage and injects a proportional amount of charge packet into the first bit of register A. The input voltage  $A_1$  which is sampled between t=0 and  $t=t_C$  appears at the output terminal  $V_{OA}$  ( $\phi_{CA}$ )  $\phi_{CA}$  is a poly and hold circuit is not used then the output appears as a pulse amplitude modulated waveform as shown in the diagram. In that case  $\phi_{RA}$  (pin 7) should be connected to  $V_{DO}$  (pin 16). If the sample and hold circuit is used then the output appears as a continuous waveform. Here  $\phi_{RA}$  (pin 7) should be clocked coincident with  $\phi_{SA}$  (pin 5) and the two pins can be connected together.

Analog shift register B can be operated in an analogous manner with  $V_{IB}$  as the analog input,  $\phi_{1B}$  as the transport clock,  $\phi_{SB}$  as the input sampling clock and  $\phi_{RB}$  as the output sample and hold clock

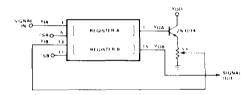

910-Bit Analog Delay in Series Mode — The two analog shift registers A and B can be connected in series to provide 910 bits of analog delay as shown in the schematic below. The analog signal input voltage is applied to  $V_{IA}$ . The output of register A is connected to the input of register B with a simple emitter follower buffer stage. In order to insure proper charge injection of register B,  $V_{RB}$  should be adjusted. The timing diagram shown in Fig. 10 applies in this mode of operation. Here  $\phi_{1B} = \phi_{1B}$ ,  $\phi_{SA} = \phi_{SB}$ ,  $\phi_{RA} = V_{DD}$ , and  $\phi_{RB}$  is clocked.

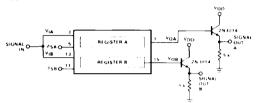

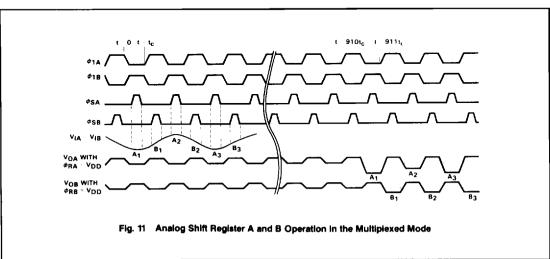

**910-Bit Analog Delay in Multiplexed Mode** — The two analog shift registers can be connected in parallel to provide 910-bit of analog delay as shown in the schematic below. The analog signal input voltage is applied to both  $V_{IA}$  and  $V_{IB}$ . The outputs at  $V_{OB}$  can be combined as shown in Fig. 8 to recover the analog input information.

The necessary waveforms to operate the device in this mode is shown in Fig. 11. In this case  $\phi_{SA}$  samples the analog input  $A_1$  at  $V_{IA}$  between t=0 and  $t=t_C$ .  $\phi_{SB}$  samples the analog input B, at  $V_{IB}$ , between  $t=t_C$  and  $t=2t_C$ . The output corresponding to  $A_1$  appears at  $V_{OA}$  at  $t=910t_C$ . The output corresponding to  $B_1$  appears at  $V_{OB}$  @  $t=911t_C$ . This mode of operation results in an effective sampling rate of twice the rate of  $\phi_{1A}$ ,  $\phi_{1B}$ ,  $\phi_{SA}$  and  $\phi_{SB}$ .

### CCD321A/B

**Stop/Start Mode Operation** — The charge packets in the two analog shift registers can be held stationary by stopping  $\phi_{1A}$  and  $\phi_{1B}$  in their LOW state.  $\phi_{SA}$ ,  $\phi_{SB}$ ,  $\phi_{RA}$ ,  $\phi_{RB}$  can also be stopped in the LOW state or kept clocking as usual. The two shift registers should not be connected in series in the stop-start mode of operation.

The CCD321 is available in four different classes for different applications. The CCD321A-1 is a high quality broadcast 1H delay line for video systems with 1% differential gain and 1° differential phase. The CCD321A-2/B-2 is a high quality video delay line with 3% differential gain and 3° differential phase.

The CCD321A-3/B-3 is tested in the START/STOP mode of operation and parameters are guaranteed in this mode. The CCD321A-4/B-4 is tested at audio speeds; audio parameters are specified and guaranteed. The dc and clock characteristics of the four classes are the same. The ac characteristics vary as shown below.

**Caution:** The device has limited built-in gate protection. Charge build-up should be minimized. Care should be taken to avoid shortings pins  $V_{OA}$  and  $V_{OB}$  to ground during operation of the device.

| DC CHAR         | ACTERISTICS: TA = 55°C, Note 16                     |       |      |      |       |                                                                                      |

|-----------------|-----------------------------------------------------|-------|------|------|-------|--------------------------------------------------------------------------------------|

| SYMBOL          | CHARACTERISTICS                                     | RANGE |      |      |       | CONDITIONS                                                                           |

|                 |                                                     | MIN   | TYP  | MAX  | UNITS | CONDITIONS                                                                           |

| V <sub>DD</sub> | Output Drain Voltage                                | 14.5  | 15.0 | 15.5 | \ \   |                                                                                      |

| V <sub>2</sub>  | Analog Shift Register DC Transport<br>Phase Voltage |       | 6.0  |      | v     | Note 1                                                                               |

| VRA, VRB        | Analog Reference Inputs Voltage                     |       | 3-7  |      | V     | Note 2                                                                               |

| Vgg             | Signal Ground                                       |       | 0.0  |      |       |                                                                                      |

| Vss             | Substrate Ground                                    |       | 0.0  |      |       | Note 3                                                                               |

| VIA, VIB        | Input DC Level                                      |       | 3-7  |      | V     | Note 2                                                                               |

| VOA. VOB        | Output DC Level                                     |       | 6-11 |      | V     | V <sub>DD</sub> = 15 V                                                               |

| RiN             | Small Signal Input Resistance                       |       | 1.0  |      | MΩ    | Resistance from Pins 3, 4, 12 or 13 to Vss. V <sub>IA</sub> = V <sub>IB</sub> = 3 V  |

| Cin             | Small Signal Input Capacitance                      |       | 10   |      | pF    | Capacitance from Pins 3, 4, 12 or 13 to Vss. V <sub>IA</sub> = V <sub>IB</sub> = 3 V |

| Rout            | Small Signal Output Resistance                      |       | 250  |      | Ω     | V <sub>DD</sub> = 15 V                                                               |

| ODM             | Output DC Mismatch Between A & B Registers          |       | ±1   |      | V     |                                                                                      |

| OAM             | Output AC Mismatch Between A & B Registers          |       | ±20  |      | %     |                                                                                      |

| SYMBOL                                | CHARACTERISTICS                                 |      | RANGE |      | 1     | CONDITIONS  |

|---------------------------------------|-------------------------------------------------|------|-------|------|-------|-------------|

| STMBOL                                | CHARACTERISTICS                                 | MIN  | TYP   | MAX  | UNITS |             |

| Vφ1AL, Vφ1BL                          | Analog Shift Register Transport Clocks LOW      | 0    | 0.5   | 0.8  | V     | Note 4      |

| Vф1AH, Vф1BH                          | Analog Shift Register Transport Clocks HIGH     | 12.0 | 13.0  | 15.0 | V     | Note 4      |

| VØSAL, VØSBL                          | Input Sampling Clocks LOW                       | 0    | 0.5   | 0.8  | ν     | Note 5      |

| Vфsaн, Vфsвн                          | Input Sampling Clocks HIGH                      | 12.0 | 13.0  | 15.0 | v     | Note 5      |

| VØRAL, VØRBL                          | Output Sample and Hold Clocks LOW               | 0    | 0.5   | 0.8  | V     | Note 6      |

| V <sub>PRAH</sub> , V <sub>PRBH</sub> | Output Sample and Hold Clocks HIGH              | 12.0 | 13.0  | 15.0 | v     | Note 6      |

| fφ1A,fφ1B                             | Analog Shift Register Transport Clock Frequency | 0.02 |       | 20   | MHz   | See Note 17 |

| tφsa,fφsb                             | Input Sampling Clocks Frequency                 | 0.02 |       | 20   | MHz   | See Note 17 |

| fφ <sub>RA</sub> ,fφ <sub>RB</sub>    | Output Sample and Hold Clocks Frequency         | 0.02 |       | 20   | MHz   | See Note 17 |

### **ABSOLUTE MAXIMUM RATINGS**

Storage Temperature Operating Temperature All Pins with Respect to V<sub>SS</sub> 25°C to 100°C 25°C to 55°C 0.3 V to 18 V

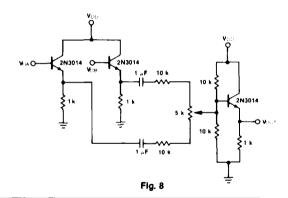

CCD321A-1 AC CHARACTERISTICS: T<sub>A</sub> 55°C. Both registers in the multiplexed mode, Clock Rate = 7.16 MHz. Sampling Rate = 14.32 MHz. Vout = 700 mV = See Test Load Configuration, Figure 8

| SYMBOL    | CHARACTERISTIC               |     | RANGE |     |        |            |

|-----------|------------------------------|-----|-------|-----|--------|------------|

|           |                              | MIN | TYP   | MAX | UNITS  | CONDITIONS |

| BW        | Signal Bandwidth 3 dB Down   | 5.0 |       |     | MHz    | Note 7     |

| IG        | Insertion Gain               | 0   | 30    | 6.0 | dB     | Note 8     |

| 7 G       | Differential Gain            |     |       | 2.0 | %      | Note 9     |

| Δφ        | Differential Phase           | ,   |       | 1.0 | degree | Note 9     |

| S/N       | Signal-to-Noise Ratio        | 58  |       |     | dB     | Note 10    |

| Victoriax | Maximum Input Signal Voltage |     | 1.0   |     | Vpk-pk |            |

CCD321A-2/B-2 AC CHARACTERISTICS: T<sub>A</sub> 55°C. Both registers in the multiplexed mode, Clock Rate = 7.16 MHz, Sampling Rate = 14.32 MHz | V<sub>OUT</sub> = 700 mV | See Test Load Configuration, Figure 8

| SYMBOL              | CHARACTERISTIC               | RANGE |     |     |                    |            |

|---------------------|------------------------------|-------|-----|-----|--------------------|------------|

|                     |                              | MIN   | TYP | MAX | UNITS              | CONDITIONS |

| BW                  | Signal Bandwidth 3 dB Down   | 4.2   | 5 0 |     | MHz                | Note 7     |

| IG                  | Insertion Gain               | 0     | 3.0 | 6.0 | đВ                 | Note 8     |

| 2 G                 | Differential Gain            |       |     | 3.0 | 9/0                | Note 9     |

| Δ φ                 | Differential Phase           |       |     | 3.0 | degrees            | Note 9     |

| S/N                 | Signal-to-Noise Ratio        | 58    |     |     | dB                 | Note 10    |

| V <sub>L(max)</sub> | Maximum Input Signal Voltage |       | 10  |     | V <sub>pk pk</sub> |            |

| SYMBOL   | CHARACTERISTIC               |     | RANGE |      |                    |              |

|----------|------------------------------|-----|-------|------|--------------------|--------------|

|          |                              | MIN | TYP   | MAX  | UNITS              | CONDITIONS   |

| BW       | Signal Bandwidth 3 dB Down   | 4.2 | 5.0   |      | MHz                | Note 7       |

| IG       | Insertion Gain               | 0   | 3.0   | 6.0  | dB                 | Note 8       |

| 7 G      | Differential Gain            |     |       | 3.0  | 0/0                | Note 9       |

| Δ φ      | Differential Phase           |     |       | 3.0  | degrees            | Note 9       |

| S/N      | Signal-to-Noise Ratio        | 55  |       |      | dΒ                 | Note 10      |

| SN       | Spacial Noise                |     | 10.0  | 20.0 | mV                 | Notes 11, 12 |

| Vi (max) | Maximum Input Signal Voltage |     | 1.0   |      | V <sub>pk pk</sub> |              |

CCD321A-4/B-4 AC CHARACTERISTICS: T<sub>A</sub> = 45°C. Both registers in the multiplexed mode. Clock Rate = 7.16 MHz. Sampling Rate = 14.32 MHz. V<sub>OUT</sub> ≥ 700 mV. : See Test Load Configuration, Figure 8:

| SYMBOL CHARACTERISTIC | OHADAGTERIGTIO                |     | RANGE |     |                    | 001151710110 |

|-----------------------|-------------------------------|-----|-------|-----|--------------------|--------------|

|                       | CHARACTERISTIC                | MIN | TYP   | MAX | UNITS              | CONDITIONS   |

| BW                    | Signal Bandwidth (3 dB Down)  | 23  | 25    |     | kHz                | Note 7       |

| IG                    | Insertion Gain                | 0   | 3.0   | 6.0 | dB                 | Note 8       |

| THD                   | Total Harmonic Distortion     |     | 0.5   | 1.0 | %                  | Note 13      |

| S/N                   | Signal-to-Noise Ratio         | 60  | 65    |     | dB                 | Note 14      |

| V <sub>I (max)</sub>  | Maximum Input Signal Voltage  |     | 1.0   |     | V <sub>pk-pk</sub> |              |

| RSO                   | Rate of Average Signal Offset |     | 15    |     | mv/ms              | Note 15      |

- Vz level should be 1/2 of the φ1a or φ2a HiGH level. Adjustment in the range of ±1 V may be necessary to maximize signal bandwidth. Signal charge injection is proportional to the difference Vi and Va. Adjustment of either Vi or Va is necessary to assure proper operation. Negative transients below ground of fast rise and fall times of the clocks may cause charge injection from substrate to the shift registers. Anegative bias on Vs. of -2 0 to -5 0 Vdc will eliminate the injection phenomenon.

Ceta = Ceta = 30 pF = Capacitance with respect to Vss.

Ceta = Ceta = 10 pF = Capacitance with respect to Vss.

Ceta = Ceta = 10 pF = Capacitance with respect to Vss.

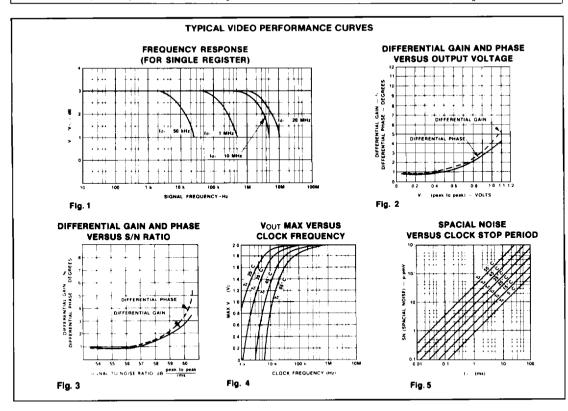

Signal Bandwidth is typically 1/3 to 1/2 of the sampling rate. See Fig. 1.

Insertion Gain = 20 Log Vout/Vin.

Differential Gain and Differential Phase are measured with Tektronix NTSC Signal Generator (147A) and Vector Scope (520A). See Figure 2.

Video S/N is defined as the ratio the peak-to-peak output signal to RMS random (temporal) noise. The peak-to-peak signal is the maximum output level that satisfies the ΔG and Δφ specs. See Fig. 3.

In the start/stop mode of operation is recommended that the rise and fall times of φ1a and φ1g exceed 20 ns to eliminate charge injection.

Spacial Noise is the peak-to-peak spacial variation (fixed pattern noise) in the device output after clocks have been stopped. It is usually caused by the variation of leakage current density in the shift registers. Spacial noise is a function of the clock stop period and temperature. See Figure 5. Input Signal = 1 kHz sine wave. See Figure 6. Audio S/N is defined as the ratio of RMS signal to RMS noise at 23 kHz bandwidth. Both are measured with an HP3400A RMS Voltmeter. See Figure 6. Audio S/N is defined as the ratio of RMS signal to RMS noise at 23 kHz bandwidth. Both are measured with an HP3400A RMS voltmeter. See Figure 6. Audio S/N is defined as the ratio of RMS signal to RMS noise at 28 kHz bandwidth. Both are measured with an HP3400A RMS voltmeter. See Figure 6. Audio S/N is defined

### TYPICAL AUDIO PERFORMANCE CURVES

# TOTAL HARMONIC DISTORTION (THD) AND S/N RATIO VERSUS VOUT

Fig. 6

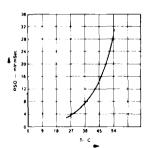

# RATE OF AVERAGE SIGNAL OFFSET VERSUS TEMPERATURE

Fig. 7

# TEST LOAD CONFIGURATION FOR MULTIPLEXED OPERATION IN VIDEO

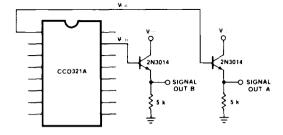

## TEST LOAD CONFIGURATION FOR SINGLE REGISTER OPERATION IN AUDIO AND VIDEO

Fig. 9

### ORDERING INFORMATION

To order the CCD321 specify the "device and package type" as shown below:

| CLASS, APPLICATION                  | SIDEBRAZE PKG. | CERDIP PKG. |

|-------------------------------------|----------------|-------------|

| Broadcast quality video             | CCD321A1       |             |

| Industrial quality video            | CCD321A2       | CCD321B2    |

| Time base compression and expansion | CCD321A3       | CCD321B3    |

| Audio delay line                    | CCD321A4       | CCD321B4    |

Also available is a fully-assembled module that contains all the necessary circuitry to operate the CCD321. The module is designed to help the system designer become familiar with the operation of the device, and for use in OEM systems.

The CCD321VM is a video module using a CCD321A-3 or B-3. The module includes the necessary electronics to perform time base compression and expansion, and variable video signal delay. The module requires a single power supply for operation.

Schematics and component layouts are included in the shipping packages for the CCD321VM. For further information on the CCD321VM please contact your distributor.

### NOTES

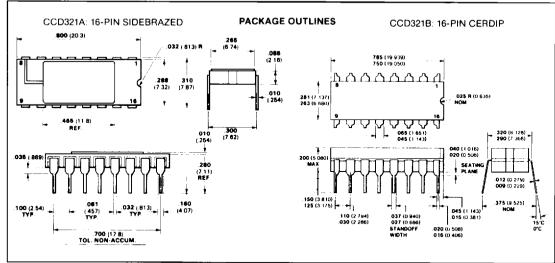

All dimensions in inches  $\cdot$  bold  $\cdot$  and millimeters  $\cdot$  parentheses  $\cdot$ . Header is black ceramic  $\cdot$  Al<sub>2</sub>O<sub>3</sub> $\cdot$ .

Pins are Alloy 42, plated with gold (321A) or nickel (321B). Top cover connected to pin 8 (VSS substrate) on 321A.