## 54F/74F675

### 16-Bit Serial-In, Serial/Parallel-Out Shift Register

#### Description

The 'F675 contains a 16-bit serial-in, serial-out shift register and a 16-bit parallel-out storage register. Separate serial input and output pins are provided for expansion to longer words. By means of a separate clock, the contents of the shift register are transferred to the storage register. The contents of the storage register can also be loaded back into the shift register. A HIGH signal on the Chip Select input prevents both shifting and parallel loading.

- Serial-to-Parallel Converter

- 16-Bit Serial I/O Shift Registerd

- 16-Bit Parallel-Out Storage Register

- Recirculating Parallel Transfer

- Expandable for Longer Words

Ordering Code: See Section 5

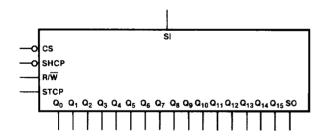

#### **Logic Symbol**

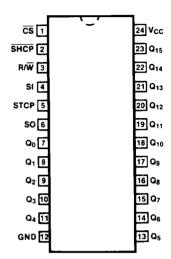

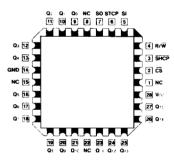

#### **Connection Diagrams**

Pin Assignment for DIP and SOIC

Pin Assignment for LCC and PCC

#### Input Loading/Fan-Out: See Section 3 for U.L. definitions

| Pin Names                       | Description                                   | <b>54F/74F(U.L.)</b><br>HIGH/LOW |

|---------------------------------|-----------------------------------------------|----------------------------------|

| SI                              | Serial Data Input                             | 0.5/0.375                        |

| <u>cs</u>                       | Chip Select Input (Active LOW)                | 0.5/0.375                        |

| SHCP                            | Shift Clock Pulse Input (Active Falling Edge) | 0.5/0.375                        |

| STCP                            | Store Clock Pulse Input (Active Rising Edge)  | 0.5/0.375                        |

| R/W                             | Read/Write Input                              | 0.5/0.375                        |

| so                              | Serial Data Output                            | 25/12.5                          |

| Q <sub>0</sub> -Q <sub>15</sub> | Parallel Data Outputs                         | 25/12.5                          |

#### **Functional Description**

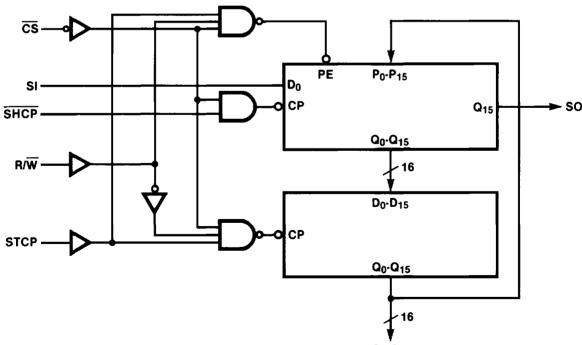

The 16-bit shift register operates in one of four modes, as determined by the signals applied to the Chip Select ( $\overline{CS}$ ), Read/Write ( $R/\overline{W}$ ) and Store Clock Pulse (STCP) input. State changes are indicated by the falling edge of the Shift Clock Pulse ( $\overline{SHCP}$ ). In the Shift Right mode, data enters D<sub>0</sub> from the Serial input (SI) pin and exits from Q<sub>15</sub> via the Serial Data Output (SO) pin. In the Parallel Load mode, data from the storage register outputs enter the shift register and serial shifting is inhibited.

The storage register is in the Hold mode when either  $\overline{CS}$  or  $R/\overline{W}$  is HIGH. With  $\overline{CS}$  and  $R/\overline{W}$  both LOW, the storage register is parallel loaded from the shift register on the rising edge of STCP.

To prevent false clocking of the shift register, SHCP should be in the LOW state during a LOW-to-HIGH transition of  $\overline{CS}$ . To prevent false clocking of the storage register, STCP should be LOW during a HIGH-to-LOW transition of  $\overline{CS}$  if R/W is LOW, and should also be LOW during a HIGH-to-LOW transition of R/W if  $\overline{CS}$  is LOW.

#### **Block Diagram**

#### **Shift Register Operations Table**

|    | Con      | trol Input | Operating |                               |  |  |

|----|----------|------------|-----------|-------------------------------|--|--|

| cs | R/W SHCP |            | STCP      | Mode                          |  |  |

| Н  | х        | Х          | ×         | Hold                          |  |  |

| Ļ  | L        | 1          | X         | Shift Right                   |  |  |

| L  | Н        | 1          | L         | Shift Right                   |  |  |

| L  | Н        | ı          | н         | Parallel Load;<br>No Shifting |  |  |

#### **Storage Register Operations Table**

| Inputs |     |      | Operating     |

|--------|-----|------|---------------|

| ĊŚ     | R/W | STCP | Mode          |

| Н      | Х   | Х    | Hold          |

| L      | ј н | x    | Hold          |

| L      | L   | 1    | Parallel Load |

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

= LOW-to-HIGH Transition

= HIGH-to-LOW Transition

Please note that this diagram is provided only for the understanding of logic  $Q_0$ - $Q_1$ 5 operations and should not be used to estimate propagation delays.

# DC Characteristics over Operating Temperature Range (unless otherwise specified)

|        | Parameter            | 54F/74F |     |     |       |                       |  |

|--------|----------------------|---------|-----|-----|-------|-----------------------|--|

| Symbol |                      | Min     | Тур | Max | Units | Conditions            |  |

| Icc    | Power Supply Current |         | 106 | 160 | mA    | V <sub>CC</sub> = Max |  |

### AC Characteristics: See Section 3 for waveforms and load configurations

| Symbol                               | Parameter                                   | 54F/74F                                              | 54F                                                              | 74F                                                                 | Units | Fig.<br>No. |

|--------------------------------------|---------------------------------------------|------------------------------------------------------|------------------------------------------------------------------|---------------------------------------------------------------------|-------|-------------|

|                                      |                                             | $T_A = +25$ °C<br>$V_{CC} = +5.0$ V<br>$C_L = 50$ pF | T <sub>A</sub> , V <sub>CC</sub> = Mil<br>C <sub>L</sub> = 50 pF | T <sub>A</sub> , V <sub>CC</sub> =<br>Com<br>C <sub>L</sub> ≈ 50 pF |       |             |

|                                      |                                             | Min Typ Max                                          | Min Max                                                          | Min Max                                                             |       |             |

| f <sub>max</sub>                     | Maximum Clock Frequency                     | 100 130                                              |                                                                  | 80                                                                  | MHz   | 3-1         |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay<br>STCP to Q <sub>n</sub> | 6.5 11.0 14.0<br>6.5 11.0 14.0                       |                                                                  | 6.5 15.0<br>6.5 15.0                                                | ns    | 3-1<br>3-7  |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay<br>SHCP to SO             | 5.5 9.0 11.5<br>5.5 9.0 11.5                         |                                                                  | 5.5 12.5<br>5.5 12.5                                                | ns    | 3-1<br>3-8  |

AC Operating Requirements: See Section 3 for waveforms

| Symbol                                   | Parameter                               | 54F/74F                             | 54F                                       | 74F                                    | Units  | Fig.<br>No.      |

|------------------------------------------|-----------------------------------------|-------------------------------------|-------------------------------------------|----------------------------------------|--------|------------------|

|                                          |                                         | $T_A = +25$ °C<br>$V_{CC} = +5.0$ V | T <sub>A</sub> , V <sub>CC</sub> =<br>Mil | T <sub>A</sub> , V <sub>CC</sub> = Com |        |                  |

|                                          |                                         | Min Typ Max                         | Min Max                                   | Min Max                                |        |                  |

| t <sub>s</sub> (H)                       | Setup Time, HIGH<br>CS or R/W to STCP   | 0                                   |                                           | 0                                      |        | 0.5              |

| t <sub>h</sub> (L)                       | Hold Time, LOW<br>CS or R/W to STCP     | 7.0                                 |                                           | 7.0                                    | ns     | 3-5              |

| t <sub>s</sub> (H)<br>t <sub>s</sub> (L) | Setup Time, HIGH or LOW<br>SI to SHCP   | 3.0<br>3.0                          |                                           | 3.0<br>3.0                             |        | 2.6              |

| t <sub>h</sub> (H)<br>t <sub>h</sub> (L) | Hold Time, HIGH or LOW<br>SI to SHCP    | 3.0<br>3.0                          |                                           | 3.0<br>3.0                             | ns<br> | 3-6              |

| t <sub>s</sub> (H)<br>t <sub>s</sub> (L) | Setup Time, HIGH or LOW<br>R/W to SHCP  | 10.0<br>10.0                        |                                           | 10.0<br>10.0                           |        | 3-6              |

| t <sub>h</sub> (H)<br>t <sub>h</sub> (L) | Hold Time, HIGH or LOW<br>R/W to SHCP   | 0                                   |                                           | 0<br>0                                 | ns     |                  |

| t <sub>s</sub> (H)                       | Setup Time, HIGH or LOW<br>STCP to SHCP | 10.0<br>10.0                        |                                           | 10.0<br>10.0                           | ns     | 3-6              |

| t <sub>h</sub> (H)<br>t <sub>h</sub> (L) | Hold Time, HIGH or LOW<br>STCP to SHCP  | 0                                   |                                           | 0<br>0                                 | l lis  | ა <del>-</del> 0 |

| t <sub>s</sub> (L)                       | Setup Time, LOW<br>CS to SHCP           | 7.0                                 |                                           | 7.0                                    |        | 2.6              |

| t <sub>h</sub> (H)                       | Hold Time, HIGH<br>CS to SHCP           | 0                                   |                                           | 0                                      | ns     | 3-6              |

| t <sub>w</sub> (H)<br>t <sub>w</sub> (L) | SHCP Pulse Width,<br>HIGH or LOW        | 5.0<br>5.0                          |                                           | 6.0<br>6.0                             | ns     | 3-8              |

| t <sub>w</sub> (H)<br>t <sub>w</sub> (L) | STCP Pulse Width,<br>HIGH or LOW        | 6.0<br>5.0                          |                                           | 7.0<br>6.0                             | ns     | 3-8              |