The Future of Analog IC Technology

# DESCRIPTION

The HFC0100 is a peak current mode controller with Green Mode Operation. Its high efficiency feature over the entire line and load range meets the stringent world-wide energy efficiency requirements.

The HFC01 00 integrate d with a high voltage current sou rce, its valley detector ensures minimum Drain-Source voltage switching (Quasi-Resonant oper ation). Whe n the output t power falls below a given level, the controller enters the burst mode.

The HFC0100 features variable protections like Thermal Sh utdown (TSD), Vcc Un der voltage Lockout (UVLO), Over Load Protection (OLP), Over Voltage Protection (OVP).

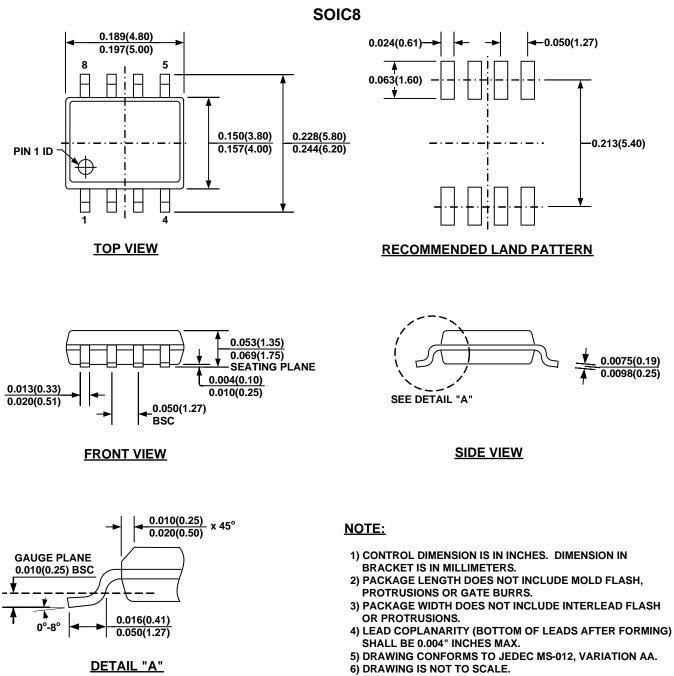

The HF C0100 is a vailable in the 8-p in SOI C8 package.

# FEATURES

- Universal Main Input Voltage (85~265VAC)

- Quasi-Resonant Operation

- Valley Switching for high efficiency and EMI

- Active Burst Mode for low standby powe r consumption

- Internal High Voltage Current Source

- High level of integration, allows a very low number external component count

- Maximum Frequency Limited

- Internal Soft Start

- Internal 250nS Leading Edge Blanking

- Thermal shutdown (auto resta rt with hysteresis)

- Vcc Under Voltage Lockout with Hysteresis (UVLO)

- Over Voltage Protection

- Over Load Protection.

### APPLICATIONS

- Battery ch arger: cellular phone, digital camera, video camera, electrical shaver, emergency lighting system, etc

- Standby power supply: CRT-TV, Projection-TV, LCD-TV, PDP-TV, Desk top PC, Audio system, etc

- SMPS: Inc jet printer, DVD player/recorder, VCR, CD player, Set top box, Air conditioner, refrigerator, washing machine, dish washer, Adapter for NB, etc

For MPS green status, please visit MPS website under Quality Assurance. "MPS" and "The Future of Analog IC Technology" are Registered Trademarks of Monolithic Power Systems, Inc.

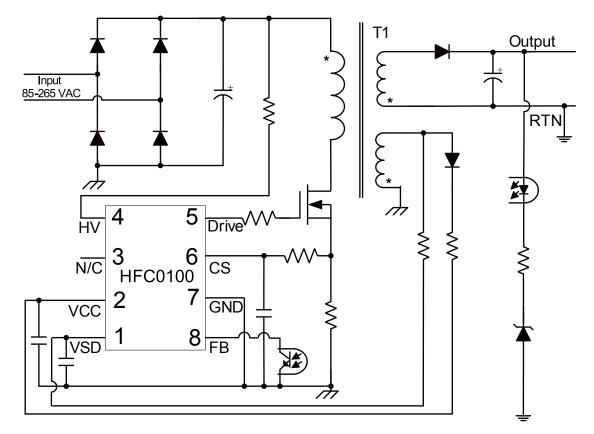

# **TYPICAL APPLICATION**

### **ORDERING INFORMATION**

| Part Number* | Package | Top Marking | Free Air Temperature (T <sub>A</sub> ) |

|--------------|---------|-------------|----------------------------------------|

| HFC0100HS    | SOIC8   | HFC100      | -40°C to +125°C                        |

\*For Tape & Reel, add suffix –Z (e.g. HFC0100HS–Z);

For RoHS compliant packaging, add suffix –LF (e.g. HFC0100HS–LF–Z)

# PACKAGE REFERENCE

### ABSOLUTE MAXIMUM RATINGS (1)

| HV Break Down Voltage0.7V to               | 700V כ              |

|--------------------------------------------|---------------------|

| Vcc, DRV to GND0.3V                        | to 22V              |

| FB, CS, VSD to GND0.3\                     | / to 7V             |

| Continuous Power Dissipation $(T_A = +25)$ | 5°C) <sup>(2)</sup> |

|                                            | 1.3W                |

| Junction Temperature                       | 150°C               |

| Thermal Shut Down                          | .150°C              |

| Thermal Shut Down Hysteresis               | 50°C                |

| Lead Temperature                           |                     |

| Storage Temperature60°C to +               | ·150°C              |

| ESD Capa bility Human Body Model (All      | Pin s               |

| except HV)                                 |                     |

| ESD Capability Machine Model               | . 200V              |

|                                            |                     |

### Recommended Operation Conditions <sup>(3)</sup>

| Operating Vcc range8                     | V to 20V |

|------------------------------------------|----------|

| Maximum Junction Temp. (T <sub>J</sub> ) | +125°C   |

####

#### Notes:

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature re T J (MAX), the junction-to-ambient thermal resistance  $\theta_{JA}$ , and the ambient temperature T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is ca lculated by P<sub>D</sub> (MAX) = (T J (MAX)-T<sub>A</sub>)/ $\theta_{JA}$ . Exceeding the maximum allowable power r dissipation will cause excessive die temperature, and the regulator will g o into thermal shutdown. Internal thermal shutdown circuitr y pr otects the device from permanent damage.

- 3) The device is not guarant eed to function outside of its operating conditions.

- 4) Measured on JESD51-7, 4-layer PCB.

<sup>1)</sup> Exceeding these ratings may damage the device.

# **ELECTRICAL CHARACTERICS**

### For typical value T<sub>J</sub>=25℃

| Parameter                                                                     | Symbol               | Conditions                                                  | Min             | Тур  | Max  | Unit |

|-------------------------------------------------------------------------------|----------------------|-------------------------------------------------------------|-----------------|------|------|------|

| Start-up Current Source (Pin HV)                                              |                      |                                                             |                 |      |      |      |

| Charging current from Pin HV                                                  | I <sub>charge</sub>  | Vcc=6V;V <sub>HV</sub> =400V                                | 1.4             | 2    | 2.6  | mA   |

| Leakage current from Pin HV                                                   | I <sub>leak</sub>    | With auxiliary<br>supply; V <sub>HV</sub> =400V,<br>Vcc=13V |                 | 20   |      | μA   |

| Break Down Voltage                                                            | V <sub>BR</sub>      |                                                             | 700             |      |      | V    |

| Supply Voltage Management (Pin Vcc)                                           |                      |                                                             |                 |      |      | •    |

| Vcc Upper Level at which the Intern al<br>High Voltage Current Source Stops   | V <sub>CCH</sub>     |                                                             | 10.6            | 11.8 | 13   | V    |

| Vcc Lower Level at which the Internal<br>High Voltage Current Source Triggers | V <sub>CCL</sub>     |                                                             | 7.2             | 8    | 8.8  | V    |

| Vcc Re -charge Level at which the protection occurs                           | Vccp                 |                                                             |                 | 5.5  |      | V    |

| Internal IC Consumption, 1nF Load on Drive Pin,                               | lcc1                 | Fs=100kHz,<br>Vcc=12V                                       | 2.0             |      |      | mA   |

| Internal IC Consumption, Latch off phase,                                     | Icc2 VC              | C=6V                                                        |                 | 450  |      | μA   |

| Feedback Management (Pin FB)                                                  | •                    |                                                             |                 |      |      | •    |

| Internal Pull Up Resistor                                                     | R <sub>FB</sub>      |                                                             |                 | 10   |      | kΩ   |

| Internal Pull Up Voltage                                                      | Vup                  |                                                             |                 | 4.5  |      | V    |

| FB Pin to Current Limit Division Ratio                                        | l <sub>div</sub>     |                                                             |                 | 3    |      |      |

| Internal Soft-Start Time                                                      | Tss                  |                                                             |                 | 2.4  |      | mS   |

| FB Decrea sing Level at which the controller enter the Burst Mode             | V <sub>BURL</sub>    |                                                             |                 | 0.5  |      | V    |

| FB Increa sing Level at which the controller leave the Burst Mode             | V <sub>BURH</sub>    |                                                             |                 | 0.7  |      | V    |

| Over Load Set Point                                                           | V <sub>OLP</sub>     |                                                             |                 | 3.7  |      | V    |

| Valley Switching Management (Pin VS                                           | D)                   |                                                             |                 | •    |      | · ·  |

| Valley Switching Threshold Voltage                                            | V <sub>VSD</sub>     |                                                             | 40              | 55   | 70   | mV   |

| Valley Switching Hysteresis                                                   | V <sub>hys</sub>     |                                                             |                 | 10   |      | mV   |

|                                                                               | V <sub>VSDH</sub>    | High State;<br>Ipin2=3.0mA                                  | 7 7.5 8         |      |      |      |

| Pin VSD Clamp Voltage                                                         | $V_{VSDL}$           | Low State;<br>Ipin2=-2.0mA                                  | -0.8 -0.65 -0.5 |      | -0.5 | - V  |

| Valley Switching Propagation Delay                                            | $T_{VSD}$            | Pull down from 2V<br>to -100mV                              | 120 160         |      | 200  | nS   |

| Minimum Off Time                                                              | T <sub>min</sub>     |                                                             | 6.6             | 7.8  | 9    | μS   |

| Re-start time After Las t Valley detec t Transition                           | T <sub>restart</sub> |                                                             |                 | 4.6  |      | μS   |

| OVP Sampling Delay                                                            | T <sub>OVPS</sub>    |                                                             |                 | 3.5  |      | μS   |

| Pin VSD OVP reference level                                                   | V <sub>OVP</sub>     |                                                             |                 | 6    |      | V    |

| Internal Impedance                                                            | Rint                 |                                                             |                 | 24   |      | kΩ   |

| <b>Current Sampling Management (Pin C</b>                                     | S)                   |                                                             |                 |      |      |      |

| Leading Edge Blanking                                                         | T <sub>LEB</sub>     |                                                             |                 | 250  |      | nS   |

| Driving Signal (Pin DRIVE)                                                    |                      | · ·                                                         |                 |      |      |      |

| Sourcing Resistor                                                             | R <sub>H</sub>       |                                                             |                 | 17   |      | Ω    |

| Sinking Resistor                                                              | RL                   |                                                             |                 | 7    |      | Ω    |

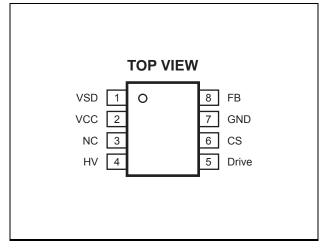

### **PIN FUNCTIONS**

| Pin # | Name  | Description                                                                                                                                                                                                           |

|-------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 VS  | D     | Input from the auxiliary flyback signal, it ensures discontinuous operation and valley switching. It also offers a fixed OVP detection.                                                                               |

| 2 V   | сс    | Supply voltage Pin. This pin is connected to an external bulk capacitor of typically 22uf and a ceramic capacitor of typically 0.1uF.                                                                                 |

| 3     | N/C   | This Pin ensures adequate creepage distance.                                                                                                                                                                          |

| 4     | HV    | Input for the start up current unit.                                                                                                                                                                                  |

| 5     | Drive | Output of the driving signal.                                                                                                                                                                                         |

| 6     | CS    | Input of the current sense.                                                                                                                                                                                           |

| 7 GN  | ١D    | Ground.                                                                                                                                                                                                               |

| 8     | FB    | The Pin sets the peak cu rrent limit, by conne cting an optocoupler to this Pin. A feedback voltage of 3.7V will trigger an over load protection, and a feedback voltage of 0.5V will trigger a burst mode operation. |

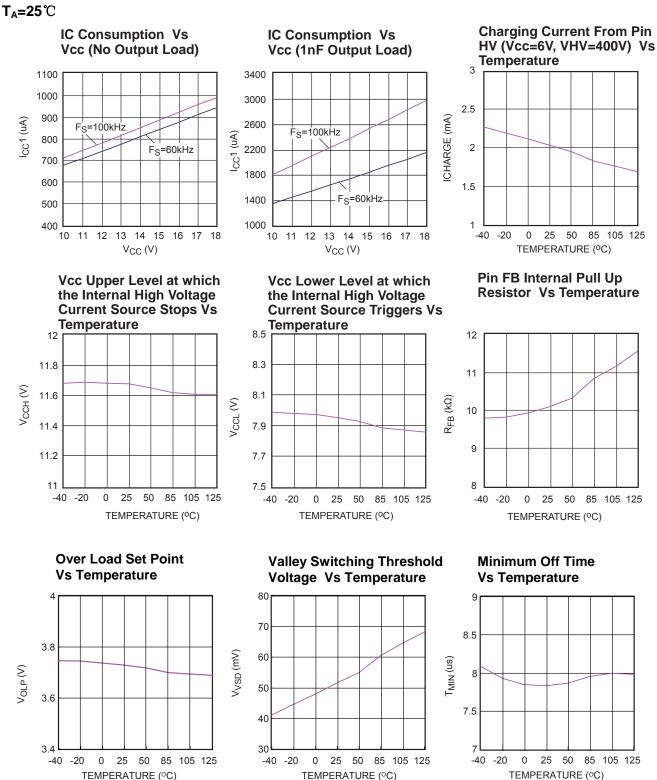

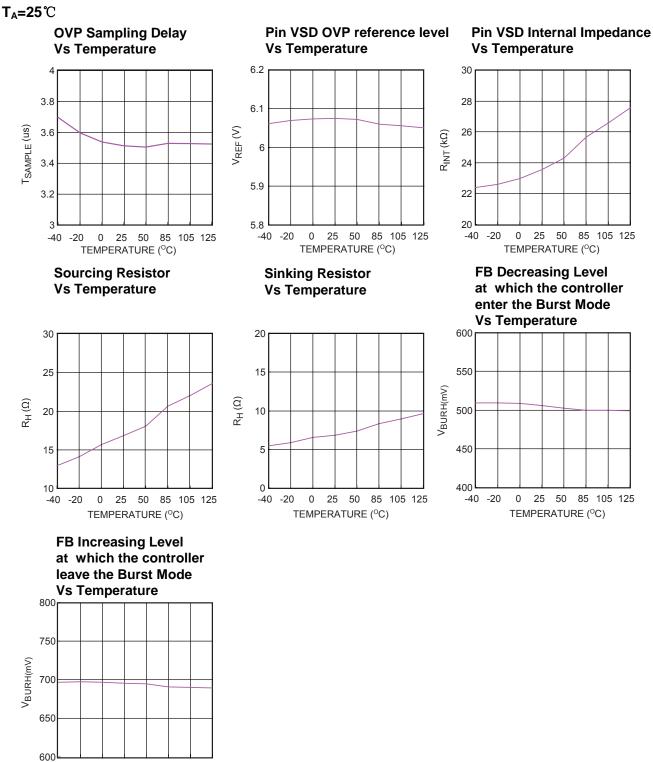

# **TYPICAL PERFORMANCE CHARACTERISTICS**

-40 -20

0

TEMPERATURE (°C)

25 50 85 105 125

# **TYPICAL PERFORMANCE CHARACTERISTICS** (continues)

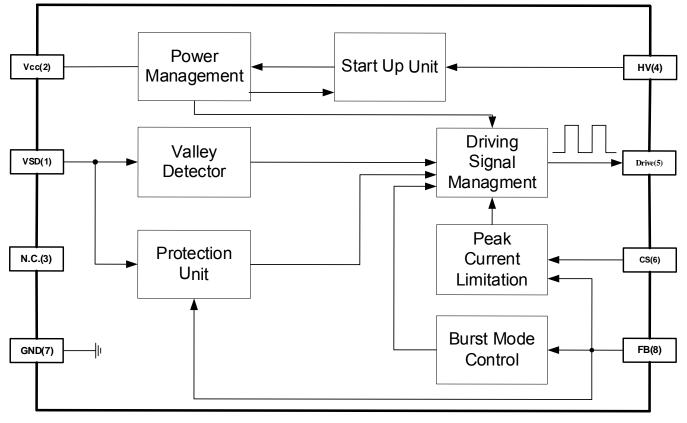

# **BLOCK DIAGRAME**

Figure 1— Block Diagram

# **OPERATION**

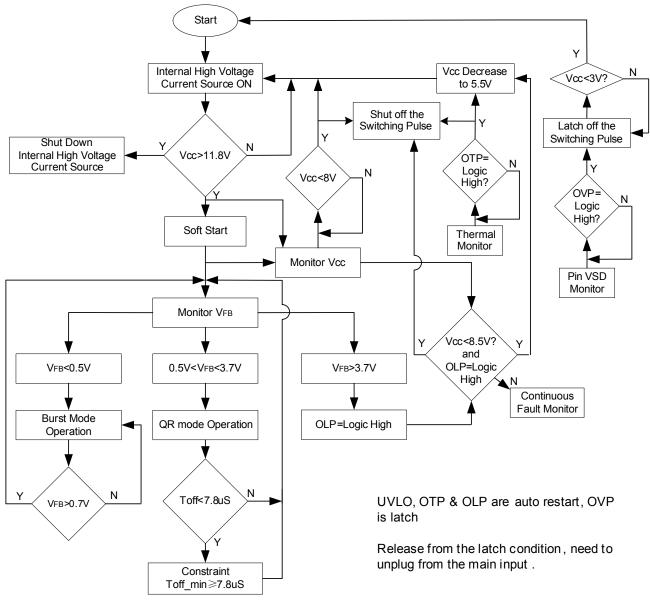

The HFC0100 incorp orates all t he necessa ry features needed to a reliable Switch Mode Power Supply. Its valley det ector ensur es minimu m Drain-Source voltage switching (Q uasi-Resonant operation). When the o utput power falls be low a given level, the regulato r enters the burst mode. An internal minimu m off time limiter prevents the free running frequency to exceed 150kHz.

#### Start-Up

Initially, the IC is self su pplying from the internal high voltag e current source unit which drawn from the HV pin.

The IC starts switchin g and the internal hig h voltage current source unit is stopped as soon as the voltage on Pin Vcc reaches t he threshold  $V_{CCH}$ —11.8V.

Before the supply is taken over by the auxiliary winding of the transformer, the Vcc capa citor supplies HFC0100 to maintain Vcc.

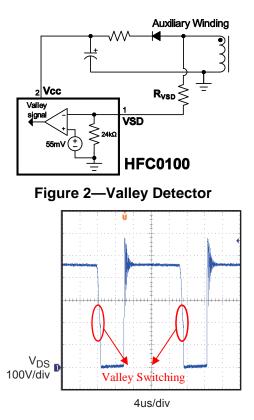

#### **Quasi-Resonant Operation**

The HFC0100 opera tes in Discontinuous Conduction Mode (DCM). The valley detector ensures minimum Drain-Source voltage switching (Quasi-Resonant operation)

As a result, there are virtually no primary s witch turn on losses and no secondary diode recovery losses. It ensures the reduction of the EMI noise.

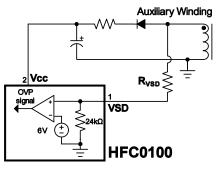

Figure2 shows the valley detector unit.

When the voltage:

$$(V_{DS} - 4J_{in}) x \frac{N_{aux}}{N_{Dri}^2} x \frac{24k\Omega}{4k\Omega + R_{VSD}}$$

55mV

V<sub>DS</sub>—Drain Source Voltage of the primary FET

V<sub>IN</sub>—Input Voltage

Naux — Auxiliary Winding Turns of the transformer

N<sub>pri</sub>—Primary Winding Turns of the transformer

The valley detector se nds out a valley signal to turn on the primary FET.

Figure3 shows a typi cal drain source voltage waveform with valley switching.

Figure 3—Valley Switching

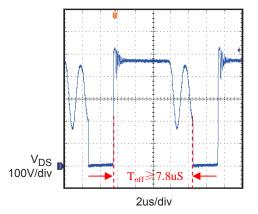

To ensure the switching frequency below the EN55022 start limit---150kHz, HFC0100 employs an internal minimum off time limiter---7.8 $\mu$ S, shows as figure 4.

Figure 4—Minimum Off Time Limit

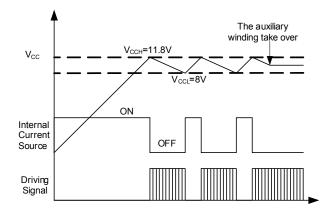

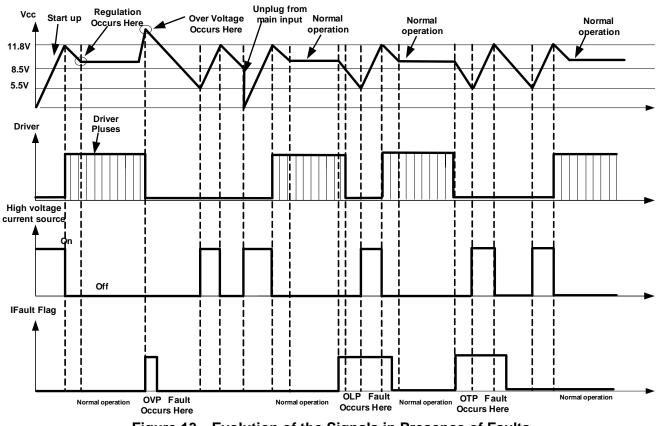

#### Vcc Under-Voltage Lock-out

When the Vcc below the UVLO threshold-8V, the HFC0100 stops swit ching and the internal high voltage current source unit re-starts, the Vcc external bulk capacitor is re-charged by it.

Figure 5 shows the typ ical waveform with Vcc under voltage lock out.

#### Figure 5—Vcc Under-Voltage Lock Out

#### **Over-Voltage Protection (OVP)**

The positive plateau of auxiliary win ding voltage is proportional to the output voltage, the OVP us e the auxiliary winding voltage instea d of directly monitoring the output voltage.

The Figure 6 shows the OVP sample unit.

If the voltage:

$$V_{O} \times \frac{N_{aux}}{N_{SEC}} \times \frac{24k\Omega}{24k\Omega + R_{VSD}} > 6V$$

Vo-Output voltage

N<sub>aux</sub>—Auxiliary Winding Turns of the transformer

N<sub>SEC</sub>—Secondary Winding Tur ns of t he transformer

The OVP ci rcuit is trig gered, and the HFC010 0 stops the switching cycle and goes into latche d fault condition. The controller stays fully latched in this position until the Vcc is decreased down to 3V, e.g. when the user unplugs the power supply from the main supply and re-plugs it.

Figure 6—OVP Sample Unit

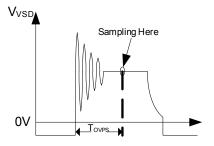

To avoid the mis-trigger due to the oscillat ion of the leakag e inductan ce and the parasitic capacitance, the OVP sampling has a T  $_{OVPS}$  blanking, typical 3.5µS, shows as Figure 7.

#### Figure 7

#### Over Load Protection (OLP)

The maxi mum output power is limited by the maximum switching fr equency and maximum primary pe ak current. If the output consumes more than the maximum output power, the output voltage is drawn below the set point, this reduces the current through the optocouple r LED, which also reduces the transistor current, thus increases the FB voltage.

By continuously monitoring the Pin FB voltage , when the feedback voltage exceeds the threshold V  $_{OLP}$ —3.7V, it shuts off t he switchin g cycle. The HFC0100 e nters a saf e low power operation that prevents from any lethal thermal or stress damage. As soon a s the defa ult disappears, the power supply resumes operation.

During the start up or load transient, the F B voltage will be high en ough temporarily to mistrigger the OLP, to prevent t his unde sired protection, OLP circuit is designed to be triggered after Vcc is decreased below 8.5V.

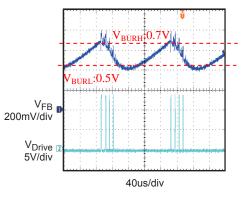

#### **Burst Operation**

To minimize the power dissipat ion in no load or light load, the HFC010 0 enters the burst mo de operation. As the load decreases, the FB voltage decreases,, the HFC0100 stops the switching cycle when the FB voltage drop s below the threshold V <sub>BURL</sub>—0.5V. And the o utput voltage starts to drop at a rate dependent on the load. This causes the FB volt age to rise again. Once 0.7V, switching resumes. The FB voltage then falls and rises repeat edly. The burst mode operation alternately enables and disables switching cycle of the MOSFET thereby reducing switching loss in the no load or light lo ad conditions.

Figure 8 shows the typical F B and Drive waveform during the burst mode.

Figure 8—Burst Mode

#### **Thermal Shutdown (TSD)**

To prevents from any lethal thermal damage. The HFC0100 shuts down switching cycle when th e inner temperature exceeds 150DegC. As soon as the inner temperature drops below 100DegC, the power supply resumes operation.

#### Soft-Start

To reduce the stress on primary MOSFET and secondary diode durin g start up, to smoothly establish the output voltage, the H FC0100 has an internal soft-start circuit that increases the current comparator inverting input voltage, together with the MOSF ET current, slowly after it starts up. The pulse width to the power switching

starts up. The pulse width to the power switching device is progressively increased to establish the correct wo rking cond itions for t ransformers, inductors, and capacitors.

#### **Current Limit Setting**

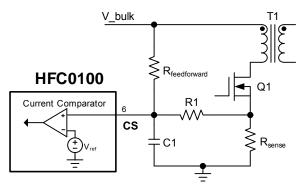

The switch current is sensed by the resistor series between the Source of the FET and the ground. And the current limit is determined by the

FB signal,  $V_{\text{Limit}} = \frac{V_{\text{FB}}}{I_{\text{div}}} = \frac{V_{\text{FB}}}{3}$ . To limit the

maximum output power, the current limit is clamped at 1V when  $V_{FB}$  is bigger than 3.3V.

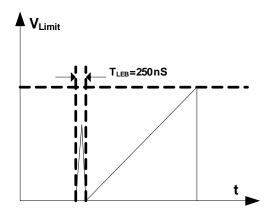

#### Leading Edge Blanking

In order to avoid the premature termination of the switching pulse due to the parasitic capacitance, an internal leading edg e blanking (LEB) unit is employed b etween the CS Pin and the curre nt comparator input. During the blanking time, the path, CS Pi n to the current comparator input, is blocked. Figure 9 shows the leading edge blanking.

#### Figure 9—Leading Edge Blanking

#### **Over Power Compensation**

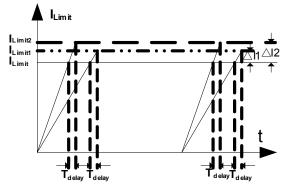

In the case of current sensing, sh ows as figure 10, the turn off of the F ET is delayed due to the propagation delay of the control cir cuit, the delay time is the inherent ch aracteristic of the control circuit, so  $T_{delay}$  can be seen fixed. This delay will cause an overshoot of the peak current.  $\triangle I2$  is bigger than  $\triangle I1$  due to the bigger rising ratio(th e higher input voltage, the bigger rising ratio).

The propagation delay is done by means of the feedforward resistor, shown as Figure 1 1. Through this method, a dding one o ffset voltage at CS pin (the higher input voltage, the big ger offset voltage.).

Figure 10—Propagation delay of the current limit

Figure 11—Over Power Compensation

Figure 12 shows the HFC0100 control flow chart.

Figure 13 shows the H FC0100 evolution of the signals in presence of faults

Figure 12—Control Flow Chart

Figure 13—Evolution of the Signals in Presence of Faults

### PACKAGE INFORMATION

**NOTICE:** The information in this document is subject to change without notice. Users should warrant and guarantee that third party Intell ectual Property rights are not infring ed upon when integrating MPS product s into any application. MPS will not assume any legal responsibility for any said applications.