## International Rectifier

PD-97806

# HIGH RELIABILITY RADIATION HARDENED LOW POWER DC-DC CONVERTER

#### **Description**

The ML-Series of isolated DC-DC converters for space applications are low power radiation hardened high reliability devices designed for hostile radiation environments such as those encountered by geostationary earth orbit satellites, deep space probes and communication systems. Features include small size, high efficiency, low weight, and a good tolerance to total ionizing dose, single event effects, and environmental stresses such as temperature extremes, mechanical shock, and vibration. All components are fully derated to meet the requirements of EEE-INST-002 (NASA) and ECSS-Q-30-11A (ESA). Extensive documentation including worst case analysis, radiation susceptibility, thermal analysis, stress analysis, and reliability analysis are available.

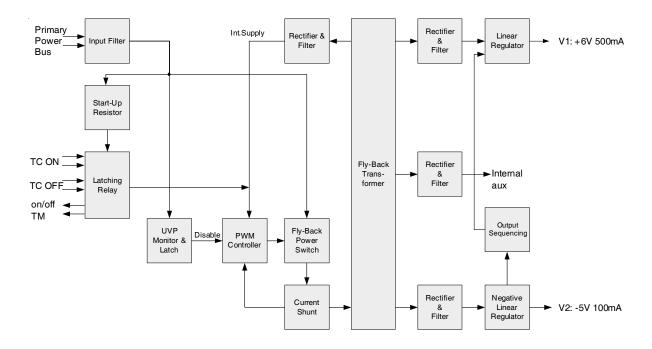

The ML-Series converter has two outputs – one positive and one negative - each is independently regulated via linear post regulators. The outputs are sequenced during turn-on and turn-off such that negative output comes up first at turn-on and stays up at turn-off until the positive output has decreased. The ML-series converters incorporate a fixed frequency flyback power converter and internal EMI filter that meets the requirements for most major satellite power buses. The converter includes isolated On/Off telecommand with associated status telemetry. The converter also includes input under voltage shut-down functionality.

Due to the linear post regulation of the outputs, the ML-Series is well suited for use in RF-applications where low noise, high output voltage accuracy, and high CS attenuation is required.

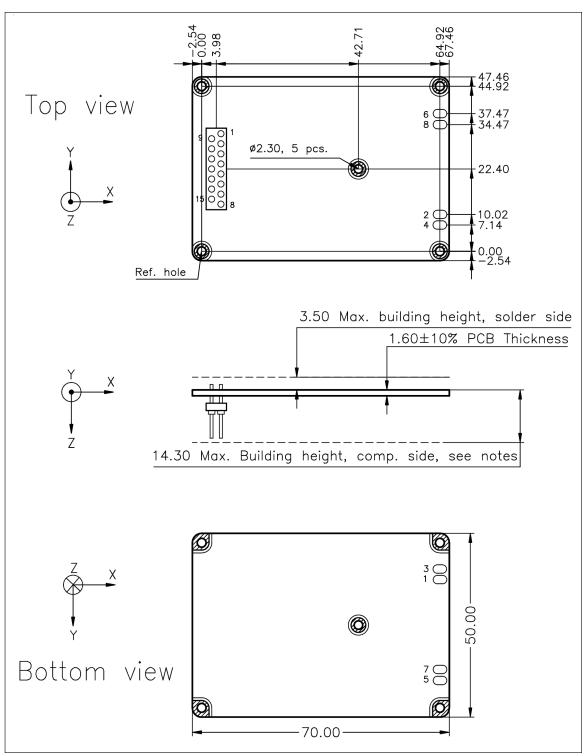

Each converter is provided as a complete board assembly for installation into the host equipment chassis. The board is conformal coated (except for mating surfaces) and is mounted in the host chassis using screws. The board outline is L x W x H:  $70 \text{mm} \times 50 \text{mm} \times 18 \text{mm}$ . The weight is less than 50 grams.

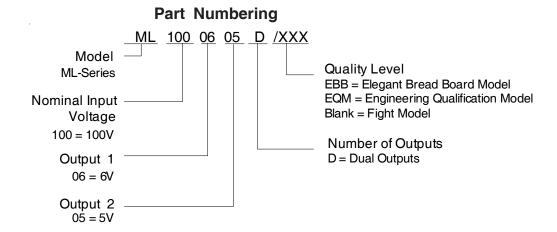

#### ML1000605D 100V Input, Dual Output

#### **Features**

- Total Dose > 100 krad(Si)

- SEE > 82 MeV<sub>•</sub>cm<sup>2</sup>/mg

- Low Weight < 50 grams

- 97V to 103V DC Input Range

- O/P 1: +6.0V (up to 500mA)

- O/P 2: -5.0V (up to 100mA)

- Output Ripple: < 1mVrms (100Hz 50MHz)

- CS Rejection Input to Outputs: > 90dB (50Hz - 1.0MHz)

- 10MΩ @ 100VDC Isolation

- Input Under-Voltage Protection

- Meets Conducted Emission Requirements of Major Power Buses:

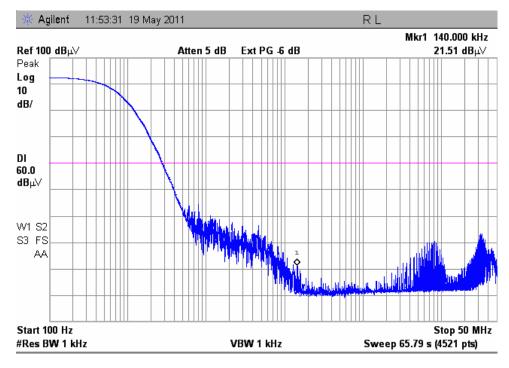

100Hz - 100kHz: 80dBuArms 100kHz - 10MHz: -20dB/decade 10MHz - 50MHz: 40dBuArms

- Short Circuit and Overload Protection

- Meets Derating Requirements of EEE-INST 002 and ECSS-Q-30-11A

- Isolated On/Off Control via High Level Pulse Command (Latching Relay)

- Status Telemetry (Relay Contact Type)

- Workmanship Per IPC-A610 Class 3

- Board is Coated with ARATHANE-5750

#### **Applications**

Low Power RF Systems (like LNA) on-board Satellites

Non-flight versions of the ML-Series converters are available for system development purposes. Variations in electrical specifications and screening to meet custom requirements can be accommodated.

### ML1000605D (100V Input, Dual Output)

#### **Circuit Description**

The ML-Series converters utilize two-stage regulation with a flyback topology with a switching frequency of 140kHz for primary regulation and linear post regulation for each of the outputs.

The Output power is limited under any load fault condition to approximately 120% of rated output. An overload condition on the positive output causes the converter output to behave like a constant current source with the output voltage dropping below nominal. An overload condition at the negative output causes the positive output to shut-down in order to protect RF-transistors in the load. The converter will resume normal operation when the load current is reduced below the current limit point.

An under-voltage protection circuit prohibits the converter from operating when the line voltage is too low for safe operation. In case of an under voltage event the converter will not start when the input voltage returns to its nominal level before an Off-command followed by an On-command has been issued.

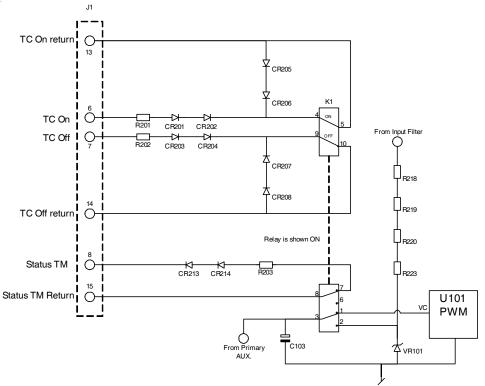

The isolated On/Off telecommand is made with a latching relay and is intended for use with a 26V pulse command. A status telemetry derived from a spare set of contacts in the relay is used for status telemetry.

For further information please refer to the ML-Series generic description available at <a href="https://www.irf.com">www.irf.com</a>.

#### **Design Methodology**

The ML-Series is developed using a proven conservative design methodology, which includes selecting radiation tolerant, and established reliability components and full derating to the requirements of EEE-INST-002 and ECSS-ST-11A.

#### **Specifications**

| Absolute Maximum Ratings |                    | Recommended Operatin         | Recommended Operating Conditions |  |  |

|--------------------------|--------------------|------------------------------|----------------------------------|--|--|

| Input voltage range      | -0.5Vdc to +120Vdc | Input voltage range (Note 9) | +97Vdc to +103Vdc                |  |  |

| Output power             | Internally limited | Output power                 | 0 to Max. Rated                  |  |  |

| Operating mounting point | -55°C to +100°C    | Operating mounting point     | -40°C to +75°C *                 |  |  |

| temperature (Note 10)    |                    | temperature (Note 9)         |                                  |  |  |

| Storage temperature      | -55°C to +125°C    | Cold start temperature       | -55°C                            |  |  |

#### **Electrical Performance Characteristics**

\* Meets full derating

|                                                                             |           | Conditions                                                                                                                               |                  | Limits         |                  |      |

|-----------------------------------------------------------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------|------------------|------|

| Parameter                                                                   | Condition | $-40^{\circ}$ C ≤ Tc ≤ $+75^{\circ}$ C<br>V <sub>IN</sub> = 100V DC $\pm$ 0.5%, C <sub>L</sub> = 0 $\mu$ F<br>unless otherwise specified | Min Nom Max      |                | Max              | Unit |

| Primary Input Voltage                                                       |           |                                                                                                                                          | 97               | 100            | 103              | V    |

| Output voltage (V <sub>OUT</sub> )<br>(O/P 1, O/P 2)                        |           | Note 1                                                                                                                                   |                  |                |                  |      |

| +6.0V<br>-5.0V                                                              | 1 1       | $0\% \le I_{OUT} \le 100\%$ of rated load                                                                                                | +5.970<br>-4.975 | +6.00<br>-5.00 | +6.030<br>-5.025 | V    |

| +6.0V<br>-5.0V                                                              | 2 2       | $0\% \le I_{OUT} \le 100\%$ of rated load                                                                                                | +5.940<br>-4.950 |                | +6.060<br>-5.050 | V    |

| +6.0V<br>-5.0V                                                              | 3         | $0\% \le I_{OUT} \le 100\%$ of rated load                                                                                                | +5.880<br>-4.900 |                | 6.120<br>5.100   | V    |

| Output power ( P <sub>OUT</sub> )<br>(O/P 1, O/P 2)<br>+6.0V<br>-5.0V       | 1,2,3     | V <sub>IN</sub> = 97, 100, 103V                                                                                                          |                  |                | 3.0<br>0.5       | W    |

| Output current ( I <sub>OUT</sub> )<br>(O/P 1, O/P 2)<br>+6.0V<br>-5.0V     | 1,2,3     | V <sub>IN</sub> = 97, 100, 103V                                                                                                          | 0                |                | 500<br>100       | mA   |

| Line regulation (VR <sub>LINE</sub> )  Each output                          | 1,2,3     | $V_{IN} = 97, 100, 103V$<br>$I_{OUT} = 10\%, 50\%, 100\%$ rated                                                                          | -1.0             |                | 1.0              | mV   |

| Load regulation (VR <sub>LOAD</sub> )  Each output                          | 1,2,3     | $I_{OUT} = 10\%$ , 50%, 100% rated $V_{IN} = 97$ , 100, 103V                                                                             | -1.0             |                | 1.0              | mV   |

| Cross regulation ( VR <sub>CROSS</sub> )                                    | 1,2,3     | V <sub>IN</sub> = 97, 100, 103V, Note 1                                                                                                  |                  |                | 1.0              | mV   |

| Input current                                                               | 1,2,3     | I <sub>OUT</sub> = 0, commanded On<br>Commanded Off                                                                                      |                  | 10             | 15<br>2.0        | mA   |

| Switching frequency (F <sub>S</sub> )                                       | 1,2,3     | Notes 1, 7                                                                                                                               | 126              | 140            | 154              | kHz  |

| Input under voltage<br>Trig level                                           | 1,2,3     | $0\% \le I_{OUT} \le 100\%$ of rated load                                                                                                | 85               |                | 95               | V    |

| Output Sequencing Turn-on delay O/P 2 to O/P 1 Turn-off delay O/P1 to O/P 2 | 1,2,3     | I <sub>OUT</sub> ≥ 20% for Output 1                                                                                                      | 2.0<br>1.0       |                | 12<br>8.0        | ms   |

#### ML1000605D (100V Input, Dual Output)

#### **Electrical Performance Characteristics** (continued)

|                                                                                |           | Conditions                                                                                                             |                  | Limits   |                    |              |

|--------------------------------------------------------------------------------|-----------|------------------------------------------------------------------------------------------------------------------------|------------------|----------|--------------------|--------------|

| Parameter                                                                      | Condition | $-40^{\circ}$ C ≤ T <sub>C</sub> ≤ +75°C<br>$V_{IN}$ = 100V DC ± 0.5%, $C_L$ = 0 $\mu$ F<br>unless otherwise specified | Min              | Nom      | Max                | Unit         |

| Output ripple (V <sub>RIP</sub> ) Each output +6.0V -5.0V                      | 1         | V <sub>IN</sub> = 97, 100, 103V<br>I <sub>OUT</sub> = 100% rated load<br>Frequency domain 100Hz – 50MHz<br>Note 1      |                  |          | 1.0<br>1.0         | mVrms        |

| +6.0V<br>-5.0V                                                                 | 1,2       | Time domain 100Hz – 50MHz<br>Notes 1, 2                                                                                |                  |          | 30<br>30           | mVpp         |

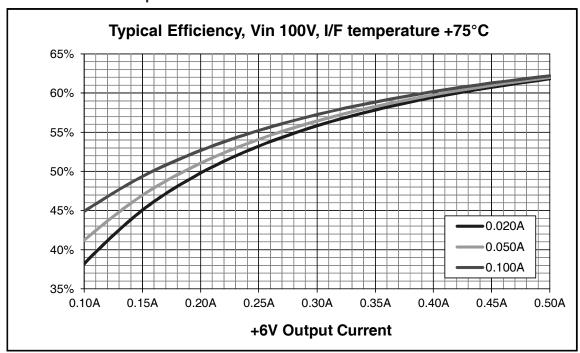

| Efficiency ( E <sub>FF</sub> ) For combined output power of 0.70W 1.75W        | 1,2,3     | $I_{OUT} = 20\%$ rated load $I_{OUT} = 50\%$ rated load                                                                | 37<br>52         | 38<br>54 |                    | %            |

| 3.50W Telecommand I/F Pulse Voltage high Pulse Voltage low Pulse duration      | 1,2,3     | I <sub>out</sub> = 100% rated load  Note 1                                                                             | +22<br>-40<br>10 | 62       | +30<br>0.5<br>1000 | V<br>V<br>ms |

| Telemetry<br>Converter On<br>Converter Off                                     | 1,2,3     |                                                                                                                        | 400<br>1.0       | 422      | 450                | ohm<br>Mohm  |

| Current Limit Point<br>Each output<br>+6.0V<br>-5.0V                           | 1,2,3     | V <sub>OUT</sub> = 100mV below Nominal                                                                                 | 550<br>110       |          | 700<br>150         | mA           |

| Output response to<br>step load changes ( V <sub>TLD</sub> )<br>+6.0V<br>-5.0V | 1,2,3     | 20% to / from 100% Load, Note 3                                                                                        | -70<br>-50       |          | 70<br>50           | mV pk        |

| Recovery time,<br>step load changes ( T <sub>TLD</sub> )<br>+6.0<br>-5.0       | 1,2,3     | 20% to / from 100% Load , Notes 3, 4                                                                                   |                  |          | 2.5<br>2.5         | ms           |

| Turn-on Response Overshoot (V <sub>OS</sub> ) +6.0V -5.0V Turn-on Delay        | 1,2,3     | 10% Load, Full Load<br>Note 5                                                                                          | 2.0              |          | 60<br>50<br>10     | mV<br>ms     |

| Capacitive Load ( C <sub>L</sub> )<br>+6.0V<br>-5.0V                           | 1         | I <sub>OUT</sub> = 100% rated load<br>No effect on DC performance<br>Notes 1, 6<br>Each output                         |                  |          | 100<br>100         | μF           |

#### **Electrical Performance Characteristics** (continued)

| Doromotor                                                   | Condition                          | Conditions<br>-40°C ≤ Tc ≤ +75°C                                                                     |                            | Limits |     | Unit  |  |

|-------------------------------------------------------------|------------------------------------|------------------------------------------------------------------------------------------------------|----------------------------|--------|-----|-------|--|

| Parameter                                                   | Condition                          | $V_{\text{IN}}$ = 100V DC ± 0.5%, $C_{\text{L}}$ = 0 $\mu$ F unless otherwise specified              | Min                        | Nom    | Max | Offit |  |

| EMC conducted susceptibility (Line rejection)               | 1                                  | I <sub>OUT</sub> = 100% rated load Primary power sine wave injection of 2Vp-p, 100Hz to 1MHz, Note 1 |                            | 110    |     | dB    |  |

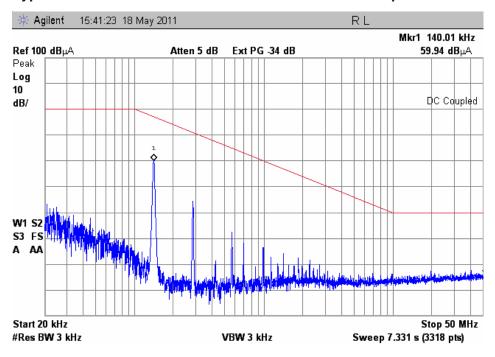

| Electromagnetic Interference (EMI), conducted emission (CE) | 1                                  | I <sub>OUT</sub> = 100% rated load, Notes 1, 7                                                       | Limits per Figures 4 and 5 |        | 5   |       |  |

| Isolation                                                   | solation 1 Inp<br>telecon<br>telei |                                                                                                      | 10                         |        |     | МΩ    |  |

| Device Weight                                               |                                    |                                                                                                      |                            |        | 50  | g     |  |

| Failure Rate                                                |                                    | MIL-HDBK-217F2, SF, 35°C, Note 8                                                                     |                            |        | 60  | FITs  |  |

#### Notes: Specification and Electrical Performance Characteristics Tables

- Parameter is tested as part of design characterization or after design changes. Thereafter, parameter shall be quaranteed to the limits specified.

- 2. Guaranteed for a D.C. to 50MHz bandwidth. Tested using a 10.7MHz bandwidth.

- 3. Load current step transition time  $\geq$  10  $\mu$ s.

- 4. Recovery time is measured from the initiation of the transient to where VouT has returned to within ±1% of its steady state value.

- 5. Turn-on delay time from application of telecommand pulse to the point where Output 2 = 98% of nominal output voltage.

- 6. Capacitive load may be any value from 0 to the maximum limit without compromising the output sequencing performance. A capacitive load in excess of the maximum limit may influence the output sequencing performance and start-up time, converter operation and dc performance will remain intact.

- 7. The switching frequency and 1st and 2nd harmonic of the input ripple is tested on every unit.

- MIL-HDBK-217F2 stress-dependent method is used with 2 exceptions: For soldering a fixed failure rate at 0.035FIT is used and for power MOSFETs the dissipated power (instead of rated power) is used for the Pr parameter. 1 FIT is 1 failure in 10<sup>9</sup> hours.

- 9. The converter meets full derating per EEE-INST-002 and ECSS-Q-30-11A with the following exception: For Schottky diode JANS1N5819 a maximum derated junction temperature of +110°C. For EEE-INST-002 it is required that ceramic capacitors with a voltage stress below 10V shall be rated for minimum 100V in the product such capacitors is rated for 50V minimum.

- 10. Although operation temperatures between -55°C to +100°C and -40°C to+75°C is guaranteed, no parameter limits are specified.

#### Electrical Performance Characteristics - Definition of Conditions

| Condition | Definition                                 | Comment                                                |

|-----------|--------------------------------------------|--------------------------------------------------------|

| 1         | BOL @ +25°C interface temperature          | Initial setting                                        |

| 2         | BOL @ -40°C to +75°C interface temperature | Initial setting and worst case temperature variation   |

| 3         | EOL @ -40°C to +75°C interface temperature | Worst case performance including initial setting,      |

|           |                                            | temperature variation, aging and radiation degradation |

#### **Model Definition and Test Plans**

#### **Model Definition**

| Model | Description                                                                                                                                | Build Standard                                                                                                                                                                                   |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EBB   | The EBB is an electrical representative model.                                                                                             | The PCB will be hand soldered by the engineering group. No staking and conformal coating is foreseen                                                                                             |

|       | The EBB is intended to be used by customers in their proto type at equipment level.  EBB models are built at IR's Danish Design Center.    | Preferably same type of EEE parts as intended for flight, but lower grade will be used for convenience. For resistors and capacitors different types with same basic characteristics may be used |

| EQM   | The EQM is an electrical and mechanical representative model.  The EQM is intended to be used by customer in their EQM at equipment level. | Flight standard for processes.  Same type of EEE parts as intended for flight, but lower grade may be used for convenience.                                                                      |

| FM    | Flight standard models.                                                                                                                    | Full flight standard                                                                                                                                                                             |

#### Test Plan - A

|          | The EBB must pass the following tests:                                                     |           |                              |  |  |  |

|----------|--------------------------------------------------------------------------------------------|-----------|------------------------------|--|--|--|

| Test No. | Type of Test                                                                               | Location* | Remarks                      |  |  |  |

| 1        | Electrical performance test,<br>room temperature incl. Limited<br>EMC test (CE 50kHz-1MHz) | IRD       | Acceptance Test Procedure    |  |  |  |

| 2        | Electrical performance test in temperature (Q-level)                                       | IRD       | Acceptance Test Procedure    |  |  |  |

| 3        | Electrical performance test,<br>room temperature incl. Limited<br>EMC test (CE 50kHz-1MHz) | IRD       | Acceptance Test Procedure    |  |  |  |

| 4        | Final Inspection                                                                           | IRD       | General inspection Procedure |  |  |  |

#### Test Plan - B

| The EQM must pass the following tests: |                                                                                      |                     |                                     |  |  |  |

|----------------------------------------|--------------------------------------------------------------------------------------|---------------------|-------------------------------------|--|--|--|

| Test No.                               | Type of Test                                                                         | Location*           | Remarks                             |  |  |  |

| 1                                      | Electrical performance test, room temperature incl. Limited EMC test (CE 50kHz-1MHz) | IRSJ                | Acceptance Test Procedure           |  |  |  |

| 2                                      | Thermal cycling with electrical monitoring of input and outputs (Q-level)            | IRSJ                | Acceptance Test Procedure 10 cycles |  |  |  |

| 3                                      | Electrical performance test in temperature (Q-level)                                 | IRSJ                | Acceptance Test Procedure           |  |  |  |

| 4                                      | Random Vibration test in (Q-level)                                                   | External test house | Vibration Test Procedure            |  |  |  |

| 5                                      | Electrical performance test, room temperature incl. Limited EMC test (CE 50kHz-1MHz) | IRSJ                | Acceptance Test Procedure           |  |  |  |

| 6                                      | Mechanical Measurements                                                              | IRSJ                | Acceptance Test Procedure           |  |  |  |

| 7                                      | Final Inspection                                                                     | IRSJ                | General inspection Procedure        |  |  |  |

#### Test Plan - C

| The FM must pass the following tests: |                                                                                      |           |                              |  |  |  |

|---------------------------------------|--------------------------------------------------------------------------------------|-----------|------------------------------|--|--|--|

| Test No.                              | Type of Test                                                                         | Location* | Remarks                      |  |  |  |

| 1                                     | Electrical performance test, room temperature incl. Limited EMC test (CE 50kHz-1MHz) | IRSJ      | Acceptance test procedure    |  |  |  |

| 2                                     | Electrical performance test in temperature (A-levels)                                | IRSJ      | Acceptance test procedure    |  |  |  |

| 3                                     | Electrical performance test, room temperature incl. Limited EMC test (CE 50kHz-1MHz) | IRSJ      | Acceptance test procedure    |  |  |  |

| 4                                     | Electrical performance test, room temperature                                        | IRSJ      | Acceptance Test Procedure    |  |  |  |

| 5                                     | Mechanical Measurements                                                              | IRSJ      | Acceptance test procedure    |  |  |  |

| 6                                     | Final Inspection                                                                     | IRSJ      | General inspection procedure |  |  |  |

#### Note:

Location\* - IRD: IR's Danish Design Center, Skovlunde, Denmark

- IRSJ: IR's Site in San Jose, California, USA

## International TOR Rectifier

#### **Radiation Performance**

#### TID

The TID radiation performance is guaranteed by worst case analysis with radiation degradation data for each radiation sensitive component used in the DC-DC converter. For TID radiation verification testing (RVT) for each wafer lot for all sensitive components is part of the EEE parts requirements per table below.

#### **TID RVT Plan Table**

| Component Type  | RVT Plan (applicable to all flight lots)                                         |

|-----------------|----------------------------------------------------------------------------------|

| JANS2N2222A     | LDRS 0.01 to 0.1 rad up to 200 krad per IR RVT plan                              |

| JANS2N2907A     | LDRS 0.01 to 0.1 rad up to 200 krad per IR RVT plan                              |

| JANSR2N7492T2   | RVT by Manufacturer (HDR)                                                        |

| IRHF57214SESCS  | RVT by Manufacturer (HDR)                                                        |

| IRHLUB770Z4SCS  | RVT by Manufacturer (HDR)                                                        |

| IRHLUB7970Z4SCS | RVT by Manufacturer (HDR)                                                        |

| LM124AWR        | RVT by Manufacturer (ELDRS)                                                      |

| IS2-1009RH      | RVT by Manufacturer (HDR)<br>LDRS 0.01 to 0.1 rad up to 100 krad per IR RVT plan |

| UC1845A         | LDRS 0.01 to 0.1 rad/s up to 100kRad per IR RVT plan                             |

#### SEE

The SEE radiation performance is guaranteed by a combination of derating and mitigation at circuit level. For mitigation at circuit level both theoretical analysis and testing with imposed SEE effects are performed. The applicable SEE and mitigation concept is presented in table below.

The maximum output perturbation is 5% of the nominal output voltage during any SEE.

#### **Applicable SEE and Mitigation Methods Table**

| Component Type    | Applicable SEE                 | Mitigation Concept                                                           |

|-------------------|--------------------------------|------------------------------------------------------------------------------|

| RH MOSFET         | SEGR                           | Vds derating in combination with SEE SOA curves from manufacturer data sheet |

| Op-Amp            | SET, 15us perturbation to rail | Mitigation at circuit level (filtering)                                      |

| Voltage reference | SET, 10us perturbation to rail | Mitigation at circuit level (filtering)                                      |

| PWM               | SET, 15us perturbation to rail | Mitigation at circuit level (filtering)                                      |

|                   | Double Pulses                  | Mitigation at circuit level (filtering, no saturation of magnetic parts)     |

|                   | Missing Pulses                 | Mitigation at circuit level (filtering, no saturation of magnetic parts)     |

#### **EEE Parts Technical Standard**

For component screening and DPA rules, refer to the generic ML-Series data sheet at www.irf.com.

#### **Random Vibration**

| Axis    | Frequency Range (Hz) | Level         | PSD Level (g <sub>rms</sub> ) | Duration (S) |

|---------|----------------------|---------------|-------------------------------|--------------|

|         | 20-100               | +6 dB/oct     |                               |              |

| X, Y, Z | 100-1600             | 0.5 SQR(g)/Hz | 29.9                          | 180          |

|         | 1600-2000            | -12 dB/oct    |                               |              |

#### Fig 1- Block Diagram

#### **Grounding and Isolation Scheme**

| Parameter Grounding & Isolation Performance |                                                                  |

|---------------------------------------------|------------------------------------------------------------------|

| Isolation:                                  |                                                                  |

| Primary to Secondary:                       | > 10 MOhm // < 50nF                                              |

| Telecommand:                                | Floating                                                         |

| Status TM:                                  | Floating                                                         |

| Grounding:                                  | Secondary return bound to chassis via multiple screw connections |

#### **Interface Schematics**

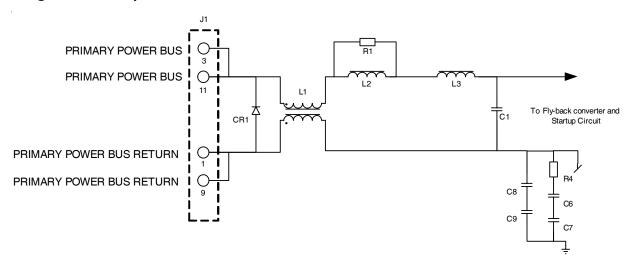

Fig 2 - Power Input:

| Component | Component Type | Package  | Value      | Voltage (V) |

|-----------|----------------|----------|------------|-------------|

| C1        | BR40 II        | RADIAL   | 0.56μF     | 200         |

| C6        | CDR33BX        | SMD 1210 | 27nF       | 100         |

| C7        | CDR33BX        | SMD 1210 | 27nF       | 100         |

| C8        | CDR33BX        | SMD 1210 | 27nF       | 100         |

| C9        | CDR33BX        | SMD 1210 | 27nF       | 100         |

| CR1       | 1N5806US       | A- MFLF  | 2.5A       | 150         |

| L1        | R6.3           | TOROID   | 2 X109.8µH |             |

| L2        | HIGH FLUX      | TOROID   | 90μΗ       |             |

| L3        | HIGH FLUX      | TOROID   | 30μΗ       |             |

| R1        | RWR81S         | RWR      | 9.09ohms   | 500         |

| R4        | RM1206B        | SMD 1206 | 21.5ohms   | 100         |

Fig 3 - TM / TC Interface:

| Component | Component Type | Package  | Value     | Voltage (V) |

|-----------|----------------|----------|-----------|-------------|

| CR201     | 1N6640US       | D-5D     | 0.3A      | 75          |

| CR202     | 1N6640US       | D-5D     | 0.3A      | 75          |

| CR203     | 1N6640US       | D-5D     | 0.3A      | 75          |

| CR204     | 1N6640US       | D-5D     | 0.3A      | 75          |

| CR205     | 1N6640US       | D-5D     | 0.3A      | 75          |

| CR206     | 1N6640US       | D-5D     | 0.3A      | 75          |

| CR207     | 1N6640US       | D-5D     | 0.3A      | 75          |

| CR208     | 1N6640US       | D-5D     | 0.3A      | 75          |

| CR213     | 1N6640US       | D-5D     | 0.3A      | 75          |

| CR204     | 1N6640US       | D-5D     | 0.3A      | 75          |

| C103      | CWR29          | SMD H    | 33μF      | 25          |

| K201      | J422-26M SHOC  | TO-5     |           | 26.5        |

| R118      | RM1206B        | SMD 1206 | 21.5kohms | 100         |

| R119      | RM1206B        | SMD 1206 | 21.5kohms | 100         |

| R120      | RM1206B        | SMD 1206 | 21.5kohms | 100         |

| R123      | RM1206B        | SMD 1206 | 21.5kohms | 100         |

| R201      | RM1206B        | SMD 1206 | 215ohms   | 100         |

| R202      | RM1206B        | SMD 1206 | 215ohms   | 100         |

| VR101     | 1N4109UR-1     | DO-213AA |           | 15          |

#### **EMI Performance**

Fig 4 - Typical Conducted Emission Performance at Power Input:

Fig 5 - Typical Conducted Emission Performance at Output 1:

#### **Power Conversion Efficiency**

Fig 6 - Typical Power Conversion Efficiency Vs +6V Output Current Parametric with -5V Output Current

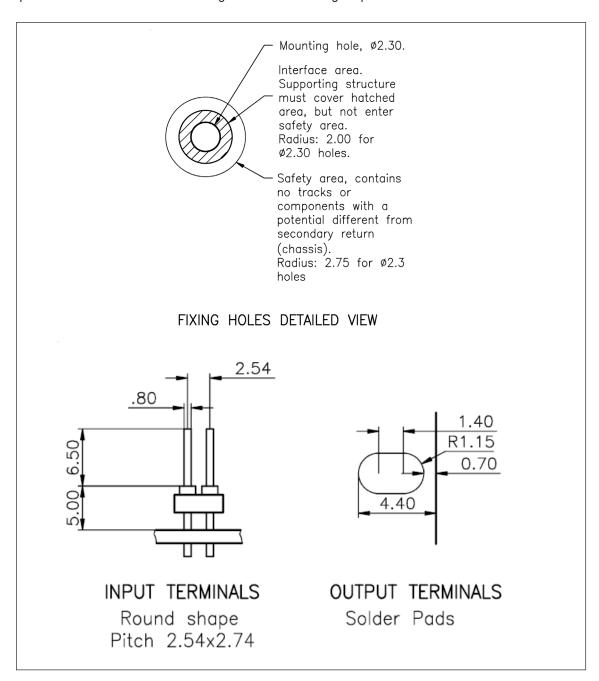

#### **Recommended Mounting Stud Design**

It is foreseen with a mounting stud design with circular mounting studs made out of aluminum with a diameter of 4.0mm and a treaded hole support mounting with M2 screws.

5pcs M2 screws are used for mounting the board. Mounting torque shall be 30Ncm ± 5.0Ncm.

#### **Mechanical Interface**

#### ML1000605D (100V Input, Dual Output)

#### **Pin Designation Tables**

| Input Terminals Assignment List                   |       |                    |  |  |

|---------------------------------------------------|-------|--------------------|--|--|

| Indent.: Input Terminals (Solder, Pins, Straight) |       |                    |  |  |

| Pin #                                             | Pin # | Function           |  |  |

|                                                   | 1     | Input Power Return |  |  |

| 9                                                 |       | Input Power Return |  |  |

|                                                   | 2     | Rerserved          |  |  |

| 10                                                |       | Rerserved          |  |  |

|                                                   | 3     | Input Power        |  |  |

| 11                                                |       | Input Power        |  |  |

|                                                   | 4     | Chasis (Ground)    |  |  |

| 12                                                |       | Voltage TM         |  |  |

|                                                   | 5     | Chasis (Ground)    |  |  |

| 13                                                |       | TC On Return       |  |  |

|                                                   | 6     | TC On              |  |  |

| 14                                                |       | TC Off Return      |  |  |

|                                                   | 7     | TC Off             |  |  |

| 15                                                |       | TM Status Return   |  |  |

|                                                   | 8     | TM Status          |  |  |

| Outpu   | Output Terminals Assignment List        |                      |  |  |

|---------|-----------------------------------------|----------------------|--|--|

| Indent. | Indent.: Output Terminals (Solder Pads) |                      |  |  |

| Pin #   | Pin # Function                          |                      |  |  |

| 1       | 2                                       | V1 (Positive Output) |  |  |

| 3       | 4                                       | Chasis (Ground)      |  |  |

| 5       | 6                                       | Chasis (Ground)      |  |  |

| 7       | 8                                       | V2 (Negative Output) |  |  |

#### **Thermal Design Information**

The thermal design for the ML-Series is solely based on heat conduction through the mounting interfaces/mounting screws into the host equipment chassis.

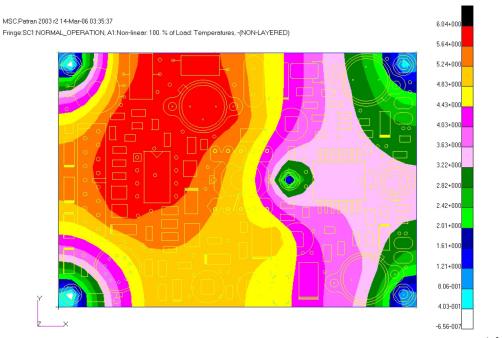

The maximum power loss during normal operation is 2.0W. The temperature profile for the board based on all screw mounting points kept at isothermal level is given below.

#### **Application Information**

#### **Standard Documentation**

- Interface Control Drawing

- User's Manual

- End Item Data Package with CoC, Applicable Configuration, MIP Photo and Test Results

#### **Design Justification Documentation**

The following documentation can be made available upon request:

- Worst Case Analysis

- Parts Stress Analysis

- Thermal Analysis

- Mechanical Analysis

- FMECA

- Reliability Assessment

- Declared Components List

- Declared Materials List

- Declared Process List

WORLD HEADQUARTERS: 101 N, Sepulveda Blvd., El Segundo, California 90245, USA Tel: (310) 252-7105

IR SAN JOSE: 2520 Junction Avenue, San Jose, California 95134, USA Tel: (408) 434-5000

IR DENMARK: Literbuen10C, DK-2740 Skovlunde, Denmark, Tel: +45 4457 5010

Visit us at www.irf.com for sales contact information.

Data and specifications subject to change without notice. 04/2013