Shipped in packet-tape reel(5000pcs/Reel)

AK8772 is ultra-small Hall effect IC of a single silicon chip composed of Hall element and a signal processing IC.

| Bipolar Hall | Supply Voltage | Power down | Ultra High               | Output | SON |  |

|--------------|----------------|------------|--------------------------|--------|-----|--|

| Effect Latch | 1.6~5.5V       | Function   | Sensitivity<br>Bop:1.8mT | CMOS   |     |  |

Notice: It is requested to read and accept "IMPORTANT NOTICE" written on the back of the front cover of this catalogue.

## Features

- $\cdot$  Precision Bipolar Hall Effect Latch

- $\cdot$  Power manageability through "PDN" pin Current consumption in Power down mode is less than 1  $\mu$ A

- Low current consumption at active mode : less than avg.  $150\mu$ A@VDD=3V

- · Ultra small SON package : 1.1×1.4×t0.37mm, Halogen free

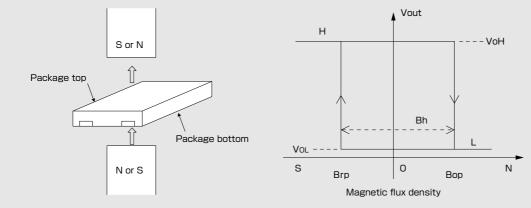

# Operational Characteristics

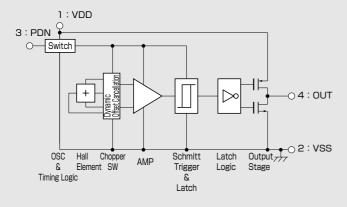

## Functional Block Diagram

| Item                                  | Function                                                                         |  |  |  |

|---------------------------------------|----------------------------------------------------------------------------------|--|--|--|

| osc                                   | Generates operating clock                                                        |  |  |  |

| Timing logic                          | Generates timing signal requires for Chopper SW, AN and COMP                     |  |  |  |

| Hall Element                          | Hall element fabricated by CMOS process                                          |  |  |  |

| Chopper SW                            | Performs chopping in order to cancel the offset voltage of Hall sensor           |  |  |  |

| AMP                                   | Reduce offset voltage and amplifies Hall output voltage                          |  |  |  |

| Schmitt Trigger Hysteresis comparator |                                                                                  |  |  |  |

| Output Stage                          | CMOS output, During the power down mode, output is latched in its previous state |  |  |  |

# **ASAHI KASEI MICRODEVICES**

•Please be aware that our products are not intended for use in life support equipment, devices, or systems. Use of our products in such applications requires the advance written approval of our sales staff. Certain applications using semiconductor devices may involve potential risks of personal injury, property damage, or loss of life. In order to minimize these risks, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards. Inclusion of our products in such applications is understood to be fully at the risk of the customer using our devices or systems.

#### Absolute Maximum Ratings

| Item                 | symbol           | Min. | Max.                  | Unit | Note    |

|----------------------|------------------|------|-----------------------|------|---------|

| Power supply voltage | V <sub>DD</sub>  | -0.3 | +6.5                  | V    |         |

| Output current       | I <sub>OUT</sub> | -0.5 | +0.5                  | mA   | OUT pin |

| Input voltage        | VIN              | -0.3 | V <sub>DD</sub> +0.3* | V    | PDN pin |

| Input current        | IIN              | -10  | +10                   | mA   | PDN pin |

| Storage temperature  | T <sub>STG</sub> | -55  | +125                  | °C   |         |

\*) Less than +6.5V.

Note) Stress beyond these listed values may cause permanent damage to the device.

#### Recommended Operating Conditions

| Item                  | symbol          | Min. | Typ. | Max. | Unit |

|-----------------------|-----------------|------|------|------|------|

| Power supply voltage  | V <sub>DD</sub> | 1.6  | 3.0  | 5.5  | V    |

| Operating temperature | T <sub>a</sub>  | -30  |      | +85  | C    |

#### Electrical Characteristics (Ta=25°C VDD=3.0V)

| Item                       | symbol           | Min.                 | Тур. | Max.   | Unit | Note                         |

|----------------------------|------------------|----------------------|------|--------|------|------------------------------|

| Current consumption 1      | I <sub>DD1</sub> |                      |      | 1      | μA   | PDN=0V                       |

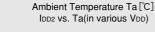

| Current consumption 2      | I <sub>DD2</sub> |                      | 60   | 150    | μA   | PDN=V <sub>DD,</sub> Average |

| PDN Input current          | I <sub>IN</sub>  | -1                   |      | 1      | μA   |                              |

| PDN input H voltage        | V <sub>IH</sub>  | 0.7V <sub>DD</sub>   |      |        | V    |                              |

| PDN input L voltage        | V <sub>IL</sub>  |                      |      | 0.3    | V    |                              |

| High Level output voltage  | V <sub>OH</sub>  | V <sub>DD</sub> -0.4 |      |        | V    | I <sub>out</sub> =-0.5mA     |

| Low level output voltage   | V <sub>OL</sub>  |                      |      | 0.4    | V    | I <sub>out</sub> =+0.5mA     |

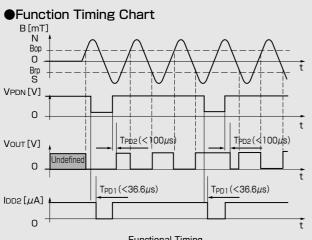

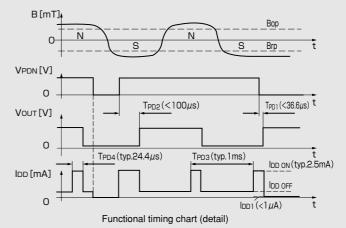

| PDN mode transition time 1 | T <sub>PD1</sub> |                      |      | (36.6) | μs   | *Active→PDN                  |

| PDN mode transition time 2 | T <sub>PD2</sub> |                      |      | 100    | μs   | PDN→Active                   |

| Pulse drive period         | T <sub>PD3</sub> | 0.5                  | 1.0  | 1.5    | ms   | When $PDN = V_{DD}$          |

| Pulse drive time           | T <sub>PD4</sub> | 12.2                 | 24.4 | 36.6   | μs   |                              |

| PDN 'H' input pulse width  | Tw               | 100                  |      |        | μS   |                              |

\*)This transition time is not guaranteed by inspection because PDN input timing and internal timing are asynchronous

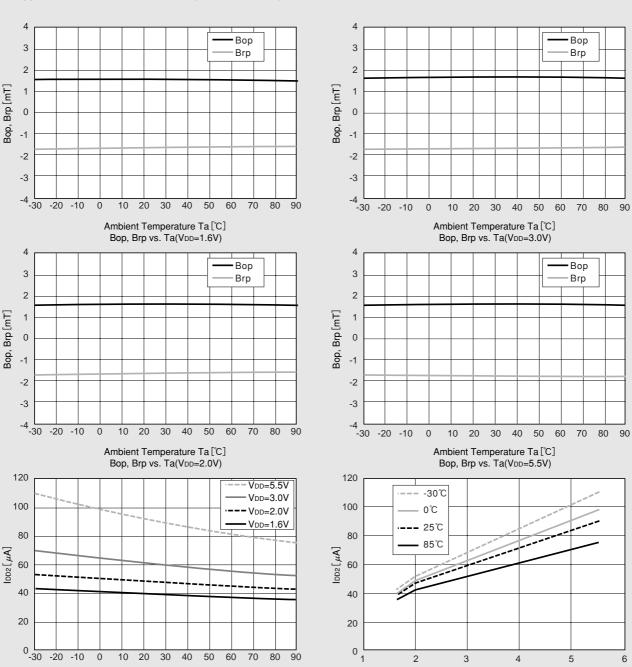

### ●Magnetic Characteristics① (Ta=25℃ VDD=3.0V)

| Item            | symbol          | Min. | Тур. | Max. | Unit |

|-----------------|-----------------|------|------|------|------|

| Operating point | B <sub>op</sub> |      | 1.8  | 4.0  | mT   |

| Releasing point | B <sub>rp</sub> | -4.0 | -1.8 |      | mT   |

| Hysteresis      | B <sub>h</sub>  |      | 3.6  |      | mT   |

## ●Magnetic Characteristics② (Ta=-30°C~85°C VDD=1.6~5.5V)

| Item            | symbol          | Min. | Тур. | Max. | Unit |

|-----------------|-----------------|------|------|------|------|

| Operating point | B <sub>op</sub> |      | 1.8  | 4.2  | mT   |

| Releasing point | B <sub>rp</sub> | -4.2 | -1.8 |      | mT   |

| Hysteresis      | B <sub>h</sub>  |      | 3.6  |      | mT   |

Note) The specifications in Magnetic Characteristics (2) are design targets.

С

n

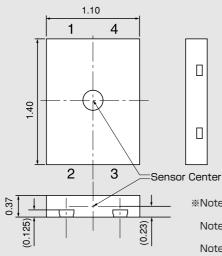

## Package (Unit:mm)

\*\*Note 1) Sensitive area position referenced to the center of package within  $\phi$ O.3mm circle.

Note 2) Tolerances of dimension otherwise noted is  $\pm 0.05 \text{mm.}$

Note 3) Hatched area is plated.

Note 4) Center pad area (TAB) should be tied to the VSS or floating

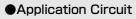

| No. | Pin name | Function            | Note                            |

|-----|----------|---------------------|---------------------------------|

| 1   | VDD      | Power supply pin    |                                 |

| 2   | VSS      | Ground pin          |                                 |

| 3   | PDN      | Power down pin.     | CMOS Input. This pin has to be  |

|     |          | H:Device active     | tied to "H" level when external |

|     |          | L:Device power down | power control is not used.      |

| 4   | OUT      | Output pin          | CMOS Output                     |

Functional Timing

Note1) During power down mode, output is latched in its previous state.

Note2) When VDD is supplied, the time from reaching VDD= 1.6V to the update of the output state is equal to TPD2. When PDN pin set to 'L' from 'H' during sampling is performing, the device transits to power down mode after sampling is completed. And when PDN pin set to 'L' from 'H' while sampling is not performing, the device transits to power down mode immediately.

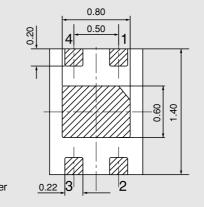

## Footprint (for reference)

$0.35^{\pm 0.10}$

0.22<sup>±0.05</sup>

0.80

1.70

0.60

$0.50^{\pm 0.05}$

21

•Typical Characteristic Data (for reference)

g

k

0 р

n

6

VDD [V]

IDD2 vs.VDD Ta(in various Ta)

## **IMPORTANT NOTICE** -

- These products and their specifications are subject to change without notice. When you consider any use or application of these products, please make inquiries the sales office of Asahi Kasei Microdevices Corporation (AKM) or authorized distributors as to current status of the products.

- Descriptions of external circuits, application circuits, software and other related information contained in this document are provided only to illustrate the operation and application examples of the semiconductor products. You are fully responsible for the incorporation of these external circuits, application circuits, software and other related information in the design of your equipments. AKM assumes no responsibility for any losses incurred by you or third parties arising from the use of these information herein. AKM assumes no liability for infringement of any patent, intellectual property, or other rights in the application or use of such information contained herein.

- Any export of these products, or devices or systems containing them, may require an export license or other official approval under the law and regulations of the country of export pertaining to customs and tariffs, currency exchange, or strategic materials.

- AKM products are neither intended nor authorized for use as critical components<sub>Note1</sub> in any safety, life support, or other hazard related device or system<sub>Note2</sub>, and AKM assumes no responsibility for such use, except for the use approved with the express written consent by Representative Director of AKM. As used here:

Note1) A critical component is one whose failure to function or perform may reasonably be expected to result, whether directly or indirectly, in the loss of the safety or effectiveness of the device or system containing it, and which must therefore meet very high standards of performance and reliability.

reliability. Note2) A hazard related device or system is one designed or intended for life support or maintenance of safety or for applications in medicine, aerospace, nuclear energy, or other fields, in which its failure to function or perform may reasonably be expected to result in loss of life or in significant injury or damage to person or property.

It is the responsibility of the buyer or distributor of AKM products, who distributes, disposes of, or otherwise places the product with a third party, to notify such third party in advance of the above content and conditions, and the buyer or distributor agrees to assume any and all responsibility and liability for and hold AKM harmless from any and all claims arising from the use of said product in the absence of such notification.