# THIS DOCUMENT IS FOR MAINTENANCE PURPOSES ONLY AND IS NOT RECOMMENDED FOR NEW DESIGNS

DS2177-2.1

### MV95408 50MHz 8-BIT CMOS VIDEO DAC

The MV95408 is a CMOS 8-bit, 50MHz Digital to Analog converter, designed for use in both video graphics and general digital television applications.

A very low external component count has been achieved by including the loop amplifier and reference voltage source on chip.

The device contains a data input register and registered video controls (BLANK, REFWHITE, OVERBRT and SYNC). These control inputs and associated internal circuitry allows the MV95408 to be used in video graphics systems by providing the necessary video pedestal levels. The STRDAC input allows the video pedestals to be disabled in conventional DAC applications.

This device is capable of directly driving 75 $\Omega$  lines with standard RS-343A or RS-170 video levels, using the appropriate R<sub>SFT</sub> external resistor.

Pull up resistors have been added to tie all unused control inputs into their inactive (High) states.

#### **FEATURES**

- Low Power Consumption (180mW Typ)

- 50MHz Pipeline Operation

- ±1 LSB Differential Linearity Error

- ±1 LSB Integral Linearity Error

- RS-343A/RS-170 Compatible Levels

- On Chip Reference Voltage Source

- Guaranteed Monotonic

- Drives  $75\Omega$  Loads Directly

- Single 5V Power Supply

#### ORDERING INFORMATION

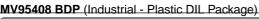

Fig.1 Pin connections - top view

#### **APPLICATIONS**

- Data Conversion (general)

- Computer Graphics

- Waveform Synthesis

- Commercial TV

- Instrumentation

#### **ABSOLUTE MAXIMUM RATINGS** (Reference to GND)

DC Supply Voltage, V<sub>DD</sub>

Digital Input Voltage

Analog Output Short Circuit Duration

Ambient Operating Temperature

Storage Temperature Range

-0.3 to +7V

-0.3 to V<sub>DD</sub> +0.3V

Indefinite

-40°C to +85°C

-55°C to +125°C

#### MV95408

#### **ELECTRICAL CHARACTERISTICS**

These characteristics are guaranteed over the following conditions (unless otherwise stated):

As specified in recommended operating conditions. Full temperature range = -40°C to +85°C

DC CHARACTERISTICS

| Parameter                                      | Symbol           | Temp<br>(°C) | Min.    | Value<br>Typ.    | Max.                 | Units             | Conditions                                               |

|------------------------------------------------|------------------|--------------|---------|------------------|----------------------|-------------------|----------------------------------------------------------|

| Resolution                                     |                  | Full         | 8       |                  |                      | Bits              |                                                          |

| Integral linearity error                       | INL              | 25<br>Full   |         | ±0.5             | ±1                   | LSB<br>LSB        |                                                          |

| Differential linearity error                   | DNL              | 25<br>Full   |         | ±0.5             | ±1                   | LSB<br>LSB        |                                                          |

| Gain error                                     |                  | 25           |         | ±1%              | ±5%                  | %                 | Of full scale                                            |

| Analog output                                  |                  |              |         |                  |                      |                   |                                                          |

| Grey scale current range                       |                  | 25           |         | 8.8              |                      | mA                |                                                          |

| 10% Over Bright level relative to White level  |                  | 25           | 26      | 255<br>27<br>10  | 28                   | LSB<br>LSB<br>IRE |                                                          |

| White level relative to Blank level            |                  | 25           | 275     | 276              | 277                  | LSB               |                                                          |

| Black level relative to Blank level            |                  | 25           | 20      | 100<br>21<br>7.5 | 22                   | IRE<br>LSB<br>IRE | $75\Omega$ singly terminated load $R_{SET} = 1.8k\Omega$ |

| White level relative to Black level            |                  | 25           |         | 255<br>92.5      |                      | LSB<br>IRE        | (graphics mode)                                          |

| Blank level                                    |                  | 25           | 107     | 111<br>40        | 115                  | LSB<br>IRE        |                                                          |

| Sync level                                     |                  | 25           |         | 0                |                      | LSB               |                                                          |

| LSB size                                       | LSB              | 25           |         | 2.58             |                      | mV                |                                                          |

| Output compliance                              | V <sub>oc</sub>  | 25           | -0.3    |                  | +1.5                 | V                 |                                                          |

| Digital inputs                                 |                  |              |         |                  |                      |                   |                                                          |

| High level I/P voltage                         | $V_{IH}$         | 25           | 3       |                  | V <sub>DD</sub> +0.3 | V                 |                                                          |

| Low level I/P voltage                          | V <sub>IL</sub>  | 25           | GND-0.3 |                  | 1.2                  | V                 |                                                          |

| High level I/P current                         | I <sub>IH</sub>  | 25           |         |                  | +1                   | μΑ                |                                                          |

| Low level I/P current                          | I <sub>IL</sub>  | 25           |         |                  | -1                   | μΑ                |                                                          |

| Internal voltage reference (V <sub>REF</sub> ) | V <sub>REF</sub> | 25           | 0.95    | 1.0              | 1.05                 | V                 |                                                          |

| V <sub>RFF</sub> temperature coefficient       |                  | Full         | 0.90    | 40               | 1.10                 | V<br>ppm/°C       |                                                          |

| VREF temperature coemicient                    |                  |              |         | +0               |                      | ppiii/ C          |                                                          |

### AC CHARACTERISTICS (Refer to Fig. 3)

| Parameter                      | Symbol            | Temp<br>(°C) | Min. | Value<br>Typ. | Max. | Units    | Conditions                  |

|--------------------------------|-------------------|--------------|------|---------------|------|----------|-----------------------------|

| Max clock rate                 | f <sub>MAX</sub>  | Full         | 50   |               |      | MHz      | maximum<br>guaranteed freq. |

| Clock high time                | t <sub>CLKH</sub> | 25           | 7    |               |      | ns       |                             |

| Clock low time                 | t <sub>CLKL</sub> | 25           | 7    |               |      | ns       |                             |

| Data and control setup time    | t <sub>SU</sub>   | 25           | 6    |               |      | ns       |                             |

| Data and control hold time     | t <sub>H</sub>    | 25           | 2    |               |      | ns       |                             |

| Analog output delay            | t <sub>DLY</sub>  | 25           |      | 10            |      | ns       |                             |

| Analog output rise/fall time   | t <sub>RF</sub>   | 25           |      | 3             | 6    | ns       |                             |

| Analog output settling time    | t <sub>S</sub>    | 25           |      | 15            |      | ns       |                             |

| Glitch energy                  |                   | 25           |      | 100           |      | pV-sec   |                             |

| V <sub>DD</sub> supply current | IDD               | 25           |      | 30<br>42      |      | mA<br>mA | fc = 15MHz<br>fc = 50MHz    |

| THERMAL CHARACTERISTICS       |    |    |      |  |  |  |  |  |

|-------------------------------|----|----|------|--|--|--|--|--|

| Thermal Resistance            | DP | MP |      |  |  |  |  |  |

| Chip to case $\theta_{jC}$    | 20 | 30 | °C/W |  |  |  |  |  |

| Chip to ambient $\theta_{iA}$ | 75 | 93 | °C/W |  |  |  |  |  |

| COMMENDED OPERATING CONDITI                                | UNS             |

|------------------------------------------------------------|-----------------|

| R <sub>LOAD</sub> (I <sub>OUT</sub> and I <sub>OUT</sub> ) | 75Ω             |

| V <sub>DD</sub>                                            | $5.0V \pm 0.5V$ |

| R <sub>SFT</sub> (graphics applications)                   | 1.8kΩ           |

| R <sub>SET</sub> (straight DAC applications)               | 1.2kΩ           |

#### **CIRCUIT DESCRIPTION**

As illustrated in the function block diagram, Fig. 2, the MV95408 contains an 8-bit D-to-A converter, input registers, a loop amplifier and voltage reference.

On the falling edge of each clock cycle, as shown in Fig. 3, eight data bits are latched into the device and passed to the 8-bit D-to-A converter. Also latched on the falling edge of the clock signal, the SYNC and BLANK inputs add the necessary weighted currents to the analog outputs to produce the required output levels for use in video applications. Table 1 details how the SYNC, BLANK, REFWHITE and OVERBRT inputs modify the DAC output levels.

To obtain a high data throughput rate, the decoding logic of the MV95408 is fully pipelined. This introduces a one clock cycle delay between the latching of the input data and the resultant DAC output.

It also ensures synchronisation of the internal data and a minimal output glitch energy.

The DAC employed by the MV95408 eliminates the need for precision component ratios by using a segmented architecture in which equal weight bit currents are either routed to  $I_{OUT}$  or  $\overline{I_{OUT}}$ . The use of identical current sources and current steering their outputs means that monotonicity is guaranteed.

The MV95408 eliminates the need for an external voltage reference by providing a nominally 1.0V reference on chip. An on-chip loop amplifier also provides stability of the full scale output current against power supply and temperature variations. The full scale output current is set by an external resistor  $R_{\mbox{\footnotesize SET}}$ . By adjustment of this value it is possible to implement RS-343A or RS-170 video levels as explained in the application notes.

Fig.3 Timing diagram

| Description    | STRDAC | SYNC | BLANK | REFWHITE | OVERBRT | OUTPUT<br>DATA | I <sub>OUT</sub><br>(LSB) |

|----------------|--------|------|-------|----------|---------|----------------|---------------------------|

| REFWHITE + 10% | 1      | 1    | 1     | 0        | 0       | Х              | 414                       |

| REFWHITE       | 1      | 1    | 1     | 0        | 1       | Х              | 387                       |

| FULL WHITE     | 1      | 1    | 1     | 1        | 1       | \$FF           | 387                       |

| OVERBRIGHT     | 1      | 1    | 1     | 1        | 0       | DATA           | DATA +<br>132 + 27        |

| FULL BLACK     | 1      | 1    | 1     | 1        | 1       | \$00           | 132                       |

| BLANK          | 1      | 1    | 0     | Х        | Х       | Х              | 111                       |

| DATA-SYNC      | 1      | 0    | 1     | 1        | 1       | DATA           | DATA + 21                 |

| SYNC           | 1      | 0    | 0     | Х        | Х       | Х              | 0                         |

| STRDAC MODE    | 0      | Х    | 1     | 1        | Х       | DATA           | DATA                      |

Table 1: Video output truth table

### MV95408

| Pin   | Name                                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2     | CLK                                 | The clock input. The falling edge of the clock latches the DATA, BLANK, SYNC, OVERBRT and REFWHITE inputs into the logic pipeline. The decoded data will be latched into the DAC output 1 clock cycle later. The clock frequency determines the update rate of the DAC output.                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 3-10  | D <sub>7</sub> -D <sub>0</sub>      | The data inputs. D <sub>0</sub> is the least significant bit (LSB). The coding is in straight binary only.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 13,15 | I <sub>OUT</sub> , I <sub>OUT</sub> | The current output and its complement. These are the high impedance current source outputs of the DAC capable of driving a 75 $\Omega$ load up to a voltage of 1.5V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 14    | GND                                 | Analog ground for the DAC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 20    | V <sub>DD</sub>                     | Analog power for the DAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 11    | V <sub>REF</sub>                    | The output of the internal voltage reference generator. This output is nominally 1V, and should be decoupled with a 10nF capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 12    | R <sub>SET</sub>                    | The full scale adjust control. The R <sub>SET</sub> resistor is connected from this pin to ground. An internal loop amplifier adjusts a reference current flowing through the R <sub>SET</sub> resistor so that the voltage across the resistor is equal to the V <sub>REF</sub> voltage. This reference current has a weighting equal to 16 LSB's.                                                                                                                                                                                                                                                                                                                                             |

| 1     | BLANK                               | The composite blank control input. A logical zero on this input removes the Black pedestal from the I <sub>OUT</sub> output, whilst forcing the internal data to the DAC to \$00. This input is latched on the clock falling edge and will override the REFWHITE and OVERBRT inputs. The Black pedestal is 7.5 IRE units (actually 21 LSB's). If left open circuit this input is internally tied high.                                                                                                                                                                                                                                                                                          |

| 17    | SYNC                                | The composite sync control input. A logical zero on this input removes the Blank pedestal from the I <sub>OUT</sub> output. The Blank pedestal is nominally 40 IRE units (actually 111 LSB's). The SYNC input does not override any other control lines. This input is latched on the clock falling edge. If left open circuit this input is internally tied high.                                                                                                                                                                                                                                                                                                                              |

| 19    | REFWHITE                            | The reference white level control input. A logical zero on this input overrides the input data, forcing the data to \$FF. The BLANK input will override this input. If left open circuit this input is internally tied high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 18    | OVERBRT                             | The 10% overbright control input. A logical zero on this input switches the Overbright pedestal into the I <sub>OUT</sub> output. The Overbright pedestal is 10 IRE units (actually 27 LSB's). This input does not override any other input. The BLANK input overrides this input. If left open circuit this input is internally tied high.                                                                                                                                                                                                                                                                                                                                                     |

| 16    | STRDAC                              | The straight DAC control input. A logical zero on this input causes the Black, Blank and Overbright pedestals to be disabled, removing them from both $I_{OUT}$ and $I_{\overline{OUT}}$ . This allows the DAC contribution to the output to be extended to a full 1 Volt. To obtain this extra DAC range, it is necessary to reduce the $R_{SET}$ resistor value, see application notes. The $\overline{BLANK}$ the $\overline{REFWHITE}$ inputs may still be used to force the input data to \$00 or \$FF respectively. With the $\overline{STRDAC}$ pin held low the output current can be calculated from:  Output current = Data x 1 LSB  Where 1 LSB= $\frac{V_{REF}}{16 \times R_{SET}}$ |

|       |                                     | Full scale = 255 LSB $V_{REF} = 1.0V$ typ.  The exact value of 1 LSB must be calculated from the full scale output. If left open circuit this input is internally tied high and the device will be configured for video graphics. In this mode the output current can be calculated from:  Output current = (DATA + 21 + 111) x 1 LSB $V_{REF} = 1.0V$ typ.                                                                                                                                                                                                                                                                                                                                     |

#### **APPLICATIONS INFORMATION**

#### RS-343A and RS-170 Video Generation

For generation of RS-343A compatible video levels (see Fig.4) it is recommended that a singly terminated 75 $\Omega$  load be used with an  $R_{SET}$  resistor value of approximately 1.82k $\Omega$

Similarly for the generation of RS-170 video levels a singly terminated 75 $\Omega$  load should be used but in association with an R<sub>SET</sub> value of approximately 1.29k $\Omega$  to provide the increased voltage range.

#### **Non-Video Applications**

The MV95408 may be used in non-video applications as explained in the pin description for  $\overline{\text{STRDAC}}$  mode.The relationship between  $R_{\text{SET}}$  and the full scale output current has been explained previously and for a singly terminated 75 $\Omega$  load an  $R_{\text{SET}}$  resistor value of approximately 1.19k $\Omega$  should be used.

#### **PCB LAYOUT CONSIDERATIONS**

The PCB layout should provide low noise on the MV95408 power and ground lines by shielding the digital inputs and providing adequate decoupling. The PCB should utilise both power and ground planes for best performance, connecting both planes to their respective regular PCB planes through a ferrite bead located as close as possible to the device. For best performance, a 100nF capacitor should be used to decouple the reference and supply pins. Decoupling should take place as close to the device as possible to reduce lead inductance. The digital inputs to the device should be isolated as much as possible from the analog outputs and other analog circuitry and should not overlay the analog ground and power planes.

To reduce noise pick-up, long clock lines to the device should be avoided. For best performance the analog output should have a  $75\Omega$  load connected to analog ground.

Fig.4 Composite video output waveform

Fig.5 Applications/test board

## HEADQUARTERS OPERATIONS GEC PLESSEY SEMICONDUCTORS

Cheney Manor, Swindon, Wiltshire, United Kingdom. SN2 2QW

Tel: (01793) 518000 Fax: (01793) 518411

#### GEC PLESSEY SEMICONDUCTORS

P.O. Box 660017, 1500 Green Hills Road, Scotts Valley, California 95067-0017, United States of America. Tel (408) 438 2900 Fax: (408) 438 5576

#### CUSTOMER SERVICE CENTRES

- FRANCE & BENELUX Les Ulis Cedex Tel: (1) 64 46 23 45 Fax: (1) 64 46 06 07

- GERMANY Munich Tel: (089) 3609 06-0 Fax: (089) 3609 06-55

- ITALY Milan Tel: (02) 66040867 Fax: (02)66040993

- JAPAN Tokyo Tel: (03) 5276-5501 Fax: (03) 5276-5510

- NORTH AMERICA Scotts Valley, USA Tel: (408) 438 2900 Fax: (408) 438 7023

- SOUTH EAST ASIA Singapore Tel: (65) 3827708 Fax: (65) 3828872

- SWEDEN Stockholm Tel: 46 8 702 97 70 Fax: 46 8 640 47 36

- •TAIWAN, ROC Taipei Tel: 886 2 5461260 Fax: 886 2 7190260

- UK, EIRE, DENMARK, FINLAND & NORWAY

Swindon Tel: (01793) 518510 Fax: (01793) 518582

These are supported by Agents and Distributors in major countries world-wide.

© GEC Plessey Semiconductors 1994 Publication No.DS2177 Issue No. 2.1 July 1994

TECHNICAL DOCUMENTATION - NOT FOR RESALE. PRINTED IN UNITED KINGDOM

This publication is issued to provide information only which (unless agreed by the Company in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. The Company reserves the right to alter without prior knowledge the specification, design or price of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to the Company's conditions of sale, which are available on request.

# For more information about all Zarlink products visit our Web Site at www.zarlink.com

Information relating to products and services furnished herein by Zarlink Semiconductor Inc. trading as Zarlink Semiconductor or its subsidiaries (collectively "Zarlink") is believed to be reliable. However, Zarlink assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Zarlink or licensed from third parties by Zarlink, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Zarlink, or non-Zarlink furnished goods or services may infringe patents or other intellectual property rights owned by Zarlink.

This publication is issued to provide information only and (unless agreed by Zarlink in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Zarlink without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Zarlink's conditions of sale which are available on request.

Purchase of Zarlink s  $I^2C$  components conveys a licence under the Philips  $I^2C$  Patent rights to use these components in and  $I^2C$  System, provided that the system conforms to the  $I^2C$  Standard Specification as defined by Philips.

Zarlink and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc.

Copyright 2001, Zarlink Semiconductor Inc. All Rights Reserved.

TECHNICAL DOCUMENTATION - NOT FOR RESALE