# 4-BIT SHIFT REGISTER WITH 3-STATE OUTPUTS

- FULLY SYNCHRONOUS SERIAL OR PARAL-LEL DATA TRANSFERS

- NEGATIVE EDGE-TRIGGERED CLOCK INPUT

- PARALLEL ENABLE MODE CONTROL INPUT

- 3-STATE BUSSABLE OUTPUT BUFFERS

- INPUT CLAMP DIODES LIMIT HIGH SPEED TERMINATION EFFECTS

#### DESCRIPTION

The T74LS295A is a 4-Bit Shift Register with serial and parallel synchronous operating modes, independent 3-state output buffers. The Parallel Enable input (PE) controls the shift-right or parallel load operation. All data transfer and shifting occur synchronously with the HIGH to LOW clock transition.

The 3-State output buffers are controlled by an active HIGH Output Enable input (EO).

Disabling the output buffers does not affect the shifting or loading of input data, but it does inhibit serial expansion.

The LS295A is fabricated with the Schottky barrier diode process for high speed and is completely compatible with all TTL families.

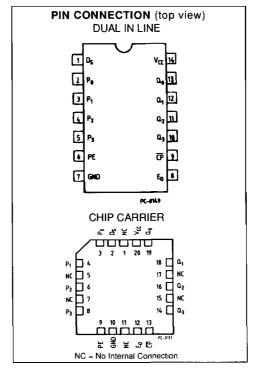

### **PIN NAMES**

| PE                             | PARALLEL ENABLE INPUT   |

|--------------------------------|-------------------------|

| Ds                             | SERIAL DATA INPUT       |

| P <sub>0</sub> -P <sub>3</sub> | PARALLEL DATA INPUTS    |

| L E₀                           | OUTPUT ENABLE INPUT     |

| CP                             | CLOCK PULSE (active LOW |

|                                | going edge) INPUT       |

| Q <sub>0</sub> -Q <sub>3</sub> | 3-STATE OUTPUTS         |

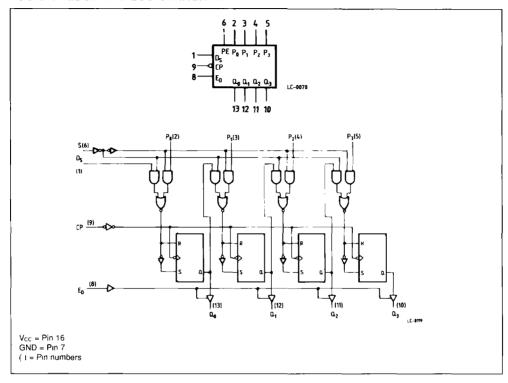

## LOGIC SYMBOL AND LOGIC DIAGRAM

## **ABSOLUTE MAXIMUM RATINGS**

| Symbol | Parameter                         | Value       | Unit |

|--------|-----------------------------------|-------------|------|

| Vcc    | Supply Voltage                    | - 0.5 to 7  | V    |

| Vı     | Input Voltage, Applied to Input   | - 0.5 to 15 | V    |

| Vo     | Output Voltage, Applied to Output | - 0.5 to 10 | V    |

| 1,     | Input Current, Into Inputs        | - 0.5 to 30 | mA   |

| lo     | Output Current, Into Outputs      | 60          | mA   |

Stresses in excess of those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions in excess of those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **GUARANTEED OPERATING RANGE**

| Part Numbers | Sup    | ply Volt | age    | Temperature     |

|--------------|--------|----------|--------|-----------------|

| Turt Numbers | Min.   | Тур.     | Max.   | - Tomperature   |

| T74LS295AXX  | 4.75 V | 5.0 V    | 5.25 V | 0 °C to + 70 °C |

XX = Package type

### TRUTH TABLE - PRESENT OUTPUT STATES AND MODE SELECTION

| MODE SELECT — TRUTH TABLE |    |     |     |    |          |                |                |                |  |  |

|---------------------------|----|-----|-----|----|----------|----------------|----------------|----------------|--|--|

| OPERATING                 |    | INP | UTS |    | OUTPUTS* |                |                |                |  |  |

| MODE                      | PΕ | CP  | Ds  | Pn | Qo       | $\mathbf{Q}_1$ | Q <sub>2</sub> | Q <sub>3</sub> |  |  |

| Shift Right               | 1  | ユ   | П   | Х  | L        | <b>q</b> 0     | q <sub>1</sub> | q <sub>2</sub> |  |  |

|                           |    | ᄀ   | h   | Х  | Н        | ٩o             | q <sub>1</sub> | $q_2$          |  |  |

|                           | Ι. | _   |     | _  | l _      | _              | _              | _              |  |  |

The indicated data appears at the Q outputs when Eo is HIGH. the outures are all forced to the high impedance "off" state.

Pn (Qn) = Lower case letters indicate the state of the referenced input (or output) one set-up time prior to the HIGH to LOW clock

Parallel Load  $\mid h \mid \neg L \mid X \mid P_n \mid P_0 \quad P_1 \quad P_2 \quad P_3 \mid I = LOW \ Voltage \ Level one set-up time prior to the HIGH to LOW Parallel Load <math>\mid h \mid \neg L \mid X \mid P_n \mid P_0 \quad P_1 \quad P_2 \quad P_3 \mid I = LOW \ Voltage \ Level one set-up time prior to the HIGH to LOW Parallel Load <math>\mid h \mid \neg L \mid X \mid P_n \mid P_0 \quad P_1 \quad P_2 \quad P_3 \mid I = LOW \ Voltage \ Level one set-up time prior to the HIGH to LOW Parallel Load <math>\mid h \mid \neg L \mid X \mid P_n \mid P_0 \quad P_1 \quad P_2 \quad P_3 \mid I = LOW \ Voltage \ Level one set-up time prior to the HIGH to LOW Parallel Load <math>\mid h \mid \neg L \mid X \mid P_n \mid P_0 \quad P_1 \quad P_2 \quad P_3 \mid I = LOW \ Voltage \ Level one set-up time prior to the HIGH to LOW Parallel Load <math>\mid h \mid \neg L \mid X \mid P_n \mid P_0 \quad P_1 \quad P_2 \quad P_3 \mid I = LOW \ Voltage \ Level one set-up time prior to the HIGH to LOW Parallel Load Par$ clock transition.

#### **FUNCTIONAL DESCRIPTION**

The LS295A is a 4-Bit Shift Register with serial and parallel synchronous operating modes. It has a Serial (Ds) and four Parallel Data outputs (Po-P3) inputs and four parallel 3-State output buffers (Qo-Q3). When the parallel Enable (PE) input is HIGH, data is transferred from the Parallel Data Inputs (Po-Pa) into the register synchronously with the HIGH to LOW transition of the Clock (CP). When the PE is LOW, a HIGH to LOW transition on the clock transfers the serial data on the Ds input to register  $Q_0$ , and shifts data from  $Q_0$  to  $Q_1$ ,  $Q_1$  to  $Q_2$  and  $Q_2$  to  $Q_3$ . The input data and parallel enable are fully edge-triggered and must be stable only one set-up time before the HIGH to LOW clock transition.

The 3-State Output buffers are controlled by an active HIGH Output Enable input (E<sub>0</sub>). When the E<sub>0</sub> is HIGH, the four register outputs appear at the Qn-Q3 outputs. When Eo is LOW, the outputs are forced to high impedance "off" state. The 3-State output buffers are completely independent of the register operation, i.e. the input transition on the E<sub>0</sub> input do not affect the serial or parallel data transfers of the register. If the outputs are tied together, all but one devices must be in the high impedance state to avoid high currents that would exceed the maximum rating.

Designers should ensure that Output Enable signals to 3-State devices whose outputs are tied together are designed so there is no overlap.

X = Don't Care

L = LOW Voltage Level

H = HIGH Voltage Level

When Eo is LOW, the indicated data is loaded into the register, but h = HIGH Voltage Level one set-up time prior to the HIGH to LOW

### DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE

| Symbol          | Parameter                             | L    | Limits   |           | Test Condition<br>(note 1)                                                                                                |                                                                         | Unit     |

|-----------------|---------------------------------------|------|----------|-----------|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|----------|

| Syllibol        | Parameter                             | Min. | Typ. (*) | Max.      |                                                                                                                           |                                                                         |          |

| V <sub>IH</sub> | Input HIGH Voltage                    | 2.0  |          |           | Guaranteed Input HIGH Voltage for All Inputs                                                                              |                                                                         | ٧        |

| ViL             | Input LOW Voltage                     |      |          | 0.8       | Guaranteed Input LOW Voltage for All Inputs                                                                               |                                                                         | V        |

| $V_{CD}$        | Input Clamp Diode Voltage             |      | - 0.65   | - 1.5     | V <sub>CC</sub> = MIN, I <sub>IN</sub>                                                                                    | = -18 mA                                                                | V        |

| $V_{OH}$        | Output HIGH Voltage                   | 2.4  | 3.4      |           | V <sub>CC</sub> = MIN, I <sub>OH</sub> = - 2.6 mA<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> per Truth Table |                                                                         | V        |

| $V_{OL}$        | Output LOW Voltage                    |      | 0.25     | 0.4       | I <sub>OL</sub> = 4 mA                                                                                                    | ,                                                                       | v        |

|                 |                                       |      | 0.35     | 0.5       | I <sub>OL</sub> = 8 mA                                                                                                    | V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub><br>per Truth Table | ٧        |

| lozh            | Output Off Current HIGH               |      |          | 20        | V <sub>CC</sub> = MAX, V <sub>OUT</sub> = 2.7 V                                                                           |                                                                         | μА       |

| lozL            | Output Off Current LOW                |      |          | - 20      | V <sub>CC</sub> = MAX, V                                                                                                  | <sub>IN</sub> = 0.5 V                                                   | μА       |

| I <sub>IH</sub> | Input HIGH Current                    |      |          | 20<br>0.1 | $V_{CC} = MAX$ , $V_{IN} = 2.7 \text{ V}$<br>$V_{CC} = MAX$ , $V_{IN} = 7.0 \text{ V}$                                    |                                                                         | μA<br>mA |

| lıL             | Input LOW Current                     |      |          | - 0.4     | V <sub>CC</sub> = MAX, V                                                                                                  | mA                                                                      |          |

| los             | Output Short Circuit Current (note 2) | - 20 |          | - 100     | V <sub>CC</sub> = MAX, V <sub>OUT</sub> = 0 V                                                                             |                                                                         | mA       |

| lcc             | Power Supply Current<br>Output HIGH   |      | 14       | 23        | V <sub>CC</sub> = MAX, V <sub>CP</sub> =<br>V <sub>E</sub> = 4.5 V                                                        |                                                                         | m.A      |

|                 | Power Supply Current<br>Output HIGH   |      | 14       | 25        | $V_{CC} = MAX$ , $V_{CP} = 0$ V, $V_{E} = 0$ V                                                                            |                                                                         | mA       |

Notes: 1 Conditions for testing, not shown in the table are chosen to guarantee operationunder "worst case" conditions.

2 Not more than one output should be shorted at a time. (\*) Typical values are at  $V_{CC}$  = 5.0 V,  $T_A$  = 25  $^{\circ}C$ .

# AC CHARACTERISTICS : $T_A = 25 \, ^{\circ}\! C$

| Symbol                               | Parameter                             | Limits |          |          | Test Conditions |                                                     | 11-:4 |

|--------------------------------------|---------------------------------------|--------|----------|----------|-----------------|-----------------------------------------------------|-------|

|                                      | Parameter                             | Min.   | Тур.     | Max.     | rest Conditions |                                                     | Unit  |

| f <sub>MAX</sub>                     | Shift Frequency                       | 30     | 45       |          | Fig. 1          | , FO.V                                              | MHz   |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay,<br>Clock to Output |        | 24<br>16 | 30<br>26 | Fig. 1          | $V_{CC} = 5.0 \text{ V}$ $C_L = 15 \text{ pF}$      | ns    |

| tрzн                                 | Output Enable Time to HIGH Level      |        | 12       | 18       | Figs. 4, 5      | $C_L = 15 \text{ pF}$ $R_L = 2 \text{ k}\Omega$     | ns    |

| t <sub>PZL</sub>                     | Output Enable Time to LOW Level       |        | 14       | 20       | Figs. 3, 5      |                                                     | ns    |

| t <sub>PLZ</sub>                     | Output Disable Time from LOW Level    |        | 17       | 24       | Figs. 3, 5      | C <sub>L</sub> = 5 pF                               | ns    |

| t <sub>PHZ</sub>                     | Output Disable Time from HIGH Level   |        | 15       | 20       | Figs. 4, 5      | $R_L = 2 k\Omega$                                   | ns    |

| t <sub>W</sub> (CP)                  | Clock Pulse Width                     | 20     |          |          | Fig. 1          |                                                     | ns    |

| t <sub>s</sub> (Data)                | Set-up Time, Data to Clock            | 20     |          |          | Fig. 1          | 7,, 50,,                                            | ns    |

| t <sub>s</sub> (Data)                | Hold Time, Data to Clock              | 10     |          |          |                 | $V_{CC} = 5.0 \text{ V}$<br>$C_{L} = 15 \text{ pF}$ | ns    |

| t <sub>S</sub> (PE)                  | Set-up Time, PE to Clock              | 20     |          |          | Fig. 1          |                                                     | ns    |

| t <sub>h</sub> (PE)                  | Hold Time, PE to Clock                | 0      |          |          |                 |                                                     | ns    |

### **DEFINITION OF TERMS**

SET-UP TIME  $(t_s)$  - is defined as the minimum time required for the correct logic level to be present at the logic input prior to the clock transition from HIGH to LOW in order to be recognized and transferred to the outputs.

HOLD TIME  $(t_h)$  - is defined as the minimum time following the clock transition from HIGH to LOW that

the logic level must be maintained at the input in order to ensure continued recognition. A negative HOLD TIME indicates that the correct logic level may be released prior to the clock transition from HIGH to LOW and still be recognized.

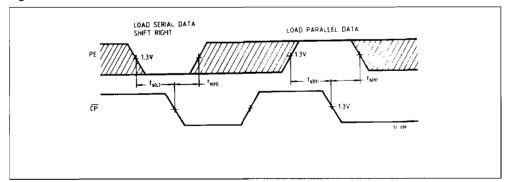

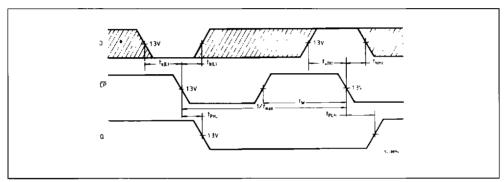

### **AC WAVEFORMS**

The shaded areas indicate when the input is permitted to change for predictable output performance.

Figure 1.

The data input is Ds for PE = LOW and Pn for PE = HIGH.

Figure 2.