CFS1020B is a 16-bit wide last-in-first-out circuit which can be used as a stack with built-in stack pointer. The data is allowed to be written onto the top of the stack during the next clock cycle following the push operation. The depth of the LIFO can grow to five. After a depth of five is reached, FLN goes LOW. Any further push onto a full stack overwrites data at the top of the stack. Data is allowed to be read from the stack for the rest of the cycle following the pop operation. When the stack is empty, EMPN goes LOW. The stack pointer points the next location to be written. When the stack pointer is 000, the stack is empty. When the stack pointer is 101, the stack is full.

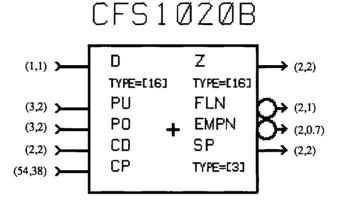

### PIN CONNECTION DIAGRAM:

### **FEATURES:**

- 5-word deep

- Full/empty signal

- Synchronous clear

- 16-bit data

**EQUIVALENT USED GATES: 684 GATES**

(for rough area estimates)

THIS MEGAFUNCTION CONSISTS OF: 684 soft-coded gates.

**POWER:** NOT AVAILABLE.

FAULT COVERAGE(%): 98.93%

FUNCTIONAL TABLE:

| I    | NPUTS |    |            | OPERATION |  |  |

|------|-------|----|------------|-----------|--|--|

| l CD | PU    | PO | ;<br> <br> | OPERATION |  |  |

| 1 0  |       |    |            | CLEAR     |  |  |

| 1 1  | 0     | 0  |            | HOLD      |  |  |

| 1 1  | 1     | 0  |            | PUSH      |  |  |

| 1 1  | 0     | 1  | 1          | POP       |  |  |

| 1    | 1     | 1  | <b></b>    | UNDEFINED |  |  |

# PIN DESCRIPTION:

| D15:0 | DATA INPUT TO THE LIFO |

|-------|------------------------|

| PU    | PUSH CONTROL INPUT     |

| PO    | POP CONTROL INPUT      |

| CD    | CLEAR CONTROL INPUT    |

| CP    | CLOCK INPUT            |

| Z15:0 | DATA OUTPUT BUS        |

| FLN   | FULL SIGNAL OUTPUT     |

| EMPN  | EMPTY SIGNAL OUTPUT    |

| SP2:0 | STACK POINTER OUTPUT   |

# CYCLE TIME AND CLOCK CHARACTERISTICS:

|   |         |       |      | <br>  |     |      |      | _   |

|---|---------|-------|------|-------|-----|------|------|-----|

| 1 |         | TIME  |      | 1     | 10K | TYP. | (ns) | ļ   |

| 1 | MINIMUM | CLOCK |      | <br>1 |     | 10   |      | - I |

| 1 | MINIMUM | CLOCK | HIGH | <br>• |     | 8    |      | - 1 |

| 1 | MINIMUM | CYCLE |      | <br>1 |     | 18   |      | -   |

|   |         |       |      |       |     |      |      |     |

## MAXIMUM COMBINATIONAL PROPAGATION DELAY:

|   | INPUT | • |     |   |   |     | (ns) |  |   | -<br> <br> - |

|---|-------|---|-----|---|---|-----|------|--|---|--------------|

|   |       | i | FLN | ŀ | Z | - 1 | EMPN |  |   | _            |

| 1 |       |   |     |   |   |     | 4    |  | 4 | -            |

ASSUMING OUTPUT LOADING OF 2

# SET-UP TIME AND HOLD TIME:

| <br>  INPUT | }<br>!      | 10K T  | YP. | (ns) |

|-------------|-------------|--------|-----|------|

| INFOI       | 1           | SET-UP | ŀ   | HOLD |

| PU          |             | 7      |     | 0    |

| l PO        |             | 7      | 1   | 0    |

| D           | 1           | 3      |     | 0    |

| CD          | _ <b></b> . | 3      | l   | 0    |