Dual, Ultra Low Noise, High PSRR 300mA Linear Regulator

# DESCRIPTION

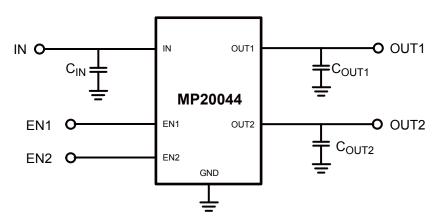

The MP20044 is a dual-channel, micropower, ultra low noise, low dropout and high PSRR linear regulator. The output voltage of MP20044 ranges from 1.2V to 5.0V in 100mV increments and 1% accuracy by operating from a +2.5V to +6.0V input. The MP20044 can supply up to 300mA of load current at each channel.

The MP20044 uses an internal PMOS as the pass element, which consumes 114µA supply current (both LDOs on) at no load condition. The EN1 and EN2 pins control each output respectively. When both channels shutdown simultaneously, the chip will be turned off and consume nearly zero operation current which is suitable for battery-power devices. The MP20044 features current limit and over temperature protection.

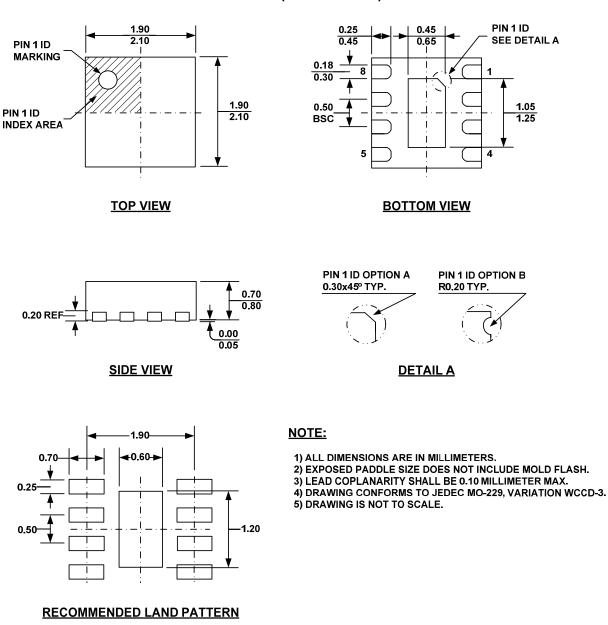

It is available in a 2mm x 2mm TQFN8 package.

### **FEATURES**

- Wide Operating Voltage Ranges: 2.5V to 6V

- Two LDOs in a 2mmx2mm TQFN8 Package

- Up to 300mA Output Current (Per Channel)

- Dual Enable Pins Control Each Output

- 72dB PSRR at 10kHz

- 11µV<sub>RMS</sub> Ultra Low Noise Output with No Noise Bypass Capacitor Required

- 73mV Dropout at 100mA Load

- Very Fast Line/Load Transient Responses with Small Input/Output Capacitor

- Current Limit and Thermal Protection

### **APPLICATIONS**

- Cellular Phones

- Battery-powered Equipment

- Laptop, Notebook, and Palmtop Computers

- Hand-held Equipment

- Wireless LAN

All MPS parts are lead-free and adhere to the RoHS directive. For MPS green status, please visit MPS website under Products, Quality Assurance page. "MPS" and "The Future of Analog IC Technology" are registered trademarks of Monolithic Power Systems, Inc.

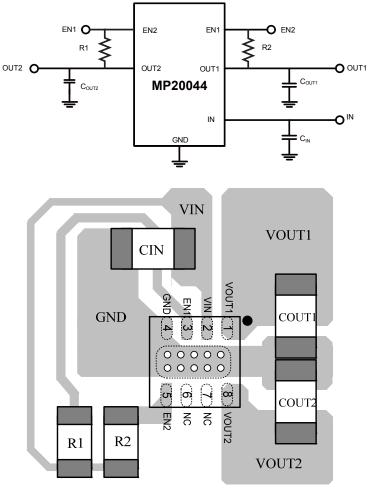

### TYPICAL APPLICATION

| Part Number        | V <sub>OUT1</sub> | V <sub>OUT2</sub> | Package            | Free Air Temperature (T <sub>A</sub> ) | Top Marking |

|--------------------|-------------------|-------------------|--------------------|----------------------------------------|-------------|

| MP20044DGT-JG-LF-Z | 2.5V              | 1.8V              |                    |                                        |             |

| MP20044DGT-GM-LF-Z | 1.8V              | 2.8V              | TQFN8<br>(2mmx2mm) |                                        |             |

| MP20044DGT-SS-LF-Z | 3.3V              | 3.3V              |                    |                                        |             |

| MP20044DGT-LS-LF-Z | 2.7V              | 3.3V              |                    | -40°C to +85°C                         |             |

| MP20044DGT-SM-LF-Z | 3.3V              | 2.8V              |                    |                                        |             |

| MP20044DGT-PP-LF-Z | 3.0V              | 3.0V              |                    |                                        | 3W          |

| MP20044DGT-CG-LF-Z | 1.2V              | 1.8V              |                    |                                        |             |

| MP20044DGT-SJ-LF-Z | 3.3V              | 2.5V              |                    |                                        |             |

| MP20044DGT-SG-LF-Z | 3.3V              | 1.8V              |                    |                                        |             |

| MP20044DGT-BG-LF-Z | 1.3V              | 1.8V              |                    |                                        |             |

#### **ORDERING INFORMATION\***

\* Available options are identified by those with top marking. For other options, please contact factory to check availability.

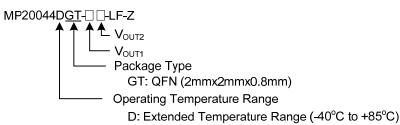

### **ORDERING GUIDE\*\***

\*\* For RoHS Compliant Packaging, add suffix - LF (e.g. MP20044DGT-D-LF);

For Tape and Reel, add suffix -Z (e.g. MP20044DGT-D-LF-Z).

#### **OUTPUT VOLTAGE SELECTOR GUIDE\*\*\***

| Code | V <sub>OUT</sub> | Code | V <sub>OUT</sub> |

|------|------------------|------|------------------|

| С    | 1.2              | Т    | 2.65             |

| В    | 1.3              | L    | 2.7              |

| F    | 1.5              | М    | 2.8              |

| W    | 1.6              | N    | 2.85             |

| G    | 1.8              | V    | 2.9              |

| D    | 1.85             | Р    | 3.0              |

| Y    | 1.9              | Q    | 3.1              |

| Н    | 2.0              | X    | 3.15             |

| E    | 2.1              | R    | 3.2              |

| J    | 2.5              | S    | 3.3              |

| K    | 2.6              | Z    | 5.0              |

\*\*\* Code in **Bold** are standard versions. For other output voltages between 1.2V and 5.0V contact factory for availability. Minimum order quantity on non-standard versions is 25,000 units.

# ABSOLUTE MAXIMUM RATINGS (1)

### Recommended Operating Conditions <sup>(3)</sup>

| Supply Input Voltage                    | 2.5V to 6.0V    |

|-----------------------------------------|-----------------|

| Enable Input Voltage                    | 0V to 6.0V      |

| Operating Junct. Temp (T <sub>J</sub> ) | -40°C to +125°C |

Thermal Resistance $\boldsymbol{\theta}_{JA}$  $\boldsymbol{\theta}_{JC}$ 2mmx2mm TQFN8......80......16 ... °C/W

#### Notes:

- 1) Exceeding these ratings may cause permanent damage to the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature T<sub>J</sub>(MAX), the junction-toambient thermal resistance  $\theta_{JA}$ , and the ambient temperature T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub>(MAX)=(T<sub>J</sub>(MAX)-T<sub>A</sub>)/ $\theta_{JA}$ . Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- 3) The device is not guaranteed to function outside its operating conditions.

- 4) Measured on JESD51-7 4-layer board.

# **ELECTRICAL CHARACTERISTICS**

$V_{IN}$ =3.5V,  $V_{OUT1}$ =2.5V,  $V_{OUT2}$ =1.8V,  $C_{IN}$ = $C_{OUT1}$ = $C_{OUT2}$ =1 $\mu$ F, EN1=EN2= $V_{IN}$ , Typical Value at T<sub>A</sub>=25°C for each LDO unless otherwise noted.

| Parameter                      | Symbol                   | Condition                                                                         |         | Min | Тур  | Мах  | Units             |

|--------------------------------|--------------------------|-----------------------------------------------------------------------------------|---------|-----|------|------|-------------------|

| Input Voltage                  | V <sub>IN</sub>          | V <sub>IN</sub> =2.5V to 6.0V                                                     |         | 2.5 |      | 6    | V                 |

| Output Voltage Range           | V <sub>OUT</sub>         | -                                                                                 |         | 1.2 |      | 5.0  | V                 |

| Output Voltage Accuracy        | $\Delta V_{OUT}$         | I <sub>LOAD</sub> = 1mA                                                           |         |     |      | 2.5  | %                 |

| Load regulation <sup>(5)</sup> | $\Delta V_{OUT}$         | $I_{LOAD}$ = 1mA to 300mA                                                         |         |     | 15   | 35   | mV                |

| Line Regulation <sup>(6)</sup> | $\Delta V_{\text{LINE}}$ | V <sub>IN</sub> =(V <sub>OUT</sub> +0.3V or 2.5V)<br>to 6V, I <sub>OUT</sub> =1mA |         |     |      | 0.05 | %/V               |

| Maximum Output Current         | I <sub>MAX</sub>         | Continuous                                                                        |         | 300 |      |      | mA                |

| Current Limit                  | I <sub>LIM</sub>         | Short circuit current limit                                                       |         |     | 525  |      | mA                |

| Quiescent Current              | I <sub>G</sub>           | No Load                                                                           |         |     | 114  |      | uA                |

|                                | V <sub>DROP1</sub>       | V <sub>OUT1</sub> =2.5V, I <sub>OUT1</sub> = 100mA                                |         |     | 60   |      | mV                |

| Dropout Voltage (7)            |                          | V <sub>OUT1</sub> =2.5V, I <sub>OUT1</sub> = 300mA                                |         |     | 180  |      | mV                |

| Dropout voltage                | V <sub>DROP2</sub>       | V <sub>OUT2</sub> =1.8V, I <sub>OUT2</sub> = 100mA                                |         |     | 75   |      | mV                |

|                                |                          | V <sub>OUT2</sub> =1.8V, I <sub>OUT2</sub> = 300mA                                |         |     | 220  |      | mV                |

| EN Input High Threshold        | V <sub>IH</sub>          | $V_{IN}$ = 2.5V to 6.0V                                                           |         | 1.6 |      |      | V                 |

| EN Input Low Threshold         | V <sub>IL</sub>          | $V_{IN} = 2.5V \text{ to } 6.0V$                                                  |         |     |      | 0.45 | V                 |

| EN Input Bias Current          | I <sub>SD</sub>          | $EN = GND \text{ or } V_{IN}$                                                     |         |     |      | 300  | nA                |

| Shutdown Supply Current        | I <sub>GSD</sub>         | EN1 = EN2 = GND                                                                   |         |     | 0.03 | 1    | uA                |

| Thermal Shutdown Temperature   | T <sub>SD</sub>          |                                                                                   |         |     | 140  |      | С°                |

| Thermal Shutdown Hysteresis    | $\Delta T_{SD}$          |                                                                                   |         |     | 10   |      | С°                |

|                                |                          | 100Hz to 100kHz,<br>C <sub>OUT</sub> =1µF, I <sub>LOAD</sub> =10mA                |         |     | 11   |      | μV <sub>RMS</sub> |

| Output Voltage Noise           |                          |                                                                                   |         |     |      |      | P V RMS           |

| oulput voltage Noise           |                          | 100Hz to 100kHz,                                                                  |         | 11  | 11   |      | $\mu V_{RMS}$     |

|                                |                          | $C_{OUT}=1\mu F$ , $I_{LOAD}=100mA$                                               |         |     |      |      | -                 |

|                                | PSRR                     | I <sub>Load</sub> =10mA                                                           | f=100Hz |     | 68   |      | dB                |

|                                |                          |                                                                                   | f=1kHz  |     | 66   |      | dB                |

| Output Voltage AC PSRR         |                          |                                                                                   | f=10kHz |     | 65   |      | dB                |

|                                |                          | I <sub>Load</sub> =150mA                                                          | f=100Hz |     | 69   |      | dB                |

|                                |                          |                                                                                   | f=1kHz  |     | 65   |      | dB                |

|                                |                          | f=10kHz                                                                           |         |     | 72   |      | dB                |

#### Notes:

5) Load Regulation= $\frac{\left|V_{OUT[l_{OUT(NMX)}]} - V_{OUT[l_{OUT(NMN)}]}\right|}{V_{OUT(NOM)}} \times (\%)$

6) Line Regulation=  $\left| V_{OUT[V_{N(MAX)}]} - V_{OUT[V_{N(MN)}]} \right| \times (\% / V)$

$$V_{\rm IN(MAX)} - V_{\rm IN(MIN)} \times V_{\rm OUT(NOM)}$$

7) Dropout Voltage is defined as the input to output differential when the output voltage drops 100mV below its nominal value.

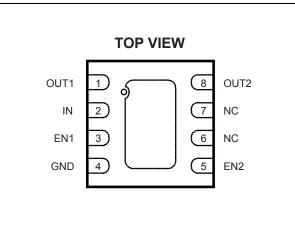

## **PIN FUNCTIONS**

| Pin # | Name | Description                                            |  |

|-------|------|--------------------------------------------------------|--|

| 1     | OUT1 | Channel 1 Output Voltage                               |  |

| 2     | IN   | Supply Input Pin                                       |  |

| 3     | EN1  | Channel 1 Enable (Active High). Do Not Float This Pin. |  |

| 4     | GND  | Common Ground                                          |  |

| 5     | EN2  | Channel 2 Enable (Active High). Do Not Float This Pin. |  |

| 6, 7  | NC   |                                                        |  |

| 8     | OUT2 | Channel 2 Output Voltage                               |  |

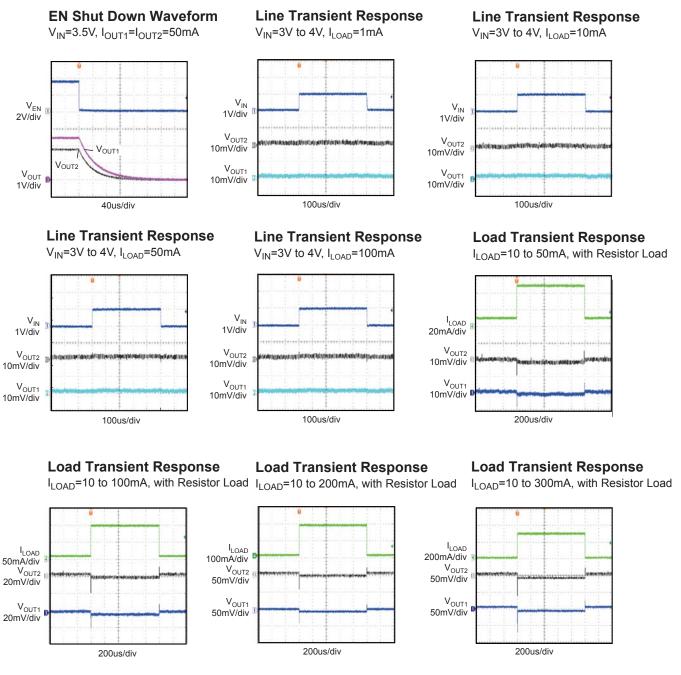

## **TYPICAL PERFORMANCE CHARACTERISTICS**

علا

$V_{IN}$ =3.5V,  $V_{OUT1}$ =2.5V,  $V_{OUT2}$ =1.8V,  $I_{OUT1}$ = $I_{OUT2}$ =0mA,  $C_{IN}$ = $C_{OUT1}$ = $C_{OUT2}$ =1µF, EN1=EN2= $V_{IN}$ , Typical Value at  $T_A$  = 25°C for Both Channel Enabled.

### **TYPICAL PERFORMANCE CHARACTERISTICS** (continued)

$V_{IN}$ =3.5V,  $V_{OUT1}$ =2.5V,  $V_{OUT2}$ =1.8V,  $I_{OUT1}$ = $I_{OUT2}$ =0mA,  $C_{IN}$ = $C_{OUT1}$ = $C_{OUT2}$ =1µF, EN1=EN2= $V_{IN}$ , Typical Value at  $T_A$  = 25°C for Both Channel Enabled.

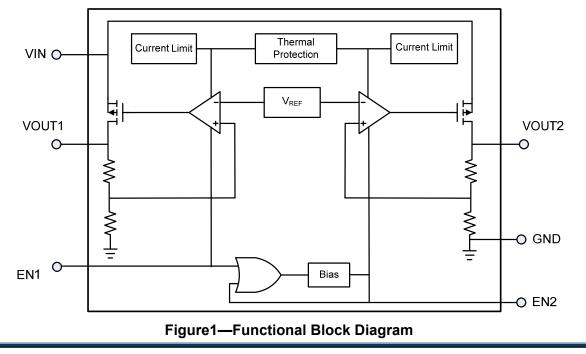

### **BLOCK DIAGRAM**

### **OPERATION**

The MP20044 integrates two low noise, low dropout, low quiescent current and high PSRR linear regulators. It is intended for use in devices that require very low voltage, low quiescent current power such as wireless LAN, battery-powered equipment and hand-held equipment. The MP20044 uses internal PMOSs as the pass elements and features internal thermal shutdown and internal current limit circuits.

#### **Dropout Voltage**

Dropout voltage is the minimum input to output differential voltage required for the regulator to maintain an output voltage within 100mV of its nominal value. Because the PMOS pass element behaves as a low-value resistor, the dropout voltage of MP20044 is very low.

#### Shutdown

The MP20044 can be switched ON or OFF by a logic input at the EN pin. A high voltage at this pin will turn the device on. When the EN pin is low, the regulator output is off. The EN pin should be tied to VIN to keep the regulator output always on if the application does not require the shutdown feature. Do not float the EN pin.

#### **Current Limit**

The MP20044 includes two independent current limit structures which monitor and control each PMOS's gate voltage limiting the guaranteed maximum output current to 300mA.

#### **Thermal Protection**

Thermal protection turns off the PMOS when the junction temperature exceeds +140°C, allowing the IC to cool. When the IC's junction temperature drops by 10°C, the PMOS will be turned on again. Thermal protection limits total power dissipation in the MP20044. For reliable operation, junction temperature should be limited to 125 °C maximum.

#### **Load-Transient Considerations**

The output response of load-transient consists of a DC shift and transient response. Because of the excellent load regulation of MP20044, the DC shift is very small. The output voltage transient depends on the output capacitor's value and the ESR. Increasing the capacitance and decreasing the ESR will improve the transient response. Typical output voltage transient spike of MP20044 for a step change in the load current from 10mA to 100mA is tens mV.

### **APPLICATION INFORMATION**

#### **Power Dissipation**

The power dissipation for any package depends on the thermal resistance of the case and circuit board, the temperature difference between the junction and ambient air, and the rate of airflow. The power dissipation across the device can be represented by the equation:

$$\mathsf{P} = (\mathsf{V}_{\mathsf{IN}} - \mathsf{V}_{\mathsf{OUT}}) \times \mathsf{I}_{\mathsf{OUT}}$$

The allowable power dissipation can be calculated using the following equation:

$$P_{(MAX)} = (T_{Junction} - T_{Ambient}) / \theta_{JA}$$

Where  $(T_{Junction} - T_{Ambient})$  is the temperature difference between the junction and the surrounding environment,  $\theta_{JA}$  is the thermal resistance from the junction to the ambient environment. Connect the GND pin of MP20044 to ground using a large pad or ground plane helps to channel heat away.

#### **Input Capacitor Selection**

Using a capacitor whose value is  $>0.47\mu$ F on the MP20044 input and the amount of capacitance can be increased without limit. Larger values will help improve line transient response with the drawback of increased size. Ceramic capacitors are preferred, but tantalum capacitors may also suffice.

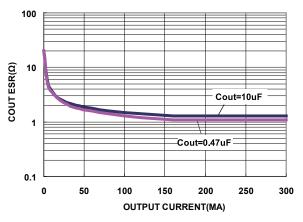

#### **Output Capacitor Selection**

The MP20044 is designed specifically to work with very low ESR ceramic output capacitor in space-saving and performance consideration. A ceramic capacitor in the range of  $0.47\mu$ F and  $10\mu$ F, and with ESR lower than  $1.2\Omega$  is suitable for the MP20044 application circuit. Output capacitor of larger values will help to improve load transient response and reduce noise with the drawback of increased size.

Figure 2—Relationship between ESR and LDO Stability

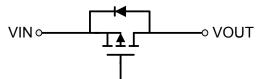

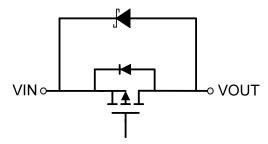

#### **Reverse Current Path**

The PMOS used in the MP20044 has an inherent diode connected between input and output (see Figure3). If  $V_{OUT}$  -  $V_{IN}$  is more than a diode-drop, this diode gets forward biased and starts to conduct. To avoid misoperation, an external Schottky connected in parallel with the internal parasitic diode prevents it from being turned on by limiting the voltage drop across it to about 0.3V (see Figure 4).

Figure 3—Inherent Diode Connected between Each Regulator Input and Output

Figure 4—External Schottky Diode Connected in Parallel with the Internal Parasitic Diode

#### PCB layout guide

PCB layout is very important to achieve good regulation, ripple rejection, transient response and thermal performance. It is highly recommended to duplicate EVB layout for optimum performance.

If change is necessary, please follow these guidelines and take figure 5 for reference.

- 1) Input and output bypass ceramic capacitors are suggested to be put close to the IN Pin and OUT Pin respectively.

- Ensure all feedback connections are short and direct. Place the feedback resistors and compensation components as close to the chip as possible.

- Connect IN, OUT and especially GND respectively to a large copper area to cool the chip to improve thermal performance and long-term reliability.

Top Layer Figure 5—PCB Layout

## **PACKAGE INFORMATION**

TQFN8 (2mm x 2mm)

**NOTICE:** The information in this document is subject to change without notice. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.