### AS7620

## 500mA Hysteretic High Voltage Step-Down Converter with Dual Power Monitor

## 1 General Description

The AS7620 is an easy-to-use, high-efficiency, high-voltage, hysteretic step-down DC-DC converter, operating in asynchronous mode. Its low-power architecture extends hold-up time in batterybacked and critical applications where maximum up-time over a wide input supply voltage range is needed, while still providing for high efficiencies of up to 90% during peak current demands.

Although the AS7620 is optimized for 24V applications found in industrial and medical systems, its ability to support 100% Duty Cycle makes the AS7620 ideal for applications demanding maximum up-time and soft power fail behavior. In combination with low idle current of only 30µA, on-demand switching reduces operating current at low load currents.

By selecting an appropriate inductor value, operating current can be lowered and switching frequencies tuned to certain load conditions.

A pin-strapped current limit input minimizes inductor peak current and thus inductor size and cost for any given application.

The device further includes output short-circuit protection and thermal shutdown. In shutdown mode, only 1µA (typ) of current is consumed.

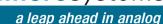

Figure 1. AS7620 - Block Diagram

## 2 Key Features

- Low quiescent current for efficient partial load operation

- Wide Supply Voltage Range, 3.6V to 32V

- 100% Duty Cycle extends operating range

- Pin-programmable cycle-by-cycle current limit

- Integrated PMOS eliminates bootstrap capacitor

- Resistor-programmable Early Power Fail Warning Input

- Power-Good Flag

- Thermal Shutdown

- Fixed 3.3V and adjustable output (1.2V to VIN)

- Small 4x4mm 12-Lead MLPQ Enhanced Power Package

- Specified from -40°C to +125°C junction and 85°C maximum ambient temperatures

### 3 Applications

The AS7620 is suitable for Industrial 24VDC applications like PLCs, robotics; Home Security and Building Control applications; Solidstate utility meters; Signage and LED column power; and Sensor interfaces.

# 4 Pin Assignments

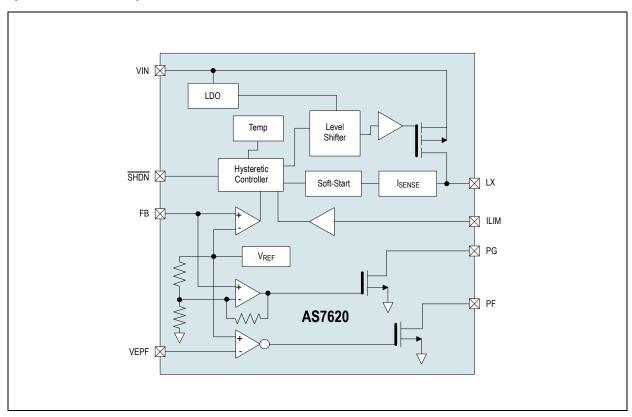

Figure 2. Pin Assignments (Top View)

### 4.1 Pin Descriptions

Table 1. Pin Descriptions

| Pin Number | Pin Name | Description                                                           |

|------------|----------|-----------------------------------------------------------------------|

| 1          | VIN      | High Voltage Power Supply Input                                       |

| 2          | GND      | Must be connected to GND                                              |

| 3          | LX       | Power Output to Inductor                                              |

| 4          | GND      | Must be connected to GND                                              |

| 5          | FB       | Feedback input                                                        |

| 6          | ILIM     | Current Limit input                                                   |

| 7          | SHDN     | Shutdown input, active low                                            |

| 8          | GND      | Must be connected to GND                                              |

| 9          | GND      | Must be connected to GND                                              |

| 10         | PF       | Early Power Fail output, open drain, active LOW                       |

| 11         | VEPF     | Comparator voltage input for early power fail warning                 |

| 12         | PG       | Power Good, open drain, active HIGH output, monitors feedback voltage |

| Pad        | PGND     | Exposed pad. Connect to GND plane to help thermal dissipation         |

# 5 Absolute Maximum Ratings

Stresses beyond those listed in Table 2 may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in Electrical Characteristics on page 4 is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Table 2. Absolute Maximum Ratings

| Parameter                                 | Min   | Max               | Units | Comments                                                                                                                                                                                                                                                                           |

|-------------------------------------------|-------|-------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Electrical Parameters                     |       |                   |       |                                                                                                                                                                                                                                                                                    |

| Vin                                       | -0.3  | 40                | V     |                                                                                                                                                                                                                                                                                    |

| LX                                        | -0.3  | VIN+0.3           | V     |                                                                                                                                                                                                                                                                                    |

| FB, SHDN                                  | -0.3  | VIN+0.3<br>or 5.5 | V     | Whichever is lower                                                                                                                                                                                                                                                                 |

| All other pins except LX, FB and SHDN     | -0.3  | 3.6               | V     |                                                                                                                                                                                                                                                                                    |

| Input Current (latch-up immunity)         | -30   | +30               | mA    | Norm: JEDEC 78 <sup>1</sup>                                                                                                                                                                                                                                                        |

| Electrostatic Discharge                   |       |                   |       |                                                                                                                                                                                                                                                                                    |

| Electrostatic Discharge HBM               | +/- 1 |                   | kV    | Norm: MIL 883 E method 3015                                                                                                                                                                                                                                                        |

| Temperature Ranges and Storage Conditions |       |                   |       |                                                                                                                                                                                                                                                                                    |

| Package Power Dissipation                 |       | 1                 | W     | θJA = 32°C/W for a 4-layer board, 4 vias, TAMB = +70°C                                                                                                                                                                                                                             |

| Storage Temperature                       | -55   | 150               | °C    |                                                                                                                                                                                                                                                                                    |

| Junction Temperature                      |       | 150               | °C    |                                                                                                                                                                                                                                                                                    |

| Package body temperature                  |       | 260               | °C    | The reflow peak soldering temperature (body temperature) specified is in accordance with IPC/ JEDEC J-STD-020"Moisture/Reflow Sensitivity Classification for Non-Hermetic Solid State Surface Mount Devices".  The lead finish for Pb-free leaded packages is matte tin (100% Sn). |

| Humidity non-condensing                   | 5     | 85                | %     |                                                                                                                                                                                                                                                                                    |

| Moisture Sensitive Level                  |       | 3                 |       | Represents a max. floor life time of 168h                                                                                                                                                                                                                                          |

<sup>1.</sup> Voltage on pin 7 (SHDN) limited to +5.5V

### **6 Electrical Characteristics**

Vout=3.3V,  $L_X=10\mu H$ ,  $C_X=100\mu F$ , typical values at Vin=+24V and TAMB=  $+25^{\circ}C$  (unless otherwise specified). All limits are guaranteed. The parameters with min and max values are guaranteed with production tests or SQC (Statistical Quality Control) methods.

Table 3. Electrical Characteristics

| Symbol            | Paramet                               | er                     | Conditions                                                                              | Min                                                                                         | Тур   | Max                 | Units |

|-------------------|---------------------------------------|------------------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-------|---------------------|-------|

| Тамв              | Operating Temperature Range           |                        |                                                                                         | -40                                                                                         |       | 85                  | °C    |

| TJ                | Operating Junction                    | Temperature            |                                                                                         | -40                                                                                         |       | 125                 | °C    |

| VIN               | Input Voltage Range                   |                        |                                                                                         | 3.6                                                                                         | 24    | 32                  | V     |

| Vcc               | - Input voltage                       | Kange                  | VEPF, ILIM                                                                              | -0.3                                                                                        |       | 3.6                 | V     |

| V <sub>ST</sub>   | Start-up Vo                           | Itage                  |                                                                                         | 3.3                                                                                         |       |                     | V     |

|                   |                                       | AS7620-A               |                                                                                         | 1.19                                                                                        |       | Vin                 | V     |

| Vout              | Output Voltage                        | AS7620-B               | Initial, at 25°C amb.                                                                   | 3.267                                                                                       | 3.300 | 3.333               | V     |

|                   |                                       | A37020-D               | Over line, load and temperature                                                         | 3.218                                                                                       |       | 3.383               | V     |

|                   |                                       | AS7620-A               | Initial, at 25°C amb.                                                                   | 1.178                                                                                       | 1.190 | 1.202               | V     |

| VFB               | Feedback voltage                      | A37020-A               | Over line and temperature                                                               | 1.166                                                                                       |       | 1.214               | V     |

|                   |                                       | AS7620-B               |                                                                                         | 3.218                                                                                       | 3.300 | 3.383               | V     |

| V <sub>HYS</sub>  | Controller Hysteresis                 | AS7620-A               | At FB node                                                                              | 8                                                                                           | 15    | 30                  | mV    |

| VH15              | Controller Hysteresis                 | AS7620-B               | ALFBIIIQUE                                                                              | 22                                                                                          | 42    | 82                  | IIIV  |

| $V_{EPF}$         | Early Power Fail                      | Threshold              | at V <sub>EPF</sub>                                                                     |                                                                                             | 1.19  |                     | V     |

| $V_{PG}$          | Power Good TI                         | hreshold               | of V <sub>FB</sub> at FB pin                                                            | 91                                                                                          | 93    | 95                  | %     |

|                   | Line Regula                           | ation                  | VIN=8V to 24V, $R_L$ =200 $\Omega$                                                      |                                                                                             | 0.1   |                     | % / V |

|                   | Load Regul                            | ation                  | 10% to 90% load change                                                                  |                                                                                             | 0.9   |                     | %     |

| I                 | Input Pigg Current                    | AS7620-A               | ED air                                                                                  |                                                                                             |       | 200                 | nA    |

| I <sub>FB</sub>   | Input Bias Current                    | AS7620-B               | - FB pin                                                                                | 91 93<br>0.1<br>0.9<br>3                                                                    | 3     | 5                   | μA    |

| lout              | Output Cur                            | rrent                  |                                                                                         |                                                                                             |       | I <sub>LIM</sub> /2 | mA    |

|                   | I <sub>LIM</sub> Switch Current Limit |                        | ILIM=0V <sup>1</sup>                                                                    | 192                                                                                         | 240   | 288                 |       |

| I <sub>LIM</sub>  |                                       | ILIM=Vout <sup>2</sup> | 576                                                                                     | 720                                                                                         | 864   | mA                  |       |

|                   |                                       |                        | ILIM=open                                                                               | -0.3 3.3 1.19 3.267 3.218 1.178 1.166 3.218 3. 8 22 1 91 (0) 192 2 576 7 800 1 (0) 8 0.22 0 | 1000  | 1200                |       |

|                   | P-Channel on re                       | esistance              |                                                                                         |                                                                                             | 0.4   | 0.8                 | Ω     |

|                   | Maximum Dut                           | y Cycle                | At VIN=3.6V                                                                             |                                                                                             |       | 100                 | %     |

| ton               | Minimum On                            | ı-Time                 | Current limit is not attained to turn off the switch before the minimum on-time expired | 8                                                                                           | 10    | 12                  | μs    |

| toff              | Minimum Off                           | f-Time                 |                                                                                         | 0.22                                                                                        | 0.42  | 0.62                | μs    |

| 1.                | Quiescent Current                     | Non-switching          |                                                                                         | 30                                                                                          | 45    | μA                  |       |

| lQ                | Quiescent C                           | urrent                 | Ιουτ=500μΑ                                                                              |                                                                                             | 37    |                     | μA    |

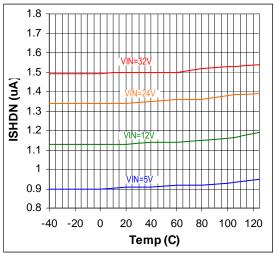

| I <sub>SHDN</sub> | Shutdown C                            | urrent                 | TAMB= +25°C                                                                             |                                                                                             | 1     | 5                   | μA    |

| V <sub>LO</sub>   | Shutdown Thi                          | reshold                | SHDN                                                                                    |                                                                                             |       | 1                   | V     |

| I <sub>IBN</sub>  | Logic Input Bias                      | s Current              | SHDN                                                                                    |                                                                                             |       | 1                   | μA    |

| T <sub>SHDN</sub> | Shutdown Tem                          | perature               |                                                                                         |                                                                                             | 160   |                     | °C    |

|                   | T <sub>SHDN</sub> Hyste               | eresis                 |                                                                                         |                                                                                             | 10    |                     | °C    |

<sup>1.</sup>  $LX=100\mu H$ ,  $C_X=10\mu F$ , Initial accuracy only. For temperature variation, please refer to performance graphs.

<sup>2.</sup> VOUT from 1.5V to 3.6V

# 7 Typical Operating Characteristics

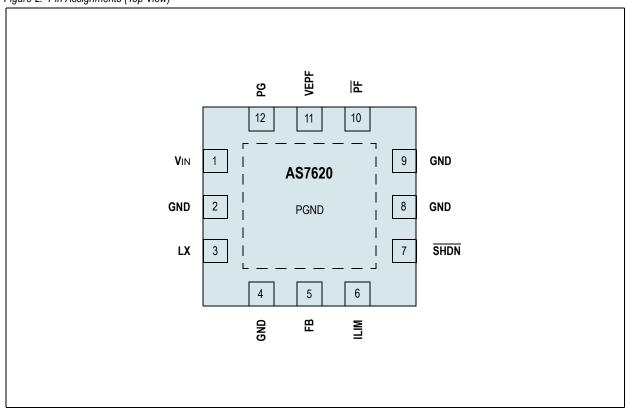

Figure 3. Efficiency vs. Output Current, Vout=4.5V

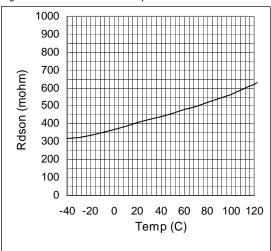

Figure 4. PMOS Rdson vs. Temperature

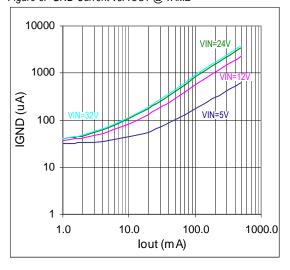

Figure 5. GND Current vs. IOUT @ TAMB

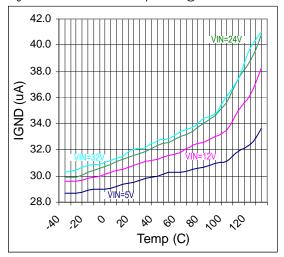

Figure 6. GND Current vs. Temperature @ IOUT=0A

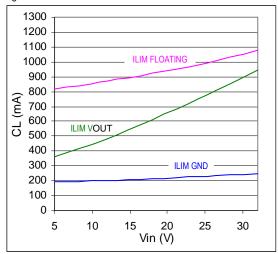

Figure 7. Current Limit Threshold vs. VIN

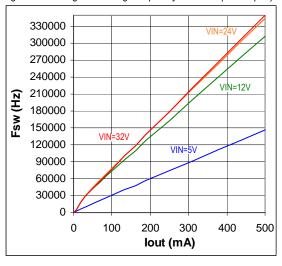

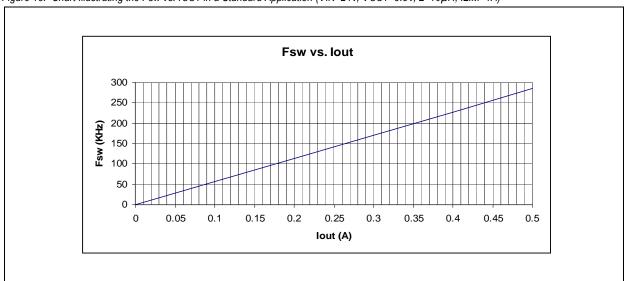

Figure 9. Average Switching Frequency vs. IOUT (ILIM=open)

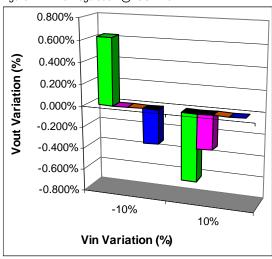

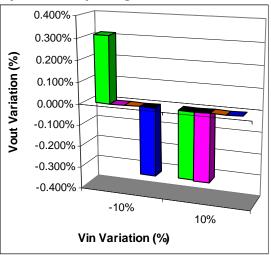

Figure 11. Line Regulation @ IOUT=10mA

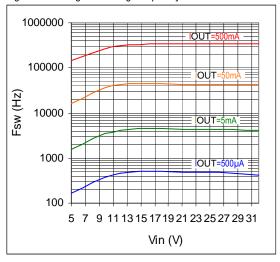

Figure 8. Average Switching Frequency vs. VIN

Figure 10. Shutdown Current vs. Temperature

Figure 12. Line Regulation @ IOUT=500mA

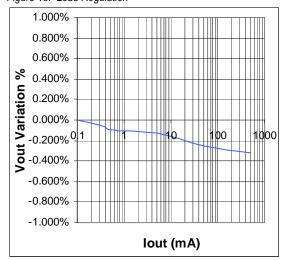

Figure 13. Load Regulation

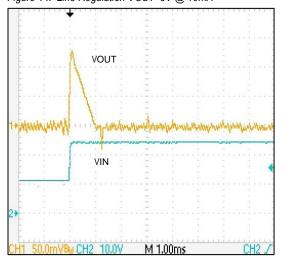

Figure 14. Line Regulation VouT=5V @ 10mA

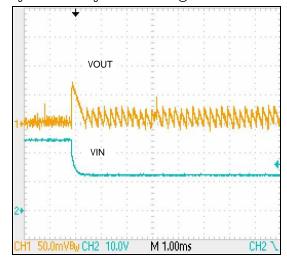

Figure 15. Line Regulation Vout=5V @ 10mA

Figure 16. Load Regulation Vour=5V 10mA →500mA

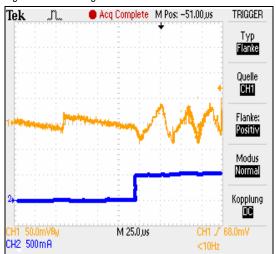

**Note:** All measurements taken at VIN=24V, VOUT=3.3V, and TAMB=25°C using the typical application circuit specified in Figure 17, unless otherwise specified.

# 8 Detailed Description

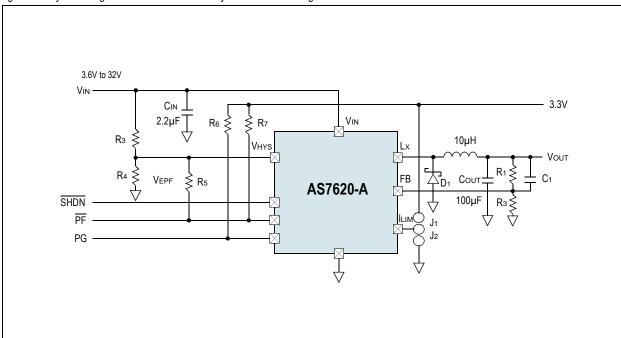

Figure 17. System Diagram of AS7620-A with Early Power Fail Warning

Table 4. AS7620 Output Voltage Options

| AS7620 | AS7620A-BQFT | AS7620B-BQFT |  |

|--------|--------------|--------------|--|

| Vout   | ADJ.         | 3.3V         |  |

#### 8.1 Shut Down

The device can be shut down by providing a voltage lower than 1V at the SHDN pin (7). In this condition, the consumption is only 1µA (typ). The AS7620 is providing an internally regulated pull-up circuit. No external pull-up resistor shall be used, which could otherwise damage the shutdown input. Connect the SHDN input directly to an open drain port only.

#### 8.2 Soft Start

The device implements a soft start by limiting the inrush current into the output choke. Initially, the internal PMOS is turned on until the current reaches the programmed current limit (see Current Limit on page 9) and then is immediately turned off. It will be turned on again when the current approaches 0A. In this time frame, the FB voltage (VFB) will be lower than the reference and so the duty cycle will be driven by the current limit only.

#### 8.3 Regulation

Both AS7620-A and AS7620-B are based on a hysteretic control method. Moreover, the switch current is monitored to make the converter always work in discontinuous current mode (DCM). The advantages of this type of control system can be summarized as following:

- High efficiency even at light load

- Intrinsically stable

- Simplicity

- Readiness during the load transient

The internal PMOS is switched on when the VFB is lower than VREF-V<sub>HYST</sub>/2 and the current is 0A (DCM). The on time will be terminated if the VFB is over VREF+V<sub>HYST</sub>/2 or if the current limit (CL) is triggered. In practice, considering the most common application conditions (L=10 $\mu$ H ÷ 100 $\mu$ H; C=10 $\mu$ F - 100 $\mu$ F) and setting the CL threshold according to the load, the on time is normally terminated by the CL intervention and the output voltage ripple will stay within 1.25% of the output voltage (typ) or V<sub>HYST</sub> \* VOUT / VREF.

#### 8.4 VOLT Selection

The AS7620-B features a 3.3V fixed output voltage. The AS7620-A provides an adjustable output from 1.2V (VREF) up to virtually VIN (see 100% Duty Cycle Operation on page 11). To select the desired VOUT, the related resistor divider has to be tuned according to the following formula:

$$V_{OUT} = V_{REF} \bullet \left(1 + \frac{Rh}{Rl}\right)$$

(EQ 1)

#### Where:

Rh is the high side resistor of the output divider RI is the resistor of the output divider

**Note:** It is suggested to select resistors in the range of hundreds of  $k\Omega$  in order to limit the current consumption.

#### 8.5 Current Limit

The current is sensed during the on time of the internal PMOS. Three different current limit thresholds can be selected by the ILIM pin:

- 1. 240mA (typ) ILIM shorted to GND

- 2. 720mA (typ) ILIM shorted to VOUT (from 1.5V to 3.6V)

- 3. 1000mA (typ) ILIM floating

This threshold is intended as peak current limit. If the current reaches the threshold during the on time, the PMOS is turned off and it will be turned on again only when the current approaches 0A and the feedback voltage is equal or lower than VREF. The maximum output current is ILIM/2.

#### 8.6 Switching Frequency

The switching frequency ( $f_{SW}$ ) changes according to the application conditions and, in particular, to the output current in order to optimize the efficiency in any load condition. Anyway, it is always possible to estimate the  $f_{SW}$  during the design process. As described in the Regulation (refer to page 8) – the converter always works in DCM and, normally, the peak current into the inductor is the CL threshold (ILIM). The average of the inductor current must be equal to the output current. The following formula provides the relationship between inductor current and output current:

$$IOUT = \frac{1}{Tsw} \bullet \frac{1}{2} \bullet \frac{ILIM^2 \bullet L \bullet V_{IN}}{(V_{IN} - V_{OUT}) \bullet V_{OUT}}$$

(EQ 2)

Consequently, the f<sub>sw</sub> can be expressed as following:

$$Fsw = \frac{2 \bullet I_{OUT} \bullet (V_{IN} - V_{OUT}) \bullet V_{OUT}}{ILIM^2 \bullet L \bullet V_{IN}}$$

(EQ 3)

Figure 18. Chart Illustrating the Fsw vs. IOUT in a Standard Application (VIN=24V, VOUT=3.3V, L=10µH, ILIM=1A)

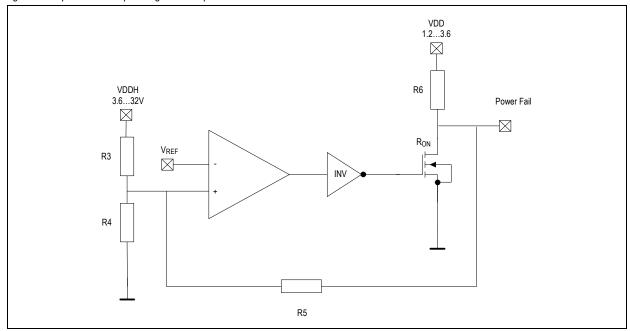

#### 8.7 Power Fail / Power Good

AS7620A-B monitors input and output voltage by VEPF (pin 11) and VFB (pin 5) respectively. Two dedicated flags  $\overline{PF}$  (pin 10) and PG (pin 12) are provided outside to inform about early input power fail (active low) and output within regulation. Figure 19 illustrates the typical connection for VEPF. During start up,  $\overline{PF}$  is initially low. By selecting R3, R4, R5 and R6, it is possible to set the desired input voltage threshold above which the input power is considered stable. Once VIN (VDDH in Figure 19) reaches Vinth,  $\overline{PF}$  is released and so an additional voltage contribution from VDD is added at the VPF pin, realizing in fact a hysteresis to eliminate  $\overline{PF}$  oscillation due to power supply noise.

Figure 19. Open-Drain Output Stage for Comparator

Table 5 provides the resistors values covering all the standard input BUS. The resistors values are 1% commercial values. It is mandatory to use the correct resistors values to guarantee the respect of maximum absolute voltages at EPF and PF pin. VDD has been considered 3.3V. Otherwise EPF pin should be shorted to GND and PF left floating.

Terminology:

VRST: Reset voltage for the EPF. It is 90% of the Input BUS voltage.

VTRIP: Trip voltage for the EPF. It is 80% of the Input BUS voltage.

Table 5. EPF Network Selection with Different Input BUS

| VIN (V) | VRST (V) | VTRIP (V) | R3 (KΩ) | <b>R4</b> ( <b>K</b> Ω) | <b>R5</b> ( <b>K</b> Ω) | R6 (KΩ) |

|---------|----------|-----------|---------|-------------------------|-------------------------|---------|

| 5       | 4.5      | 4         | 365     | 143                     | 1740                    | 1370    |

| 6       | 5.4      | 4.8       | 464     | 143                     | 1870                    | 1430    |

| 9       | 8.1      | 7.2       | 768     | 140                     | 2050                    | 1580    |

| 12      | 10.8     | 9.6       | 1070    | 140                     | 2100                    | 1650    |

| 15      | 13.5     | 12        | 1370    | 140                     | 2150                    | 1690    |

| 20      | 18       | 16        | 1870    | 140                     | 2210                    | 1740    |

| 24      | 21.6     | 19.2      | 2260    | 140                     | 2260                    | 1740    |

| 28      | 25.3     | 22.5      | 2670    | 140                     | 2260                    | 1740    |

#### 8.8 Thermal Protection

The internal junction temperature is continuously monitored. If it reaches 150°C (min), the PMOS is turned off. The device can switch again if the temperature is decreased by at least 10°C. If the over-temperature persists, the device will be shut down again resulting in a hiccup mode for the output power.

## 9 Application Information

### 9.1 Input Capacitors

An input capacitor is required to sustain the peak current requested by the turning on of the internal PMOS. When used, the capacitor helps to reduce the noise and saves the input battery life. The input capacitor has to withstand the input RMS current, which can be calculated by the following formula:

$$Irms = I_{OUT} \bullet \sqrt{\frac{V_{OUT} \bullet (V_{IN} - V_{OUT})}{V_{IN}}}$$

(EQ 4)

While designing for wide input/output voltage range, the worst case of Irms=1/2\*IOUT must be considered. Suggested capacitors are low ESR OSCON, polymer, aluminum or MLCCs. Tantalum types are not recommended for their weakness in withstanding big inrush currents.

#### 9.2 Output Inductor

The inductor together with the output capacitor represents the output filter. Using the AS7620, the inductor is charged and completely discharged at every switching cycle being that the converter is forced to work in DCM. Values from 10µH to 100µH are suitable to work with AS7620 and its selection should consider the following statements:

- Bigger inductor implies lower f<sub>sw</sub>

- Bigger inductor implies lower bandwidth

The inductor must be rated to withstand the peak current (ILIM) and the RMS current  $Irms = \sqrt{I_{OUT}^2 + \frac{\Delta IL^2}{3}}$

### 9.3 Output Capacitor

The output capacitor together with the inductor represents the output filter. The bigger the capacitance is, the lower will be the output ripple. Usually, low ESR MLCCs are preferred as they are inexpensive and small in size. Any value from 10µF is suitable, considering the load transient specifications of the application as well.

#### 9.4 Free Wheeling Diode

The inductor current is forced through the diode during the off-times. The average current flowing through it is  $\frac{1}{2} \bullet fsw \bullet \frac{ILIM^2 \bullet L}{V_{OUT}}$

The reverse voltage must be higher than the input voltage and safely it is common to consider 30% more. Normally, a schottky diode is preferred because of its low forward voltage.

### 9.5 Stability

Even though the hysteretic voltage mode is intrinsically stable, an excessive noise at the FB could cause instability. For this reason care must be taken drawing the layout, reducing the noise and shielding the FB path from it. The main noise generator is the switching node, which is commutated from GND to VIN by the internal PMOS and the free wheeling diode and through which a pulse current flows. It is wise to add a MLCC capacitor as close as possible to the VIN pin of the device and provide a wide/short path between the LX pin and the external components (inductor and diode). It is preferable to draw the FB path as far as possible from the LX node and, perhaps, shielding it with a GND track. Another recommendation is to use low ESL output capacitors, thus avoiding electrolytic parts. A big ESL adds a square wave contribution on the FB that can make the device work improperly.

#### 9.6 100% Duty Cycle Operation

Thanks to the PMOS structure of the internal switch, the device can actually work at 100% duty cycle. This feature is very helpful during the load transient, because the maximum power can be transferred to the output in order to recover as fastest. The device will try to work at 100% duty whenever the FB voltage is lower than the upper window's threshold. Moreover, in this condition, the safety is always guaranteed by the current limit.

### 9.7 Demo Board

A demonstration board is available to test the device functionalities and performance in a standard application. For further information, please refer to the AS7620EB datasheet.

Figure 20. Demo Board Photograph

# **10 Package Drawings and Markings**

Figure 21. 12-pin MLPQ 4x4mm Marking

Table 6. Packaging Code YYWWXZZ

| YY                                  | WW                 | X                | ZZ                              |

|-------------------------------------|--------------------|------------------|---------------------------------|

| last two digits of the current year | manufacturing week | plant identifier | free choice / traceability code |

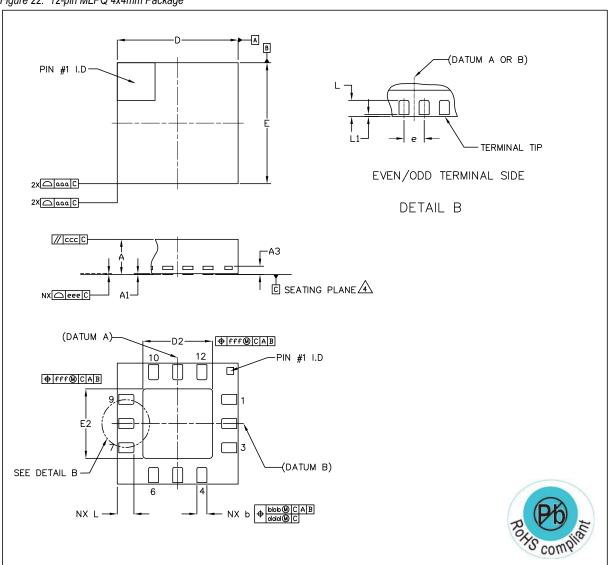

Figure 22. 12-pin MLPQ 4x4mm Package

| REF. | MIN          | NOM      | MAX          |

|------|--------------|----------|--------------|

| Α    | 0.80         | 0.90     | 1.00         |

| A1   | 0            | 0.02     | 0.05         |

| A3   | -            | 0.20 REF | _            |

| L    | 0.45         | 0.55     | 0.65         |

| L1   | 0.00         | _        | 0.15         |

| b    | 0.00<br>0.25 | 0.30     | 0.15<br>0.35 |

| D    |              | 4.00 BSC |              |

| E    |              | 4.00 BSC |              |

| е    |              | 0.80 BSC |              |

| D2   | 2.20         | 2.30     | 2.40         |

| E2   | 2.20         | 2.30     | 2.40         |

| aaa  | I            | 0.15     | _            |

| bbb  | ı            | 0.10     | -            |

| ccc  | ı            | 0.10     | -            |

| ddd  | ı            | 0.05     | -            |

| eee  |              | 0.08     | _            |

| fff  | 1            | 0.10     | _            |

| N    |              | 12       |              |

#### NOTE:

- 1. DIMENSIONS & TOLERANCEING CONFIRM TO ASME Y14.5M-1994.

- 2. ALL DIMENSIONS ARE IN MILLIMETERS. ANGELS ARE IN DEGREES.

- 3. DIMENSION 6 APPLIES TO METALLIZED TERMINAL AND IS MEASURED BETWEEN 0.25mm AND 0.30mm FROM TERMINAL TIP. DIMENSION L1 REPRESENTS TERMINAL FULL BACK FROM PACKAGE EDGE UP TO 0.15mm IS ACCEPTABLE.

- $\stackrel{\textstyle \triangle}{\triangle}$  Coplanarity applies to the exposed heat slug as well as the terminal.

- 5. RADIUS ON TERMINAL IS OPTIONAL.

- 6. N IS THE TOTAL NUMBER OF TERMINALS.

| al austrian    | nicrosys        | stems           | ASSEMBLY ENGINEERING                                                 |                                                         |

|----------------|-----------------|-----------------|----------------------------------------------------------------------|---------------------------------------------------------|

| DRAVN<br>RH8   | a leap ahead i  | n analog        | TITLE<br>SAWN QFN, PULL BACK, 4x4x0.9mm,<br>12 LEAD, 2.30mm SQ. ePAD | REFERENCE DOCUMENT<br>JEDEC MO — 220<br>LATEST REVISION |

| CHECKED<br>GBO | DATE 2010.10.29 |                 | DRAVING ND.<br>QKJ                                                   | UNIT                                                    |

| APPROVED MKR   | 2010.10.29      | SHEET<br>1 DF 1 | DIMENSION AND TOLERANCE                                              | SCALE<br>NOT IN SCALE                                   |

# 11 Ordering Information

The devices are available as the standard products shown in Table 7.

Table 7. Ordering Information

| Ordering Code | Marking              | Output     | Description                                                                                          | Delivery Form | Package           |

|---------------|----------------------|------------|------------------------------------------------------------------------------------------------------|---------------|-------------------|

| AS7620-BQFT   | AS7620 or<br>AS7620A | adjustable | 500mA Hysteretic High Voltage Step-Down Converter with Dual Power Monitor                            | Tape and Reel | 12-pin MLPQ 4x4mm |

| AS7620B-BQFT* | AS7620B              | 3.3V       | 500mA Hysteretic High Voltage Step-Down<br>Converter with Dual Power Monitor<br>without Output Delay | Tape and Reel | 12-pin MLPQ 4x4mm |

<sup>\*</sup>Available on request

Note: All products are RoHS compliant.

Buy our products or get free samples online at ICdirect: http://www.austriamicrosystems.com/ICdirect

Technical Support is found at http://www.austriamicrosystems.com/Technical-Support

For further information and requests, please contact us mailto:sales@austriamicrosystems.com or find your local distributor at http://www.austriamicrosystems.com/distributor

Design the AS7620 online at http://www.austriamicrosystems.com/analogbench analogbench is a powerful design and simulation support tool that operates in on-line and off-line mode to evaluate performance and generate application-specific bill-of-materials for austriamicrosystems' power management devices.

### Copyrights

Copyright © 1997-2011, austriamicrosystems AG, Tobelbaderstrasse 30, 8141 Unterpremstaetten, Austria-Europe. Trademarks Registered ®. All rights reserved. The material herein may not be reproduced, adapted, merged, translated, stored, or used without the prior written consent of the copyright owner.

All products and companies mentioned are trademarks or registered trademarks of their respective companies.

#### Disclaimer

Devices sold by austriamicrosystems AG are covered by the warranty and patent indemnification provisions appearing in its Term of Sale. austriamicrosystems AG makes no warranty, express, statutory, implied, or by description regarding the information set forth herein or regarding the freedom of the described devices from patent infringement. austriamicrosystems AG reserves the right to change specifications and prices at any time and without notice. Therefore, prior to designing this product into a system, it is necessary to check with austriamicrosystems AG for current information. This product is intended for use in normal commercial applications. Applications requiring extended temperature range, unusual environmental requirements, or high reliability applications, such as military, medical life-support or life-sustaining equipment are specifically not recommended without additional processing by austriamicrosystems AG for each application. For shipments of less than 100 parts the manufacturing flow might show deviations from the standard production flow, such as test flow or test location.

The information furnished here by austriamicrosystems AG is believed to be correct and accurate. However, austriamicrosystems AG shall not be liable to recipient or any third party for any damages, including but not limited to personal injury, property damage, loss of profits, loss of use, interruption of business or indirect, special, incidental or consequential damages, of any kind, in connection with or arising out of the furnishing, performance or use of the technical data herein. No obligation or liability to recipient or any third party shall arise or flow out of austriamicrosystems AG rendering of technical or other services.

#### **Contact Information**

Headquarters

austriamicrosystems AG Tobelbaderstrasse 30 A-8141 Unterpremstaetten, Austria

Tel: +43 (0) 3136 500 0 Fax: +43 (0) 3136 525 01

For Sales Offices, Distributors and Representatives, please visit:

http://www.austriamicrosystems.com/contact