### **Preliminary**

### Programmable Peripheral ZPSD6XX(V) Family

Field-Programmable Microcontroller Peripherals with Embedded Micro⇔ Cells™

#### Introduction

The ZPSD6XX(V) series is a complete family of Field Programmable Microcontroller Peripherals with Embedded Micro⇔Cell™ Programmable Logic. The devices are used to rapidly implement highly integrated embedded control systems. The device family offers a variety of functions including Zero Power PLDs (ZPLDs) with embedded Micro⇔Cells, dynamically reconfigurable I/O Ports, programmable power management, EPROM, SRAM and other functions.

Drawing from WSI's years of experience with microcontroller (MCU) applications, the new ZPSD6XX(V) product family radically simplifies the addition of programmable logic to embedded system designs. New innovative "microcontroller-macrocells", called Micro⇔Cells, bring inexpensive programmable logic to MCU-based embedded system designs. Because the Micro⇔Cells are directly connected to the system address/data bus, their NVM-based programmable logic is tightly coupled to the software programs running in the system MCU. The MCU's ability to communicate directly with the Micro⇔Cells at the Flip-Flop level makes ZPSD6XX(V) devices ideal for implementing the functions most frequently needed in embedded systems.

Communicating with Microcontrollers — Regardless of the function they perform, all microcontroller peripherals must communicate to the MCU. All MCUs require clock, data bus, chip select, and read or write signals. To implement these signals using current industry standard PLDs required the use of valuable product terms and macrocells in each PLD chip. In the case of most embedded system designs, this left so few remaining usable PLD resources to implement the peripheral function that designers dismissed the use of a PLD as too expensive.

The Micro⇔Cell directly connects its PLD logic to the MCU. The MCU then sees the PLD in the ZPSD6XX(V) as a decoded location in the address map. Direct read and write operations can be easily and simply performed. Functions like counters and serial ports can be constructed with programmable logic without any design time or resources lost interfacing to the MCU.

### **Key Features**

| A simple, programmable interface to 8 or 16 bit microcontrollers using either multiplexed or non-multiplexed busses. The bus interface logic directly decodes microcontroller control signals. Microcontroller families supported include the Intel 8031, 80196, 80186, 80C251 and 80386EX; Motorola 68HC11, 68HC16, 68HC12 and 683XX; Philips 8031 and 8051XA; National 16000; Zilog Z80 and Z8; and Neuron 3150. |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Three ZPLDs (Zero Power PLDs) with 12 Output Micro⇔Cells and 23 Input Micro⇔Cells, 63 inputs and 129 product terms. The ZPSD6XX(V) ZPLDs may be used to efficiently implement a variety of logic functions including state machines and address decoders for internal and external control. The ZPLD also provides seven external chip select outputs.                                                             |

| Embedded Input and Output Micro⇔Cells that enable efficient implementation of user defined system logic functions that require both microcontroller software and hardware interaction.                                                                                                                                                                                                                             |

| Zero Power CMOS technology reduces the device standby current to 10 µA typical.                                                                                                                                                                                                                                                                                                                                    |

Return to Main Menu 12-1

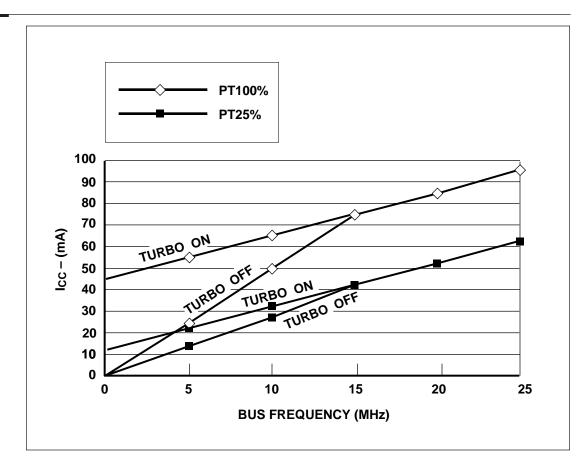

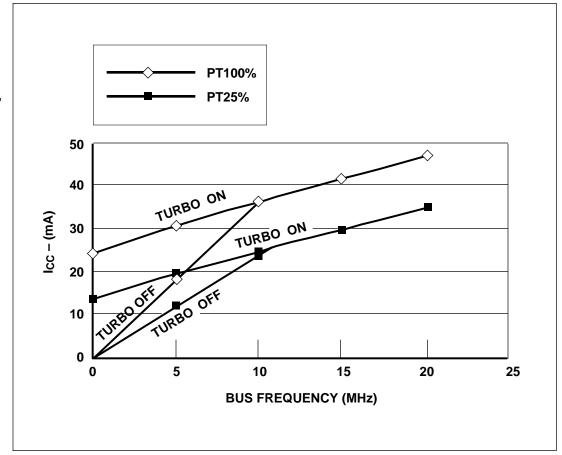

Active power is as low as 0.8 mA per bus MHz.

### Key Features (cont.)

| Twenty six individually configurable I/O Port pins. The Ports may be used as MCU I/Os, PLD I/Os, latched MCU address outputs or special function I/Os. Fifteen I/O port pins can be configured as open drain outputs.                                                                                                                                                                                                                                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Internal EPROM in densities of 256 Kbit, 512 Kbit and 1 Mbit, configurable in eight or sixteen-bit widths. The EPROM is divided into eight equal-size blocks, accessible by user-specified addresses. The access time includes address latching and PLD decoding. The EPROM includes a low power option.                                                                                                                                                                           |

| Internal 4 Kbit SRAM can be configured in eight or sixteen-bit data widths. The SRAM retains data if power is lost by automatically switching to standby power.                                                                                                                                                                                                                                                                                                                    |

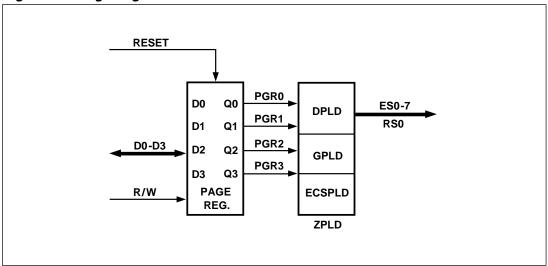

| A page register expands the microcontroller address space by a factor of sixteen.                                                                                                                                                                                                                                                                                                                                                                                                  |

| A security bit prevents copying the ZPSD6XX(V) configuration and ZPLD logic as well as the EPROM contents.                                                                                                                                                                                                                                                                                                                                                                         |

| ZPSD6XXV(V) devices (2.7V to 5.5V operation) are specifically designed for low voltage and low power applications.                                                                                                                                                                                                                                                                                                                                                                 |

| The programmable Power Management Unit (PMU) supports two separate, low-power modes allowing operations with as little as 10 $\mu A$ (at 5V $V_{CC}$ ). The device can automatically detect a lack of microcontroller activity and put the PSD into power down mode.                                                                                                                                                                                                               |

| The devices are available in EPROM versions. The ceramic package is ideal for prototyping and low-volume production, and in OTP versions for high-volume, low-cost applications.                                                                                                                                                                                                                                                                                                   |

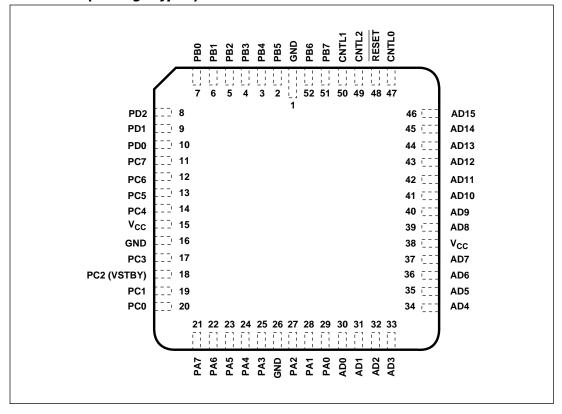

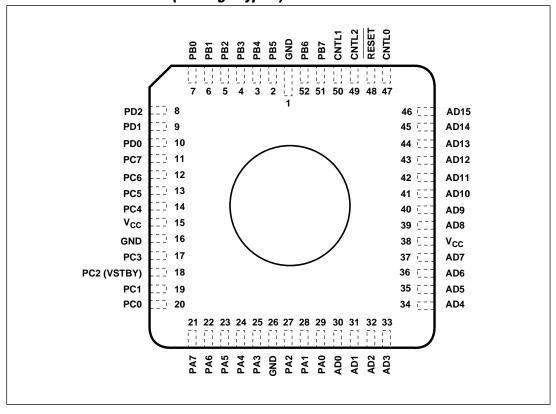

| Package choices include 52 pin plastic chip carrier (J), ceramic chip carrier (L), and plastic quad flat pack (U).                                                                                                                                                                                                                                                                                                                                                                 |

| ZPSD6XX(V) family development is supported by the WSI's PC based PSDsoft <sup>™</sup> design system. The software is MS-Windows <sup>®</sup> and Windows 95 compatible. The suite includes PSDabel <sup>™</sup> (ABEL <sup>®</sup> ), to specify the ZPLD logic, and an efficient fitter. The tool also includes the PSDsilosIII simulator from SIMUCAD <sup>™</sup> . The MagicPro <sup>®</sup> III programmer is an engineering development tool and can program any PSD device. |

### General Information

The ZPSD6XX(V) series of Field Programmable Microcontroller Peripherals combine an innovative architecture with advanced technology to provide a user-programmable, high-performance, low-power solution to microcontroller system design. The embedded input and output Micro⇔Cells enable efficient implementation of user defined logic functions that require both software and hardware interaction. The devices eliminate the need for discrete 'glue' logic and allow the development of entire systems using only a few highly integrated devices.

# **ZPSD Background**

Portable and battery powered systems have recently become major embedded control application segments. As a result, the demand for electronic components having extremely low power consumption has increased dramatically. Recognizing this need, WSI, Inc. has developed a new ZPSD (Zero Power PSD) technology. ZPSD products virtually eliminate the DC component of power consumption reducing it to standby levels. Eliminating the DC component is the basis for the words "Zero Power" in the ZPSD name. ZPSD products also minimize the AC power component when the chip is changing states. The result is a programmable microcontroller peripheral family that replaces at least six discrete circuit functions while drawing much less power than a single EPROM.

Please refer to the revision block at the end of this document for updated information.

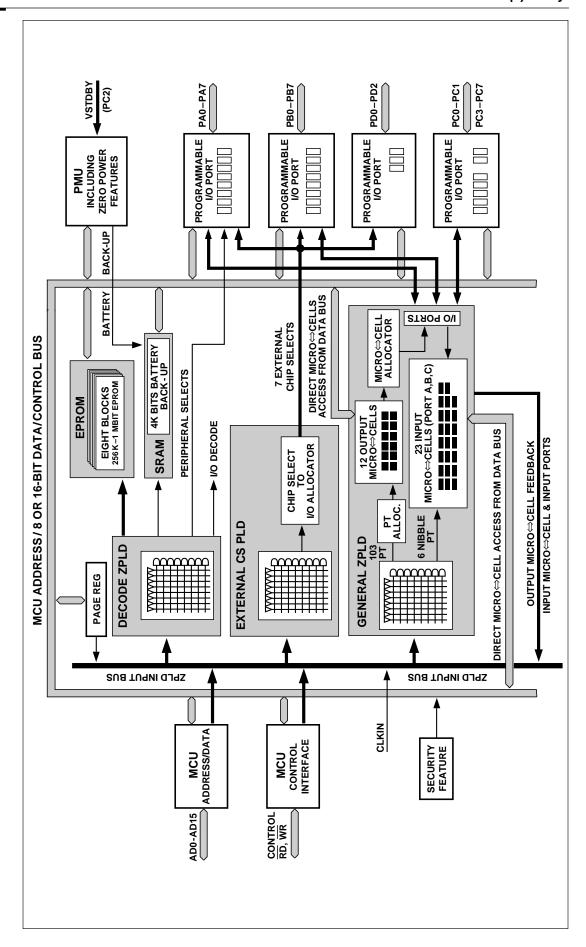

Figure 1. ZPSD6XX(V) Architecture

### Integrated Power Management™ Operation

Upon each address or logic input change to the ZPSD, the device powers up from low power standby for a short time. The ZPSD consumes only the necessary power to deliver new logic or memory data to its outputs as a response to the input change. After the new outputs are stable, the ZPSD latches them and automatically reverts back to standby mode. The  $I_{CC}$  current flowing during standby mode and during DC operation is identical and is only a few microamperes.

The ZPSD automatically reduces its DC current drain to these low levels and does not require controlling by the CSI (Chip Select) input. Disabling the CSI pin unconditionally forces the ZPSD to standby mode independent of other input transitions.

The only significant power consumption in the ZPSD occurs during AC operation. The ZPSD contains the first architecture to apply zero power techniques to memory circuit blocks as well as logic.

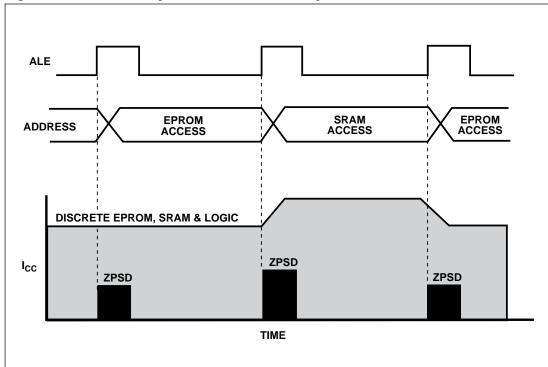

Figure 2 compares ZPSD zero power operation to the operation of a discrete solution. A standard microcontroller (MCU) bus cycle usually starts with an ALE (or AS) pulse and the generation of an address. The ZPSD detects the address transition and powers up for a very short time. The ZPSD then latches the outputs of the PAD, EPROM and SRAM to the new values. After finishing these operations, the ZPSD shuts off its internal power and enters standby mode. The time taken for the entire cycle is less than the ZPSD's "access time."

The ZPSD will stay in standby mode if the address does not change between bus cycles (for example, looping on a single address or a Halt operation). In an alternate system implementation using an EPROM, SRAM and other discrete components, the system will consume operating power during the entire bus cycle. This is because the chip select inputs on the memory devices are usually active throughout the entire cycle. The AC power consumption of the ZPSD may be calculated using the ALE frequency.

Figure 2. ZPSD Power Operation vs. Discrete Implementation

### Development System

The ZPSD6XX(V) family is supported by the Windows-based PSDsoft Development System. The PSDsoft design flow is shown in Figure 3. The ZPLD design entry is done using PSDabel, which creates a minimized logic implementation, and provides logic simulation of the ZPLDs. The ZPSD6XX(V) Bus Interface and I/O Port configuration are entered in PSDconfiguration.

The PSDcompiler, comprised of a fitter and an address translator, generates an object file from the PSDabel, PSDconfiguration and MCU code files. The object file is then downloaded to a programmer (MagicPro III, Data I/O, or other third party programmer for device programming) or to a PSDsimulator (PSDsilos III Logic simulator) for device-level simulation.

**PSDabel ZPLD DESCRIPTION GENERATE ABEL FILE OR USE DESIGN TEMPLATE PSDconfiguration CONFIGURE PSD BUS INTERFACE PSDcompiler FITTER ZPLD FITTING PROGRAM CODE FILE** ADDRESS TRANSLATOR **EPROM MAPPING** THIRD PARTY **PROGRAMMERS** OBJ FILE **PSDprogrammer PSDsimulator** Magic Pro® III PROGRAMMER **PSDsilos III** CHIP SIMULATION CHIP PROGRAMMING

Figure 3. PSDsoft Development Tools

# **Device Versions**

The ZPSD6XX(V) window package versions are ideal for general purpose embedded systems development. The ZPSD6XX(V) plastic packaged OTP versions deliver the lowest cost ZPSD6XX(V) solution.

# *ZPSD6XX(V) Family*

There are 6 devices in the ZPSD6XX(V) family. The part classifications are based on EPROM size and data bus width. The features of each part are listed in Table 1.

Table 1. ZPSD6XX(V) Product Matrix

| Part         | Bus    | I/O  | EPROM | SRAM  |

|--------------|--------|------|-------|-------|

| #            | Width  | Pins | K Bit | K Bit |

| ZPSD601(V)E1 | x8/x16 | 26   | 256   | 4     |

| ZPSD611(V)E1 | x8     | 26   | 256   | 4     |

| ZPSD602(V)E1 | x8/x16 | 26   | 512   | 4     |

| ZPSD612(V)E1 | x8     | 26   | 512   | 4     |

| ZPSD603(V)E1 | x8/x16 | 26   | 1024  | 4     |

| ZPSD613(V)E1 | x8     | 26   | 1024  | 4     |

### Table 2. ZPSD6XX(V) Pin Descriptions

The following table describes the pin names and pin functions of the ZPSD6XX(V). Pins that have multiple names and/or functions are defined by configuration.

| Pin Name                           | Pin   | Туре | Function Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|------------------------------------|-------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| ADIO0-7                            | 30-37 | I/O  | <ol> <li>Address/Data Port, interface to Microcontroller Bus</li> <li>Input pins for multiplexed low order address/data byte.         ALE or AS latches address A0-7. The PSD drives data out only if read is active and one of the internal PSD functional blocks is selected.</li> <li>Address A0-7 inputs for non-multiplexed bus or 80C251 mode</li> <li>A4/D0-A11/D7 inputs in 80C51XA mode</li> <li>Address (or latched address) inputs to ZPLD</li> </ol>                                                                                                                         |  |  |  |

| ADIO8-15                           | 39-46 | I/O  | <ol> <li>Address/Data Port, interface to Microcontroller Bus</li> <li>Address A8-15 inputs in 8-bit data bus mode, or as multiplexed high order address/data byte inputs in 16-bit data bus mode. ALE or AS latches address A8-15.         The PSD drives data out only if read is active and one of the internal PSD functional blocks is selected.     </li> <li>Address A8-15 inputs in non-multiplexed bus mode</li> <li>AD8-AD15 inputs in 80C251 mode</li> <li>A12-A19 or A12/D8 - A19/D15 inputs in 80C51XA mode</li> <li>Address ( or latched address) inputs to ZPLD</li> </ol> |  |  |  |

| CNTL0) (WR, R_W, WRL)              | 47    | I    | Write Input pin with multiple configurations. Depending on the MCU interface selected, this pin can be:  1. WR – active low write input  2. R_W – read/write pin, low for write bus cycle  3. WRL – for 16 bit data bus only, write to low byte, active low  4. Control signal (CNTL0) input to ZPLD                                                                                                                                                                                                                                                                                     |  |  |  |

| CNTL1 (RD, E, DS, LDS, PSEN)       | 50    | 1    | Read or Data Strobe Input pin with multiple configurations.  Depending on the MCU interface selected, this pin can be:  1. RD – active low read input  2. E – E clock input.  During a write bus cycle, E is high and R/W is low  During a read bus cycle, E is high and R/W is high  3. DS – Data Strobe, active low  4. LDS – Strobe for low data byte, 16-bit data bus mode, active low  5. PSEN – Program Select Enable, active low in read bus cycle (80C251 configuration)  6. Control signal (CNTL1) input to ZPLD                                                                |  |  |  |

| CNTL2 49 I  (PSEN, BHE, UDS, SIZO) |       | _    | Read or other Control input pin with multiple configuration Depending on the MCU interface selected, this pin can be 1. PSEN – Program Select enable, active low in code fetch bus cycle 2. BHE – High byte enable, 16-bit data bus 3. UDS – Strobe for high data byte, 16-bit data bus mode, active low 4. SIZO – Byte enable input 5. Control signal (CNTL2) input or general input to ZPLD                                                                                                                                                                                            |  |  |  |

# Table 2. ZPSD6XX(V) Pin Descriptions (cont.)

| Pin Name                                               | Pin                                    | Туре                               | Function Description                                                                                                                                                                                                                                                                                                                                            |

|--------------------------------------------------------|----------------------------------------|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET                                                  | 48                                     | I                                  | Active low input. Resets I/O Ports, ZPLD Micro⇔Cells and some of the Configuration Registers. Must be active at power up.                                                                                                                                                                                                                                       |

| PA0<br>PA1<br>PA2<br>PA3                               | 29<br>28<br>27<br>25                   | I/O                                | Port A, PA0 – 3. This port is pin configurable and has multiple functions:  1. MCU I/O – standard output or input port  2. External chip select (ECSPLD) output, or input to GPLD  3. Latched address outputs (see Table 3)  4. As Address A0-3 inputs in 80C51XA mode  5. As Data Bus Port (D0–3) in non-multiplexed bus configuration  6. Peripheral I/O mode |

| PA4<br>PA5<br>PA6<br>PA7                               | 24<br>23<br>22<br>21                   | I/O<br>CMOS<br>or<br>Open<br>Drain | Port A, PA4−7. This port is pin configurable and has multiple functions:  1. MCU I/O – standard output or input port  2. GPLD Micro⇔Cell (McellAB) output or input  3. Latched address outputs (see Table 3)  4. As Data Bus Port (D4−7) in non-multiplexed bus configuration  5. Peripheral I/O mode                                                           |

| PB0<br>PB1<br>PB2<br>PB3                               | 7<br>6<br>5<br>4                       | I/O                                | Port B, PB0-3. This port is pin configurable and has multiple functions:  1. MCU I/O – standard output or input port  2. External chip select (ECSPLD) output, or input to GPLD  3. Latched address outputs (see Table 3)  4. As Data Bus Port (D8-11) in non-multiplexed bus configuration with 16-bit data bus                                                |

| PB4<br>PB5<br>PB6<br>PB7                               | 3<br>2<br>52<br>51                     | I/O<br>CMOS<br>or<br>Open<br>Drain | Port B, PB4-7. This port is pin configurable and has multiple functions:  1. MCU I/O – standard output or input port  2. GPLD Micro⇔Cell (McellAB) output or input  3. Latched address outputs (see Table 3)  4. As Data Bus Port (D12-15) in non-multiplexed bus configuration with 16-bit data bus                                                            |

| PC0<br>PC1<br>PC3<br>PC4<br>PC5<br>PC6<br>PC7<br>(WRH) | 20<br>19<br>17<br>14<br>13<br>12<br>11 | I/O<br>CMOS<br>or<br>Open<br>Drain | Port C, PC0, PC1, PC3−7. This port is pin configurable and has multiple functions:  1. MCU I/O – standard output or input port  2. GPLD Micro⇔Cell (McellC) output or input  3. PC7 pin only (WRH), Write strobe input for high byte. Active low, for 16-bit MCU with WRH                                                                                       |

| PC2<br>(Vstby)                                         | 18                                     | I                                  | Port C pin PC2. Dedicated SRAM Standby Voltage Input. Pin should be grounded if Vstby is not required.                                                                                                                                                                                                                                                          |

Table 2.

ZPSD6XX(V) Pin

Descriptions

(cont.)

| Pin Name        | Pin           | Туре | Function Description                                                                                                                                                                                                |

|-----------------|---------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

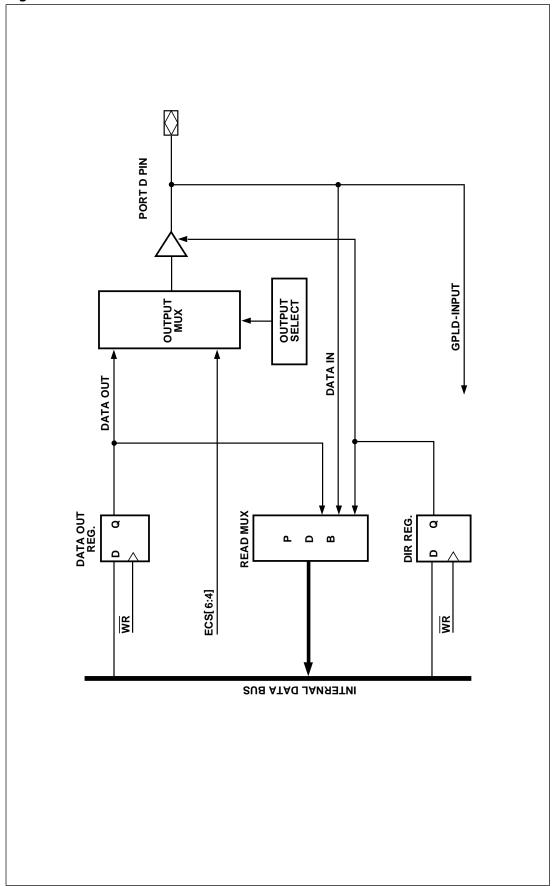

| PD0<br>(ALE)    | 10            | I/O  | Port D Pin PD0 can be configured as:  1. ALE input - latches addresses on ADIO0–15 pins  2. MCU I/O  3. GPLD input  4. ECSPLD output                                                                                |

| PD1<br>(CLKIN)  | 9             | I/O  | Port D Pin PD1 can be configured as:  1. MCU I/O  2. GPLD input  3. External chip select (ECSPLD) output  4. CLKIN clock input − clock input to the GPLD Micro⇔Cells, the APD power down counter and GPLD AND Array |

| PD2<br>(CSI)    | 8             | I/O  | Port D Pin PD2 can be configured as:  1. MCU I/O  2. GPLD input  3. External (ECSPLD) output  4. CSI input – When low, the CSI enables the PSD EPROM/SRAM. When high, the EPROM/SRAM are disabled to conserve power |

| V <sub>CC</sub> | 15<br>38      |      | Power pins                                                                                                                                                                                                          |

| GND             | 1<br>16<br>26 |      | Ground pins                                                                                                                                                                                                         |

Table 3. I/O Port Latched Address Output Assignments\*

| Microcontroller                 | Port A (3:0)  | Port A (7:4)  | Port B (3:0)   | Port B (7:4)    |

|---------------------------------|---------------|---------------|----------------|-----------------|

| 8051XA (8-Bit)                  | N/A           | Address [7:4] | Address [11:8] | N/A             |

| 80C251<br>(Page Mode)           | N/A           | N/A           | Address [11:8] | Address [15:12] |

| All Other 8-Bit<br>Multiplexed  | Address [3:0] | Address [7:4] | Address [3:0]  | Address [7:4]   |

| 8051XA (16-Bit)                 | N/A           | Address [7:4] | Address [11:8] | Address [15:12] |

| All Other 16-Bit<br>Multiplexed | Address [3:0] | Address [7:4] | Address [11:8] | Address [15:12] |

| 8-bit<br>Non-Multiplexed<br>Bus | N/A           | N/A           | Address [3:0]  | Address [7:4]   |

N/A = Not Applicable

<sup>\*</sup>Refer to the I/O Port Section on how to enable the Latched Address Output function.

ZPSD6XX(V) Register Description and Address Offset Tables 4 and 4A show the offset address to the ZPSD6XX(V)registers relative to the CSIOP base address. The CSIOP space is the 256 bytes of address that is allocated by the user to the internal ZPSD6XX(V) registers. Some Motorola 16-bit microcontrollers, including the M68HC16, M68302 and M683XX, have a different data byte orientation requiring separate address offset maps.

Table 4 shows the CSIOP address offsets for all MCUs except those from Motorola in 16-bit mode. Table 4A shows the address offsets for Motorola MCUs in 16-bit mode.

Table 4. Register Address Offset

| Register Name        | Port A | Port B | Port C | Port D | Other * | Description                                                                              |

|----------------------|--------|--------|--------|--------|---------|------------------------------------------------------------------------------------------|

| Data In              | 00     | 01     | 10     | 11     |         | Reads Port pin as input,<br>MCU I/O input mode                                           |

| Control              | 02     | 03     |        |        |         | Selects mode between MCU I/O or Address Out                                              |

| Data Out             | 04     | 05     | 12     | 13     |         | Stores data for output<br>to Port pins, MCU I/O<br>output mode                           |

| Direction            | 06     | 07     | 14     | 15     |         | Configures Port pin as input or output                                                   |

| Drive                | 08     | 09     | 16     | 17     |         | Configures Port pin<br>between CMOS,<br>Open Drain and<br>Slew rate                      |

| Input Micro⇔Cell     | 0A     | 0B     | 18     |        |         | Reads Input Micro⇔Cell                                                                   |

| Enable Out           | 0C     | 0D     | 1A     |        |         | Reads the status of the output enable to the I/O Port driver                             |

| Output<br>Micro⇔Cell | 20     | 20     | 21     |        |         | Read – reads output of Micro⇔Cells (McellC, McellAB) Write – loads Micro⇔cell Flip-Flops |

| PMMR0                |        |        |        |        | В0      | Power Management<br>Register 0                                                           |

| PMMR1                |        |        |        |        | B2      | Power Management<br>Register 1                                                           |

| Page                 |        |        |        |        | E0      | Page Register                                                                            |

| VM                   |        |        |        |        | E2      | 8031/PIO Configuration<br>Register                                                       |

<sup>\*</sup>Other registers that are not part of the I/O ports.

ZPSD6XX(V) Register Description and Address Offset (cont.)

Table 4A. Register Address Offset for 16-Bit Motorola Microcontrollers in 16-Bit Mode

| Register Name     | Port A | Port B | Port C | Port D | Other * | Description                                                                              |

|-------------------|--------|--------|--------|--------|---------|------------------------------------------------------------------------------------------|

| Data In           | 01     | 00     | 11     | 10     |         | Reads Port pin as input,<br>MCU I/O input mode                                           |

| Control           | 03     | 02     |        |        |         | Selects mode between<br>MCU I/O or Address Out                                           |

| Data Out          | 05     | 04     | 13     | 12     |         | Stores data for output<br>to Port pins, MCU I/O<br>output mode                           |

| Direction         | 07     | 06     | 15     | 14     |         | Configures Port pin as input or output                                                   |

| Drive             | 09     | 08     | 17     | 16     |         | Configures Port pin<br>between CMOS,<br>Open Drain and Slew rate                         |

| Input Micro⇔Cell  | 0B     | 0A     | 19     |        |         | Reads Input<br>Micro⇔Cell                                                                |

| Enable Out        | 0D     | 0C     | 1B     |        |         | Reads the status of the output enable to the I/O Port driver                             |

| Output Micro⇔Cell | 21     | 21     | 20     |        |         | Read – reads output of Micro⇔Cells (McellC, McellAB) Write – loads Micro⇔cell Flip-Flops |

| PMMR0             |        |        |        |        | B1      | Power Management<br>Register 0                                                           |

| PMMR1             |        |        |        |        | В3      | Power Management<br>Register 1                                                           |

| Page              |        |        |        |        | E1      | Page Register                                                                            |

| VM                |        |        |        |        | E3      | 8031/PIO Configuration<br>Register                                                       |

<sup>\*</sup>Other registers that are not part of the I/O ports.

### *ZPSD6XX(V) Architectural Overview*

ZPSD6XX(V) devices consist of several major functional blocks. Figure 1 shows the architecture of the ZPSD6XX(V) device family. The functions of each block are described briefly in the following sections. Many of the blocks perform multiple functions, and are user configurable.

#### **Zero Power PLDs**

The device contains three ZPLD blocks each optimized for a different function as shown in Table 5. The functional partitioning of the ZPLDs reduces power consumption, optimizes cost/performance and ease of design entry.

The Decode PLD (DPLD) is used to decode and generate chip selects for the ZPSD6XX(V) internal memory, registers and peripheral mode. The External Chip Select PLD (ECSPLD) is optimized to generate chip selects for devices external to the ZPSD6XX(V). The General Purpose PLD (GPLD) can implement user defined logic functions. The DPLD and ECSPLD have combinatorial outputs while the GPLD has 12 Output Micro⇔Cells. The ZPSD6XX(V) also has 23 Input Micro⇔Cells that can be configured as inputs to the ZPLD. The ZPLDs receive their inputs from the ZPLD Input bus and are differentiated by their output destinations, number of product terms, and Micro⇔Cells.

The ZPLDs are designed to consume minimum power by using Zero Power design techniques. The speed and power consumption of the ZPLD is controlled by the Turbo Bit in the PMMR0 Register that is set by the microcontroller.

#### I/O Ports

The ZPSD6XX(V) has 26 I/O pins divided among four ports. Each I/O pin can be individually configured to provide many functions. Ports A, B, C and D can be configured as standard MCU I/O ports, ZPLD I/O, or latched address outputs for microcontrollers using multiplexed address/data busses.

Ports A and B can also be configured as a data port for microcontrollers with a non-multiplexed bus. In these modes, Port A is connected to D0–7 and Port B to D8–15.

Table 5.

| Name                     | Abbreviation | Inputs | Outputs | Product Terms |

|--------------------------|--------------|--------|---------|---------------|

| Decode PLD               | DPLD         | 63     | 12      | 13            |

| External Chip Select PLD | ECSPLD       | 24     | 7       | 7             |

| General PLD              | GPLD         | 63     | 12      | 109           |

ZPSD6XX(V) Architectural Overview (cont.)

#### Microcontroller Bus Interface

The ZPSD6XX(V) easily interfaces with most popular eight and sixteen-bit microcontrollers with either multiplexed or non-multiplexed address/data busses. The device is configured to respond to the microcontroller control signals which are also used as inputs to the ZPLDs.

#### Memory

The ZPSD6XX(V) contains EPROM and SRAM. The EPROM densities available are 256 Kbit, 512 Kbit and 1 Mbit. The memory space is divided into eight equally-sized blocks. Each block can be located in a different address space defined by the user. The access time of the EPROM includes the address latching and DPLD decoding.

The 4 Kbit SRAM may be used as a scratch pad memory and an extension of the microcontroller SRAM. The SRAM data is retained in the event of a system power down, provided a backup battery is connected to the Vstby pin (PC2). Switching from the V<sub>CC</sub> supply to standby power occurs automatically when V<sub>CC</sub> drops below Vstby voltage.

#### Page Register

The four-bit Page Register expands the address range of the microcontroller by sixteen times. The paged address can be used as part of the address space to access external memory and peripherals or internal EPROM, SRAM and I/O.

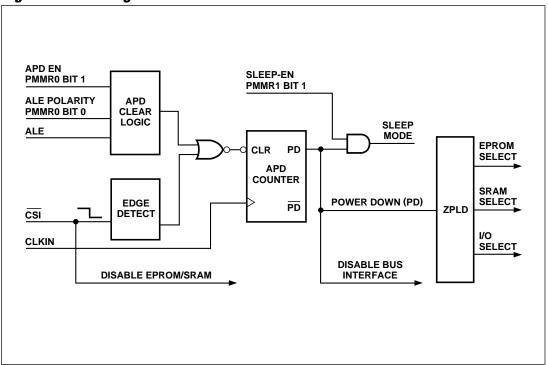

#### **Power Management Unit**

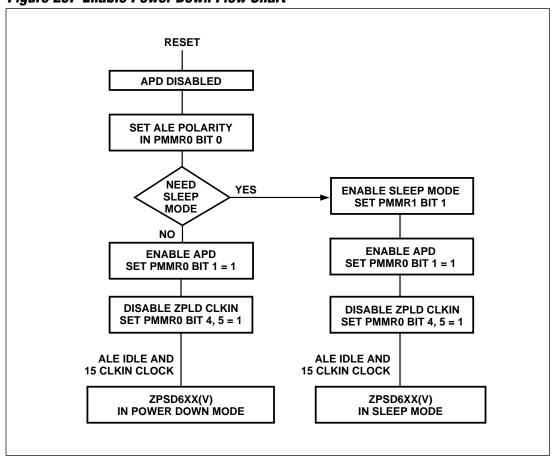

The Power Management Unit (PMU) in the ZPSD6XX(V) enables the user to control the power consumption on selected functional blocks based on system requirements. The PMU includes an Automatic Power Down unit (APD) that will turn off device functions due to microcontroller inactivity in one of two modes: the Power Down mode and Sleep mode.

Other power saving features, such as the CMiser and Turbo bits in the PMU, allow the EPROM/SRAM/ZPLD to operate at a slower rate to conserve power.

### The ZPSD6XX(V) Functional Blocks

The ZPSD6XX(V) consists of five major functional blocks:

☐ ZPLD Block

☐ Bus Interface

☐ I/O Ports

☐ Memory Block

☐ Power Management Unit

The functions of each block are described in the following sections. Many of the blocks perform multiple functions, and are user configurable.

#### **ZPLDs**

The Zero Power PLDs (ZPLDs) bring programmable logic functionality to the ZPSD6XX(V). After specifying the logic for the ZPLDs by using the PSDabel tool in PSDsoft, the logic configuration is programmed into the device and available when power is applied.

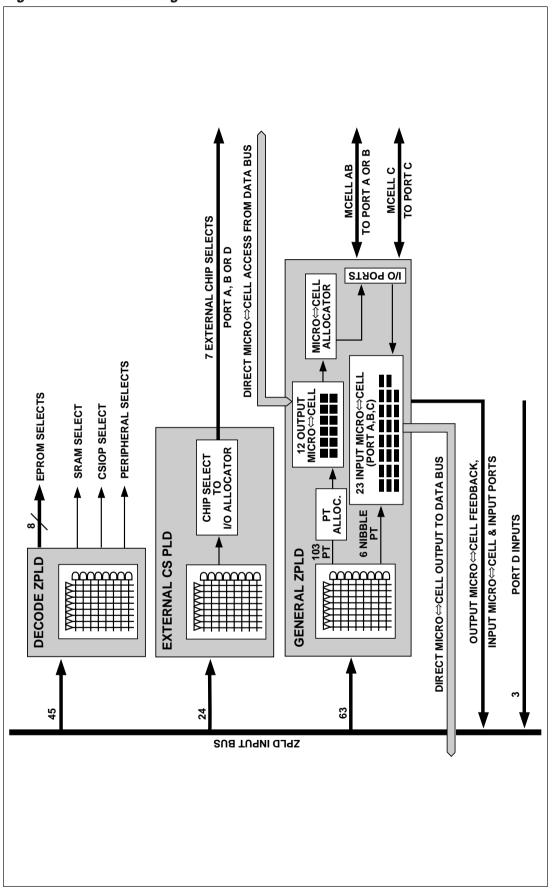

The ZPLDs (DPLD, ECSPLD and GPLD) consist of an AND array. The GPLD architecture includes 12 Output Micro⇔Cells in addition to the AND array. There are 23 Input Micro⇔Cells that can be configured as inputs to the ZPLD. Figure 4 shows the organization of the ZPLD.

The AND array is used to form product terms specified using the PSDabel tool in the PSDsoft development system. When the inputs used in a term are true, the output is active. The GPLD Input Bus consists of 63 signals as shown in Table 6. Both the true and complement value of inputs are available to the AND array. The DPLD and ECSPLD Input Busses consist of fewer inputs and are a subset of the 63 inputs.

Table 6. GPLD Inputs

| Input Source                         | Input Name                           | Number of Signals |

|--------------------------------------|--------------------------------------|-------------------|

| MCU Address Bus                      | A[15:0]*                             | 16                |

| MCU Control Signals                  | CNTL[2:0]                            | 3                 |

| Reset                                | RST                                  | 1                 |

| Power Down                           | PDN                                  | 1                 |

| I/O Ports Inputs (Input Micro⇔Cells) | PA[7:0], PB[7:0]<br>PC[7:3], PC[1:0] | 23                |

| Port D Inputs                        | PD[2:0]                              | 3                 |

| Page Register                        | PGR[3:0]                             | 4                 |

| Port A or B Micro⇔Cell Feedback      | MCELLAB.FB[7:4]                      | 4                 |

| Port C Micro⇔Cell Feedback           | MCELLC.FB[7:0]                       | 8                 |

<sup>\*</sup>NOTE: The address inputs are A[19:4] in 80C51XA mode.

Figure 4. ZPLD Block Diagram

The ZPLDs can minimize power consumption by switching off when inputs remain unchanged for an extended time of about 70ns. Setting the Turbo mode bit to off (Bit 3 of the PMMR0 register) automatically places the ZPLDs into standby if no inputs are changing. Turbo off mode increases propagation delays while reducing power consumption. Refer to the Power Management Unit on how to set up the Turbo Bit. Power is further reduced by the PSDsoft development tools which disables unused product terms.

Each of the three ZPLDs has unique characteristics suited for its applications. They are described in the following sections.

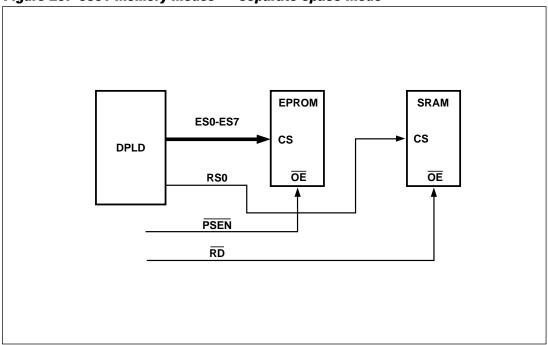

#### Decode PLD

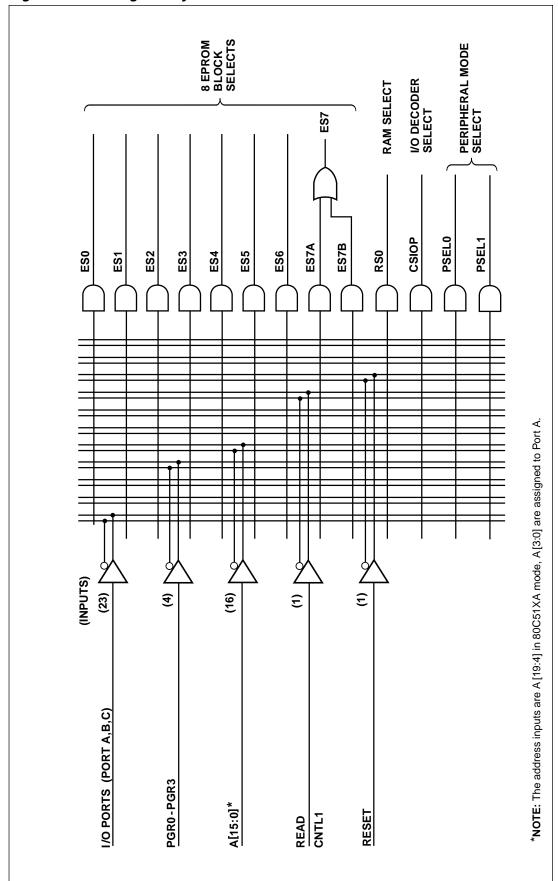

The Decode PLD (DPLD), shown in Figure 5, is used to select the internal ZPSD6XX(V) functions: EPROM blocks, SRAM, Registers (CSIOP) and the Port A Peripheral Mode. All the select signals are active high and have one product term, except ES7 which has two. The CSIOP is the select line for the ZPSD6XX(V) internal registers that occupies 256 bytes of memory space. A second level decoder selects a register based on the address inputs A[7-0].

Each EPROM block has its own chip select. The chip select of the eighth EPROM block has two product terms, ES7A and ES7B. This allows the eighth block to reside in two memory spaces, where ES7B can typically select reset vectors or configuration bytes that are stored in the MCU address space.

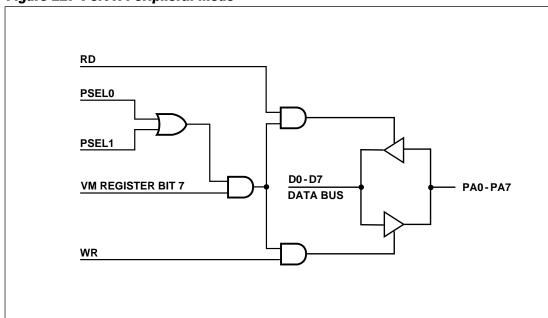

PSEL 0 & 1 are used as inputs to Port A to control the port's Peripheral I/O mode operation. Usually PSEL 0&1 are defined in term of the MCU address inputs. This mode is explained in the I/O Port section.

Table 7. DPLD Inputs

| Input Source          | Input Name                           | Number of Bits |

|-----------------------|--------------------------------------|----------------|

| MCU Address Bus       | A[15:0]*                             | 16             |

| I/O Ports A, B, and C | PA[7:0], PB[7:0]<br>PC[7:3], PC[1:0] | 23             |

| Page Register         | PGR[3:0]                             | 4              |

| Control Signal        | CNTL1 (Read)                         | 1              |

| Reset Pin             | RESET                                | 1              |

\*NOTE: The address inputs are A[19:4] in 80C51XA mode, A[3:0] are assigned to Port A.

Figure 5. DPLD Logic Array

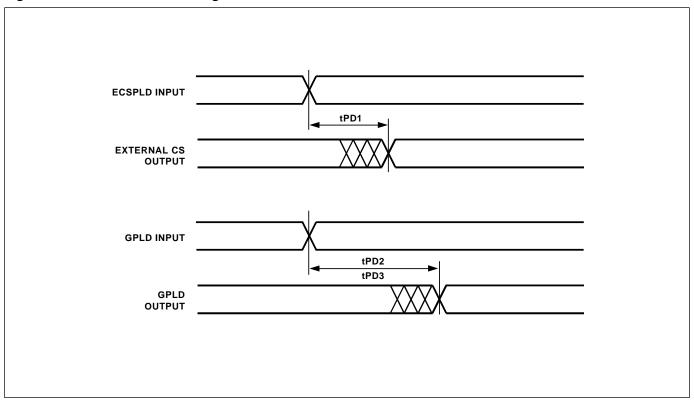

#### **External Chip Select PLD**

The External Chip Select PLD (ECSPLD) provides the means to select external devices. The output buffer of the ECSPLD can be configured to operate in high slew rate by writing a "1" to the corresponding bit in the Drive Register. The slew rate is a measurement of the rise and fall times of the output. A higher slew rate means a faster output response while a lower slew rate is a slower response. Refer to Table 25 in the I/O Section for setting up the Drive Register.

Faster transitions are more likely to cause line reflections and system noise than slower rates. Adjusting the slew rate allows a trade-off between greater speed and noise sensitivity. The selection should be based on the performance requirements of the system and its noise characteristics. Set the corresponding bits in the Drive Register to "0" (for normal speed) or "1" (for fast drive). The default value is zero.

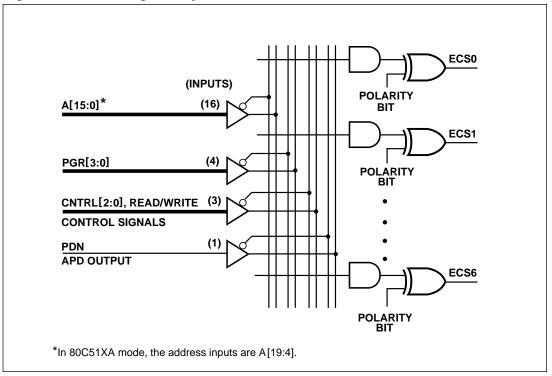

The ECSPLD has 24 inputs as shown in Table 8. Its outputs are combinatorial, of either polarity, and have one product term each as shown in Figure 6.

Table 8. ECSPLD Inputs

| r                   |            |                |  |  |  |

|---------------------|------------|----------------|--|--|--|

| Input Source        | Input Name | Number of Bits |  |  |  |

| MCU Address Bus     | A[15:0]*   | 16             |  |  |  |

| MCU Control Signals | CNTL[2:0]  | 3              |  |  |  |

| Power Down Signal   | PDN**      | 1              |  |  |  |

| Page Register       | PGR[3:0]   | 4              |  |  |  |

|                     |            |                |  |  |  |

<sup>\*</sup>In 80C51XA mode, the address inputs are A[19:4]

The seven ECSPLD outputs may be driven off the device through Ports A, B, or D, as shown in Table 9, via the Micro⇔Cell Allocator. Port selection is specified in the PSDabel file or assigned by the PSDcompiler.

Table 9. ECSPLD Output Port Assignments

| ECSPLD Output | Port A, B, or D Assignments |

|---------------|-----------------------------|

| ECS0          | PA0, PB0                    |

| ECS1          | PA1, PB1                    |

| ECS2          | PA2, PB2                    |

| ECS3          | PA3, PB3                    |

| ECS4          | PD0*                        |

| ECS5          | PD1*                        |

| ECS6          | PD2*                        |

<sup>\*</sup>Port D has no output enable (.oe) product terms for ECS4-6 outputs.

<sup>\*\*</sup>APD output. When PDN is high, the PSD6XX(V) is in power down mode

Figure 6. ECSPLD Logic Array

#### **General PLD**

The General PLD (GPLD) is used to implement system logic such as MCU loadable counters, system mailboxes or handshaking protocols. In addition the GPLD can implement random logic and state machine functions.

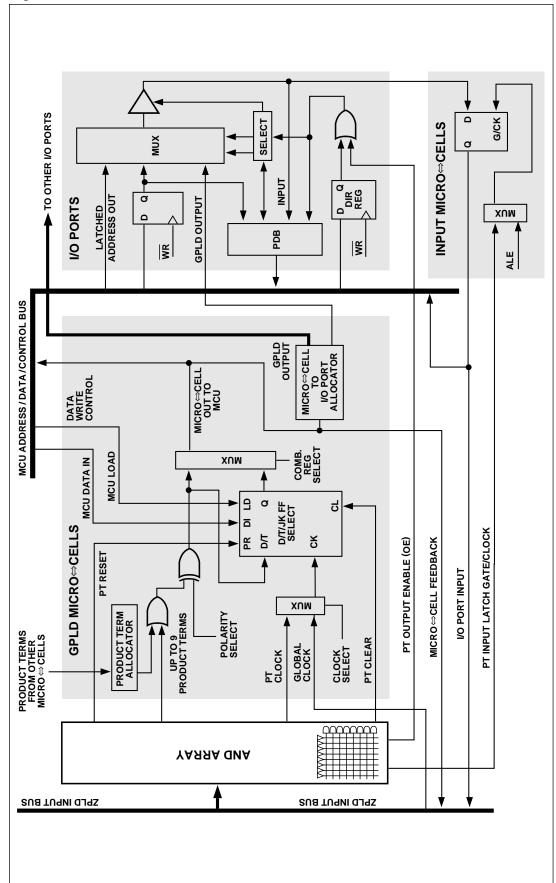

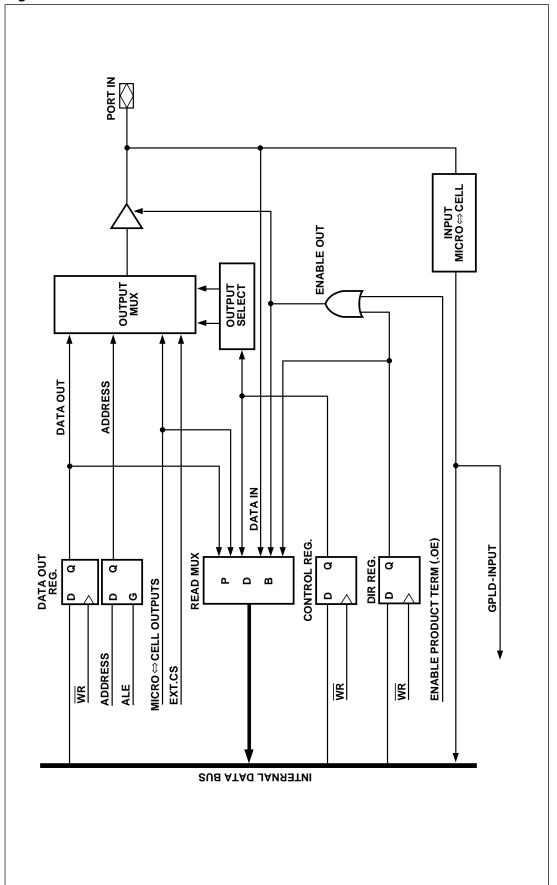

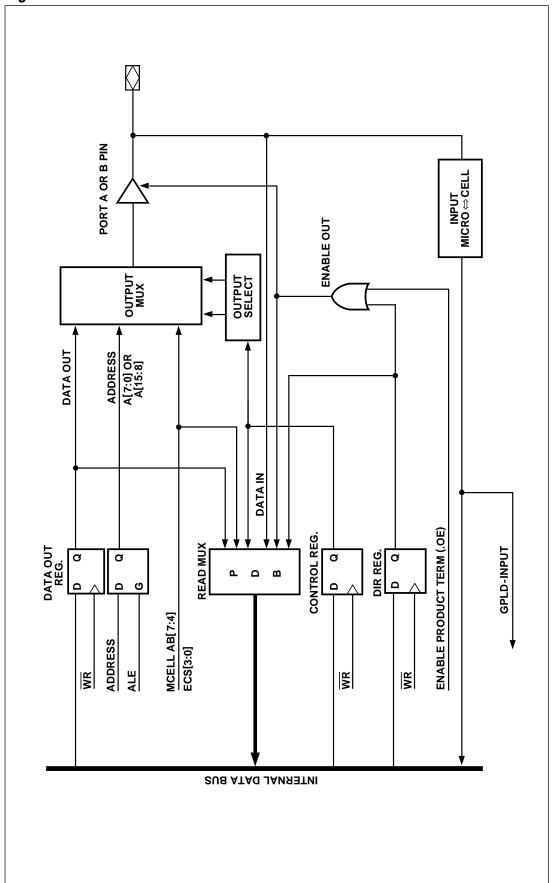

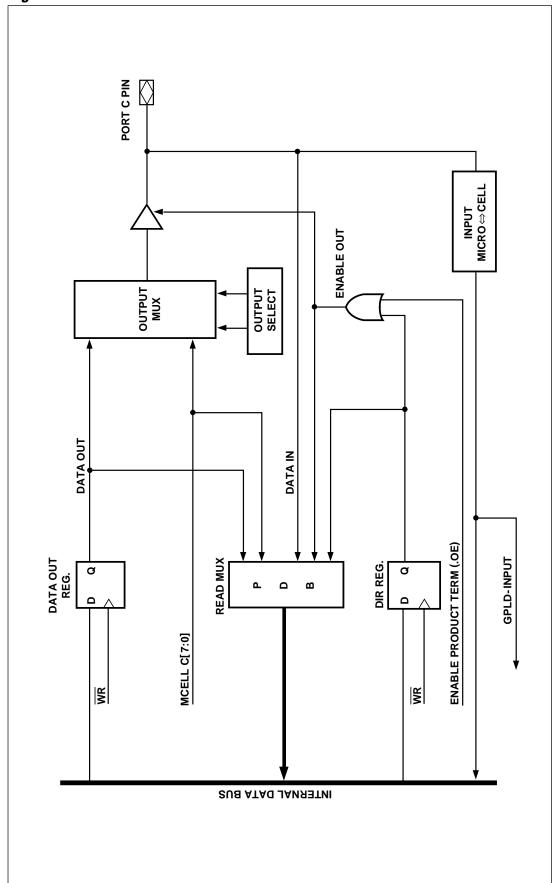

The GPLD has Output and Input Micro⇔Cells. The GPLD, Output and Input Micro⇔Cells architectures appear in Figure 7 along with the Port. The Micro⇔Cells are configured using the PSDsoft development system. Like the other ZPLDs, the GPLD has an AND array which can generate up to 109 product terms, a maximum of nine product terms for each of the twelve Micro⇔Cells.

The Input and Output Micro⇔Cells are connected to the ZPSD6XX(V) internal data bus and can be directly accessed by the microcontroller. This enables the MCU software to load data into the Output Micro⇔Cells or read data from both the Input and Output Micro⇔Cells. This feature allows efficient implementation of system logic and eliminates the need to connect the data bus to the AND logic array as required in most standard PLD macrocell architectures.

Figure 7. The GPLD and I/O Port

#### Output Micro⇔Cell

Eight of the Output Micro⇔Cells are connected to Port C pins (except PC2) and are named as McellC0-7. The remaining four Micro⇔Cells can be connected to Port A or Port B and are named as McellAB4-7. If an McellAB output is not assigned to a specific pin in PSDabel, the Micro⇔Cell Allocator will assign it to either Port A or B. Table 10 shows the Micro⇔Cells and Port assignment.

Table 10. Output Micro⇔Cell Port and Data Bit Assignments

| Output<br>Micro⇔Cell | Port<br>Assignment | Native<br>Product<br>Terms | Max<br>Borrowed<br>Product<br>Terms | Data Bit for<br>Loading or<br>Reading in<br>8-Bit Mode | Data Bit for<br>Loading or<br>Reading in<br>16-Bit Mode |

|----------------------|--------------------|----------------------------|-------------------------------------|--------------------------------------------------------|---------------------------------------------------------|

| McellC0              | Port C0            | 4                          | 5                                   | D0                                                     | D8                                                      |

| McellC1              | Port C1            | 4                          | 5                                   | D1                                                     | D9                                                      |

| McellC2              | *                  | 4                          | 5                                   | D2                                                     | D10                                                     |

| McellC3              | Port C3            | 4                          | 5                                   | D3                                                     | D11                                                     |

| McellC4              | Port C4            | 4                          | 5                                   | D4                                                     | D12                                                     |

| McellC5              | Port C5            | 4                          | 5                                   | D5                                                     | D13                                                     |

| McellC6              | Port C6            | 4                          | 5                                   | D6                                                     | D14                                                     |

| McellC7              | Port C7            | 4                          | 5                                   | D7                                                     | D15                                                     |

| McellAB4             | Port A4, B4        | 3                          | 6                                   | D4                                                     | D4                                                      |

| McellAB5             | Port A5, B5        | 3                          | 6                                   | D5                                                     | D5                                                      |

| McellAB6             | Port A6, B6        | 3                          | 6                                   | D6                                                     | D6                                                      |

| McellAB7             | Port A7, B7        | 3                          | 6                                   | D7                                                     | D7                                                      |

<sup>\*</sup>Internal node only.

#### The Product Term Allocator

All Micro⇔Cells have the same basic cell architecture except McellC has four native product terms and McellAB has three product terms. The GPLD also has a Product Term Allocator with which the PSDcompiler can automatically borrow product terms from one Micro⇔Cell to another. The McellC may borrow up to five product terms from other Micro⇔Cells for a total of nine product terms. The McellAB has three native product terms and can borrow up to six product terms. Borrowing allows Micro⇔Cell outputs needing more product terms to use the unused product terms of others.

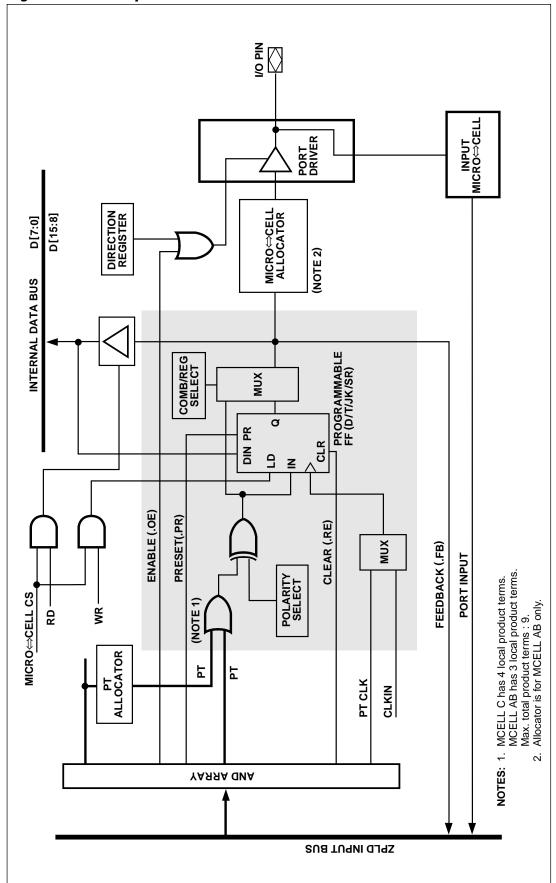

The architecture of the 12 Output Micro⇔Cells, as shown in Figure 8, consists of native product terms and borrowed product terms from other Micro⇔Cells. The polarity of the product term input is controlled by the XOR gate. The Micro⇔Cell can implement either sequential logic, using the Flip-Flop element, or combinatorial functions. The multiplexer selects the combinatorial or the sequential logic as the Micro⇔Cell output. The multiplexer output can drive a Port pin and has also a feedback path to the AND array inputs.

#### Micro⇔Cell Flip-Flop Type

The Flip-Flop in the Micro⇔Cell can be configured as a D, Toggle, JK or SR type by using PSDabel in PSDsoft. The Flip-Flop Clock, Preset and Clear inputs are driven from a product term of the AND array. Alternatively, the device clock input (CLKIN) can be used for the Flip-Flop. The Preset and Clear are active high inputs; the Flip-Flop is clocked by the rising edge of the clock input.

Figure 8. GPLD Output Micro⇔Cell

#### Loading and Reading the Micro⇔Cells

The GPLD Micro⇔Cells occupy a memory location in the MCU address space as defined by the CSIOP (refer to the I/O section). The Flip-Flops in each of the 12 Micro⇔Cells can be loaded from the data bus by a microcontroller write bus cycle to the Micro⇔Cell (see I/O Port section for Micro⇔Cell Addresses). A "1" in the data bit that associates with the Micro⇔Cell will load a "1" to the Flip-Flop, a "0" in the data bit will load a "0" to the Flip-Flop. The loading bus cycle takes priority over other Flip-Flop inputs that include the Preset, Clear and clock. See Table 11 for the data bits that are connected to the Micro⇔Cells. The ability to load the Flip-Flops and read them back is useful in such applications as loadable counters, shift registers, mailboxes or handshaking protocols.

Table 11. Micro⇔Cell Flip-Flop Loading

| LD | Din | CIk | In    | PR             | CLR     | Q |

|----|-----|-----|-------|----------------|---------|---|

| 1  | 1   | Х   | Х     | Х              | Х       | 1 |

| 1  | 0   | Х   | Х     | Х              | Х       | 0 |

| 0  | Х   |     | Norma | l Flip-Flop Fu | ınction |   |

NOTE: LD is "1" when the MCU writes to the Micro⇔Cell address

#### The Output Enable

The Micro⇔Cell can be connected to a ZPSD6XX(V) I/O pin as PLD output. The output enable of each of the Port pin output driver is controlled by a single product term (.oe) from the AND array ORed with the Direction Register output. Upon power up, if no output enable (.oe) equation is defined and the pin is declared as a ZPLD output in PSDsoft, the pin is enabled.

If the Micro⇔Cell output is declared as internal node and not as Port pin output in the PSDabel file, then the Port pin can be used for other I/O functions. The internal node feedback can be routed as an input to the AND array.

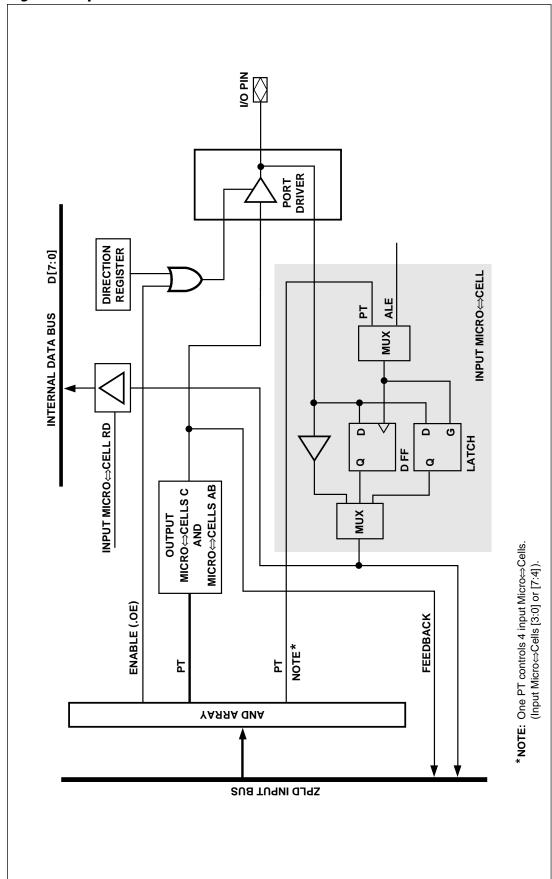

#### *Input Micro⇔Cell*

The Input Micro⇔Cells as shown in Figure 9 are used to latch, register or pass incoming Port signals prior to driving them onto the ZPLD Input bus. The outputs of these Micro⇔Cells can also be read by the microcontroller through the internal Data Bus. The GPLD has 23 Input Micro⇔Cells, one for each pin of Ports A, B and C (except PC2). The Input Micro⇔Cells are individually configurable.

The enable/clock for the latch and Flip-Flop is driven by a multiplexer whose inputs are a product term from the GPLD AND array and the MCU address strobe (ALE). Each product term output is used to latch/clock four Input Micro⇔Cells. Port inputs [3:0] can be controlled by one product term and [7:4] can be controlled by another one.

The Input Micro⇔Cell configurations are specified by equations written in PSDabel. Outputs of the Micro⇔Cells can be read by the microcontroller via the "Input Micro⇔Cell" buffer. See the I/O Port section on how to read the Micro⇔Cells.

Input Micro⇔Cells can use the ALE to latch the higher address bits (A31 – A16). The latched addresses are routed to the ZPLD as inputs.

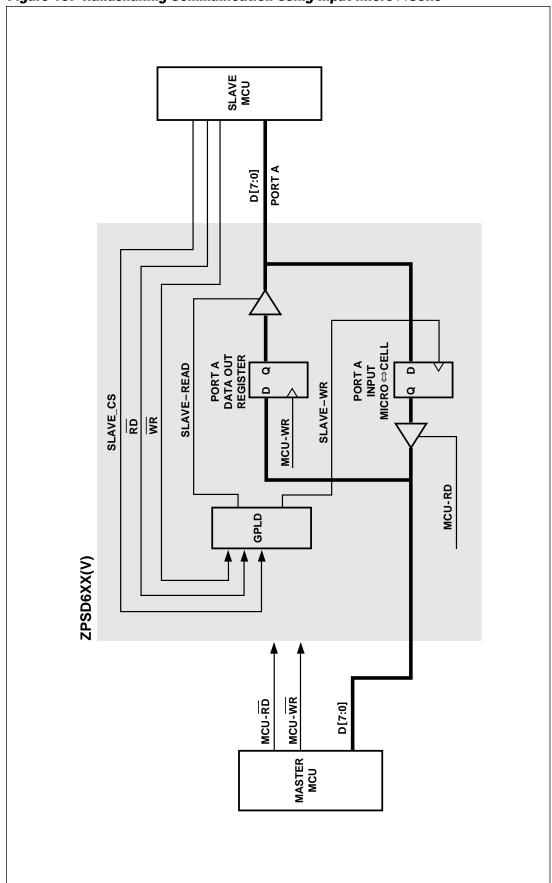

The Input Micro⇔Cell is particularly useful in handshaking communication applications where two processors wish to pass data between each other through a commonly accessible storage. Figure 10 shows a typical configuration where the Master MCU writes to the Port A Data Out Register that is read by the Slave MCU via the activation of the Slave-Read output enable product term. The Slave MCU can write to Port A Input Micro⇔Cells by activating the Slave-WR product term. The Master MCU can then read the Input Micro⇔Cells. The Slave-Read and Slave-WR signals are product terms that are derived from the Slave MCU signals RD, WR, and Slave\_CS.

Figure 9. Input Micro⇔Cell

Figure 10. Handshaking Communication Using Input Micro⇔Cells

#### Bus Interface

The "no-glue logic" ZPSD6XX(V) Microcontroller Bus Interface can be directly connected to the most popular microcontrollers. Some of these microcontrollers with their bus types and control signals are shown in Table 12. The interface type is specified using the PSDsoft tools.

Table 12. Microcontroller Busses and Control Signals

| MCU            | Data Bus | CNTLO            | CNTL1 | CNTL2 | PC7 | PD0** | ADI00  | PA3-PA0 |

|----------------|----------|------------------|-------|-------|-----|-------|--------|---------|

| 8031           | 8        | WR               | RD    | PSEN  | *   | ALE   | A0     | *       |

| 68330          | 8        | R/W              | DS    | *     | *   | ALE   | A0     | *       |

| 80198          | 8        | $\overline{WR}$  | RD    | *     | *   | ALE   | A0     | *       |

| 68HC11         | 8        | R/W              | Е     | *     | *   | AS    | A0     | *       |

| 80C51XA        | 8        | $\overline{WR}$  | RD    | PSEN  | *   | ALE   | A4     | A3-A0   |

| 80C251         | 8        | $\overline{WR}$  | PSEN  | *     | *   | ALE   | A0     | *       |

| 80C251         | 8        | $\overline{WR}$  | RD    | PSEN  | *   | ALE   | A0     | *       |

| Z8             | 8        | $R/\overline{W}$ | DS    | *     | *   | AS    | A0     | *       |

| Neuron<br>3150 | 8        | R/W              | DS    | *     | *   | *     | A0     | *       |

| 80196          | 16       | WRL              | RD    | BHE   | *   | ALE   | A0     | *       |

| 80196          | 16       | WRL              | RD    | *     | WRH | ALE   | A0     | *       |

| 68HC12***      | 16       | $R/\overline{W}$ | Е     | A0    | *   | _     | LSTRB  | *       |

| 68302          | 16       | $R/\overline{W}$ | LDS   | UDS   | *   | AS    | _      | *       |

| 68330          | 16       | $R/\overline{W}$ | DS    | BHE   | *   | AS    | A0/BLE | *       |

| 68332          | 16       | R/W              | DS    | SIZ0  | *   | AS    | A0     | *       |

| 80C51XA        | 16       | WRL              | RD    | PSEN  | WRH | ALE   | A4/D0  | A3-A1   |

| 68LC302        | 16       | WEL              | ŌĒ    |       | WEH | AS    |        | *       |

| 80186          | 16       | WR               | RD    | BHE   | *   | ALE   | A0     | *       |

| 80C166         | 16       | $\overline{WR}$  | RD    | BHE   | *   | ALE   | A0     | *       |

<sup>\*</sup>Not used CNTL2 pin can be configured as GPLD input. Other not used pins (PC7, PD0, PA3-0) can be configured for other I/O functions.

Table 12 shows the names of the ZPSD6XX(V) bus interface control pins and their functions. The control pins have multiple functions and can be configured to interface to many microcontrollers. Depending on the microcontroller, some of the control input pins are not required and may be used as GPLD input or other I/O functions. Specific examples of interfaces to different microcontrollers are provided in the following sections. For microcontrollers that have more than 16 address lines, Port A, B, or C pins may be used as additional address inputs.

<sup>\*\*</sup>ALE/AS input is optional for microcontrollers with a non-multiplexed bus.

<sup>\*\*\*</sup>This configuration is for the 68HC12 with non-mux bus.

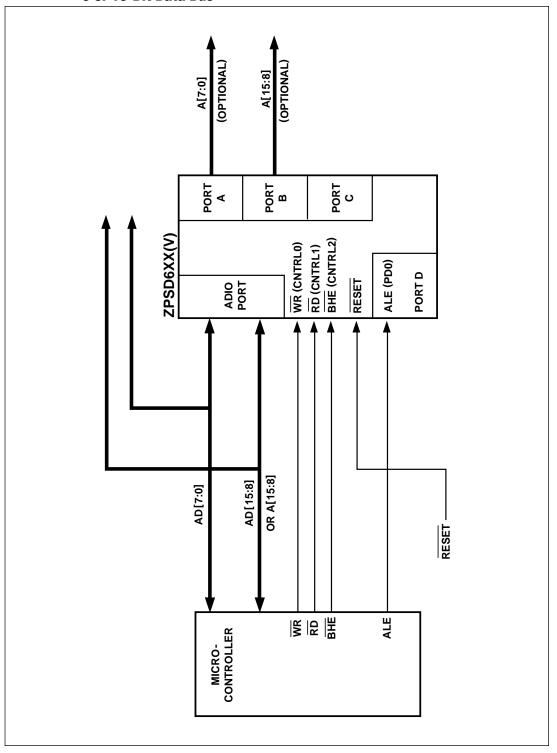

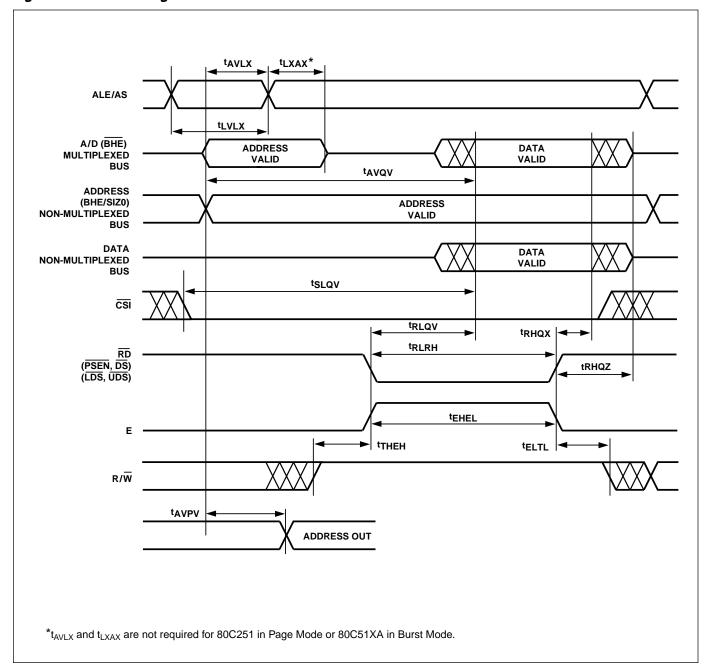

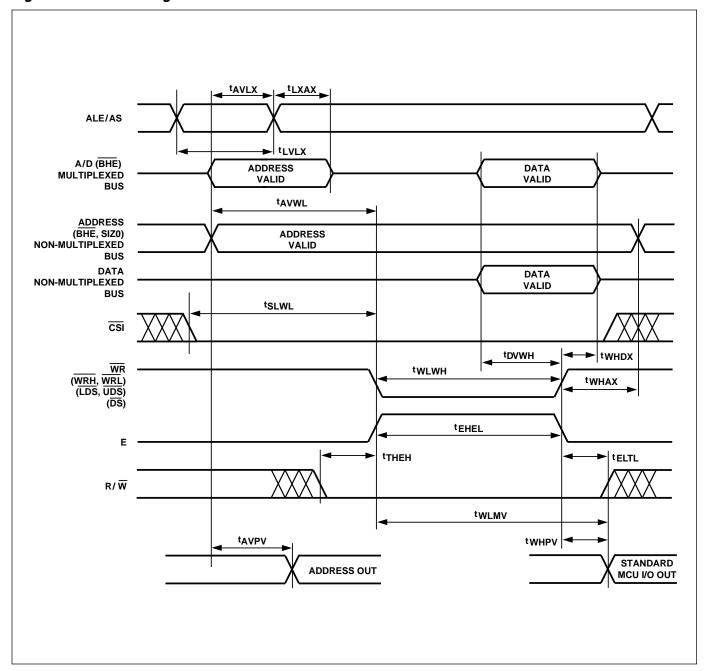

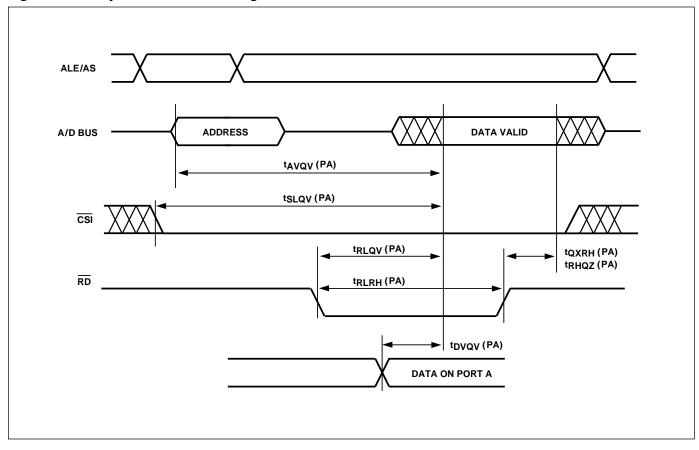

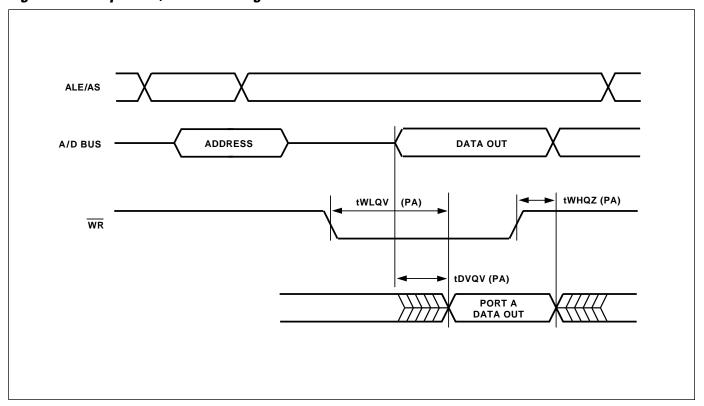

### **ZPSD6XX(V)** Interface To a Multiplexed Bus

Figure 11 shows an example of a system using a microcontroller with a multiplexed bus and a ZPSD6XX(V). The ADIO port on the ZPSD6XX(V) is connected directly to the microcontroller address/data bus. The bus may be multiplexed only on one byte (eight-bit data) or on both bytes (sixteen-bit data). The ALE latches the address lines internally; latched addresses can be brought out to Port A or B. The ZPSD6XX(V) drives the ADIO data bus only when one of its internal resources is accessed and the RD input is active.

Figure 11. An Example of a Typical Multiplexed Bus Interface, 8 or 16-Bit Data Bus

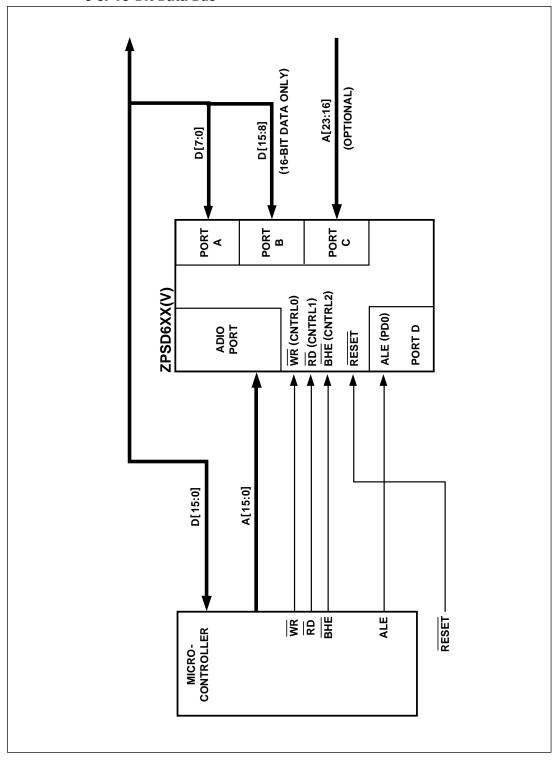

### **ZPSD6XX(V)** Interface To a Non-Multiplexed Bus

Figure 11 shows an example of a system using a microcontroller with a non-multiplexed bus and a ZPSD6XX(V). The address bus is connected to the ADIO Port, and the data bus is connected to Port A (D[7:0]) and to Ports B (D[15:8], 16-bit data bus only). The data Ports are in a tri-state mode when the ZPSD6XX(V) is not accessed by the microcontroller. Should the system address bus exceed sixteen bits, Port A, B, or C may be used as additional address inputs.

Figure 12. An Example of a Typical Non-Multiplexed Bus Interface, 8 or 16-Bit Data Bus

#### Data Byte Enable Reference

Microcontrollers have different data byte orientations. The following tables show how the ZPSD6XX(V) interprets byte/word operation in different write bus configurations. Even-byte refers to locations with address A0 equal to zero and odd byte as locations with A0 equal to one.

Table 13. 8-Bit Data Bus

| BHE | A0 | D7 – D0   |

|-----|----|-----------|

| Х   | 0  | Even Byte |

| X   | 1  | Odd Byte  |

Table 14. 16-Bit Data Bus With BHE

| BHE | AO | D15 – D8 | D7 – D0   |

|-----|----|----------|-----------|

| 0   | 0  | Odd Byte | Even Byte |

| 0   | 1  | Odd Byte | _         |

| 1   | 0  | _        | Even Byte |

Table 15. 16-Bit Data Bus With WRH and WRL

| WRH | WRL | D15 – D8 | D7 – D0   |

|-----|-----|----------|-----------|

| 0   | 0   | Odd Byte | Even Byte |

| 0   | 1   | Odd Byte | _         |

| 1   | 0   | _        | Even Byte |

Table 16. 16-Bit Data Bus With SIZO, AO (Motorola MCU)

| SIZO | AO | D15 – D8  | D7 – D0  |

|------|----|-----------|----------|

| 0    | 0  | Even Byte | Odd Byte |

| 1    | 0  | Even Byte | _        |

| 1    | 1  | _         | Odd Byte |

Table 17. 16-Bit Data Bus With UDS, LDS (Motorola MCU)

| LDS | UDS | D15 – D8  | D7 – D0  |

|-----|-----|-----------|----------|

| 0   | 0   | Even Byte | Odd Byte |

| 1   | 0   | Even Byte | _        |

| 0   | 1   | -         | Odd Byte |

#### Microcontroller Interface Examples

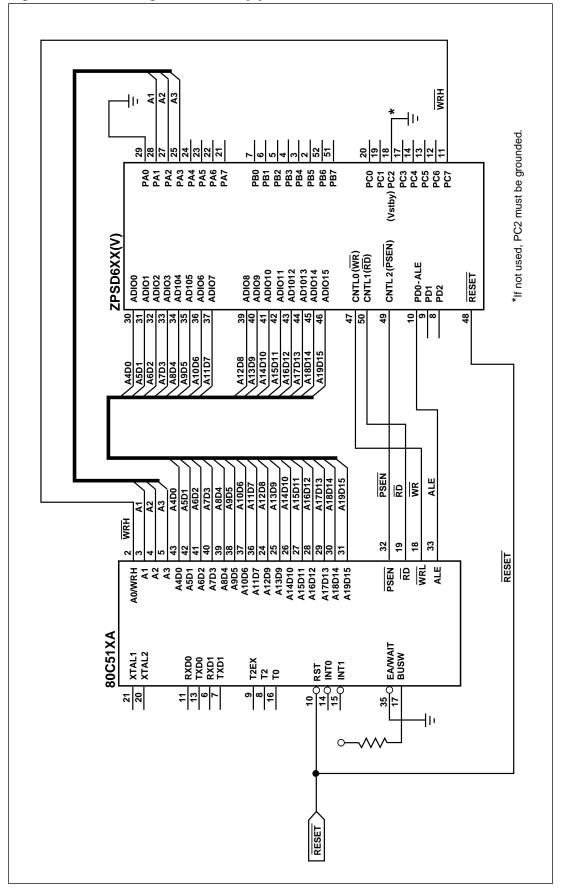

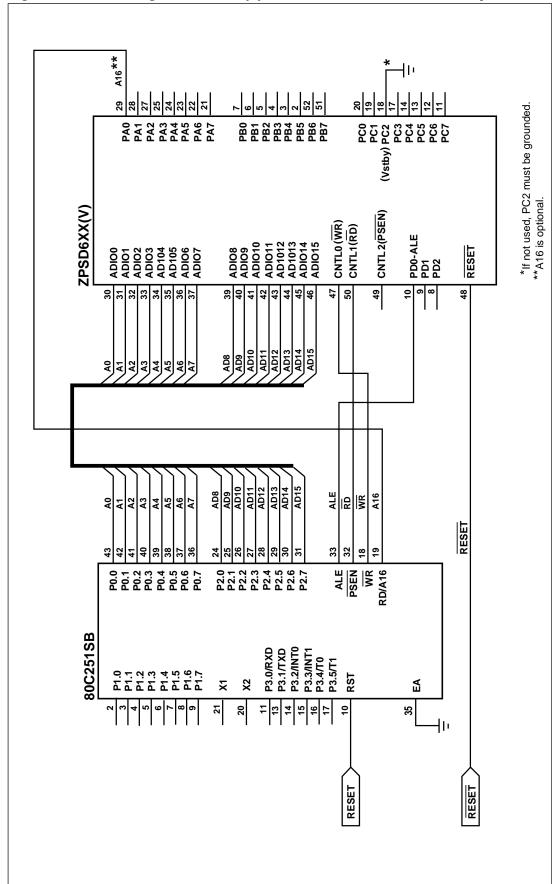

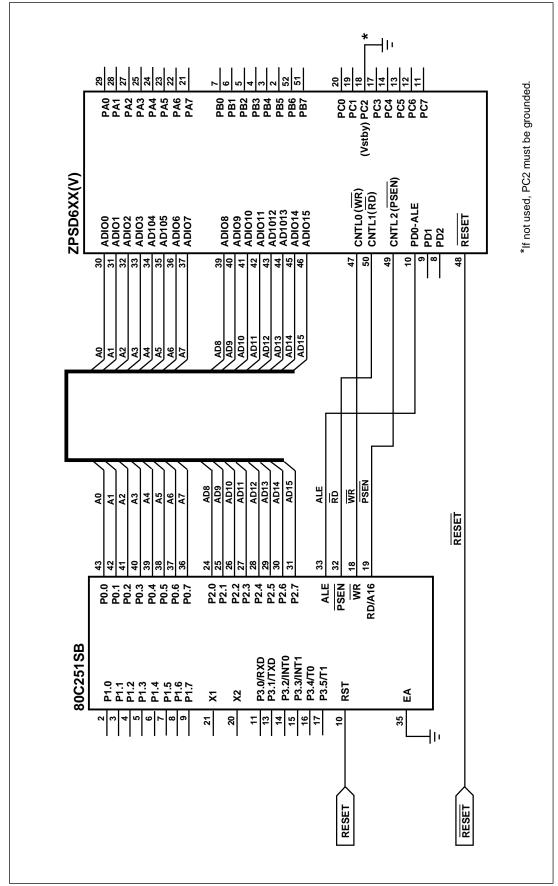

Figures 13 through 20 show examples of the basic connections between the ZPSD6XX(V) and some popular microcontrollers. The ZPSD6XX(V) control input pins are labeled as the microcontroller function for which they are configured. The MCU interface is specified using the PSDsoft tools. The PC2 pin should be grounded if Vstby is not used.

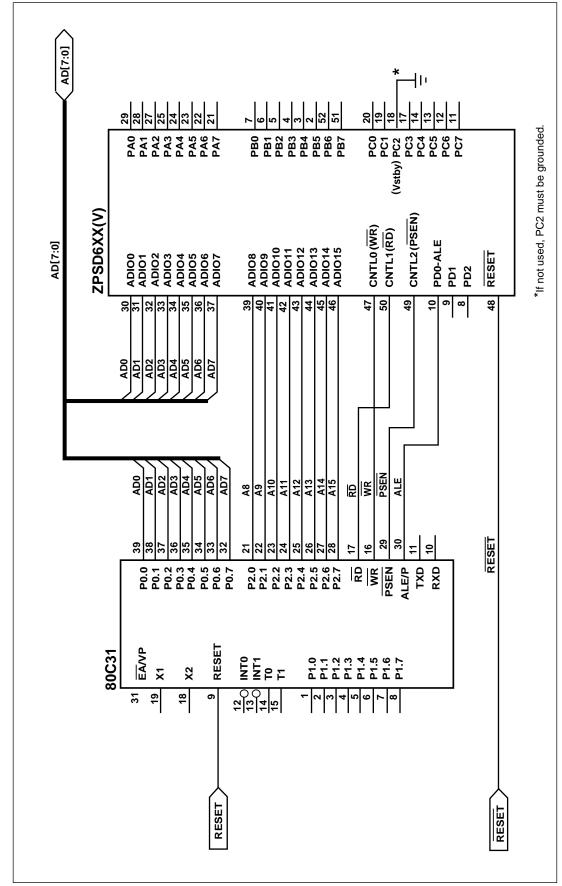

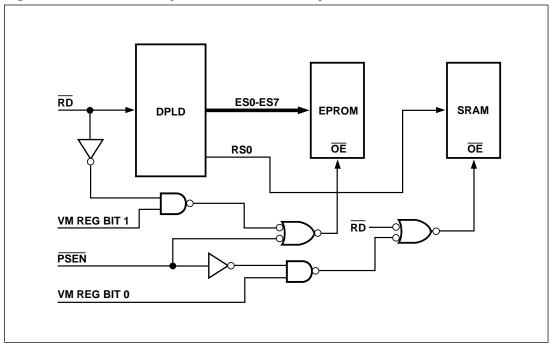

#### 80C31

Figure 13 shows the interface to the 80C31 which has an 8-bit multiplexed address/data bus. The lower address byte is multiplexed with the data bus. The microcontroller RD and WR signals may be used for accessing internal SRAM and I/O Ports while the PSEN signal is used to read the EPROM. The ALE input (Port D PD0) latches the address. Refer to the Memory Section for additional 80C31 operating modes.

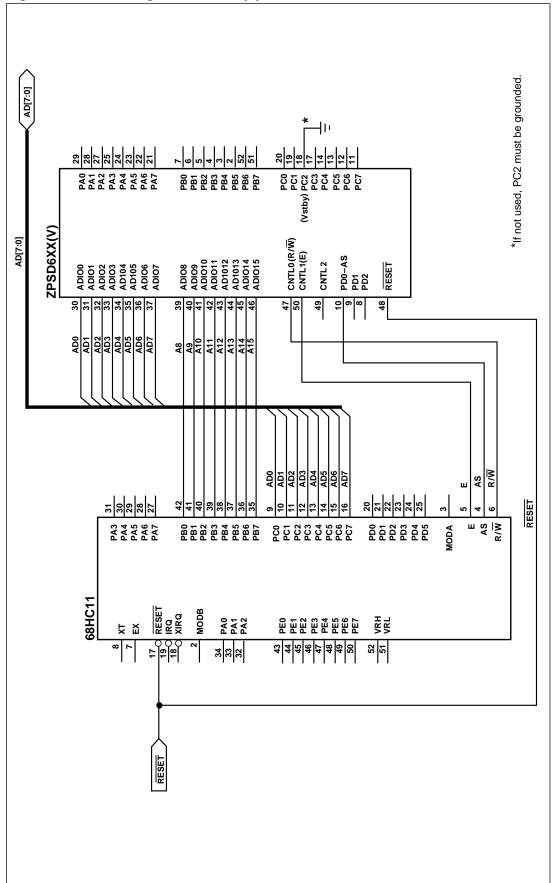

#### 68HC11

Figure 14 shows an interface to an 68HC11 where the ZPSD6XX(V) is configured in 8-bit multiplexed mode with E and R/W settings. The ECSPLD can generate the READ and WR signals for external on board devices. The CNTL2 pin is not used and can be used as a ZPLD input.

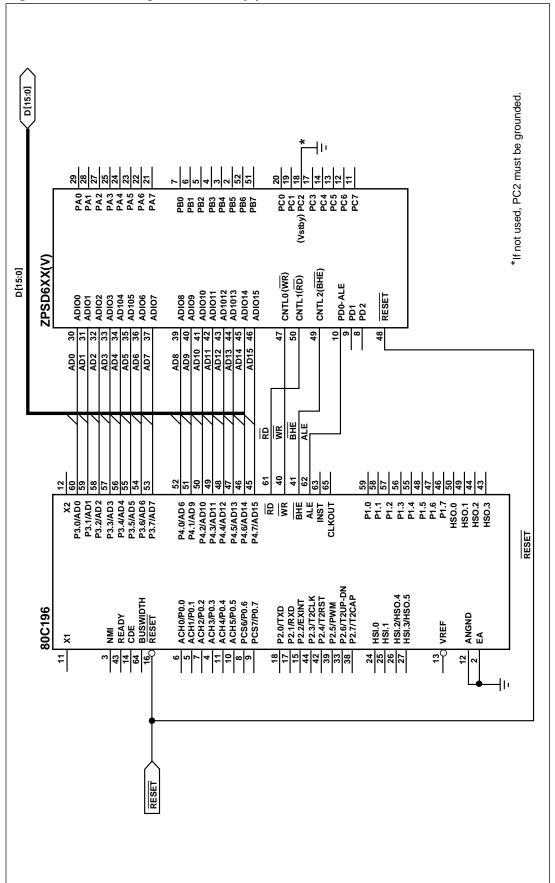

#### 80C196

In Figure 15, the Intel 80C196 microcontroller, which has a multiplexed sixteen-bit bus, is shown connected to a ZPSD6XX(V). The BHE signal is used for high data byte selection. Port pins can be configured in the PSDabel as ZPLD outputs to control the READY and BUSWIDTH pins of the 80C196.

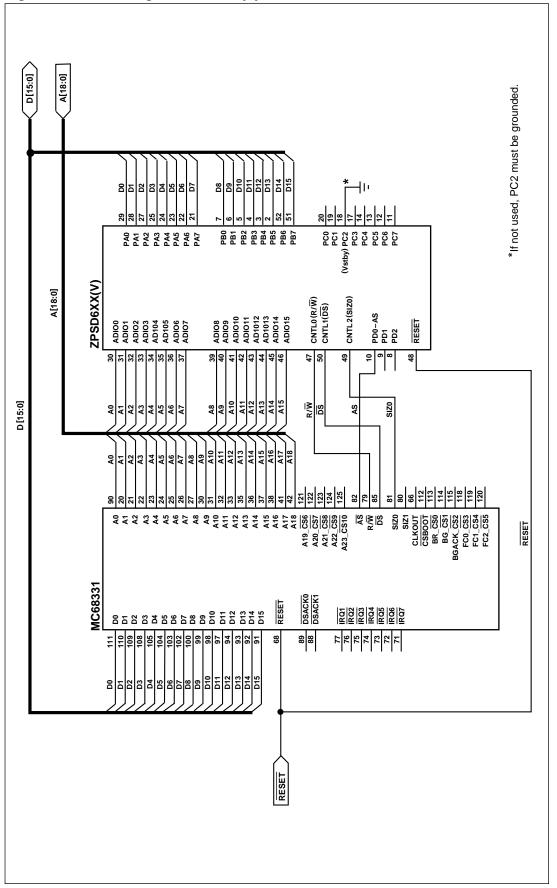

#### MC68331

Figure 16 shows a Motorola MC68331 with non-multiplexed sixteen-bit data bus and 24-bit address bus. The data bus from the MC68331 is connected to Port A (D0-7) and Port B (D8-15). The SIZ0 and A0 inputs determine the high/low byte selection.

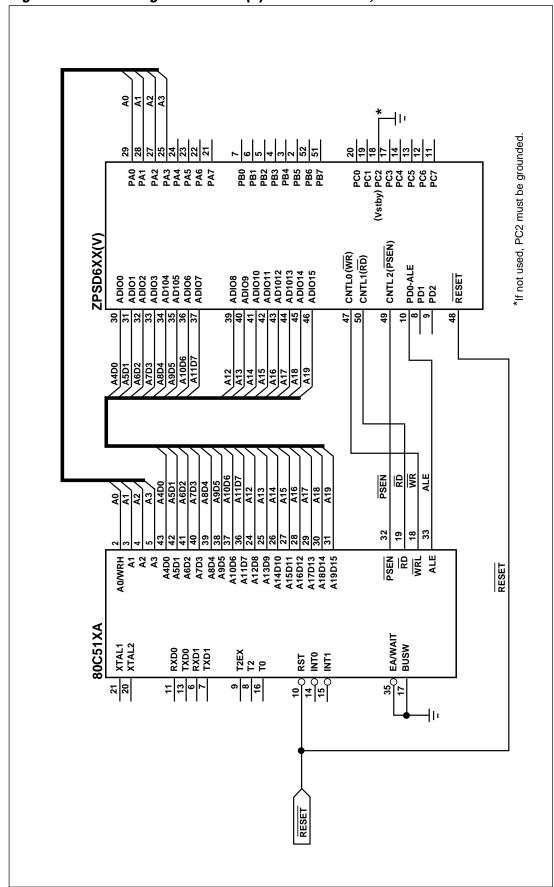

#### 80C51XA

The Philips 80C51XA microcontroller family has an 8 or 16 bit multiplexed bus that supports burst cycles. Address bits A[3:0] are not multiplexed while A[19:4] are multiplexed with data bits D[15:0] in 16-bit mode. In 8-bit mode, A[11:4] are multiplexed with data bits D[7:0].

The 80C51XA can be configured to operate with a ZPSD6XX(V) in an 8-bit (shown in Figure 17) or 16-bit (shown in Figure 18) data mode. With a 16-bit data bus, the 80C51XA's WRH pin is connected to the PC7 pin on the ZPSD6XX(V). Pin PA0 is grounded and not used.

The 80C51XA improves bus throughput and performance by executing Burst cycles to fetch codes from memory. In Burst cycles, address A19–4 are latched internally by the ZPSD6XX(V), while the 80C51XA changes the A3–0 lines to sequentially fetch up to 16 bytes of code. The PSD access time is then measured from address A3–A0 valid to data in valid. The ZPSD6XX(V) bus timing requirement in Burst cycle is identical to the normal bus cycle except the address set up or hold time with respect to ALE is not required.

#### *80C251*

The Intel 80C251 microcontroller features a user-configurable bus interface with four possible bus configurations as shown in Table 18.

Table 18. 80C251 Configurations

| Configuration | 80C251<br>Read/Write<br>Pins | Connecting<br>to PSD6XX(V)<br>Pins | Page Mode                                                    |

|---------------|------------------------------|------------------------------------|--------------------------------------------------------------|

| 1             | WR<br>RD<br>PSEN             | CNTL0<br>CNTL1<br>CNTL2            | Non-Page Mode, 80C31 compatible A[7:0] multiplex with D[7:0} |

| 2             | WR<br>PSEN only              | CNTL0<br>CNTL1                     | Non-Page Mode<br>A[7:0] multiplex with D[7:0}                |

| 3             | WR<br>PSEN only              | CNTL0<br>CNTL1                     | Page Mode<br>A[15:8] multiplex with D[7:0}                   |

| 4             | WR<br>RD<br>PSEN             | CNTL0<br>CNTL1<br>CNTL2            | Page Mode<br>A[15:8] multiplex with D[7:0}                   |

Configuration 1 is 80C31 compatible. The bus interface to the ZPSD6XX(V) is identical to that shown in Figure 13. Configurations 2 and 3 have the same bus connection as shown in Figure 19. There is only one read input (PSEN) connected to the CNTL1 pin on the ZPSD6XX(V). The A16 connection to the PA0 pin allows for a larger address input to the ZPSD6XX(V). Configuration 4 is shown in Figure 20. The RD signal is connected to CNTL1 and the PSEN signal is connected to the CNTL2.

The 80C251 has two major operating modes: Page Mode and Non-Page Mode. In Non-Page Mode, the data is multiplexed with the lower address byte. The ALE is active in every bus cycle. In Page Mode, data D[7:0] is multiplexed with address A[15:8]. In a bus cycle where there is a Page hit, the ALE signal is not active and only addresses A[7:0] are changing. The ZPSD6XX(V) supports both modes. In Page Mode, the PSD bus timing is identical to Non-Page Mode except the address hold time and setup time with respect to ALE is not required. The ZPSD6XX(V) access time is measured from address A[7:0] valid to data in valid.

Upon power up the 80C251 accesses data at addresses FFF8h and FFF9h where the bus configuration bytes reside. After the configuration register is set, the 80C251 starts executing codes from location 0000h. The 7th EPROM block in the ZPSD6XX(V) has two chip selects, ES7A and ES7B. The second chip select, (ES7B) can be defined to occupy the configuration byte locations while ES7A is assigned to a different memory space.

Figure 13. Interfacing the ZPSD6XX(V) with an 80C31 MCU

Figure 14. Interfacing the ZPSD6XX(V) with a 68HC11

Figure 15. Interfacing the ZPSD6XX(V) to an 80C196

Figure 16. Interfacing the ZPSD6XX(V) to the MC68331

Figure 17. Interfacing the ZPSD6XX(V) to the 80C51XA, 8-Bit Data Bus

# Bus Interface (cont.)

Figure 18. Interfacing the ZPSD6XX(V) to the 80C51XA, 16-Bit Data Bus

# Bus Interface (cont.)

Figure 19. Interfacing the ZPSD6XX(V) to the 80C251, with One READ Input

Bus Interface (cont.)

Figure 20. Interfacing the ZPSD6XX(V) to the 80C251, with READ and PSEN Input

#### I/O Ports

There are four programmable I/O ports: Ports A, B are 8 bits, Port C is seven bits and Port D is three bits. The ports can be configured to function in different modes of operation.

Each port pin is individually configurable allowing a single port to perform multiple functions. The configuration is defined either using the PSDsoft tools or by the microcontroller writing to the on-chip registers.

#### I/O Port Architecture

The general architecture of the I/O Port is shown in Figure 21. Individual Port diagrams are shown in Figures 23, 24 and 25, and will be discussed in the section below. If the ZPSD6XX(V) is configured to a non-multiplexed bus mode, Port A and/or Port B are connected to the MCU data bus and are not available as general purpose I/O ports.

As shown in Figure 21, the port pins contain an output multiplexer whose selects are driven by the configuration defined in PSDabel and the Control Registers. Inputs to the multiplexer include the following:

|   | Output data from the Data Out Register in the MCU I/O output mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| _ | I at the distriction of the terms of the ter |

■ Latched address outputs

☐ GPLD Micro⇔Cell output or ECSPLD external chip select output

The above inputs are also connected to the Port Data Buffer (PDB) for feedback to the Internal Data Bus that can be read by the microcontroller. The PDB is a three-state buffer operating like a multiplexer that allows only one source to be read at a time. The PDB also has inputs from the Direction Register, Control Register and direct port pin input (Data In).

The Port pin's tri-state output driver enable is controlled by a two input OR gate whose inputs come from the GPLD AND array Enable product term (.oe) and the Direction Register. If the enable product term of the array output is not defined, then the Direction Register has sole control of the buffer. Refer to Tables 19 and 20 on how the direction of a port pin is configured.

Table 19. Port Pin Direction Control, Output Enable P.T. Not Defined

| Direction Register Bit | Port Pin Mode |

|------------------------|---------------|

| 0                      | Input         |

| 1                      | Output        |

Table 20. Port Pin Direction Control, Output Enable P.T. Defined

| Direction Register Bit | Output Enable P.T.* | Port Pin Mode |

|------------------------|---------------------|---------------|

| 0                      | 0                   | Input         |

| 0                      | 1                   | Output        |

| 1                      | 0                   | Output        |

| 1                      | 1                   | Output        |

<sup>\*</sup>Port D does not have an output enable P.T.

The register contents can be altered by the microcontroller. The PDB feedback path allows the microcontroller to check the contents of the registers.

The A, B and C Ports have embedded Input Micro⇔Cells which can be configured as a latch, a register or direct input to the GPLD. The latch and register are clocked by the address strobe or a product term from the GPLD AND array. The output from the Input Micro⇔Cell drives the ZPLD input bus and can be read by the microcontroller. Refer to the Input Micro⇔Cell description in the ZPLD section.

Port A has additional logic (not shown in Figure 21) that enables it to operate in Peripheral I/O mode when the PIO bit in the VM Register is set.

Figure 21. General I/O Port Architecture

## **Port Operating Modes**

The I/O Ports have several modes of operation as shown in Table 21. The mode may be selected using the PSDabel tool and programmed into the device using Non-Volatile Memory (NVM) that is active when power is applied and cannot be altered unless the device is reprogrammed. If a mode is not defined in PSDsoft, then other modes can be set by the microcontroller writing to the Port configuration registers. The PLD I/O, Data Port and Address Input modes are NVM configurations. The other modes are initiated by the microcontroller.

If the NVM modes are not selected, the port can be altered dynamically between MCU I/O or Address Out modes by writing to the Control Register. Each bit of the eight-bit Control Register may store a "1", setting its respective bit in the port to MCU I/O, or to a "0", setting it to Address Out. The Direction Register or the output enable product term determine if the pin is input or output.

Table 21 summarizes the operating modes of the I/O ports. Not all the functions are available to every port. Table 22 shows how and where the different modes are configured.

Table 21. Port Operating Modes

| Port Mode       | Port A      | Port B      | Port C     | Port D |

|-----------------|-------------|-------------|------------|--------|

| MCU I/O         | Yes         | Yes         | Yes        | Yes    |

| PLD I/O         |             |             |            |        |

| McellAB Outputs | PA7-4       | PB7-4       | No         | No     |

| McellC Outputs  | No          | No          | PC7-3, 1-0 | No     |

| ECSPLD Outputs  | PA3-0       | PB3-0       | No         | PD2-0  |

| PLD Inputs      | Yes         | Yes         | Yes        | Yes    |

| Address Out     | Yes (A7-0)  | Yes (A7-0,  |            |        |

|                 |             | A15-8)      | No         | No     |

| Address In      | Yes         | Yes         | Yes        | No     |

| Data Port       | Yes (D7-0)  | Yes (D15-8) | No         | No     |

| Open Drain      | Yes (PA7-4) | Yes (PB7-4) | Yes        | No     |

| Slew Rate       | Yes (PA3-0) | Yes (PB3-0) | No         | No     |

| Peripheral I/O  | Yes         | No          | No         | No     |

#### Port Operating Modes (cont.)

Table 22. Port Operating Mode Settings

| Mode                       | Defined In<br>PSDabel                | Defined In<br>PSDconfiguration | Control<br>Register<br>Setting | Direction<br>Register<br>Setting     | VM<br>Register<br>Setting |

|----------------------------|--------------------------------------|--------------------------------|--------------------------------|--------------------------------------|---------------------------|

| MCU I/O                    | Declare pins only                    | NA                             | 0                              | 1 = output,<br>0 = input<br>(Note 1) | NA                        |

| PLD I/O                    | Logic equations                      | NA                             | NA*                            | (Note 1)                             | NA                        |

| Data Port<br>(Port A,B)    | NA                                   | Specify bus type               | NA                             | NA                                   | NA                        |

| Address Out<br>(Port A,B)  | Declare pins only                    | NA                             | 1                              | 1 (Note 1)                           | NA                        |

| Address In<br>(Port A,B,C) | Logic equation for Input Micro⇔Cells | NA                             | NA                             | NA                                   | NA                        |

| Peripheral I/O<br>(Port A) | Logic equations (PSEL0 & 1)          | NA                             | NA                             | NA                                   | PIO bit =1                |

<sup>\*</sup>NA - Not Applicable

NOTE 1: The direction of the Port A, B, C pins are controlled by the Direction Register ORed with the individual output enable product term (.oe) from the GPLD AND array.

#### PLD I/O Mode