## TIC226A, TIC226B, TIC226C, TIC226D, TIC226E, TIC226M, TIC226N, TIC226S

## SILICON BIDIRECTIONAL TRIODE THYRISTOR

- 8 A RMS

- 70 A Peak

- · Glass Passivated Wafer

- 100 V to 800 V Off-State Voltage

- Max I<sub>GT</sub> of 50 mA (Quadrants 1-3)

- High-temperature, High-current and high-voltage applications

- Compliance to ROHS

## **DESCRIPTION**

This device is a bidirectional triode thyristor (triac) which may be triggered from the off-state to the onstate by either polarity of gate signal with main Terminal 2 at either polarity.

## **ABSOLUTE MAXIMUM RATINGS**

| Symbol              | Ratings                                                                               | Value |     |     |     |     |     |     | Unit |   |

|---------------------|---------------------------------------------------------------------------------------|-------|-----|-----|-----|-----|-----|-----|------|---|

| - ,                 |                                                                                       | Α     | В   | С   | D   | Е   | M   | s   | N    |   |

| V <sub>DRM</sub>    | Repetitive peak off-state voltage (see Note1)                                         | 100   | 200 | 300 | 400 | 500 | 600 | 700 | 800  | V |

| I <sub>T(RMS)</sub> | Full-cycle RMS on-state current at (or below) 70°C case temperature (see note2)       | 8     |     |     |     |     | Α   |     |      |   |

| I <sub>TSM</sub>    | Peak on-state surge current full-sine-wave (see Note3)                                | 70    |     |     |     |     | Α   |     |      |   |

| I <sub>TSM</sub>    | Peak on-state surge current half-sine-wave (see Note4)                                | 8     |     |     |     |     | Α   |     |      |   |

| I <sub>GM</sub>     | Peak gate current                                                                     | ± 1   |     |     |     |     |     |     | Α    |   |

| P <sub>GM</sub>     | Peak gate power dissipation at (or below) 85°C case temperature (pulse width ≤200 µs) |       |     |     | W   |     |     |     |      |   |

| P <sub>G(AV)</sub>  | Average gate power dissipation at (or below) 85°C case (see Note5)                    | 0.9   |     |     |     | W   |     |     |      |   |

| T <sub>C</sub>      | Operating case temperature range -40 to +110                                          |       |     |     | °C  |     |     |     |      |   |

| T <sub>stg</sub>    | Storage temperature range -40 to +125                                                 |       |     |     | °C  |     |     |     |      |   |

| TL                  | Lead temperature 1.6 mm from case for 10 seconds                                      |       |     |     | °C  |     |     |     |      |   |

# TIC226A, TIC226B, TIC226C, TIC226D, TIC226E, TIC226M, TIC226N, TIC226S

## THERMAL CHARACTERISTICS

| Symbol           | Ratings                                 | Value  | Unit |  |  |

|------------------|-----------------------------------------|--------|------|--|--|

| R <sub>∂JC</sub> | Junction to case thermal resistance     | ≤ 1.8  | °C/W |  |  |

| R <sub>∂JA</sub> | Junction to free air thermal resistance | ≤ 62.5 | C/VV |  |  |

## **ELECTRICAL CHARACTERISTICS**

TC=25°C unless otherwise noted

| Symbol           | Ratings                                                                                               | Test Condition(s)                                                                                               | Min | Тур    | Max  | Unit |  |

|------------------|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-----|--------|------|------|--|

| I <sub>DRM</sub> | Repetitive peak off-state current                                                                     | $V_D$ = Rated $V_{DRM}$ , , $I_G$ = 0<br>$T_C$ = 110°C                                                          | -   | -      | ±2   | mA   |  |

| I <sub>GT</sub>  | Gate trigger current                                                                                  | $V_{\text{supply}} = +12 \text{ V}^{+}, R_{\text{L}} = 10 \Omega, t_{\text{p(g)}} = > 20 \mu\text{s}$           | -   | 2      | 50   | mA   |  |

|                  |                                                                                                       | $V_{\text{supply}} = +12 \text{ V}^{\dagger}, R_{\text{L}} = 10 \Omega, t_{\text{p(g)}} = > 20 \mu\text{s}$     | -   | -12    | -50  |      |  |

|                  |                                                                                                       | $V_{\text{supply}} = -12 \text{ V}^{\dagger}, R_L = 10 \Omega, t_{p(g)} = > 20 \mu \text{s}$                    | -   | -9     | -50  |      |  |

|                  |                                                                                                       | $V_{\text{supply}} = -12 \text{ V}^{\dagger}, R_{\text{L}} = 10 \Omega, t_{\text{p(g)}} = > 20 \mu\text{s}$     | -   | 20     | -    |      |  |

| $V_{GT}$         |                                                                                                       | $V_{\text{supply}} = +12 \text{ V}^{\dagger}, R_{\text{L}} = 10 \Omega, t_{\text{p(g)}} = > 20 \mu \text{s}$    | -   | 0.7    | 2    | V    |  |

|                  | Gate trigger voltage                                                                                  | $V_{\text{supply}}$ = +12 V†, $R_L$ = 10 $\Omega$ , $t_{p(g)}$ = > 20 $\mu$ s                                   | -   | -0.8   | -2   |      |  |

|                  |                                                                                                       | $V_{\text{supply}} = -12 \text{ V}^{\dagger}, R_L = 10 \Omega, t_{p(g)} = > 20 \mu \text{s}$                    | -   | -0.8   | -2   |      |  |

|                  |                                                                                                       | $V_{\text{supply}} = -12 \text{ V}^{\dagger}, R_L = 10 \Omega, t_{p(g)} = > 20 \mu \text{s}$                    | -   | 0.9    | 2    |      |  |

| I <sub>H</sub>   | Holding current                                                                                       | $V_{\text{supply}}$ = +12 V†, $I_{\text{G}}$ = 0 initiating $I_{\text{TM}}$ = 100 mA                            | -   | 5      | 30   | mΛ   |  |

|                  |                                                                                                       | $V_{\text{supply}} = -12 \text{ V}^{\dagger}, I_{\text{G}} = 0$<br>initiating $I_{\text{TM}} = -100 \text{ mA}$ | -   | -9     | -30  | mA   |  |

| ı                | Latching current                                                                                      | V <sub>supply</sub> = +12 V† (seeNote7)                                                                         | 50  |        | 50   | mΛ   |  |

| IL               | Latching current $\frac{V_{\text{supply}}}{V_{\text{supply}}} = -12 \text{ V}^{+} \text{ (seeNote7)}$ |                                                                                                                 | -   | -      | -50  | mA   |  |

| V <sub>TM</sub>  | Peak on-state voltage                                                                                 | $I_{TM} = \pm 12 \text{ A}, I_G = 50 \text{ mA (see Note6)}$                                                    | -   | ±1.6   | ±2.1 | V    |  |

| dv/dt            | Critical rate of rise of off-state voltage                                                            | $V_{DRM}$ = Rated $V_{DRM}$ , $I_G$ = 0<br>$T_C$ = 110°C                                                        | -   | ±100 - |      |      |  |

| dv/dt⊚           | Critical rise of communication voltage                                                                | $V_{DRM}$ = Rated $V_{DRM}$ , $I_{TRM}$ = ± 12A $T_C$ = 85°C                                                    | ±5  | -      | -    | V/µs |  |

<sup>†</sup> All voltages are whit respect to Main Terminal 1.

## TIC226A, TIC226B, TIC226C, TIC226D, TIC226E, TIC226M, **TIC226N, TIC226S**

#### Notes:

- 1. These values apply bidirectionally for any value of resistance between the gate and Main

- 2. This value applies for 50-Hz full-sine-wave operation with resistive load. Above 85°C derate linearly to 110°C case temperature at the rate of 320 mA/°C.

- 3. This value applies for one 50-Hz full-sine-wave when the device is operating at (or below) the rated value of on-state current. Surge may be repeated after the device has returned to original thermal equilibrium. During the surge, gate control may be lost.

- 4. This value applies for one 50-Hz half-sine-wave when the device is operating at (or below) the rated value of on-state current. Surge may be repeated after the device has returned to original thermal equilibrium. During the surge, gate control may be lost.

- 5. This value applies for a maximum averaging time of 20 ms.

6. This parameters must be measured using pulse techniques, t<sub>W</sub> = ≤1ms, duty cycle ≤ 2 %, voltage-sensing contacts, separate from the courrent-carrying contacts are located within 3.2mm (1/8 inch) from de device body.

- 7. The triacs are triggered by a 15-V (open circuit amplitude) pulse supplied by a generator with the following characteristics :  $R_G = 100\Omega$ ,  $t_{p(q)} = 20 \mu s$ ,  $t_r = \le 15 ns$ , f = 1 kHz.

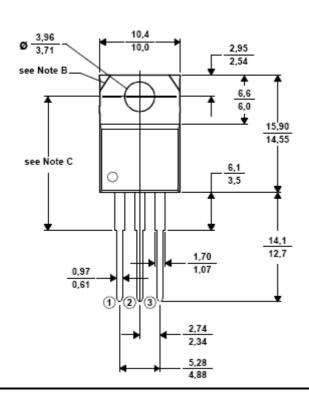

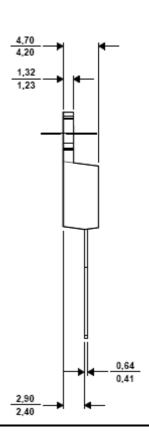

### **MECHANICAL DATA CASE TO-220**

## TIC226A, TIC226B, TIC226C, TIC226D, TIC226E, TIC226M, TIC226N, TIC226S

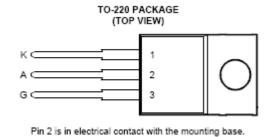

## **PINNING**

| Pin 1 : | kathode |

|---------|---------|

| Pin 2:  | Anode   |

| Pin 3 : | Gate    |

#### Revised September 2012

Information furnished is believed to be accurate and reliable. However, Comset Semiconductors assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may results from its use. Data are subject to change without notice. Comset Semiconductors makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Comset Semiconductors assume any liability arising out of the application or use of any product and specifically disclaims any and all liability, including without limitation consequential or incidental damages. Comset Semiconductors' products are not authorized for use as critical components in life support devices or systems.

www.comsetsemi.com

info@comsetsemi.com