# **SED1353**

# **STN Color LCD Controller**

- Color/monochrome LCD controller

- Pin convertible with SED1352 (monochrome LCD controller)

- Low operating voltage (2.7V to 5.5V)

- Supports interface with various types of MPUs

### **■** DESCRIPTION

SED1353 is a dot matrix graphics LCD controller capable of supporting up to  $1024 \times 1024$  (monochrome display) resolution. 256-color-display and monochrome display in up to 16-level gray scale display are available. SED1353 allows easy connection with MC68000 families and other 8/16 bits MPUs. As for memory for the display, it supports up to 128 KB SRAM.

Low operating power of SED1353 makes it a most suitable color LCD controller not only for factory automation equipments but also for small hand held equipments, too.

#### **■ FUNCTIONS**

- 16-bit. 16 MHz and MC68xxx MPU interface.

- READY or WAIT# terminal controlled 8/16 bits MPU interface.

- Either index register approah or direct mapping can be selected when making access to the internal register.

- Support a crystal oscillator or external clock input.

- 8/16 bits SRAM interface.

- Designed to operate at low power.

- Designed for two types of power save mode.

- Setup of virtual display sreen is available.

- Supports split-screen (displays two different pages on a single screen).

- Display mode:

Black and white binary display. 2/4 bits per pixel, 4/16-level gray scale display. 2/4/8 bits per pixel, 4/16/256 color display.

- 128KB (one 64K × 16 SRAM)

128KB (two 64K × 8 SRAM)

64KB (two 32KB × 8 SRAM)

40KB (8K x 8 SRAM and 32K × 8 SRAM)

32KB (one 32K × 8 SRAM)

- 16KB (two 8K  $\times$  8 SRAM) 8KB (one 8K  $\times$  8 SRAM)

Display memory interface

- · --

- LCD panel supported:

Single screen drive STN panel

Dual screen drive STN panel

- Maximum number of vertical lines:

1024 lines (for single screen drive)

2048 lines (for dual screen drive)

- SED1353D0A: Chip shipped.

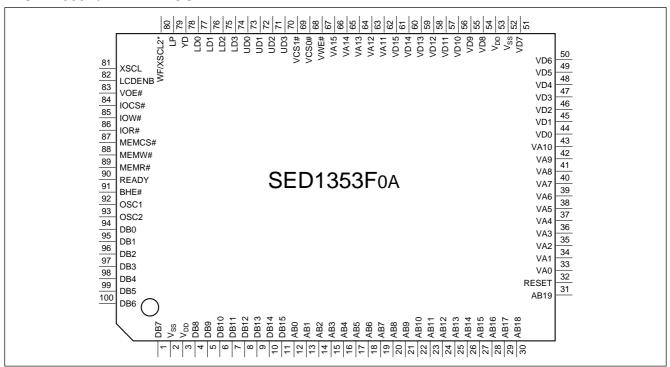

- SED1353F0A: QFP5-100 pin

- SED1353F1A: QFP15-100 pin

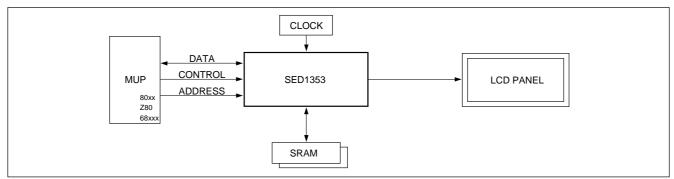

### **■ SYSTEM CONFIGURATION DIAGRAM**

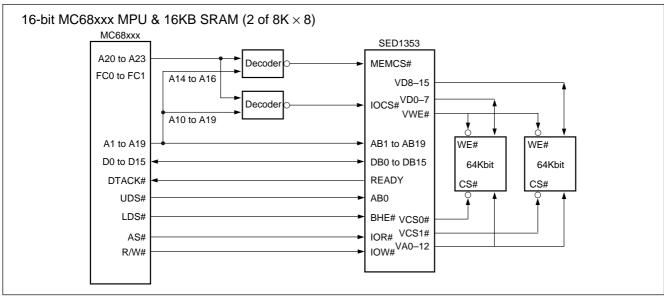

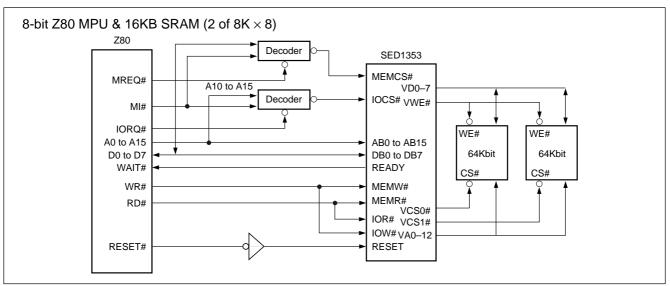

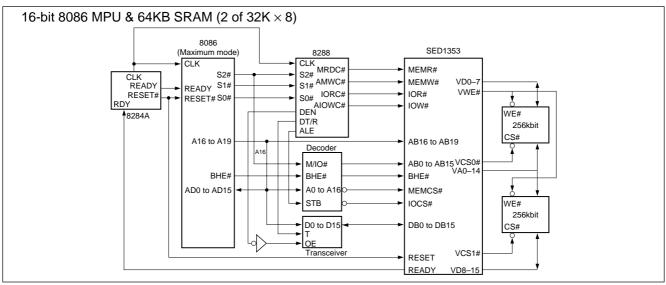

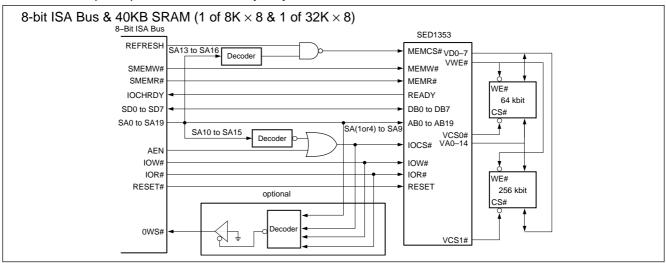

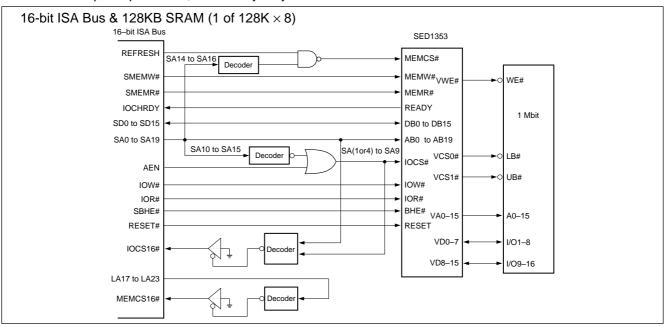

### **■ SYSTEM INTERFACE**

Note: Example implemation, actual may vary

Note: Example implemation, actual may vary

Note: Example implemation, actual may vary

Note: Example implemation, actual may vary

Note: Example implemation, actual may vary

### **■ RESOLUTIONS SUPPORTED**

|                |             | Example Display Size |                     |             |                               |                  |                   |

|----------------|-------------|----------------------|---------------------|-------------|-------------------------------|------------------|-------------------|

| Display<br>RAM | Monochrome  | 4 Grays/<br>Colors   | 16 Grays/<br>Colors | 256 Colors* | SRAM<br>Type                  | CPU<br>Interface | SRAM<br>Interface |

|                | XY          | X Y                  | X Y                 | X Y         |                               |                  |                   |

| 8KB            | 320 × 200   | 256 × 128            | 128 × 128           | _           | 1 of 8K × 8                   | 8-bit            | 8-bit             |

| 16KB           | 512 × 256   | $320 \times 200$     | 200 × 160           | 160 × 100*  | 2 of 8K × 8                   | 8-bit            | 8-bit/16-bit      |

|                |             |                      |                     |             |                               | 16-bit           | 16-bit            |

| 32KB           | 512 × 512   | 512 × 256            | 256 × 256           | 192 × 100*  | 1 of 32K × 8                  | 8-bit            | 8-bit             |

| 40KB           | 1024 × 320  | 512 × 320            | 320 × 256           | 320 × 128*  | 1 of 8K × 8 &<br>1 of 32K × 8 | 8-bit            | 8-bit             |

| 64KB           | 1024 × 512  | 512 × 512            | 512 × 256           | 256 × 256*  | 2 of 32K × 8                  | 8-bit            | 8-bit/16-bit      |

|                |             |                      |                     |             |                               | 16-bit           | 16-bit            |

| 128KB          | 1024 × 1024 | 1024 × 512           | 512 × 512           | 512 × 256*  | 1 of 64K × 16                 | 16-bit           | 16-bit            |

|                |             |                      |                     |             | 2 of 64K × 8                  | 16-bit           | 16-bit            |

Note: \* 256 colors must use 16-bit SRAM interface

The above display sizes depend on number of gray scale (colors) and memory capacity.

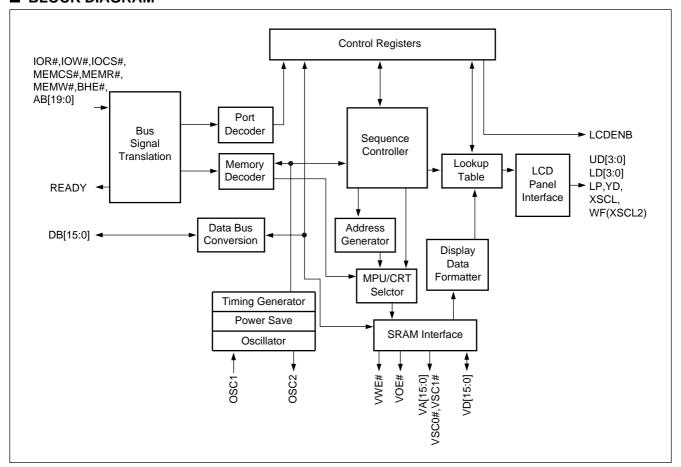

# **■ BLOCK DIAGRAM**

### **■ OVERVIEW OF THE FUNCTIONAL BLOCKS**

### **BUS Signal Translation**

This block converts the SED1353 internal bus so that it may be used for MC68000 series MPU or READY terminal controlled MPU series. This conversion is done through the setting of VD2 terminal from the Configuration Option (see page 11).

#### **Control Register**

This register block consists of 16 types of control registers. Access to these registers are available either through the direct mapping approach or index register approach.

### **Sequence Controller**

This block generates horizontal and vertical display timing being set up in the internal register.

### **LCD Panel Interface**

This block selects a gray scale for passive monochrome and color LCD panels through timing, then outputs data to the LCD panel.

### **Lookup Table**

This block consists of each RGB 16 × 4-bit palettes. In the monochrome gray scale mode, a gray scale pattern can be specified using the "Green" palette. In the color mode, all RGB palettes are used to set up a color pattern out of 4096 colors.

#### **Port Decoder**

This decoder validates a given I/O cycle through setup of VD1 terminal, VD2 to VD4 terminals, IOCS # terminal and address lines AB9 to 1 from the Configuration Option (see page 11).

### **Memory Decoder**

This decoder validates a given memory cycle through setup of VD15 to VD13, MEMCS # terminal and address lines AB19 to 17 from the Configuration Option (see page 11).

#### **Data Bus Conversion**

This block connects an external data bus (8 or 16 bits) to the internal data bus through the setup of VDD terminal from the Configuration Option (see page 11).

### **Address Generator**

This block generates the address used to validate access to the display memory.

### **MPU/CRT Selector**

This block arbitrates between MPU accees to the display memory and an access to it for LCD display.

### **Display Data Fomatter**

This block reads data from the display memory, then outputs it in the format consistant with the specified display mode (monochrome/color, levels of gray scale and number of colors).

### **Clock Inputs/Timing**

This block generates a master clock (mclk) conforming to the specified gray scale leves 1, number of colors and display memory interface. The following master clocks are available depeding on conditions specified:

– mclk = input clock: 16-grays/16-color mode (8-bit display memory) or 256-color mode (16-bit display memory).

mclk = 1/2 input clock: B&W, 4-grays/4-color mode (8-bit display memory), or 16-grays scale/16-color mode (16-bit display memory).

– mclk = 1/4 input clck: B&W, 4-grays scale/4-color mode (16-bit display memory).

Pixel clock = input clock = fosc

### **SRAM Interface**

This block generates the interface signal to the display memory (SRAM).

# **■ DC CHARACTERISTICS**

# Absolute Maximum Ratubgs

| Item            | Code | Rating                 | Unit |

|-----------------|------|------------------------|------|

| Supply voltage  | Vdd  | Vss - 0.3 + 6.0        | V    |

| Input voltage   | VIN  | Vss - 0.3 to Vdd + 0.5 | V    |

| Output voltage  | Vout | Vss - 0.3 to Vdd + 0.5 | V    |

| Storage voltage | Тѕтс | -65 to 150             | °C   |

# Recommended Operation Conditions

| Item              | Code | Conditions              | Min | Тур         | Max | Unit |

|-------------------|------|-------------------------|-----|-------------|-----|------|

| Supply voltage    | Vdd  | Vss = 0 V               | 2.7 | 3.0/3.3/5.0 | 5.5 | V    |

| Input voltage     | VIN  |                         | Vss | _           | Vdd | V    |

| Operating current | IOPR | fosc = 6MHz, 256 colors |     | 4.5/5.0/11  |     | mA   |

| Operating voltage | Topr |                         | -40 | 25          | 85  | °C   |

# Input Characteristics

| Item                     | Code | Conditions                             | Min               | Тур | Max               | Unit |

|--------------------------|------|----------------------------------------|-------------------|-----|-------------------|------|

| Low level input voltage  | VIL  | VDD = 4.5V<br>VDD = 3.0V<br>VDD = 2.7V |                   |     | 0.8<br>0.4<br>0.3 | V    |

| High level input voltage | VIH  | VDD = 5.5V<br>VDD = 3.6V<br>VDD = 3.3V | 2.0<br>1.3<br>1.2 |     |                   | V    |

| Positive threshold       | VT+  | VDD = 5.0V<br>VDD = 3.3V<br>VDD = 3.0V |                   |     | 2.4<br>1.4<br>1.3 | V    |

| Negative threshold       | VT-  | VDD = 5.0V<br>VDD = 3.3V<br>VDD = 3.0V | 0.6<br>0.5<br>0.4 |     |                   | V    |

| Hysteresis voltage       | VH   | VDD = 5.0V<br>VDD = 3.3V<br>VDD = 3.0V | 0.1<br>0.1<br>0.1 |     |                   | V    |

| Leak voltage             | lız  | _                                      | -1                |     | 1                 | μΑ   |

| Input pin capacity       | CIN  | f = 1MHz, VDD = 0V                     |                   |     | 12                | pF   |

| Pulldown resistance      | Rpd  | VDD = 5.0V, VI = VDD                   | 50                | 100 | 200               | kΩ   |

| Pulldown resistance      | Rpd  | VDD = 3.3V, VI = VDD                   | 90                | 180 | 360               | kΩ   |

| Pulldown resistance      | Rpd  | VDD = 3.0V, VI = VDD                   | 100               | 200 | 400               | kΩ   |

### Output Characteristics

| Item                                                        | Code           | Conditions                                 | Min       | Тур | Max | Unit |

|-------------------------------------------------------------|----------------|--------------------------------------------|-----------|-----|-----|------|

| Low level output voltage                                    | Vol.<br>(5.0V) | VDD = Min                                  |           |     |     |      |

| Type 1: TS1D2, CO1<br>Type 2: TS2<br>Type 3: TS3, CO3, CO3S | (5.5.)         | IOL = 4mA<br>IOL = 8mA<br>IOL = 12mA       |           |     | 0.4 | V    |

| Low level output                                            | Vol.<br>(3.3V) | VDD = Min                                  |           |     |     |      |

| Type 1: TS1D2, CO1<br>Type 2: TS2<br>Type 3: TS3, CO3, CO3S | (3.37)         | IOL = 2mA<br>IOL = 4mA<br>IOL = 6mA        |           |     | 0.3 | V    |

| Low level output voltage                                    | Vol.<br>(3.0V) | VDD = Min                                  |           |     |     |      |

| Type 1: TS1D2, CO1<br>Type 2: TS2<br>Type 3: TS3, CO3, CO3S | (3.07)         | IOL = 1.8mA<br>IOL = 3.5mA<br>IOL = 5mA    |           |     | 0.3 | V    |

| High level output voltage                                   | Vон<br>(5.0V)  | VDD = Min                                  |           |     |     |      |

| Type 1: TS1D2, CO1<br>Type 2: TS2<br>Type 3: TS3, CO3, CO3S | (0.07)         | IOL = -4mA<br>IOL = -8mA<br>IOL = -12mA    | VDD - 0.4 |     |     | V    |

| High level output voltage                                   | Vон<br>(3.3V)  | VDD = Min                                  |           |     |     |      |

| Type 1: TS1D2, CO1<br>Type 2: TS2<br>Type 3: TS3, CO3, CO3S | (3.37)         | IOL = -2mA<br>IOL = -4mA<br>IOL = -6mA     | VDD - 0.3 |     |     | V    |

| High level output voltage                                   | Vон<br>(3.0V)  | VDD = Min                                  |           |     |     |      |

| Type 1: TS1D2, CO1<br>Type 2: TS2<br>Type 3: TS3, CO3, CO3S | (0.07)         | IOL = -1.8mA<br>IOL = -3.5mA<br>IOL = -5mA | VDD - 0.3 |     |     | V    |

| Output leak current                                         | loz            | _                                          | -1        |     | 1   | μΑ   |

| Output pin capacity                                         | Соит           | f = 1MHz, VDD = 0V                         |           |     | 12  | pF   |

| Bi-directional pin capacity                                 | Свід           | f = 1MHz, VDD = 0V                         |           |     | 12  | pF   |

### ■ SED1353F0A PIN LAYOUT

<sup>\*</sup> Pin No.80 = WF: Supports every display mode except for 8-bit single color panel interface (format 1).

<sup>\*</sup> Pin No.80 = XSCL2: Supports 8-bit single color panel interface (format 1).

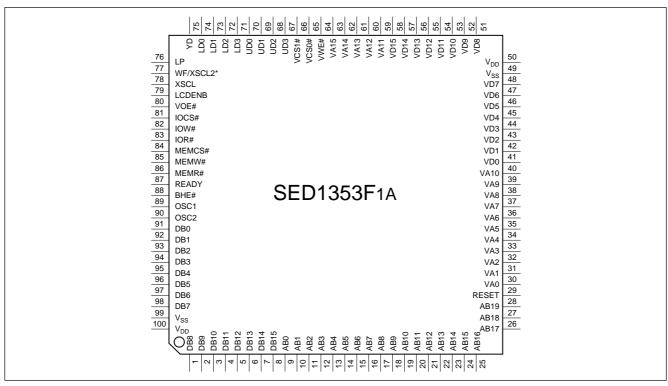

### ■ SED1353F1A PIN LAYOUT

- \* Pin No. 77 = WF: Supports every display mode except for 8-bit single color panel interface (format 1).

- \* Pin No. 77 = XSCL2: Supports 8-bit single color panel interface (format 1).

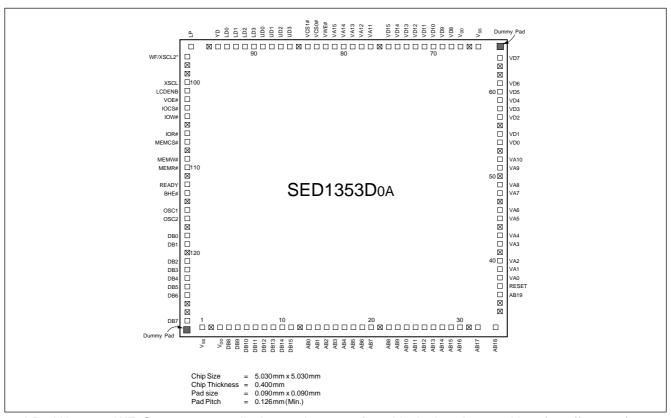

### ■ SED1353D0A PIN LAYOUT

- \* Pad No. 97 = WF: Supports every display mode except for 8-bit single color panel interface (format 1).

- \* Pad No. 97 = XSCL2: Support 8-bit single color panel interface (format 1).

# ■ PIN DESCRIPTION

I = Input

O = Output

I/O = Input and output

P = Power supply

# Bus Interface

| Pin name | Туре | FOA Pin No.        | F1A Pin No.   | Doa Pin No.                       | Description                                                                                                                                                                                                                                                                           |

|----------|------|--------------------|---------------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DB0-DB15 | I/O  | 94–100,<br>1, 4–11 | 91–98,<br>1–8 | 118–119,<br>121–125, 128,<br>4–11 | Connects to the system data bus. In 8-bit bus mode, DB8 to DB15 connect to VD0.                                                                                                                                                                                                       |

| AB0      | I    | 12                 | 9             | 13                                | When MC68000 MPU interface is used, it connects to UDS#pin (Upper Data Strobe). When other bus interface is used, it connect to the system address bus.                                                                                                                               |

| AB1–AB19 | I    | 13–31              | 10–28         | 14–20, 22–30,<br>32–33, 36        | Connects to the system bus.                                                                                                                                                                                                                                                           |

| BHE#     | I    | 91                 | 88            | 113                               | When MC68000 MPU interface is used, it connects to LDS# pin (Lower Data Strobe). When other bus interface is used, this pin functions as the bus high enable input on the 16-bit system. On 8-bit bus system, it connects to VDD.                                                     |

| IOCS#    | I    | 84                 | 81            | 103                               | Select one of 15 internal registers.                                                                                                                                                                                                                                                  |

| IOW#     | I    | 85                 | 82            | 104                               | When MC68000 MPU interface is used, it connects to R/W# pin. This input pin selects either read cycle (active high) or write cycle (active low) for data transmission. When other bus interface is used, it is active low to write data to the internal register.                     |

| IOR#     | I    | 86                 | 83            | 106                               | When MC68000 MPU interface is used, it connects to AS# pin. On the address bus, this input pin indicates an valid address is available. When other bus interface is used, this pin is active low and reads data from the internal register.                                           |

| MEMCS#   | I    | 87                 | 84            | 107                               | Accepts active low inputs, it displays access attempts to the display memory.                                                                                                                                                                                                         |

| MEMW#    | I    | 88                 | 85            | 109                               | Accepting active low inputs, it writes dat a to the display memory. When MC68000 MPU interface is used, it connects to VDD.                                                                                                                                                           |

| MEMR#    | ı    | 89                 | 86            | 110                               | Accepting active low inputs, it reads data from the display memory. When MC68000 MPU interface is used , it connects to VDD.                                                                                                                                                          |

| READY    | 0    | 90                 | 87            | 112                               | When MC68000 MPU interface is used, it is connected with DATCK# pin. As data transfer completes, it is turned low. When other system bus interface is used, it outputs low if the system wait status is needed. As data transfer completes, READY state is reset to return to High-Z. |

| RESET    | I    | 32                 | 29            | 37                                | Accepting active high, it turns all signals non-active.                                                                                                                                                                                                                               |

# Display Memory Interface

| Dia nama | T    | Fat Dia Na   | F. Dia Na    | Day Dia Ma                                     | Description                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------|------|--------------|--------------|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin name | Туре | FOA Pin No.  | F1A Pin No.  | Doa Pin No.                                    | Description                                                                                                                                                                                                                                                                                                                                                                                                             |

| VD0-VD15 | I/O  | 44–51, 54–61 | 41–48, 51–58 | 54–55, 57–61,<br>64, 68–75                     | They connect to the display memory data bus. When 16-bit interface is used, VD0 to VD7 are connected to the display memory buses in even byte address, and VD8 to VD15 are connected to those in odd memory address. When RESET is turned to high, output drivers of these pins are set to High-Z. At the falling edge of RESET, values of VD0 to VD15 are latched by this IC allowing to set various hardware options. |

| VA0-VA15 | 0    | 33–43, 62–66 | 30–40, 59–63 | 38–40, 42–43,<br>45–46, 48–49,<br>51–52, 77–81 | They connect to the display memory address buses.                                                                                                                                                                                                                                                                                                                                                                       |

| VCS1#    | 0    | 69           | 66           | 84                                             | It outputs active low chip select signal to the second SRAM or SRAMs at odd byte address.                                                                                                                                                                                                                                                                                                                               |

| VCS0#    | 0    | 68           | 65           | 83                                             | It outputs active low chip select signal to the first SRAM or SRAMs at even byte address.                                                                                                                                                                                                                                                                                                                               |

| VWE#     | 0    | 67           | 64           | 82                                             | It outputs active low used when writing data to the display memory. It is connected to the SRAM WE# pin.                                                                                                                                                                                                                                                                                                                |

| VOE#     | 0    | 83           | 80           | 102                                            | It outputs active low used for reading data from the display memory. It is connected to the SRAM OE# pin.                                                                                                                                                                                                                                                                                                               |

# ● LCD Interface

| Pin name           | FPDI-1*<br>Pin name | Туре | F <sub>0A</sub><br>Pin No. | F <sub>1A</sub><br>Pin No. | D <sub>0A</sub><br>Pin No. | Description                                                                                                                                                                                                                                     |  |

|--------------------|---------------------|------|----------------------------|----------------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| UD3-UD0<br>LD3-LD0 | UD3-UD0<br>LD3-LD0  | 0    | 70–73<br>74–77             | 67–70<br>71–74             | 86–89<br>90–93             | Display data in the dual panel mode. When 4-bit single panel is employed, LD3 to LD0 are driven to low.                                                                                                                                         |  |

| XSCL               | FPSHIFT             | 0    | 81                         | 78                         | 100                        | Shift clock of display data. Aft the falling edge of this signal, data is shifted to X driver on the LCD.                                                                                                                                       |  |

| LP                 | FPLINE              | 0    | 79                         | 76                         | 96                         | Latch clock of display data. At the falling edge of this signal, line data on the LCD X driver is latched and used for turning on the LCD Y driver.                                                                                             |  |

| WF/XSCL2           | MOD<br>FPSHIFT2     | 0    | 80                         | 77                         | 97                         | The second shift clock for 8-bit single color panel (format) mode. In other modes, it becomes LCD back plane bias signal. This output is toggled one time at each frame. (Setup of WF signal output may be changed from the internal register.) |  |

| YD                 | FPFRAME             | 0    | 78                         | 75                         | 94                         | Vertical scan start signal.                                                                                                                                                                                                                     |  |

| LCDENB             | _                   | 0    | 82                         | 79                         | 101                        | LCD enable signal. Using this signal, you can externally turn off the panel power and back light.                                                                                                                                               |  |

<sup>\*:</sup> Conforming to the VESA flat panel interface standard.

# Clock Input

| Pin name | Туре | Foa Pin No. | F1A Pin No. | Doa Pin No. | Description                                                                                                                                                                                            |

|----------|------|-------------|-------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1     | I    | 92          | 89          | 115         | When 2-pin crystal is used for the clock input, this pin is connected to the crystal along with OSC2. And, when an external oscillator circuit is used as the clock source, this pin inputs the clock. |

| OSC2     | 0    | 93          | 90          | 116         | When 2-pin crystal is used for the clock input, this pin is connected to the crystal along with OSC2. And, when an external oscillator circuit is used as the clock source, it is turned to NC.        |

# Power Supply

| Pin name | Туре | FOA Pin No. | F1A Pin No. | Doa Pin No. | Description       |

|----------|------|-------------|-------------|-------------|-------------------|

| Vdd      | Р    | 3, 53       | 50, 100     | 3, 67       | Power supply pin. |

| Vss      | Р    | 2, 52       | 49, 99      | 1, 65       | Grounding pin.    |

### **■ OPTIONAL HARDWARE CONFIGURATION**

During the RESET, SED1353 latches state of SRAM data bus (1 or 0) to offer an optimum hardware configuration to the user system. Since SED1353 has a pull down resistor inside the IC, if the following "1" applies, a  $10k\Omega$  external pull up resistor must be provided . In case of "0", the external pull up resistor is not required.

| Pin name  | Hardware configuration according to the pin status (1 or 0)                                                                                                                                                                                                                                                                                                                              |                                                                                                           |  |  |  |  |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--|--|--|--|

|           | 1                                                                                                                                                                                                                                                                                                                                                                                        | 0                                                                                                         |  |  |  |  |

| VD0       | 16-bit host bus interface                                                                                                                                                                                                                                                                                                                                                                | 8-bit host bus interface                                                                                  |  |  |  |  |

| VD1       | Direct mapping I/O access                                                                                                                                                                                                                                                                                                                                                                | Index mapping I/O access                                                                                  |  |  |  |  |

| VD2       | MC68000 MPU interface                                                                                                                                                                                                                                                                                                                                                                    | READ (WAIT#) pin controlled MPU and bus interface                                                         |  |  |  |  |

| VD3       | When 16-bit bus interface is used, there is data swap between higher-order data byte and lower-order data byte.                                                                                                                                                                                                                                                                          | When 16-bit bus interface is used, there is not data swap between higher-order and lower-order data byte. |  |  |  |  |

| VD12–VD4  | I/O mapping address select bit [9:1]  Initial bits used for selecting the address mapping of I/O reinterface.  When valid address for I/O cycle is generated, the internal with these bits.                                                                                                                                                                                              | , , ,                                                                                                     |  |  |  |  |

| VD15–VD13 | Memory mapping address select bit [3:1]  Initial bits used for selecting address mapping of memory. They correspond to address bit [19:17] of the MPU interface.  When valid address for memory cycle is generated, the internal decoder is controlled so that addressing is done as specified with these bits. "Valid memory cycle" denotes the the access where MEMCS"# is turned low. |                                                                                                           |  |  |  |  |

### ■ COMPARISON BETWEEN SED1353 AND SED1352

SED1353 is upward convertible and pin convertible with f SED1352. Thus, up grading from SED1352 to 1353 is easy in terms of both hardware and software.

The following list main difference between SED1353 and SED1352. For detailed specifications, refer to respective technical manual.

### Functional Comparison

| Specifications                                             | SED1353                                                                                   | SED1352                                                                   |

|------------------------------------------------------------|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| Color display                                              | • 4/16/256 colors                                                                         | Not available                                                             |

| Monochrome display                                         | <ul><li>black/white binary.</li><li>4/16-level gray scale.</li></ul>                      | <ul><li>Not available.</li><li>4/16-level gray scale.</li></ul>           |

| Display data format                                        | <ul><li>4/8 bits single/dual monochrome.</li><li>4/8/16 bits signal/dual color.</li></ul> | <ul><li>4/8 bits single/dual monochrome.</li><li>Not available.</li></ul> |

| Setup of vertical scan period done in horizontal direction | Programmable.                                                                             | Not available.                                                            |

| Look-up Table                                              | • 3 × 16, 4-bit width.                                                                    | • 1 × 16, 4-bit width.                                                    |

# Modifications or Additions done on the Internal Register

(See SED1353 technical manual for the detail)

| AUX [01h] |                               | AUX [0Eh] |                        |

|-----------|-------------------------------|-----------|------------------------|

| bit 2     | LCD Data Width bit 0          | bit 4     | ID Bit/RGB Index Bit 0 |

| bit 3     | Gray Shade/Color              | bit 5     | ID Bit/RGB Index Bit 1 |

|           |                               | bit 6     | Green Bank Bit 0       |

| AUX [03h] |                               | bit 7     | Green Bank Bit 1       |

| bit 1     | Color Mode                    |           |                        |

| bit 2     | BW/256 colors                 | AUX [0Fh] |                        |

|           |                               | bit 4     | Blue Bank Bit 0        |

| AUX [0Ch] |                               | bit 5     | Blue Bank Bit 1        |

| bit 0:7   | Horizontal Non-Display Period | bit 6     | Red Bank Bit 0         |

|           |                               | bit 7     | Red Bank Bit 1         |

### NOTICE:

No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as, medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. This material or portions thereof may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Law of Japan and may require an export license from the Ministry of International Trade and Industry or other approval from another government agency.

© Seiko Epson Corporation 2000 All right reserved.

All other product names mentioned herein are trademarks and/or registered trademarks of their respective companies.

### **SEIKO EPSON CORPORATION**

**ELECTRONIC DEVICES MARKETING DIVISION**

IC Marketing & Engineering Group

**ED International Marketing Department I (Europe, U.S.A)** 421-8 Hino, Hino-shi, Tokyo 191-8501, JAPAN Phone: 042-587-5812 FAX: 042-587-5564

**ED International Marketing Department II (ASIA)** 421-8 Hino, Hino-shi, Tokyo 191-8501, JAPAN Phone: 042-587-5814 FAX: 042-587-5110

■ Electronic devices information on the Epson WWW server.

http://www.epson.co.jp/device/