# ML12061 Crystal Oscillator

Legacy Device: Motorola MC12061

The ML12061 is for use with an external crystal to form a crystal controlled oscillator. In addition to the fundamental series mode crystal, two bypass capacitors are required (plus usual power supply pin bypass capacitors). Translators are provided internally for MECL and TTL outputs.

- Frequency Range = 2.0 to 20 MHz

- Operating Temperature Range =  $0 \text{ to } + 70^{\circ}\text{C}$

- Single Supply Operation: +5.0 Vdc or -5.2 V DC

- Three Outputs Available:

- 1.Complementary Sine Wave (600 mVpp typ)

- 2.Complementary MECL

- 3. Single Ended TTL

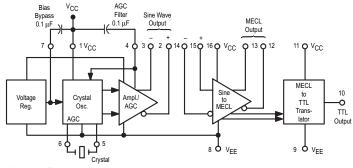

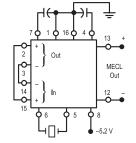

Figure 1. Block Diagram

Note: 0.1 μF power supply pin bypass capacitors not shown.

# P DIP 16 = EP PLASTIC PACKAGE CASE 648 CROSS REFERENCE/ORDERING INFORMATION PACKAGE MOTOROLA LANSDALE P DIP 16 MC112061P ML12061EP

**Note**: Lansdale lead free (**Pb**) product, as it becomes available, will be identified by a part number prefix change from **ML** to **MLE**.

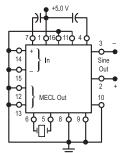

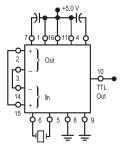

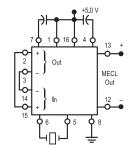

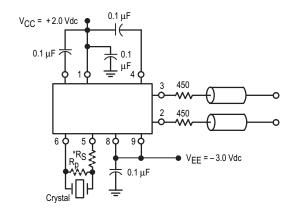

### TYPICAL CIRCUIT CONFIGURATIONS

Note:  $0.1 \, \mu F$  power supply pin bypass capacitors not shown.

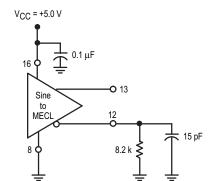

Figure 2. Sine Wave Output

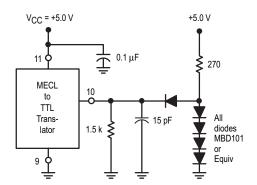

Figure 3. MTTL Output

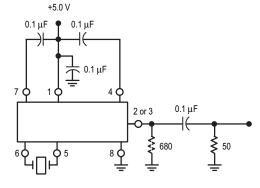

Figure 4. MECL Output (+5.0 V Supply)

Figure 5. MECL Output (-5.2 V Supply)

# CRYSTAL REQUIREMENTS

Note: Start-up stabilization time is a function of crystal series resistance. The lower the resistance, the faster the circuit stabilizes.

| Characteristic                                   | ML12061                      |

|--------------------------------------------------|------------------------------|

| Mode of Operation                                | Fundamental Series Resonance |

| Frequency Range                                  | 2.0 MHz — 20 MHz             |

| Series Resistance, R1                            | Minimum at Fundamental       |

| Maximum Effective Resistance R <sub>E(max)</sub> | 155 ohms                     |

### **ELECTRICAL CHARACTERISTICS**

|                              |                  | Test Limits          |              |              |               |                 |                 |              |              |      |  |  |

|------------------------------|------------------|----------------------|--------------|--------------|---------------|-----------------|-----------------|--------------|--------------|------|--|--|

|                              |                  | Pin<br>Under<br>Test | 0°           | ·C           | +25°C         |                 |                 | +7           | 1            |      |  |  |

| Characteristic               | Symbol           |                      | Min          | Max          | Min           | Тур             | Max             | Min          | Max          | Unit |  |  |

| Power Supply Drain Current   | Icc              | 1                    | _            | _            | 13            | 16              | 19              | _            | _            | mAdc |  |  |

|                              |                  | 1<br>11<br>16        | -<br>-<br>-  | -<br>-<br>-  | 18<br>-<br>13 | 23<br>3.0<br>16 | 28<br>4.0<br>19 | -<br>-<br>-  | -<br>-<br>-  |      |  |  |

| Input Current                | linH             | 14<br>15             | _<br>_       | -<br>-       | _<br>_        | _<br>_          | 250<br>250      | _<br>_       | _<br>_       | μAdc |  |  |

|                              | linL             | 14<br>15             | _<br>_       | _<br>_       | _<br>_        | _<br>_          | 1.0<br>1.0      | _<br>_       | _<br>_       | μAdc |  |  |

| Differential Offset Voltage  | ΔV               | 4 to 7<br>2 to 3     | _<br>_       | _<br>_       | 40<br>–200    | _<br>0          | 325<br>+200     | _<br>_       | _<br>_       | mAdc |  |  |

| Output Voltage Level         | V <sub>out</sub> | 2<br>3               | _<br>_       | _<br>_       | _<br>_        | 3.5<br>3.5      | _<br>_          | _<br>_       | _<br>_       | Vdc  |  |  |

| Logic '1' Output Voltage     | VOH1<br>(Note 1) | 12<br>13             | 4.0<br>4.0   | 4.16<br>4.16 | 4.04<br>4.04  | _<br>_          | 4.19<br>4.19    | 4.1<br>4.1   | 4.28<br>4.28 | Vdc  |  |  |

|                              | V <sub>OH2</sub> | 10                   | 2.4          | -            | 2.4           | _               | -               | 2.4          | _            |      |  |  |

| Logic '0' Output Voltage     | VOL1<br>(Note 1) | 12<br>13             | 2.98<br>2.98 | 3.43<br>3.43 | 3.0<br>3.0    | _<br>_          | 3.44<br>3.44    | 3.02<br>3.02 | 3.47<br>3.47 | Vdc  |  |  |

|                              | V <sub>OL2</sub> | 10<br>10             | _<br>_       | 0.5<br>0.5   | _<br>_        | -<br>-          | 0.5<br>0.5      | _<br>_       | 0.5<br>0.5   |      |  |  |

| Logic '1' Threshold Voltage  | VOHA             | 12<br>13             | 3.98<br>3.98 | -<br>-       | 4.02<br>4.02  | -<br>-          | _<br>_          | 4.08<br>4.08 | _<br>_       | Vdc  |  |  |

| Logic '0' Threshold Voltage  | VOLA             | 12<br>13             | -<br>-       | 3.45<br>3.45 | _<br>_        | -<br>-          | 3.46<br>3.46    | _<br>_       | 3.49<br>3.49 | Vdc  |  |  |

| Output Short Circuit Current | los              | 10                   | 20           | 60           | 20            | _               | 60              | 20           | 60           | mAdc |  |  |

**NOTE:** 1. Devices will meet standard MECL logic levels using  $V_{EE} = -5.2$  Vdc and  $V_{CC} = 0$ .

### **ELECTRICAL CHARACTERISTICS** (continued)

|                              |                    |                  |                    | TEST V             | OLTAGE/CU                               | JRRENT VAI          | LUES             |            |              |  |  |

|------------------------------|--------------------|------------------|--------------------|--------------------|-----------------------------------------|---------------------|------------------|------------|--------------|--|--|

|                              | Volts              |                  |                    |                    |                                         |                     |                  |            |              |  |  |

|                              | @ Test Temperature |                  |                    |                    | VIHmax VILmin VIHAmin VILAmax VIHT VCCL |                     |                  |            |              |  |  |

| 0°C [                        |                    |                  | 4.16               | 3.19               | 3.86                                    | 3.51                | 4.0              | 4.75       |              |  |  |

|                              | 4.19               | 3.21             | 3.90               | 3.52               | 4.0                                     | 4.75                |                  |            |              |  |  |

|                              |                    | +75°C            | 4.28               | 3.23               | 3.96                                    | 3.55                | 4.0              | 4.75       |              |  |  |

|                              |                    | Pin<br>Under     | TE                 | ST VOLTAGE         | APPLIED                                 | TO PINS LIS         | TED BELC         | w          |              |  |  |

| Characteristic               | Symbol             | Test             | V <sub>IHmax</sub> | V <sub>ILmin</sub> | V <sub>IHAmin</sub>                     | V <sub>ILAmax</sub> | V <sub>IHT</sub> | VCCL       | Gnd          |  |  |

| Power Supply Drain Current   | ICC                | 1                | -                  | _                  | _                                       | _                   | _                | _          | 8            |  |  |

|                              |                    | 1                |                    |                    | _                                       | _                   | _                | _          | 8            |  |  |

|                              |                    | 11<br>16         | 14<br>-            | 15<br>-            | _                                       | _                   | _                | _          | 8,9<br>8     |  |  |

| Input Current                | linH               | 14<br>15         | 14<br>15           | 15<br>14           | _<br>_                                  | _<br>_              | _<br>_           | -<br>-     | 8<br>8       |  |  |

|                              | linL               | 14<br>15         | 15<br>14           | -<br>-             | _<br>_                                  | -<br>-              | _<br>_           | _<br>_     | 8,14<br>8,15 |  |  |

| Differential Offset Voltage  | ΔV                 | 4 to 7<br>2 to 3 | -<br>-             | 1 1                | _<br>_                                  | -<br>-              | 5,6<br>4         | _<br>_     | 8 –          |  |  |

| Output Voltage Level         | V <sub>out</sub>   | 2 3              | _<br>_             | -<br>-             | _<br>_                                  | -                   | 4<br>4           | _<br>_     | 8<br>8       |  |  |

| Logic '1' Output Voltage     | VOH1<br>(Note 1)   | 12<br>13         | 14<br>15           | 15<br>14           | _<br>_                                  | -                   | 1 1              | _<br>_     | 8 8          |  |  |

|                              | V <sub>OH2</sub>   | 10               | 15                 | 14                 | _                                       | _                   | _                | 11,16      | 8,9          |  |  |

| Logic '0' Output Voltage     | VOL1<br>(Note 1)   | 12<br>13         | 15<br>14           | 14<br>15           | _<br>_                                  | -                   | 1 1              | _<br>_     | 8 8          |  |  |

|                              | V <sub>OL2</sub>   | 10<br>10         | 14<br>14           | 15<br>15           | _<br>_                                  | -                   | -                | 11,16<br>– | 8,9<br>8,9   |  |  |

| Logic '1' Threshold Voltage  | VOHA               | 12<br>13         | -<br>-             | -<br>-             | 14<br>15                                | 15<br>14            | _<br>_           | -<br>-     | 8<br>8       |  |  |

| Logic '0' Threshold Voltage  | VOLA               | 12<br>13         | -<br>-             | -<br>-             | 15<br>14                                | 14<br>15            | _                | <u>-</u>   | 8<br>8       |  |  |

| Output Short Circuit Current | los                | 10               | 15                 | 14                 | _                                       | -                   | _                | 11,16      | 8,9,10       |  |  |

**NOTE:** 1. Devices will meet standard MECL logic levels using  $V_{EE} = -5.2$  Vdc and  $V_{CC} = 0$ .

## **ELECTRICAL CHARACTERISTICS** (continued)

|                              | TEST VOLTAGE/CURRENT VALUES |                  |                  |             |              |              |             |               |  |

|------------------------------|-----------------------------|------------------|------------------|-------------|--------------|--------------|-------------|---------------|--|

|                              |                             |                  |                  |             |              | mA           |             |               |  |

|                              | VCC                         | Vccн             | loL              | ЮН          | Iμ           |              |             |               |  |

|                              | 5.0                         | 5.25             | 16               | -0.4        | -2.5         |              |             |               |  |

|                              |                             | +25°C            | 5.0              | 5.25        | 16           | -0.4         | -2.5        |               |  |

|                              |                             | +75°C            | 5.0              | 5.25        | 16           | -0.4         | -2.5        |               |  |

|                              |                             | Pin<br>Under     | TEST             | VOLTAGE APP | PLIED TO PIN | S LISTED BEI | LOW         |               |  |

| Characteristic               | Symbol                      | Test             | VCC              | Vccн        | loL          | ІОН          | IIL         | Gnd           |  |

| Power Supply Drain Current   | Icc                         | 1                | 1                | -           | -            | _            | -           | 8             |  |

|                              |                             | 1<br>11<br>16    | 1<br>11,16<br>16 | -<br>-<br>- | -<br>-<br>-  | -<br>-<br>-  | -<br>-<br>- | 8<br>8,9<br>8 |  |

| Input Current                | linH                        | 14<br>15         | 16<br>16         | -           | -<br>-       | -<br>-       | _<br>_      | 8<br>8        |  |

|                              | linL                        | 14<br>15         | 16<br>16         | -           | -<br>-       |              | -<br>-      | 8,14<br>8,15  |  |

| Differential Offset Voltage  | ΔV                          | 4 to 7<br>2 to 3 | 1<br>-           | _<br>_      | _<br>_       | -<br>-       | _<br>_      | 8<br>-        |  |

| Output Voltage Level         | V <sub>out</sub>            | 2 3              | 1<br>1           | _<br>_      | -            | -            | -<br>-      | 8<br>8        |  |

| Logic '1' Output Voltage     | VOH1<br>(Note 1)            | 12<br>13         | 16<br>16         | _<br>_      | -            | -<br>-       | 12<br>13    | 8<br>8        |  |

|                              | V <sub>OH2</sub>            | 10               | -                | -           | -            | 10           | -           | 8,9           |  |

| Logic '0' Output Voltage     | VOL1<br>(Note 1)            | 12<br>13         | 16<br>16         | _<br>_      | -<br>-       | - 1          | 12<br>13    | 8<br>8        |  |

|                              | V <sub>OL2</sub>            | 10<br>10         | -                | _<br>11,16  | 10<br>10     | -<br>-       | -<br>-      | 8,9<br>8,9    |  |

| Logic '1' Threshold Voltage  | VOHA                        | 12<br>13         | 16<br>16         | -<br>-      | -<br>-       | -<br>-       | 12<br>13    | 8<br>8        |  |

| Logic '0' Threshold Voltage  | V <sub>OLA</sub>            | 12<br>13         | 16<br>16         | -<br>-      | -<br>-       | -<br>-       | 12<br>13    | 8<br>8        |  |

| Output Short Circuit Current | los                         | 10               | -                | -           | -            | -            | -           | 8,9,10        |  |

**NOTE:** 1. Devices will meet standard MECL logic levels using  $V_{EE} = -5.2$  Vdc and  $V_{CC} = 0$ .

- +200 mV V<sub>CC</sub> = +2.0 Vdc 80% 50% Input (Pin 15) 20% -200 mV t-450 50% Pulse Generator (EH 137 or Equiv) PRF = 2.0 MHz TTL Output (Pin 10) 80%  $t + = t - = 2.0 \pm 0.2 \text{ ns}$ 50% MECL Output 10 12k (Pin 13) t+ t-+ 400 MECL Output 80% 9 **Q** 0 (Pin 12) MMD6150 or Equiv  $0.1 \mu F$ CT 7 All input and output cables to the scope are equal lengths of 50  $\Omega$  coaxial cable.  $C_T$  = 15 pF = total parasitic capacitance which MMD7000 includes probe, wiring, and load capacior Equiv  $V_{EE} = -3.0 \text{ Vdc}$ Unused outputs are connected to a 50  $\Omega$ ± 1% resistor to ground. -3.0 Vdc

Figure 6. AC Characteristics - MECL and TTL Outputs

|                   |                                                                |                                  |        | Test Limits                          |                       |                                      | TEST VOLTAGES/WAVEFORMS<br>APPLIED TO PINS LISTED BELOW: |                    |                                      |          |          |                                  |                |            |          |

|-------------------|----------------------------------------------------------------|----------------------------------|--------|--------------------------------------|-----------------------|--------------------------------------|----------------------------------------------------------|--------------------|--------------------------------------|----------|----------|----------------------------------|----------------|------------|----------|

|                   |                                                                | Pin<br>Under                     | 0°     | C                                    |                       | + 25°C                               | ;                                                        | +7                 | 5°C                                  |          |          |                                  |                |            |          |

| Characteristic    | Symbol                                                         | Test                             | Min    | Мах                                  | Min                   | Тур                                  | Мах                                                      | Min                | Max                                  | Unit     | Pulse In | Pulse Out                        | +2.0 Vdc       | -3.0 Vdc   | Gnd      |

| Propagation Delay | t15+10+<br>t15-10-<br>t15+12-<br>t15-12+<br>t15+13+<br>t15-13- | 10<br>10<br>12<br>12<br>13<br>13 | <br>   | 22<br>19<br>5.2<br>5.0<br>4.8<br>5.0 | _<br>_<br>_<br>_<br>_ | 17<br>12<br>4.3<br>3.7<br>4.0<br>4.0 | 25<br>18<br>5.5<br>5.2<br>5.0<br>5.0                     | <br> -<br> -<br> - | 27<br>18<br>5.8<br>5.2<br>5.2<br>5.1 | ns       | 15       | 10<br>10<br>12<br>12<br>13<br>13 | 11,16          | 8,9        | 14       |

| Rise Time         | t <sub>12+</sub><br>t <sub>13+</sub>                           | 12<br>13                         | _<br>_ | 4.0<br>4.0                           | _<br>_                | 3.0<br>3.0                           | 4.0<br>4.0                                               | _<br>_             | 4.4<br>4.4                           | ns<br>ns | 15<br>15 | 12<br>13                         | 11,16<br>11,16 | 8,9<br>8,9 | 14<br>14 |

| Fall Time         | t <sub>12-</sub><br>t <sub>13-</sub>                           | 12<br>13                         | _      | 4.0<br>4.0                           | _                     | 3.0<br>3.0                           | 4.0<br>4.0                                               | _                  | 4.0<br>4.0                           | ns<br>ns | 15<br>15 | 12<br>13                         | 11,16<br>11,16 | 8,9<br>8,9 | 14<br>14 |

|                     | Pin<br>Under | +25°C |     | +25°C |          | +25°C    |  |  | TEST VOLTA<br>TO PINS LIS |  |

|---------------------|--------------|-------|-----|-------|----------|----------|--|--|---------------------------|--|

| Characteristic      | Test         | Min   | Тур | Unit  | +2.0 Vdc | -3.0 Vdc |  |  |                           |  |

| Sine Wave Amplitude |              |       |     |       |          |          |  |  |                           |  |

|                     | 2            | 650   | 750 | mVp-p | 1        | 8,9      |  |  |                           |  |

|                     | 3            | 650   | 750 |       |          |          |  |  |                           |  |

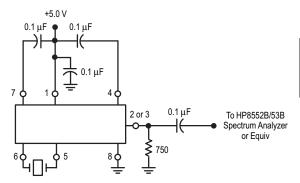

Figure 7. AC Test Circuit – Sine Wave Output

All output cables to the scope are equal lengths of 50  $\Omega$  coaxial cable. All unused cables must be terminated with a 50  $\Omega$   $\pm$  1% resistor to ground.

$450\,\Omega$  resistor and the scope termination impedance constitute a 10:1 attenuator probe.

Crystal — Reeves Hoffman Series Mode,

Series Resistance Minimum at Fundamental f = 10 MHz

$R_E = 5 \Omega$

\*R<sub>S</sub> = 15 k $\Omega$  is inserted only for test purposes. When used with the above specified crystal, it guarantees oscillation with any crystal which has an equivalent series resistance  $\leq$  155  $\Omega$

$R_{\rm D}$ : will improve start up problems value: 200–500  $\Omega$

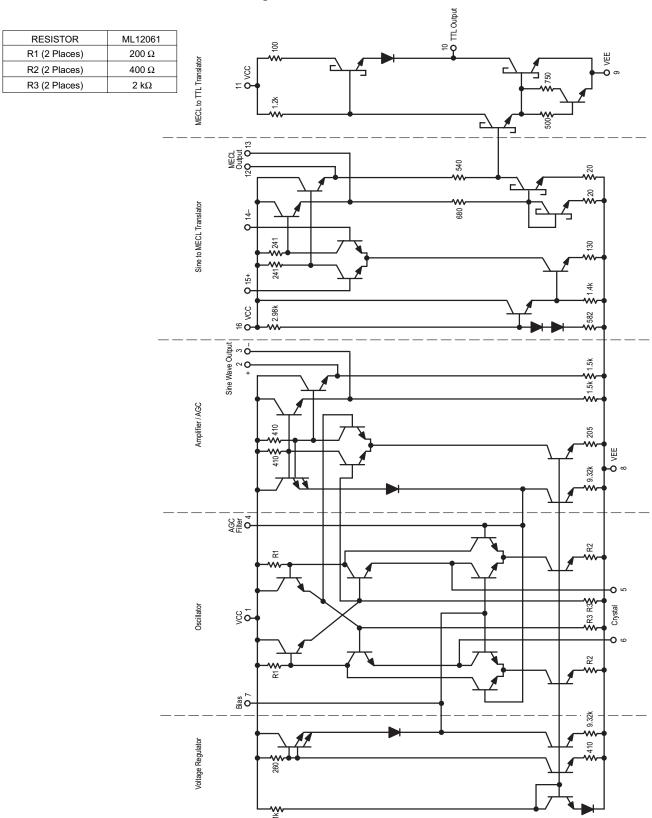

The ML12061 consists of three basic sections: an oscillator with AGC and two translators. Buffered complementary sine wave outputs are available from the oscillator section. The translators convert these sine wave outputs to levels compatible with MECL and/or TTL.

Series mode crystals should be used with the oscillator. If it is necessary or desirable to adjust the crystal frequency, a reactive element can be inserted in series with the crystal — an inductor to lower the frequency or a capacitor to raise it. When such an adjustment is necessary, it is recommended that the crystal be specified slightly lower in frequency and a series trimmer capacitor be added to bring the oscillator back on frequency. As the oscillator frequency is changed from the natural resonance of the crystal, more and more dependence is placed on the external reactance, and temperature drift of the trimming components then affects overall oscillator performance.

The ML12061 is designed to operate from a single supply—either +5.0 Vdc or -5.2 Vdc. Although each translator has separate V<sub>CC</sub> and V<sub>EE</sub> supply pins, the circuit is NOT designed to operate from both voltage levels at the same time. The separate V<sub>EE</sub> pin from the TTL translator helps minimize transient disturbance. If neither translator is being used, all unused pins (9 thru 16) should be connected to V<sub>EE</sub> (pin 8). With the translators not powered, supply current drain is typically reduced from 42 mA to 23 mA for the ML12061.

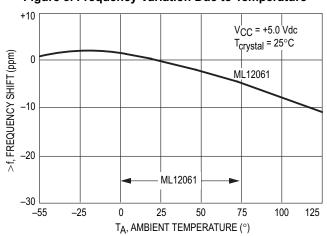

### **Frequency Stability**

Output frequency of different oscillator circuits (of a given device type number) will vary somewhat when used with a given test setup. However, the variation should be within approximately  $\pm 0.001\%$  from unit to unit. Frequency variations with temperature (independent of the crystal, which is held at 25°C) are small — about -0.08ppm/°C for ML12061 operating at 8.0 MHz.

### **Signal Characteristics**

The sine wave outputs at either pin 2 or pin 3 will typically range from 800 mV<sub>p-p</sub> (no load) to 500 mV<sub>p-p</sub> (120 ohm AC load). Approximately 500 mV<sub>p-p</sub> can be provided across 50 ohms by slightly increasing the DC current in the output buffer by the addition of an external resistor (680 ohms) from pin 2 or 3 to ground, as shown in Figure 9. Frequency drift is typically less than 0.0003% when going from a high-impedance load (1 megohm, 15pF) to the 50 ohm load of Figure 9. The DC voltage level at pin 2 or 3 is nominally 3.5 Vdc with V<sub>CC</sub> = +5.0 Vdc.

Harmonic distortion content in the sine wave outputs is crystal as well as circuit dependent. The largest harmonic (third) will usually be at least 15 dB down from the fundamental. The harmonic content is approximately load independent except

that the higher harmonic levels (greater than the fifth) are increased when the MECL translator is being driven.

Typically, the MECL outputs (pins 12 and 13) will drive up to five gates and the TTL output (pin10) will drive up to ten gates.

### **Noise Characteristics**

Noise level evaluation of the sine wave outputs operation at or 9.0 MHz, indicates the following characteristics:

- 1. Noise floor (200 kHz from oscillator center frequency) is approximately –122 dB when referenced to a 1.0 Hz bandwidth. Noise floor is not sensitive to load conditions and/or translator operation.

- 2. Close-in noise (100 Hz from oscillator center frequency) is approximately –88 dB when referenced to a 1.0 Hz bandwidth.

Figure 8. Frequency Variation Due to Temperature

Figure 9. Driving Low Impedance Loads

<sup>\*</sup> See text under signal characteristics

Figure 10. MECL Translator Load Capability

Figure 11. TTL Translator Load Capability

Figure 12. Noise Measurement Test Circuit

### ANALYZER SETTING

| Measurement    | Sweep      | Bandwidth | Video<br>Filter |

|----------------|------------|-----------|-----------------|

| Noise Floor    | 50 kHz/div | 10 kHz    | 10 Hz           |

| Close-In Noise | 20 kHz/div | 10 Hz     | 10 Hz           |

Figure 13. Circuit Schematic

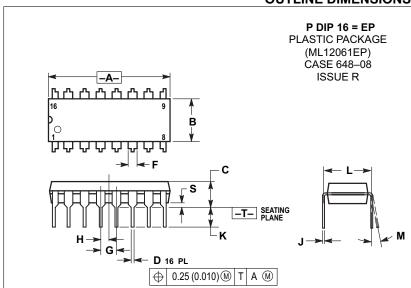

### **OUTLINE DIMENSIONS**

- 1. DIMENSIONING AND TOLERANCING PER ANSI

- DIMENSIONING AND TOLERANCING FER ANY Y14.5M, 1982. CONTROLLING DIMENSION: INCH. DIMENSION L TO CENTER OF LEADS WHEN FORMED PARALLEL.

DIMENSION B DOES NOT INCLUDE MOLD FLASH.

- ROUNDED CORNERS OPTIONAL.

|     | INC   | HES   | MILLIMETERS |       |  |  |  |

|-----|-------|-------|-------------|-------|--|--|--|

| DIM | MIN   | MAX   | MIN         | MAX   |  |  |  |

| Α   | 0.740 | 0.770 | 18.80       | 19.55 |  |  |  |

| В   | 0.250 | 0.270 | 6.35        | 6.85  |  |  |  |

| С   | 0.145 | 0.175 | 3.69        | 4.44  |  |  |  |

| D   | 0.015 | 0.021 | 0.39        | 0.53  |  |  |  |

| F   | 0.040 | 0.70  | 1.02        | 1.77  |  |  |  |

| G   | 0.100 | BSC   | 2.54 BSC    |       |  |  |  |

| Н   | 0.050 | BSC   | 1.27 BSC    |       |  |  |  |

| 7   | 0.008 | 0.015 | 0.21        | 0.38  |  |  |  |

| K   | 0.110 | 0.130 | 2.80        | 3.30  |  |  |  |

| L   | 0.295 | 0.305 | 7.50        | 7.74  |  |  |  |

| М   | 0°    | 10 °  | 0°          | 10 °  |  |  |  |

| S   | 0.020 | 0.040 | 0.51        | 1.01  |  |  |  |

Lansdale Semiconductor reserves the right to make changes without further notice to any products herein to improve reliability, function or design. Lansdale does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. "Typical" parameters which may be provided in Lansdale data sheets and/or specifications can vary in different applications, and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by the customer's technical experts. Lansdale Semiconductor is a registered trademark of Lansdale Semiconductor, Inc.