## **DEBOUNCED 8×8 KEY-SCAN CONTROLLER**

#### January 2012

#### **GENERAL DESCRIPTION**

The IS31IO7326 is a 64 key, key-scan controller. It offloads the burden of keyboard scanning from the host processor. The IS31IO7326 supports keypad matrix of up to 8×8. Key press and release events are encoded into a byte format and loaded into a key event register for retrieval by the host processor.

The IS31IO7326 integrates a debounce function which rejects false or transient key switch activities. The

interrupt output (INT) is used to signify if there are any keypad activities.

To minimize power, the IS31IO7326 automatically enters a low power standby mode when there is no keypad, I/O, or host activity.

The IS31IO7326 is available in a Pb-free 4mm × 4mm QFN-24 package.

## FEATURES

- 2.4V to 5.5V operation

- 400kHz I<sup>2</sup>C serial interface

- Available for multi-key press detect

- Low 0.3µA (typ.) standby current

- Operate in -40°C to +125°C

- Pb-free 4mm × 4mm QFN-24 package

#### APPLICATIONS

- Keypad of QWERTY type phones

- PDAs, games, and other handheld applications

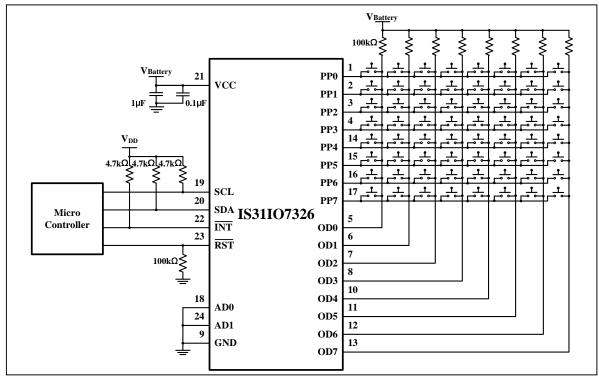

## TYPICAL APPLICATION CIRCUIT

Figure 1 Typical Application Circuit

#### **PIN CONFIGURATION**

| Package | Pin Configuration (Top View)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| QFN-24  | $\begin{array}{c} & 1 \\ PP0 \\ PP1 \\ \hline 12 \\ PP2 \\ \hline 12 \\ PP3 \\ \hline 4 \\ PP3 \\ \hline 4 \\ PP3 \\ \hline 12 \\ \hline 12 \\ \hline 12 \\ PP3 \\ \hline 12 $ |  |  |

#### **PIN DESCRIPTION**

| No.        | Pin         | Description                   |  |

|------------|-------------|-------------------------------|--|

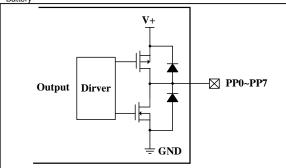

| 1~4, 14~17 | PP0~PP7     | Output ports.                 |  |

| 5~8, 10~13 | OD0~OD7     | Input ports.                  |  |

| 9          | GND         | Ground.                       |  |

| 18         | AD0         | Address setting.              |  |

| 19         | SCL         | I2C serial clock.             |  |

| 20         | SDA         | I2C serial data.              |  |

| 21         | VCC         | Power supply voltage.         |  |

| 22         | INT         | Interrupt output, active low. |  |

| 23         | RST         | Reset input, active low.      |  |

| 24         | AD1         | Address setting.              |  |

|            | Thermal Pad | Connect to GND.               |  |

Copyright © 2011 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any time without notice. ISSI assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to obtain the latest version of this device specification before relying on any published information and before placing orders for products. Integrated Silicon Solution, Inc. does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless Integrated Silicon Solution, Inc. receives written assurance to its satisfaction, that:

a.) the risk of injury or damage has been minimized;

b.) the user assume all such risks; and

c.) potential liability of Integrated Silicon Solution, Inc is adequately protected under the circumstances

## ORDERING INFORMATION Industrial Range: -40°C to +125°C

| Order Part No.      | Package           | QTY/Reel |

|---------------------|-------------------|----------|

| IS31IO7326-QFLS4-TR | QFN-24, Lead-free | 2500     |

## ABSOLUTE MAXIMUM RATINGS

| Supply voltage, V <sub>CC</sub>                                                              | -0.3V ~ +6.0V              |

|----------------------------------------------------------------------------------------------|----------------------------|

| Voltage at any input pin (Except PP0-PP7)                                                    | $-0.3V \sim V_{CC} + 0.3V$ |

| SCL, SDA, AD, RST, INT, OD0-OD3                                                              | -0.3V ~ +6.0V              |

| PP0-PP3                                                                                      | $-0.3V \sim V_{CC} + 0.3V$ |

| PP source output current                                                                     | ±100mA                     |

| PP/OD sink current                                                                           | 120mA                      |

| SDA sink current                                                                             | 10mA                       |

| INT sink current                                                                             | 10mA                       |

| Continuous power dissipation ( $T_A = 70^{\circ}C$ ) 24-Pin QFN (Derate 33.2mW/°C over 70°C) | 2.65W                      |

| Maximum junction temperature, T <sub>JMAX</sub>                                              | 150°C                      |

| Storage temperature range, T <sub>STG</sub>                                                  | -65°C ~ +150°C             |

| Operating temperature range, T <sub>A</sub>                                                  | −40°C ~ +125°C             |

| Solder information, vapor phase (60s)                                                        | 215°C                      |

| infrared (15s)                                                                               | 220°C                      |

| ESD HBM                                                                                      | 4kV                        |

|                                                                                              |                            |

Note:

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other condition beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### ELECTRICAL CHARACTERISTICS

$T_A$ = -40°C ~ +125°C, V<sub>CC</sub> = 2.4V ~ 5.5V, unless otherwise noted. Typical values are at  $T_A$  = 25°C, V<sub>CC</sub> = 3.3V. (*Note 1*)

| Symbol                            | Parameter                                                         | Condition                                                                        | Min. | Тур. | Max. | Units |

|-----------------------------------|-------------------------------------------------------------------|----------------------------------------------------------------------------------|------|------|------|-------|

| V <sub>CC</sub>                   | Supply voltage                                                    |                                                                                  | 2.4  |      | 5.5  | V     |

| $V_{POR}$                         | Power-on-reset voltage                                            | V <sub>cc</sub> falling                                                          |      |      | 2.35 | V     |

| I <sub>STB</sub>                  | Standby current<br>(Interface idle)                               | SCL,SDA and other digital inputs at $V_{\text{CC}}$                              |      | 0.3  | 1.9  | μA    |

| +                                 | Supply current<br>(Interface running)                             | $f_{SCL}$ = 400kHz<br>other digital inputs at V <sub>CC</sub>                    |      | 6.5  | 25   | μA    |

| VIH                               | Logic "1" input voltage                                           |                                                                                  | 1.4  |      |      | V     |

| V <sub>IL</sub>                   | Logic "0" input voltage                                           |                                                                                  |      |      | 0.4  | V     |

| I <sub>IH</sub> , I <sub>IL</sub> | Input leakage current                                             | SDA, SCL, AD0, AD1, $\overline{\text{RST}}$ , OD0~OD7 at V $_{\text{CC}}$ or GND | -0.2 |      | +0.2 | μA    |

| C <sub>IN</sub>                   | Input capacitance<br>SDA, SCL, AD0, AD1, RST,<br>OD0~OD7, PP0~PP7 | (Note 2)                                                                         |      | 10   |      | pF    |

|                                   |                                                                   | V <sub>CC</sub> = 2.5V, I <sub>SINK</sub> = 10mA                                 |      |      | 200  |       |

| V <sub>OL</sub>                   | Logic "0" output voltage                                          | V <sub>CC</sub> = 3.3V, I <sub>SINK</sub> = 15mA                                 |      |      | 240  | mV    |

|                                   |                                                                   | V <sub>CC</sub> = 5.0V, I <sub>SINK</sub> = 20mA                                 |      |      | 250  |       |

| V <sub>OLINT</sub>                | Output low-voltage INT                                            | I <sub>SINK</sub> = 5mA                                                          |      |      | 180  | mV    |

|                                   | Time to scan key matrix                                           | Configuration Register bit SD = 0                                                |      | 16   |      |       |

| t <sub>SCAN</sub>                 | completely                                                        | Configuration Register bit SD = 1                                                |      | 9    |      | ms    |

## TIMING CHARACTERISTICS

$T_A$  = -40°C ~ +125°C,  $V_{CC}$  = 2.4V ~ 5.5V, unless otherwise noted. Typical values are at  $T_A$  = 25°C,  $V_{CC}$  = 3.3V. (Note 3)

| Symbol               | Parameter                                          | Condition | Min. | Тур.       | Max. | Units |

|----------------------|----------------------------------------------------|-----------|------|------------|------|-------|

| f <sub>SCL</sub>     | Serial-clock frequency                             |           |      |            | 400  | kHz   |

| t <sub>BUF</sub>     | Bus free time between a STOP and a START condition |           | 1.3  |            |      | μs    |

| t <sub>hd, sta</sub> | Hold time (repeated) START condition               |           | 0.6  |            |      | μs    |

| t <sub>su, sta</sub> | Repeated START condition setup time                |           | 0.6  |            |      | μs    |

| t <sub>su, sto</sub> | STOP condition setup time                          |           | 0.6  |            |      | μs    |

| t <sub>HD, DAT</sub> | Data hold time                                     | (Note 3)  |      |            | 0.9  | μs    |

| t <sub>su, dat</sub> | Data setup time                                    |           | 100  |            |      | ns    |

| t <sub>LOW</sub>     | SCL clock low period                               |           | 1.3  |            |      | μs    |

| t <sub>HIGH</sub>    | SCL clock high period                              |           | 0.7  |            |      | μs    |

| t <sub>R</sub>       | Rise time of both SDA and SCL signals, receiving   | (Note 4)  |      | 20 + 0.1Cb | 300  | ns    |

| t <sub>F</sub>       | Fall time of both SDA and SCL signals, receiving   | (Note 4)  |      | 20 + 0.1Cb | 300  | ns    |

| t <sub>F, TX</sub>   | Fall time of SDA transmitting                      | (Note 4)  |      | 20 + 0.1Cb | 250  | ns    |

| t <sub>SP</sub>      | Pulse width of spike suppressed                    | (Note 5)  |      | 50         |      | ns    |

| C <sub>b</sub>       | Capacitive load for each bus line                  |           |      |            | 400  | pF    |

| t <sub>w</sub>       | RST pulse width                                    |           | 500  |            |      | ns    |

| t <sub>RST</sub>     | RST rising to START condition setup time           |           | 1    |            |      | μs    |

#### PORT AND INTERRUPT TIMING CHARACTERISTICS

T = -40°C ~ +125°C, V<sub>CC</sub> = 2.4V ~ 5.5V, unless otherwise noted. Typical values are at T<sub>A</sub> = 25°C, V<sub>CC</sub> = 3.3V (*Note 3*)

| Symbol           | Parameter                             | Condition              | Min. | Тур. | Max. | Untis |

|------------------|---------------------------------------|------------------------|------|------|------|-------|

| t <sub>PV</sub>  | Port output data valid                | C <sub>L</sub> ≤ 100pF |      |      | 4    | μs    |

| t <sub>PSU</sub> | Port input setup time                 | C <sub>L</sub> ≤ 100pF | 0    |      |      | μs    |

| t <sub>PH</sub>  | Port input hold time                  | C <sub>L</sub> ≤ 100pF | 4    |      |      | μs    |

| t <sub>IV</sub>  | INT input data valid time             | C <sub>L</sub> ≤ 100pF |      |      | 4    | μs    |

| t <sub>IR</sub>  | INT reset delay time from acknowledge | C <sub>L</sub> ≤ 100pF |      |      | 4    | μs    |

Note 1: All parameters are tested at T<sub>A</sub> = 25°C. Specifications over temperature are guaranteed by design.

Note 2: Guaranteed by design.

Note 3: A master device must provide a hold time of at least 300ns for the SDA signal (referred to VIL of the SCL signal) in order to bridge the undefined region of SCL's falling edge.

Note 4: Cb = total capacitance of one bus line in pF. ISINK  $\leq$  6mA. tR and tF measured between 0.3 × V<sub>CC</sub> and 0.7 × V<sub>CC</sub>.

Note 5: Input filters on the SDA and SCL inputs suppress noise spikes less than 50ns.

## DETAILED DESCRIPTION

### **I2C INTERFACE**

The IS31IO7326 uses a serial bus, which conforms to the I2C protocol, to control the chip's functions with two wires: SCL and SDA. The IS31IO7326 has a 7-bit slave

address (A7:A1), followed by the  $R/\overline{W}$  bit, A0. Set A0 to "0" for a write command and set A0 to "1" for a read command. The bit A2:A1 are selected by the connection of AD1/AD0 pin.

The complete slave address is:

#### Table 1 Slave Address:

| Bit     | A7:A3 | A2  | A1  | A0  |

|---------|-------|-----|-----|-----|

| Default | 10110 | AD1 | AD0 | 0/1 |

AD1/AD0 connects to VCC, AD1/AD0=1; AD1/AD0 connects to GND, AD1/AD0=0;

The SCL line is uni-directional. The SDA line is bi-directional (open-collector) with a pull-up resistor (typically 4.7k $\Omega$ ). The maximum clock frequency specified by the I2C standard is 400kHz. In this discussion, the master is the microcontroller and the slave is the IS31IO7326.

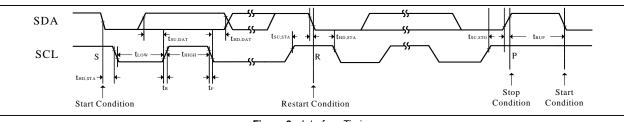

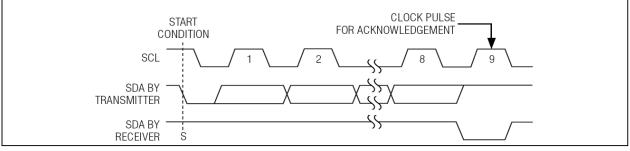

The timing diagram for the I2C is shown in Figure 3. The SDA is latched in on the stable high level of the SCL. When there is no interface activity, the SDA line should be held high.

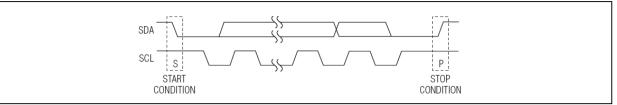

The "START" signal is generated by lowering the SDA signal while the SCL signal is high (Figure 4). The start signal will alert all devices attached to the I2C bus to check the incoming address against their own chip address.

The 8-bit chip address is sent next, most significant bit first. Each address bit must be stable while the SCL level is high.

After the last bit of the chip address is sent, the master checks for the IS31IO7326's acknowledge. The master releases the SDA line high (through a pull-up resistor). Then the master sends an SCL pulse. If the IS31IO7326 has received the address correctly, then it holds the SDA line low during the SCL pulse. If the SDA line is not low, then the master should send a "STOP" signal (discussed later) and abort the transfer.

Following acknowledge of IS31IO7326, the register address byte is sent, most significant bit first. IS31IO7326 must generate another acknowledge indicating that the register address has been received.

An 8-bit data byte is sent next, most significant bit first. Each data bit should be valid while the SCL level is stable high. After the data byte is sent, the IS31IO7326 must generate another acknowledge to indicate that the data was received.

The "STOP" signal ends the transfer. To signal "STOP", the SDA signal goes high while the SCL signal is high (Figure 4).

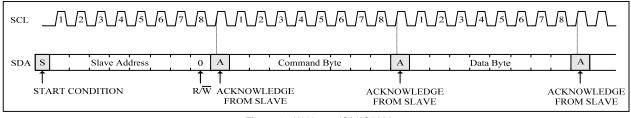

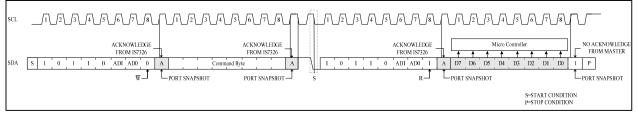

### WRITING TO THE REGISTERS

Transmit data to the IS31IO7326 by sending the device slave address and setting the LSB to "0". The command byte is sent after the address and determines which registers receive the data following the command byte (Figure 2).

#### **READING PORT REGISTERS**

To read the device data, the bus master must first send

the IS31IO7326 address with the  $R/\overline{W}$  bit set to "0", followed by the command byte, which determines which register is accessed. After a restart, the bus master must then send the IS31IO7326 address with

the R/W bit set to "1". Data from the register defined by the command byte is then sent from the IS31IO7326 to the master (Figure 6).

#### Figure 2 Writing to IS31IO7326

Figure 3 Interface Timing

#### Figure 4 START and STOP Conditions

Figure 5 Acknowledge Signal

Figure 6 Reading I/O Ports of IS31IO7326

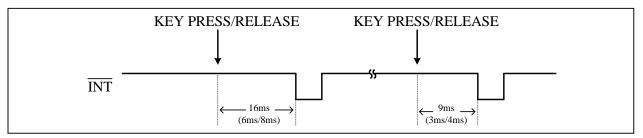

Figure 7 INT Timing

## **REGISTER DEFINITION**

### Table 2 Register Function

| Address | Name                   | Function                                   | Default   | Table |

|---------|------------------------|--------------------------------------------|-----------|-------|

| 08h     | Configuration Register | Configure the keypad scan function         | 0001 0000 | 3     |

| 10h     | Key Status Register    | Contains the information of the key events | 0000 0000 | 4     |

### Table 3 08h Configuration Register

| Bit     | D7       | D6:D5 | D4 | D3 | D2 | D1:D0 |

|---------|----------|-------|----|----|----|-------|

| Name    | Reserved | ACI   | DE | SD | LE | LT    |

| Default | 0        | 00    | 1  | 0  | 0  | 00    |

The Configuration Register is used to configure the keypad scan function.

| ACI | Auto Clear | INT |

|-----|------------|-----|

|     |            |     |

- 00 Auto clear INT disabled

- 01 Auto clear INT in 5ms

- 10 Auto clear INT in 10ms

- DE Input Port Filter Enable

- 0 Input port filter disable

- 1 Input port filter enable

- **SD** Key Scan Debounce Time

- 0 Double debounce time (6ms, 8ms)

- 1 Normal debounce time (3ms, 4ms)

- LE Long-pressed Key Detect Enable 0 Disable

- 1 Enable

- LT Long-pressed Key Detect Delay Time 00 20ms

- 00 20ms

- 01 40ms

- 10 1s

- 11 2s

## Table 4 10h Key Status Register

| Bit     | D7 | D6 | D5:D0  |

|---------|----|----|--------|

| Name    | DN | KS | KM     |

| Default | 0  | 0  | 000000 |

The Key Status Register contains the information of the key events that have been debounced (see the Table 5 of the key mapping).

- DN Indicate Data Number

- 0 One key event to report

- 1 More than one key to report

- KS Key State

- 0 Key released

- 1 Key pressed

- KM Key Mapping

KM denotes which of the 64 keys have been debounced and the keys are numbered as shown in the Table 5.

When the Key Status Register is read over (DN=0), the register is set to "0000 0000", and the  $\overline{INT}$  is cleared.

### Table 5 Key Mapping (D5:D0)

|     | PP0    | PP1    | PP2    | PP3    | PP4    | PP5    | PP6    | PP7    |

|-----|--------|--------|--------|--------|--------|--------|--------|--------|

| OD0 | 000000 | 000001 | 000010 | 000011 | 000100 | 000101 | 000110 | 000111 |

| OD1 | 001000 | 001001 | 001010 | 001011 | 001100 | 001101 | 001110 | 001111 |

| OD2 | 010000 | 010001 | 010010 | 010011 | 010100 | 010101 | 010110 | 010111 |

| OD3 | 011000 | 011001 | 011010 | 011011 | 011100 | 011101 | 011110 | 011111 |

| OD4 | 100000 | 100001 | 100010 | 100011 | 100100 | 100101 | 100110 | 100111 |

| OD5 | 101000 | 101001 | 101010 | 101011 | 101100 | 101101 | 101110 | 101111 |

| OD6 | 110000 | 110001 | 110010 | 110011 | 110100 | 110101 | 110110 | 110111 |

| OD7 | 111000 | 111001 | 111010 | 111011 | 111100 | 111101 | 111110 | 111111 |

#### Examples

- 1. If the key PP1-OD3 pressed only, and other keys keep released state, the INT asserts, the data in Key Status Register would be "0101 1001";

- 2. If the key PP4-OD6 released only, and other keys keep released state, the INT asserts, the data in Key Status Register would be "0011 0100";

- 3. If the key PP2-OD4 and PP3-OD7 are pressing, then PP2-OD4 released, the INT asserts, the first data in Key Status Register would be "1010 0010", the second data would be "0111 1011". Then judge the MSB (bit DN) in

the second data is "0". Data has read over, and  $\overline{INT}$  goes to high.

We must read over the data in Key Status Register when the  $\overline{INT}$  asserts. When judge the MSB (bit DN) in the data is "0", stop reading the Key Status Register. If there are some keys connected to the same OD port pressing at the same time, IS31IO7326 only can detect the first pressed key and others will ignore.

#### APPLICATION INFORMATION

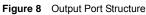

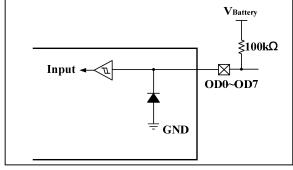

## INPUT AND OUTPUT PORT STRUCTURE

A 100k $\Omega$  pull-up resistor will force input port high at V<sub>Battery</sub>.

#### **POWER-ON RESET**

The IS31IO7326 contains an integral power-on-reset circuit that ensures all registers are reset to a known state on power-up. When  $V_{CC}$  rises above 2.4V, the circuit releases the registers and the I2C interface for normal operation. When  $V_{CC}$  drops to less than  $V_{POR}$ , the IS31IO7326 resets all register contents to the default value.

## **RST I2C RESET CONTROL**

The active-low  $\overline{\text{RST}}$  input voids any I2C transaction involving the IS31IO7326, forcing the IS31IO7326 into the I2C STOP condition. A reset does not affect the interrupt output.

#### STANDBY MODE

When the serial interface is idle, the IS31IO7326 automatically enters standby mode, drawing minimal supply current.

## **KEYPAD AUTO SCAN**

The IS31IO7326 can support an 8×8 matrix keypad scan. The 8 input ports (OD ports) need a  $100k\Omega$  pull-up resistor for each column, the 8 output ports (PP ports) for the rows pull low in standby mode.

If a change of the state of the keypad is detected, the keypad would be scanned thrice between the debounce delay. When the state changes have been reliably captured, the key event(s) are encoded and

written to temporary key status registers. The INT asserts when the key event(s) is (are) stored. Reading the Key Status Register reports the key events in the order of lowest encoding value to the highest (see

Table 5). The  $\overline{INT}$  will remain low until all of the key events are read, with one exception: When the

Auto-Clear INT is enabled, if all of the key event data

is not read before the programmed time, the  $\overline{\text{INT}}$  will return high after the programmed time. However the temporary key status registers will remain unchanged and the key event data may continue to be read until another key event is detected.

### DEBOUNCE

When the bit SD of the Configuration Register (08h) is set to "0" and there is a change of the state of the keypad, the keypad scans first and stores the data in temporary registers, then waits for about 6ms (3ms) and scans again, then waits for another 8ms (4ms) and scans a final time. If the results are the same, the data is latched into the temporary key status registers and

the INT asserted. Otherwise, the scan is halted and the device returns to standby mode. No data is latched

into the temporary key status registers and the  $\overline{\text{INT}}$  is not asserted.

#### LONG-PRESSED KEY DETECT

When the bit LE of the Configuration Register (08h) is set to "0", this function is disabled. When LE is set to "1", this function is enabled. When a key is pressed for a long period of time, the chip automatically scans

again after the INT is deasserted. When the key is still

pressed, the INT asserts again and the key event is latched into the temporary key status registers. The scanning continues until all of the keys are released.

The delay time between the INT deasserting to the next scan beginning is set by the Configuration Register (08h) bits LT.

## **KEY EVENT INTERRUPT (INT)**

Once there is key event code latched in the temporary key status registers, the device produces an interrupt

signal to the MCU on the  $\overline{\text{INT}}$  pin. When the  $\overline{\text{INT}}$  is asserted, any keypad state changes are ignored. The

INT will remain low until all of the key events are read,

with one exception: When the Auto-Clear  $\overline{INT}$  is enabled, if all of the key event data is not read before the programmed time, the  $\overline{INT}$  will return high after

the programmed time. However the temporary key status registers will remain unchanged and the key event data may continue to be read until another key event is detected. After all of the key events have been read, the device returns to standby mode waiting for the next scan.

## AUTO-CLEAR INT FUNCTION

When the ACI bits of the Configuration Register (08h) are set to "01" or "10", this function is enabled. Setting the ACI bits to "00" disables the function. When

enabled, the INT would be cleared in 5ms or 10ms after it asserts if there is no read of the Key Status Register. The data in the temporary key status

registers does not change when the INT goes low. The Key Status Register can be read regardless of whether

the  $\overline{\text{INT}}$  is high or not. However, when the  $\overline{\text{INT}}$  is cleared and there is new key event activity before the old key event data is read, the temporary key status

registers are rewritten and the  $\overline{\text{INT}}$  asserts again. In this case, the previous key event data is lost and only the new key event(s) can be read.

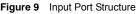

### THE INPUT PORT FILTER

The bit DE of the Configuration Register (08h) is used to enable the input port filter. When DE is set to "0", the input port filter is disabled, and the chip responds to any changes at the input port. When DE is set to "1", the input port filter is enabled and any glitch shorter than 100ns is filtered. If the input pulse width is greater than 100ns, the chip responds (Figure 10).

Figure 10 Input port debounce function

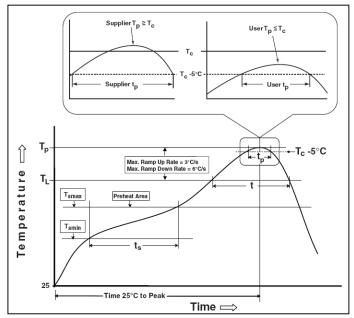

## **CLASSIFICATION REFLOW PROFILES**

| Profile Feature                                                                                    | Pb-Free Assembly                 |  |  |

|----------------------------------------------------------------------------------------------------|----------------------------------|--|--|

| Preheat & Soak<br>Temperature min (Tsmin)<br>Temperature max (Tsmax)<br>Time (Tsmin to Tsmax) (ts) | 150°C<br>200°C<br>60-120 seconds |  |  |

| Average ramp-up rate (Tsmax to Tp)                                                                 | 3°C/second max.                  |  |  |

| Liquidous temperature (TL)<br>Time at liquidous (tL)                                               | 217°C<br>60-150 seconds          |  |  |

| Peak package body temperature (Tp)*                                                                | Max 260°C                        |  |  |

| Time (tp)** within 5°C of the specified<br>classification temperature (Tc)                         | Max 30 seconds                   |  |  |

| Average ramp-down rate (Tp to Tsmax)                                                               | 6°C/second max.                  |  |  |

| Time 25°C to peak temperature                                                                      | 8 minutes max.                   |  |  |

Figure 11 Classification profile

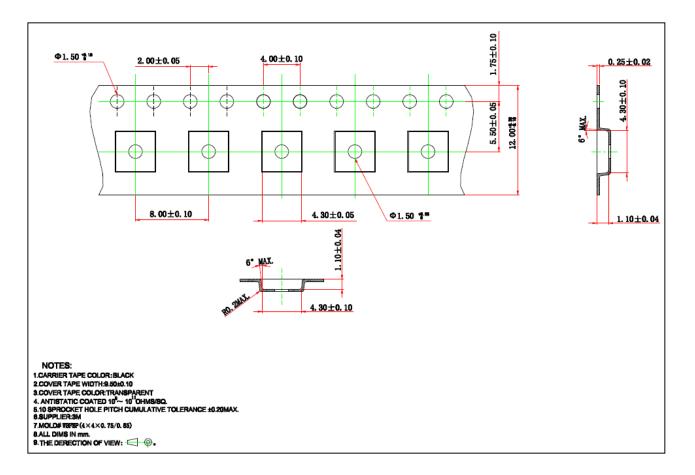

## TAPE AND REEL INFORMATION

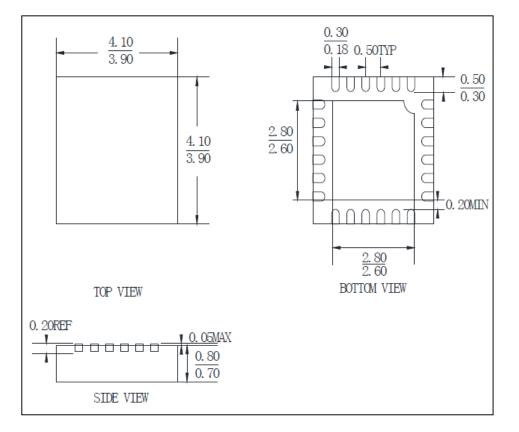

## PACKAGE INFORMATION

## QFN-24

Note: All dimensions in millimeters unless otherwise stated.