## **MULTI-FUNCTION I/O DRIVER**

#### August 2012

#### **GENERAL DESCRIPTION**

The IS31IO7325 2-wire serial-interfaced peripheral features 16 I/O ports. Ports are divided into eight push pull I/Os and eight open-drain I/Os and transition detection.

Any of the 16 I/O ports can be configured as an input or an output. All I/O ports configured as inputs are continuously monitored for state changes (transition

detection). State changes are indicated by the INT output. The interrupt is latched, allowing detection of transient changes. When the IS31IO7325 is subsequently read through the serial interface, any pending interrupt is cleared.

The open-drain outputs are rated to sink 20mA at 0.22V headroom, and are capable of driving LEDs.

The  $\overrightarrow{RST}$  input clears the serial interface, terminating any I<sup>2</sup>C communication to or from the IS31IO7325. The IS31IO7325 uses two address inputs to allow 4 I<sup>2</sup>C slave addresses. The slave address also determines the power-up logic state for the I/O ports.

#### FEATURES

- 400kHz I<sup>2</sup>C serial interface

- 2.4V to 5.5V operation

- 8 push-pull I/O ports

- 8 open-drain I/O ports, rated to 20mA sink current at 0.22V headroom

- Selectable I/O port power-up default logic states

- INT output alerts change on inputs

- Low 0.3µA (Typ.) standby current

- -40°C ~ +125°C temperature range

#### APPLICATIONS

- Cell phones

- Notebooks

- SAN/NAS

- Satellite radio

- Servers

- Automotive

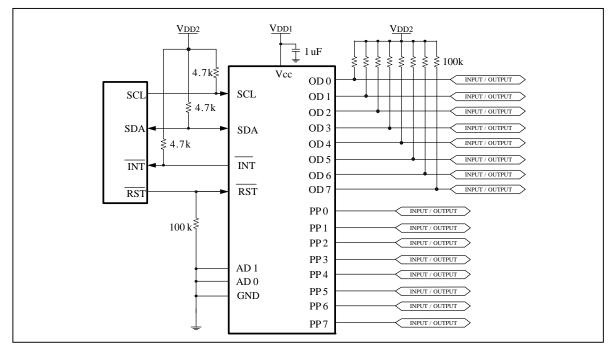

## TYPICAL APPLICATION CIRCUIT

#### Note:

V<sub>DD1</sub>: 2.4V~5.5V, 2.8V is recommended.

$V_{\text{DD2}}$ : 1.4V~5.5V,  $V_{\text{DD2}}{\leq}V_{\text{DD1,}}$  2.8V is recommended.

$V_{\mbox{\tiny DD2}}$  should be turned off when system power off because OD ports are open default!

$V_{DD2} = V_{bat}$  is forbidden.

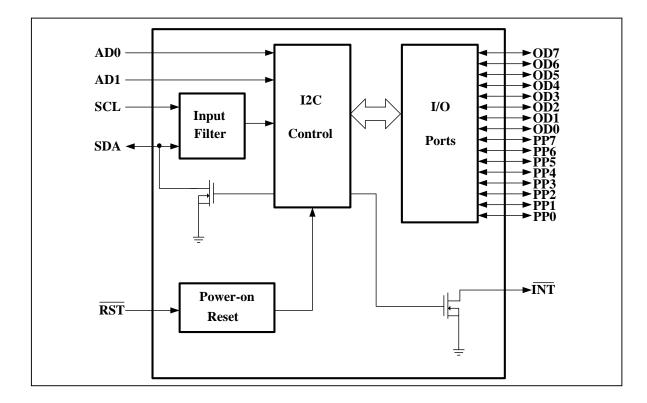

## FUNCTIONAL BLOCK DIAGRAM

Copyright © 2012 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any time without notice. ISSI assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to obtain the latest version of this device specification before relying on any published information and before placing orders for products. Integrated Silicon Solution, Inc. does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless Integrated Silicon Solution, Inc. receives written assurance to its satisfaction, that:

a.) the risk of injury or damage has been minimized;

c.) potential liability of Integrated Silicon Solution, Inc is adequately protected under the circumstances

b.) the user assume all such risks; and

## **PIN CONFIGURATION**

| Package | Pin Configuration (Top View)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| QFN-24  | TOS       01       PP7       PP6       PP7         VGS       02       1       1       1       1         VGS       02       1       1       1       1       1         VGS       02       1       1       1       1       1       1         VGS       02       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       < |

| SOP-24  | PP0       1       24       AD1         PP1       2       23       RST         PP2       3       22       INT         PP3       4       21       VCC         OD0       5       20       SDA         OD1       6       19       SCL         OD2       7       18       AD0         OD3       8       17       PP7         GND       9       16       PP6         OD4       10       15       PP5         OD5       11       14       PP4         OD6       12       13       OD7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

## **PIN DESCRIPTION**

| No.        | Pin             | Description                                                                                                    |  |  |  |  |  |

|------------|-----------------|----------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 1~4, 14~17 | PP0~PP7         | CMOS push-pull I/O ports.                                                                                      |  |  |  |  |  |

| 5~8, 10~13 | OD0~OD7         | Open-drain I/O ports.                                                                                          |  |  |  |  |  |

| 9          | GND             | Ground.                                                                                                        |  |  |  |  |  |

| 18,24      | AD0, AD1        | Address inputs. Select device slave address with AD0 and AD1.                                                  |  |  |  |  |  |

| 19         | SCL             | I <sup>2</sup> C-compatible serial-clock input.                                                                |  |  |  |  |  |

| 20         | SDA             | I <sup>2</sup> C-compatible serial-data I/O.                                                                   |  |  |  |  |  |

| 21         | V <sub>cc</sub> | Positive supply voltage. Bypass $V_{\text{CC}}$ to GND with a ceramic capacitor of at least 0.1 $\mu\text{F}.$ |  |  |  |  |  |

| 22         | ĪNT             | Interrupt output, active low. INT is an open-drain output.                                                     |  |  |  |  |  |

| 23         | RST             | Reset input, active low. Drive $\overrightarrow{RST}$ low to clear the 2-wire interface.                       |  |  |  |  |  |

|            | Thermal Pad     | Connect to GND.                                                                                                |  |  |  |  |  |

## ORDERING INFORMATION Industrial Range: -40°C to +125°C

| Order Part No.      | Package           | QTY       |  |  |  |  |  |

|---------------------|-------------------|-----------|--|--|--|--|--|

| IS31IO7325-QFLS4-TR | QFN-24, Lead-free | 2500/Reel |  |  |  |  |  |

| IS31IO7325-GRLS4    | SOP-24, Lead-free | 30/Tube   |  |  |  |  |  |

## ABSOLUTE MAXIMUM RATINGS

| Supply voltage, V <sub>DD</sub>                 | -0.3V ~ +6.0V                 |

|-------------------------------------------------|-------------------------------|

| SCL, SDA, AD, RST, INT, OD0-OD7                 | -0.3V ~ +6.0V                 |

| PP0-PP7                                         | -0.3V ~ V <sub>CC</sub> +0.3V |

| PP source output current                        | ±100mA                        |

| PP/OD sink current                              | 120mA                         |

| SDA sink current                                | 10mA                          |

| INT sink current                                | 10mA                          |

| Maximum junction temperature, T <sub>JMAX</sub> | 150°C                         |

| Storage temperature range, T <sub>STG</sub>     | -65°C ~ +150°C                |

| Operating temperature range, T <sub>A</sub>     | −40°C ~ +125°C                |

| Nata                                            |                               |

Note:

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other condition beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$V_{CC}$  = 2.4V ~ 5.5V,  $T_A$  = 25°C, unless otherwise noted. Typical values are  $V_{CC}$  = 3.3V,  $T_A$  = 25°C. (Note 1)

| Symbol                            | Parameter                              | Condition                                                  | Min.                 | Тур. | Max. | Unit |  |

|-----------------------------------|----------------------------------------|------------------------------------------------------------|----------------------|------|------|------|--|

| V <sub>CC</sub>                   | Supply voltage                         |                                                            | 2.4                  |      | 5.5  | V    |  |

| V                                 | Dower on react voltage                 | $V_{CC}$ falling, Temp = -40°C                             |                      |      | 2.35 | v    |  |

| $V_{POR}$                         | Power-on-reset voltage                 | $V_{CC}$ falling, Temp = -20°C                             |                      |      | 2.3  | v    |  |

| I <sub>STB</sub>                  | Standby current<br>(Interface idle)    | SCL and SDA and other digital inputs at $V_{\text{CC}}$    |                      | 0.3  | 1.9  | μA   |  |

| +                                 | Supply current<br>(Interface running)  | $f_{SCL}$ = 400kHz, other digital inputs at $V_{CC}$       |                      | 8    | 20   | μA   |  |

| V <sub>IH</sub>                   | Input high-voltage                     | SDA, SCL, AD0, AD1, RST,<br>OD0~OD7, PP0~PP7               | 1.4                  |      |      | V    |  |

| V <sub>IL</sub>                   | Input low-voltage                      | SDA, SCL, AD0, AD1, RST,<br>OD0~OD7, PP0~PP7               |                      |      | 0.4  | V    |  |

| I <sub>IH</sub> , I <sub>IL</sub> | Input leakage current                  | SDA, SCL, AD0, AD1, RST,<br>OD0~OD7, PP0~PP7 at VCC or GND | -0.2                 |      | +0.2 | μA   |  |

| C <sub>IN</sub>                   | Input capacitance                      | SDA, SCL, AD0, AD1, RST,<br>OD0~OD7, PP0~PP7 (Note3)       |                      | 10   |      | pF   |  |

|                                   |                                        | $V_{CC}$ = 2.5V, $I_{SINK}$ = 10mA                         |                      |      | 200  |      |  |

| V <sub>OL</sub>                   | Output low voltage<br>PP0~PP7, OD0~OD7 | V <sub>CC</sub> = 3.3V, I <sub>SINK</sub> = 15mA           |                      |      | 240  | mV   |  |

|                                   | ,                                      | $V_{CC}$ = 5.0V, I <sub>SINK</sub> = 20mA                  |                      |      | 250  |      |  |

|                                   |                                        | $V_{CC}$ = 2.5V, $I_{SOURCE}$ = 5mA                        | V <sub>CC</sub> -316 |      |      |      |  |

| V <sub>OH</sub>                   | Output high voltage<br>PP0~PP7         | $V_{CC}$ = 3.3V, $I_{SOURCE}$ = 5mA                        | V <sub>CC</sub> -213 |      |      | mV   |  |

|                                   |                                        | $V_{CC}$ = 5.0V, $I_{SOURCE}$ = 10mA                       | V <sub>CC</sub> -289 |      |      |      |  |

| V <sub>OLSDA</sub>                | Output low-voltage SDA                 | I <sub>SINK</sub> = 6mA                                    |                      |      | 180  | mV   |  |

|                                   | Output low-voltage INT                 | I <sub>SINK</sub> = 5mA                                    |                      |      | 180  | mV   |  |

#### TIMING CHARACTERISTICS

$V_{CC}$  = 2.4V ~ 5.5V,  $T_A$  = -40°C ~ +125°C, unless otherwise noted. Typical values are  $V_{CC}$  = 3.3V,  $T_A$  = 25°C. (Note3)

| Symbol               | Parameter                                          | Condition | Min. | Тур.       | Max. | Unit |

|----------------------|----------------------------------------------------|-----------|------|------------|------|------|

| $f_{\text{SCL}}$     | Serial-clock frequency                             |           |      |            | 400  | kHz  |

| t <sub>BUF</sub>     | Bus free time between a STOP and a START condition |           | 1.3  |            |      | μs   |

| t <sub>HD, STA</sub> | Hold time (repeated) START condition               |           | 0.6  |            |      | μs   |

| t <sub>su, sta</sub> | Repeated START condition setup time                |           | 0.6  |            |      | μs   |

| t <sub>su, sto</sub> | STOP condition setup time                          |           | 0.6  |            |      | μs   |

| t <sub>hd, dat</sub> | Data hold time                                     | (Note2)   |      |            | 0.9  | μs   |

| t <sub>su, dat</sub> | Data setup time                                    |           | 100  |            |      | ns   |

| t <sub>LOW</sub>     | SCL clock low period                               |           | 1.3  |            |      | μs   |

| t <sub>HIGH</sub>    | SCL clock high period                              |           | 0.7  |            |      | μs   |

| t <sub>R</sub>       | Rise time of both SDA and SCL signals, receiving   | (Note4)   |      | 20 + 0.1Cb | 300  | ns   |

| t <sub>F</sub>       | Fall time of both SDA and SCL signals, receiving   | (Note4)   |      | 20 + 0.1Cb | 300  | ns   |

| $t_{F, TX}$          | Fall time of SDA transmitting                      | (Note4)   |      | 20 + 0.1Cb | 250  | ns   |

| t <sub>SP</sub>      | Pulse width of spike suppressed                    | (Note5)   |      | 50         |      | ns   |

| Cb                   | Capacitive load for each bus line                  |           |      |            | 400  | pF   |

| t <sub>w</sub>       | RST pulse width                                    |           | 500  |            |      | ns   |

| t <sub>RST</sub>     | RST rising to START condition setup time           |           | 1    |            |      | μs   |

### Port and Interrupt INT Timing Characteristic

$V_{CC} = 2.4V \sim 5.5V$ ,  $T_A = -40^{\circ}C \sim +125^{\circ}C$ , unless otherwise noted. Typical values are  $V_{CC} = 3.3V$ ,  $T_A = 25^{\circ}C$ . (Note3)

| Parameter                             | Symbol           | Condition              | Min. | Тур. | Max. | Unti |

|---------------------------------------|------------------|------------------------|------|------|------|------|

| Port output data valid                | t <sub>PV</sub>  | C∟≤ 100pF              |      |      | 4    | μs   |

| Port input setup time                 | t <sub>PSU</sub> | C <sub>L</sub> ≤ 100pF | 0    |      |      | μs   |

| Port input hold time                  | t <sub>РН</sub>  | C∟≤ 100pF              | 4    |      |      | μs   |

| INT input data valid time             | t <sub>IV</sub>  | C <sub>L</sub> ≤ 100pF |      |      | 4    | μs   |

| INT reset delay time from acknowledge | t <sub>IR</sub>  | C <sub>L</sub> ≤ 100pF |      |      | 4    | μs   |

Note 1: All parameters are tested at TA = 25°C. Specifications over temperature are guaranteed by design.

Note 2: A master device must provide a hold time of at least 300ns for the SDA signal (referred to VIL of the SCL signal) in order to bridge the undefined region of SCL's falling edge.

Note 3: Guaranteed by design.

Note 4: Cb = total capacitance of one bus line in pF. ISINK  $\leq$  6mA. tR and tF measured between 0.3  $\times$  VCC and 0.7 $\times$  VCC.

Note 5: Input filters on the SDA and SCL inputs suppress noise spikes less than 50ns.

## Table1 Power Up Default State for I/O Ports

|                 | in<br>ection    |     | Port Power Up Default |     |     |     |     |     |     |      |      |      |      |      |      |      |      |

|-----------------|-----------------|-----|-----------------------|-----|-----|-----|-----|-----|-----|------|------|------|------|------|------|------|------|

| AD1             | AD0             | PP7 | PP6                   | PP5 | PP4 | PP3 | PP2 | PP1 | PP0 | OD7  | OD6  | OD5  | OD4  | OD3  | OD2  | OD1  | OD0  |

| GND             | GND             | 0   | 0                     | 0   | 0   | 0   | 0   | 0   | 0   | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| GND             | V <sub>CC</sub> | 0   | 0                     | 0   | 0   | 1   | 1   | 1   | 1   | 0    | 0    | 0    | 0    | Hi-Z | Hi-Z | Hi-Z | Hi-Z |

| V <sub>CC</sub> | GND             | 1   | 1                     | 1   | 1   | 0   | 0   | 0   | 0   | Hi-Z | Hi-Z | Hi-Z | Hi-Z | 0    | 0    | 0    | 0    |

| V <sub>CC</sub> | $V_{CC}$        | 1   | 1                     | 1   | 1   | 1   | 1   | 1   | 1   | Hi-Z |

## Table2 Command Byte Register

| Command Byte Address(Hex) | Function                 | Power Up Default | Protocol |

|---------------------------|--------------------------|------------------|----------|

| 00                        | Input port A (OD0~OD7)   | XXXX XXXX        | R        |

| 01                        | Input port B (PP0~PP7)   | XXXX XXXX        | R        |

| 02                        | Output port A            | Refer to Table1  | R/W      |

| 03                        | Output port B            | Refer to Table1  | R/W      |

| 04                        | Port A configuration     | 0000 0000        | R/W      |

| 05                        | Port B configuration     | 0000 0000        | R/W      |

| 06                        | Port A interrupt control | 0000 0000        | R/W      |

| 07                        | Port B interrupt control | 0000 0000        | R/W      |

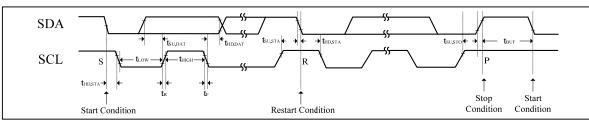

Figure 1

2-Wire Serial Interface Timing Details

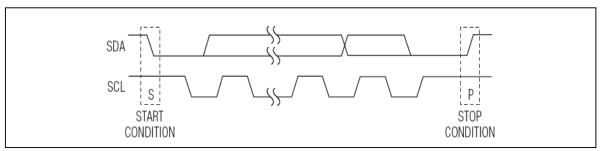

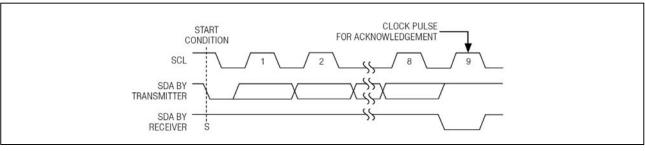

Figure 2 START and STOP Conditions

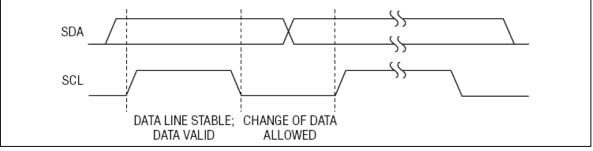

Figure 3 Bit Transfer

#### DETAILED DESCRIPTION

#### FUNCTIONAL OVERVIEW

The IS31IO7325 is a Multi-function I/O driver operating from a +2.4V to 5.5V supply with eight push-pull and eight open-drain I/O ports. Each open-drain and push-pull port is rated to sink 20mA at 0.22V headroom, and the entire device is rated to sink 320mA at 0.22V headroom into all ports combined. The outputs drive loads connected to supplies up to +5.5V.

The IS31IO7325 is set to four  $I^2C$  slave addresses using the address select inputs AD0 and AD1, and is accessed over an  $I^2C$  serial interface up to 400 kHz.

The  $\overline{\text{RST}}$  input clears the serial interface in case of a bus lockup, terminating any serial transaction to or from the IS31IO7325.

The IS31IO7325 consists of input, output port registers, configuration registers and interrupt control register. All I/O ports offer latching transition detection when configured as inputs. All input ports are continuously monitored for changes.

A latching interrupt output, INT, is programmed to flag logic changes on ports used as inputs. Data changes

on any input port forces  $\overline{INT}$  to a logic-low. Changing the I/O port level through the serial interface does not

cause an interrupt. The interrupt output  $\overline{\rm INT}\,$  is cleared successfully by reading the corresponding input/output ports.

Ports default to logic-high or logic-low on power-up in groups of four (see Table 1).

#### **INITIAL POWER-UP**

On power-up, the transition detection logic is reset,

and INT is reset. The power-up default states of the 16 I/O ports are set according to the I2C slave address selection inputs, AD0 and AD1 (see Table 1). For I/O ports used as inputs, ensure that the default states are logic-high so that the I/O ports power up in the high impedance state.

#### **POWER-ON RESET**

The IS31IO7325 contains an integral power-on-reset (POR) circuit that ensures all registers are reset to a known state on power-up. When VCC rises above VPOR (2.3V max), the POR circuit releases the registers and 2-wire interface for normal operation. When VCC drops to less than VPOR, the IS31IO7325 resets all register contents to the POR defaults.

#### **RST INPUT**

The active-low  $\overrightarrow{RST}$  input voids any I2C transaction involving the IS31IO7325, forcing the IS31IO7325 into the I2C STOP condition. A reset does not affect the interrupt output.

#### STANDBY MODE

When the serial interface is idle, the IS31IO7325 automatically enters standby mode, drawing minimal supply current.

## I/O PORT INPUT TRANSITION DETECTION

All I/O ports configured as inputs are monitored for changes since the expander was last accessed through the serial interface. The open-drain interrupt

output, INT, activates when one of the port pins changes states and only when the pin is configured as an input. The interrupt deactivates when the input/output register is read. A pin configured as an output does not cause an interrupt. Each 8-bit port register is read independently; therefore, an interrupt caused by port A (OD0~OD7) is not cleared by a read of port B (PP0~PP7)'s register.

Changing an I/O from an output to an input may cause a false interrupt to occur if the state of that I/O does not match the content of output port register. The IS31IO7325 has interrupt control register to avoid false interrupt by setting the interrupt control register bit high firstly, when the I/O state is stable, clear the interrupt control register to enable the input transition detection function.

#### ACCESSING THE IS31IO7325

#### SERIAL ADDRESSING

The IS31IO7325 operates as a slave that sends and receives data through a 2-wire interface. The interface uses a serial data line (SDA) and a serial clock line (SCL) to achieve bidirectional communication between master(s) and slave(s). A master, typically a microcontroller, initiates all data transfers to and from the IS31IO7325, and generates the SCL clock that synchronizes the data transfer (see Figure 1).

SDA operates as both an input and an open-drain output. A pull up resistor, typically 4.7k $\Omega$ , is required on SDA. SCL operates only as an input. A pull up resistor, typically 4.7k $\Omega$ , is required on SCL if there are multiple masters on the 2-wire interface, or if the master in a single-master system has an open-drain SCL output. Each transmission consists of a START condition sent by a master, followed by the IS31IO7325's 7-bit slave addresses plus R/W bits, 1 or more data bytes, and finally a STOP condition (see Figure 2).

## START AND STOP CONDITIONS

Both SCL and SDA remain high when the interface is not busy. A master signals the beginning of a transmission with a START (S) condition by transitioning SDA from high to low while SCL is high. When the master has finished communicating with the slave, the master issues a STOP (P) condition by transitioning SDA from low to high while SCL is high. The bus is then free for another transmission (see Figure 2)

#### **BIT TRANSFER**

One data bit is transferred during each clock pulse. The data on SDA must remain stable while SCL is high (Figure 3).

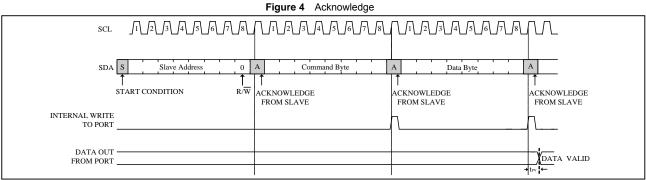

Figure 5 Writing to the IS31IO7325

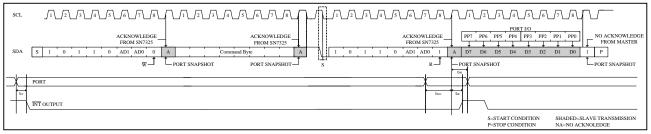

Figure 6 Reading I/O Ports of IS31IO7325

#### SLAVE ADDRESS

The IS31IO7325 has a 7-bit slave address. The 8th bit

following the 7-bit slave address is the  $R/\overline{W}$  bit. Set this bit low for a write command and high for a read command.

The complete slave address is:

| A6 | A5 | A4 | A3 | A2 | A1  | A0  | R/W |

|----|----|----|----|----|-----|-----|-----|

| 1  | 0  | 1  | 1  | 0  | AD1 | AD0 | 1/0 |

## DATA BUS TRANSACTION

The command byte is the first byte to follow the 8-bit device slave address during a write transmission (see Table 2). The command byte is used to determine which of the following registers are written or read.

## ACKNOWLEDGE

The acknowledge bit is a clocked 9th bit the recipient uses to acknowledge receipt of each byte of data (see Figure 4). Each byte transferred effectively requires 9bits. The master generates the 9th clock pulse, and the recipient pulls down SDA during the acknowledge clock pulse, such that the SDA line is stable low during the high period of the clock pulse. When the master is transmitting to the IS31IO7325, the device generates the acknowledge bit because the IS31IO7325 is the recipient. When the IS31IO7325 is transmitting to the master generates the acknowledge bit because the acknowledge bit because the acknowledge bit because the master.

#### **CONFIGURATION REGISTERS**

The configuration registers configure the directions of the I/O pins. Set the bit in the respective configuration register to enable the corresponding port as an input. Clear the bit in the configuration register to enable the corresponding port as an output.

#### INTERRUPT CONTROL REGISTERS

The interrupt control registers control the interrupt function of I/O ports when the I/O port used as input. Set the bit in the respective interrupt control register to disable the corresponding port's interrupt function. Clear the bit in the interrupt control register to enable the corresponding port's interrupt function.

#### WRITING TO PORT REGISTERS

Transmit data to the IS31IO7325 by sending the device slave address and setting the LSB to a logic zero. The command byte is sent after the address and determines which registers receive the data following the command byte.

A write to either output port groups of the IS31IO7325 starts with the master transmitting the group's slave

address with the  $R/\overline{W}\,$  bit set low. The master can now transmit the command byte and data byte.

#### **READING PORT REGISTERS**

To read the device data, the bus master must first send

the IS31IO7325 address with the  $R/\overline{W}$  bit set to zero, followed by the command byte, which determines which register is accessed. After a restart, the bus master must then send the IS31IO7325 address with

the  $R/\overline{W}$  bit set to 1. Data from the register defined by the command byte is then sent from the IS31IO7325 to the master.

The IS31IO7325 acknowledges the slave address, and

samples the ports during the acknowledge bit. INT desserts during the slave address acknowledge. When the master reads one byte from the I/O ports of the IS31IO7325 and subsequently issues a STOP condition (Figure 6), the IS31IO7325 transmits the current port data, clears the change flags, and resets

the transition detection. INT desserts during the slave acknowledge. The new snapshot data is the current port data transmitted to the master, and therefore, port changes occurring during the transmission are detected.

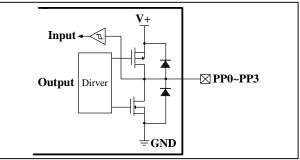

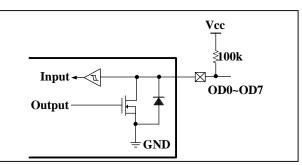

#### PORT OUTPUT SIGNAL-LEVEL TRANSLATION

The open-drain output architecture allows for level translation to higher or lower voltages than the IS31IO7325's supply. Each of the push-pull output ports has protection diodes to V+ and GND. When a port output is driven to a voltage higher than V+ or lower than GND, the appropriate protection diode clamps the output to a diode drop above V+ or below GND. When the IS31IO7325 is powered down (V+ = 0V), every output port's protection diodes to V+ and GND continue to appear as a diode clamp from each output to GND (Figure 7). Each of the I/O ports OD0~OD7 has a protection diode to GND (Figure 8). When a port is driven to a voltage lower than GND, the protection diode clamps the port to a diode drop below GND. To obtain a high voltage, Open-Drain I/O Ports should connect an resistance to Vcc(Figure 8).

In the case of LED load at OD outputs, the voltage at OD is between Vcc and GND when OD is intended high to turn off the LED, causing Icc leakage current. A 100K pull-up resistor will force OD high at Vcc and eliminate the leakage current. PP outputs can be set high at Vcc with LED load, resulting in no leakage current without any pull-up resistor.

Figure 7 IS31IO7325 Push-Pull I/O Ports Structure

Figure 8 IS31IO7325 Open-Drain I/O Ports Structure

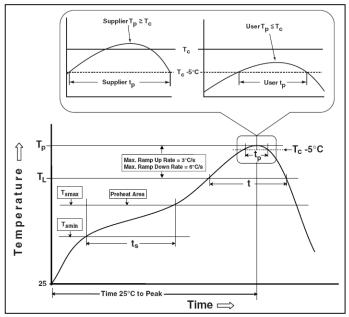

## **CLASSIFICATION REFLOW PROFILES**

| Profile Feature                                                                                               | Pb-Free Assembly                 |

|---------------------------------------------------------------------------------------------------------------|----------------------------------|

| <b>Preheat &amp; Soak</b><br>Temperature min (Tsmin)<br>Temperature max (Tsmax)<br>Time (Tsmin to Tsmax) (ts) | 150°C<br>200°C<br>60-120 seconds |

| Average ramp-up rate (Tsmax to Tp)                                                                            | 3°C/second max.                  |

| Liquidous temperature (TL)<br>Time at liquidous (tL)                                                          | 217°C<br>60-150 seconds          |

| Peak package body temperature (Tp)*                                                                           | Max 260°C                        |

| Time (tp)** within 5°C of the specified classification temperature (Tc)                                       | Max 30 seconds                   |

| Average ramp-down rate (Tp to Tsmax)                                                                          | 6°C/second max.                  |

| Time 25°C to peak temperature                                                                                 | 8 minutes max.                   |

Figure 9 Classification Profile

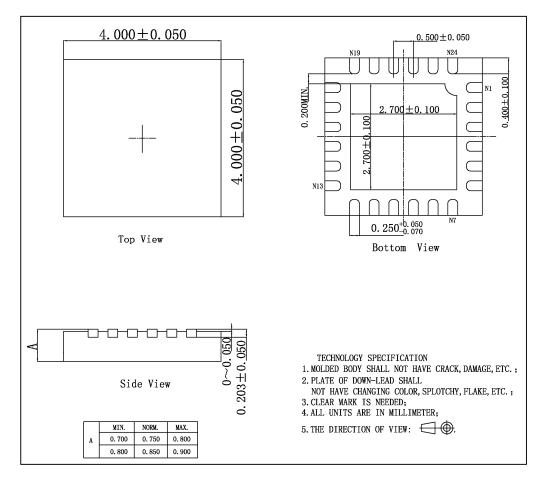

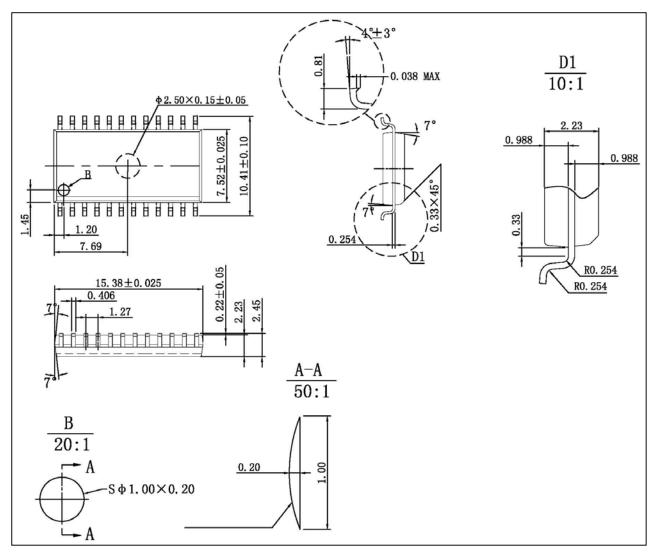

## PACKAGE INFORMATION

## QFN-24

SOP-24

Note: All dimensions in millimeters unless otherwise stated.