# Dual µPower Supervisory Circuit with Watchdog

# **FEATURES**

- Low operating voltage of 1.6V

- Low operating current of 20µA typical

- Monitors 2 supplies simultaneously

- Reset asserted down to 0.9V

- 2% accuracy over temperature range

- Open Drain (OD) or CMOS RSTB output

- 4 Reset Timeout Periods 50ms, 100ms 200ms, and 400ms

- Watch Dog Timer Function

- Independent Open Drain Watchdog Output

- TSOT-6 package

Available in Lead Free Packaging

GND WDOB 6 5 4 SP6340 6 Pin TSOT 1 3 V/1 V2 WDI **OPEN DRAIN RESET**

RSTB

# SEE PAGE 2 FOR OTHER **AVAILABLE PINOUTS**

DESCRIPTION

SP6340 and SP6342 Dual uPower Supervisory Circuit Family is a family of microprocessor reset supervisory circuits with multiple reset voltages. The family provides low voltage monitoring ability for up to two supplies with two precision factory-set thresholds. These circuits perform a single function: if any of the input supply voltages drops below its associated threshold, reset outputs are asserted. Products in the family offer watchdog functionalities. SP6340 and SP6342 are packaged in a 6-pin TSOT package. All devices are fully specified over -40°C to +85°C temperature range.

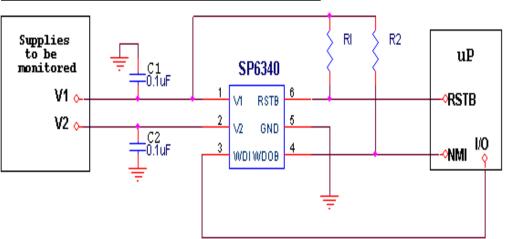

TYPICAL APPLICATION CIRCUIT

| RSTB GND WDOB                                                | RSTB GND WDOB                                          |

|--------------------------------------------------------------|--------------------------------------------------------|

| <b>SP6340</b><br>6 Pin TSOT                                  | <b>SP6342</b><br>6 Pin TSOT                            |

| 1     2     3       V1     V2     WDI       OPEN DRAIN RESET | 1     2     3       V1     V2     WDI       CMOS RESET |

| PART<br>NUMBER | V1 | V2 | Reset           | WatchDog<br>Input | WatchDog Output<br>BAR |

|----------------|----|----|-----------------|-------------------|------------------------|

| SP6340         |    |    | OD Active Low   |                   | OD Active Low          |

| SP6342         |    |    | CMOS Active Low |                   | CMOS Active Low        |

Feature and Pinout Diagram

These are stress ratings only and functional operation of the device at these ratings or any other above those indicated in the operation sections of the specifications below is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability and cause permanent damage to the device.

| Terminal Voltage (with respect to GND)<br>V1, V2 |

|--------------------------------------------------|

| Open-Drain RSTB,<br>WDOB0.3 to +6V               |

| CMOS RSTB,<br>WDOB0.3 to (V1+0.3V)               |

### ABSOLUTE MAXIMUM RATINGS

| Input Current/Output<br>Current20m         | A  |

|--------------------------------------------|----|

| WDI0.3 to (V1+0.3                          | ∨) |

| Operating Temperature<br>Range40°C to +85° | °C |

| Storage Temperature<br>Range65°C to 150°   | °C |

|                                            |    |

Thermal Resistance ØJA.....134°C/W

| PARAMETER                    |              | TYP        |              |             | CONDITIONS                                  |

|------------------------------|--------------|------------|--------------|-------------|---------------------------------------------|

| V1 = 1.6V to 5.5V; TA        | = -40°C to + | 85°C; unle | ss otherwise | noted. Typi | cal values are at TA =+25°C                 |

| Operating Voltage<br>Range   | 0.9          |            | 5.5          | V           | T <sub>A</sub> = -40°C to +85°C             |

|                              |              | 20         | 30           | uA          | V1 < 5.5V, V2 < 3.60V, all I/O<br>pins open |

| Supply Current               |              | 15         | 25           |             | V1 < 3.6V, V2 < 2.75V, all I/O<br>pins open |

|                              | 4.532        | 4.625      | 4.718        |             | Z (valid for V1 falling)                    |

|                              | 4.287        | 4.375      | 4.463        |             | Y (valid for V1 falling)                    |

|                              | 3.013        | 3.075      | 3.137        |             | X (valid for V1 falling)                    |

|                              | 2.866        | 2.925      | 2.984        |             | W (valid for V1 falling)                    |

| V1 Reset Threshold           | 2.572        | 2.625      | 2.678        | V           | V (valid for V1 falling)                    |

|                              | 2.273        | 2.320      | 2.367        |             | U (valid for V1 falling)                    |

|                              | 2.146        | 2.190      | 2.234        |             | T (valid for V1 falling)                    |

|                              | 1.636        | 1.670      | 1.704        |             | S (valid for V1 falling)                    |

|                              | 1.548        | 1.580      | 1.612        |             | R (valid for V1 falling)                    |

|                              | 2.266        | 2.313      | 2.360        |             | J (valid for V2 falling)                    |

|                              | 2.144        | 2.188      | 2.232        |             | I (valid for V2 falling)                    |

|                              | 1.631        | 1.665      | 1.698        |             | H (valid for V2 falling)                    |

|                              | 1.543        | 1.575      | 1.607        |             | G (valid for V2 falling)                    |

|                              | 1.360        | 1.388      | 1.416        |             | F (valid for V2 falling)                    |

| /2 Reset Threshold           | 1.286        | 1.313      | 1.340        | V           | E (valid for V2 falling)                    |

|                              | 1.087        | 1.110      | 1.133        |             | D (valid for V2 falling)                    |

|                              | 1.029        | 1.050      | 1.071        |             | C (valid for V2 falling)                    |

|                              | 0.816        | 0.833      | 0.850        |             | B (valid for V2 falling)                    |

|                              | 0.772        | 0.788      | 0.804        |             | A (valid for V2 falling)                    |

| Threshold 1                  |              | 0.06       |              | mV/⁰C       |                                             |

| Tempco<br>Threshold 2        |              |            |              |             |                                             |

| Tempco                       |              | 0.04       |              | mV/ºC       |                                             |

| Threshold 1                  |              |            |              |             |                                             |

| Hysteresis                   |              | 0.65       |              | %           | reference to Vth1 typical                   |

| Threshold 2<br>Hysteresis    |              | 0.5        |              | %           | reference to Vth2 typical                   |

| V1 to RST/RSTB<br>Delay      |              | 50         |              | us          | V1 = Vth1 to (Vth1-0.1V), Vth1<br>= 3.075   |

| V2 to RST/RSTB               |              | 50         |              | us          | V2 = Vth2 to (Vth2-0.1V), Vth2<br>= 1.575   |

| Delay<br>Reset Timeout       |              |            |              |             | - 1.070                                     |

| Period (T1)                  | 37           | 50         | 63           | ms          | TOPT-1                                      |

| Reset Timeout<br>Period (T2) | 74           | 100        | 126          | ms          | TOPT-2                                      |

| Reset Timeout<br>Period (T3) | 148          | 200        | 252          | ms          | ТОРТ-3                                      |

| Reset Timeout<br>Period (T4) | 296          | 400        | 504          | ms          | TOPT-4                                      |

| PARAMETER                                   | MIN         | TYP        | MAX          | UNITS        | CONDITIONS                                                                      |

|---------------------------------------------|-------------|------------|--------------|--------------|---------------------------------------------------------------------------------|

| V1 = 1.6V to 5.5V; T <sub>A</sub> =         | -40°C to +8 | 85°C; unle | ss otherwise | noted. Typic | cal values are at T₄ =+25℃                                                      |

| WDI - WATCHDOG I                            | NPUT        |            |              |              |                                                                                 |

| Watchdog Timeout<br>Period                  | 1.2         | 1.6        | 2            | sec          |                                                                                 |

| WDI Pulse Width                             | 0.1         |            |              | US           |                                                                                 |

| WDI Input<br>Threshold                      |             |            | 0.2*V1       | V            | Vil                                                                             |

| WDI Input<br>Threshold                      | 0.8*V1      |            |              | V            | Vih                                                                             |

| WDI Input Current                           | -500        |            | 500          | nA           | WDI = 0.0V or V1                                                                |

| RESET / WATCHDO                             | G OUTPU     | TS         | RSTB / WI    | OB           |                                                                                 |

| RSTB<br>(CMOS or OD)                        |             |            | 0.4          | V            | V1 = Vth1 - 0.1V, Isink = 1mA,<br>output asserted                               |

| RSTB (CMOS)                                 | 0.8*V1      |            |              | V            | V1 = Vth1 + 0.1V, Isource =<br>1mA, output not asserted                         |

| WDOB (CMOS or<br>OD)                        |             |            | 0.4          | V            | WDI = 0.0V or V1, V1 > Vth1,<br>V2 > Vth2, Isink = 1mA,<br>WDOB output asserted |

| WDOB (CMOS)                                 | 0.8*V1      |            |              | V            | V1 > Vth1, V2 > Vth2, WDOB<br>not asserted, Isource = 1mA                       |

| RSTB / WDOB<br>Output OD Leakage<br>Current |             | 2          |              | nA           | T <sub>A</sub> = +25°C                                                          |

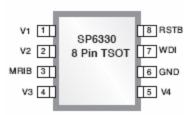

| Pin # | Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | V1   | First supply voltage input. Also powers internal circuitry. Trip threshold voltage internally set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2     | V2   | Second supply voltage input. Trip threshold voltage internally set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3     | WDI  | Watch-Dog Input pin. When no transition is detected at the WDI pin<br>for the duration of WDI timeout period, reset is asserted. WDOB<br>remains at "LOW" logic level after watchdog timeout period is<br>expired and it remains "LOW" until WDI makes a transition.<br>RST/RSTB output is not affected by the watchdog functionality in the<br>parts with separate WDOB output. The watchdog timer clears<br>whenever the reset is asserted or a transition is observed at WDI pin.                                                                                                                                                                   |

| 4     | WDOB | Watch Dog Output. Open-Drain or CMOS, active LOW. If WDI remains at "HIGH" or "LOW" logic level for longer than the watchdog timeout period, the internal watchdog timer overflows and WDOB is asserted. WDOB does not de-assert until the watchdog is cleared via transition at the WDI pin. Another scenario for WDOB to assert is when the reset output is asserted due to an under-voltage V1 or V2 condition. WDO de-asserts without a reset timeout period. Floating WDI will not disable watchdog timer in devices with dedicated WDOB output. Open-drain WDOB outputs require an external pull-up resistor. CMOS outputs are referenced to V1. |

| 5     | GND  | Common ground reference pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 6     | RSTB | Reset output. Open-Drain or CMOS, active high or low. Reset is<br>asserted when any of the supply inputs is below its trip threshold. It<br>stays asserted for 200 ms (typical / default) after the last supply input<br>traverses its trip threshold. Reset is guaranteed to be in the correct<br>state for V1>0.9V. RSTB asserts when V1 or V2 drop below their<br>corresponding reset thresholds. RSTB remains asserted for the<br>reset timeout period after V1 and V2 exceed their corresponding<br>reset thresholds. Open-drain outputs require an external pull-up<br>resistor. CMOS outputs are referenced to V1.                              |

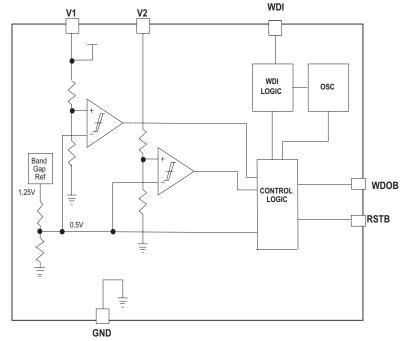

**Block Diagram**

The SP6340-SP6342 family includes a lowvoltage precision bandgap reference, two precision comparators, an oscillator, a digital counter chain, a logic control block, trimmed resistor divider chains and additional supporting circuitry. The family is designed to supervise 2 independent supply voltages. V1 and V2 supply inputs have their resistor dividers on the chip. Their trip thresholds are factory trimmed. The parts are furnished with watchdog input and output functionalities.

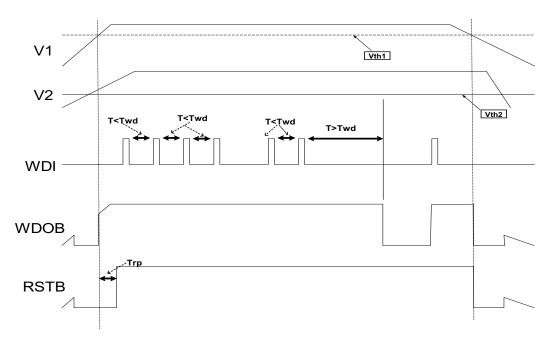

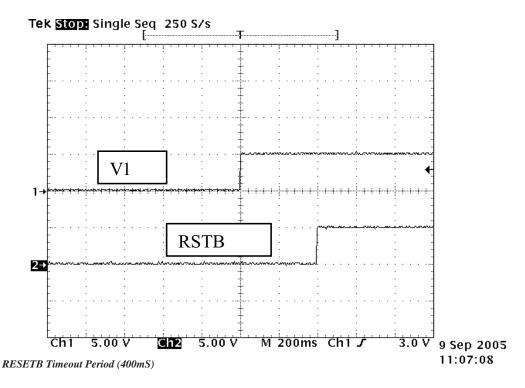

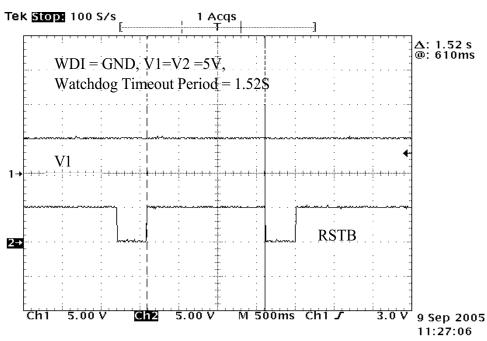

Timing Diagram for SP6340, SP6342

# **APPLICATION INFORMATION**

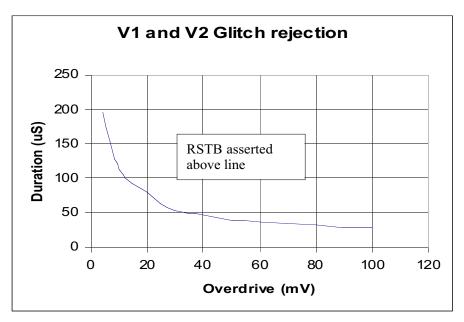

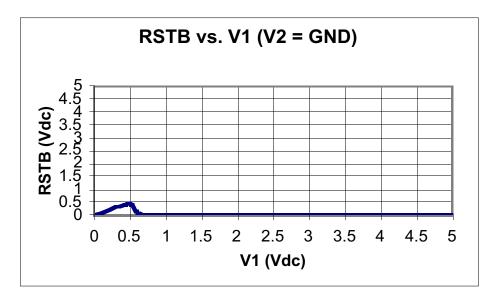

V1 and V2 Glitch Rejection

SP6340 Watchdog Timeout Period

Reset Good

9

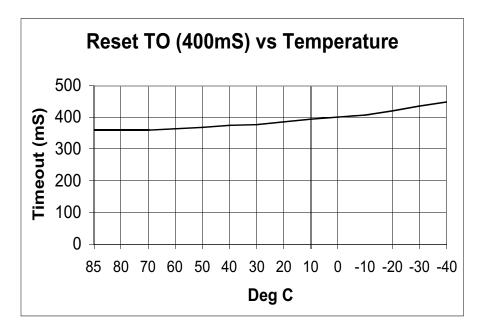

Reset Timeout vs. Temperature

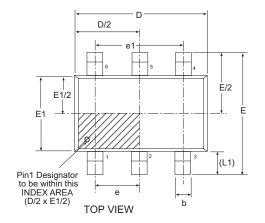

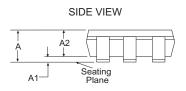

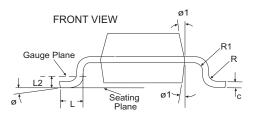

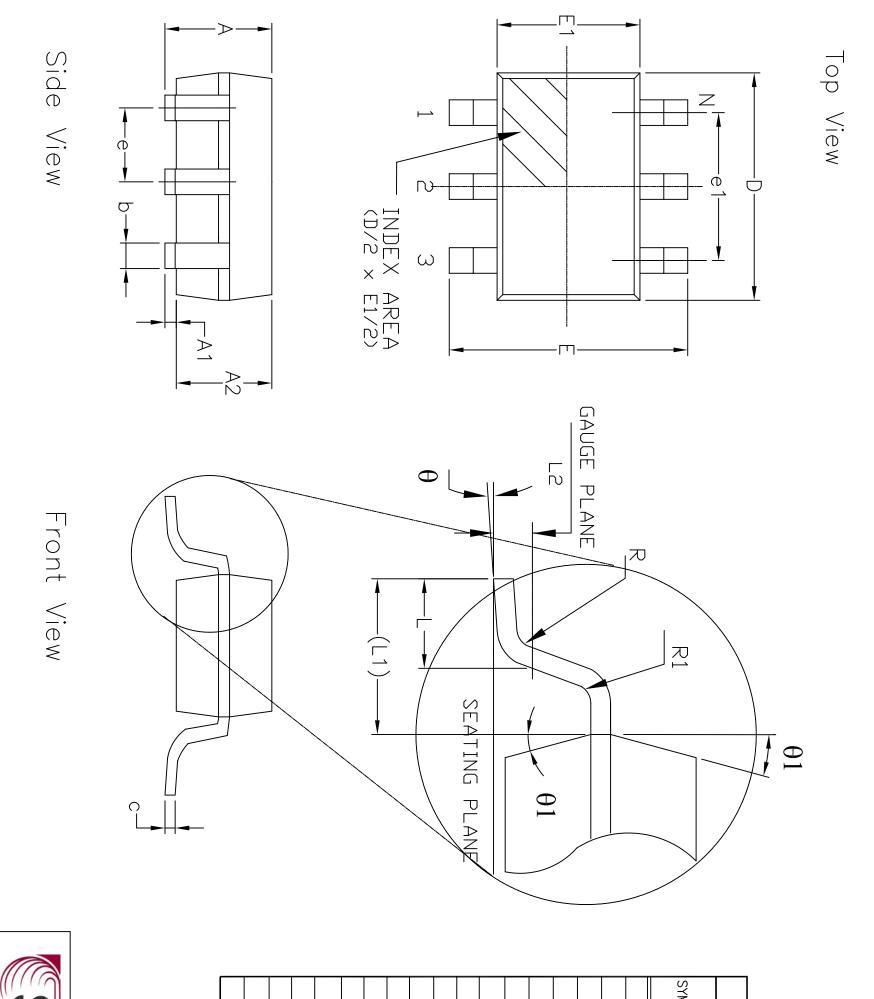

| 6 Pin 1   | ISOT    | JEDEC N                       | ИО-193 | Variation AA                                                   |         |       |  |  |  |  |

|-----------|---------|-------------------------------|--------|----------------------------------------------------------------|---------|-------|--|--|--|--|

| SYMBOL    |         | sions in Mill<br>rolling Dime |        | Dimensions in Inche<br>Conversion Factor:<br>1 Inch = 25.40 mm |         |       |  |  |  |  |

|           | MIN     | NOM                           | MAX    | MIN                                                            | NOM     | MAX   |  |  |  |  |

| A         | -       | -                             | 1.10   | -                                                              | -       | 0.043 |  |  |  |  |

| A1        | 0.00    | -                             | 0.10   | 0.000                                                          | -       | 0.004 |  |  |  |  |

| A2        | 0.70    | 0.90                          | 1.00   | 0.028                                                          | 0.036   | 0.039 |  |  |  |  |

| С         | 0.08    | -                             | 0.20   | 0.003                                                          | -       | 0.008 |  |  |  |  |

| D         |         | 2.90 BSC                      |        | 0.114 BSC                                                      |         |       |  |  |  |  |

| E         |         | 2.80 BSC                      |        | 0.110 BSC                                                      |         |       |  |  |  |  |

| E1        |         | 1.60 BSC                      |        | 0.063 BSC                                                      |         |       |  |  |  |  |

| L         | 0.30    | 0.45                          | 0.60   | 0.012                                                          | 0.018   | 0.024 |  |  |  |  |

| L1        |         | 0.60 REF                      |        | 0.024 REF                                                      |         |       |  |  |  |  |

| L2        |         | 0.25 BSC                      |        |                                                                | 0.010 B | SC    |  |  |  |  |

| Ø         | 0°      | 4°                            | 8°     | 0°                                                             | 4°      | 8°    |  |  |  |  |

| Ø1        | 4°      | 10°                           | 12°    | 4°                                                             | 10°     | 12°   |  |  |  |  |

| R         | 0.10    | -                             | -      | 0.004                                                          | -       | -     |  |  |  |  |

| R1        | 0.10    | -                             | 0.25   | 0.004                                                          | -       | 0.010 |  |  |  |  |

| b         | 0.30    | -                             | 0.50   | 0.012                                                          | -       | 0.020 |  |  |  |  |

| е         |         | 0.95 BSC                      |        |                                                                | 0.037 B | SC    |  |  |  |  |

| e1        |         | 1.90 BSC                      |        | 0.075 BSC                                                      |         |       |  |  |  |  |

| SIPEX Pkg | Signoff | Date/Rev:                     |        | JL Oct                                                         | :3-05 / | Rev A |  |  |  |  |

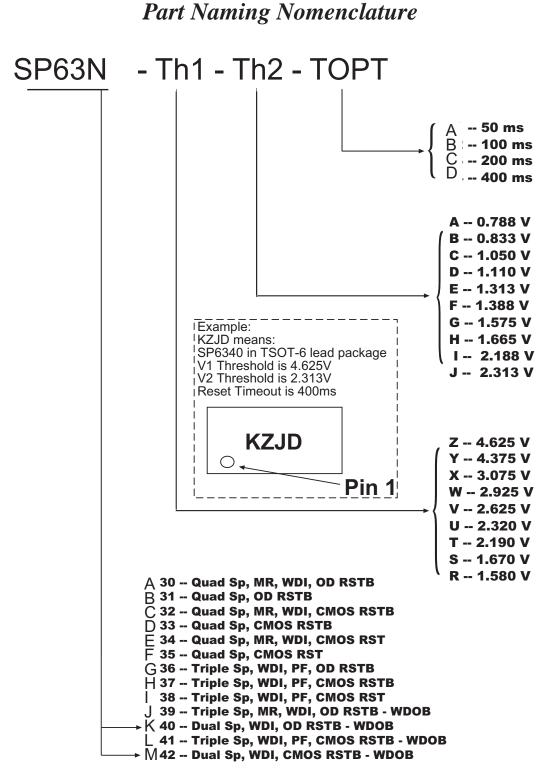

### ORDERING INFORMATION

Model

**Temperature Range**

Package Types

| SP6340EK1-L-X-X-X    | 40°C to +85°C | Lead Free 6-Pin TSOT |

|----------------------|---------------|----------------------|

| SP6340EK1-L-X-X-X/TR | 40°C to +85°C | Lead Free 6-Pin TSOT |

|                      |               |                      |

| SP6342EK1-L-X-X-X    | 40°C to +85°C | Lead Free 6-Pin TSOT |

|----------------------|---------------|----------------------|

| SP6342EK1-L-X-X-X/TR | 40°C to +85°C | Lead Free 6-Pin TSOT |

Available in Lead Free packaging only. /TR = Tape and Reel.

Pack quantity is 2,500 forTSOT-6.

Contact Factory for availability of particular voltage threshold and reset timeout options. Note that the Ordering Information denoting those options corresponds to the Part Naming Nomenclature shown on the previous page.

Ordering example: SP6340EK1-L-W-G-C/TR == W -- 2.925V for Voltage Threshold 1; G -- 1.575V for Voltage Threshold 2; and C -- 200ms reset timeout.

Sipex Corporation

Solved By Sipex<sub>TM</sub>

Headquarters and Sales Office 233 South Hillview Drive Milpitas, CA 95035 TEL: (408) 934-7500 FAX: (408) 935-7600

Sipex Corporation reserves the right to make changes to any products described herein. Sipex does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others.

# **Appendix and Web Link Information**

For further assistance:

Email: WWW Support page: Sipex Application Notes: Product Change Notices: Sipexsupport@sipex.com http://www.sipex.com/content.aspx?p=support http://www.sipex.com/applicationNotes.aspx http://www.sipex.com/content.aspx?p=pcn

Sipex Corporation Headquarters and Sales Office 233 South Hillview Drive Milpitas, CA95035 tel: (408) 934-7500 faX: (408) 935-7600

Sipex Corporation reserves the right to make changes to any products described herein. Sipex does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others.

The following sections contain information which is more changeable in nature and is therefore generated as appendices.

- 1) Package Outline Drawings

- 2) Ordering Information

If Available:

- 3) Frequently Asked Questions

- 4) Evaluation Board Manuals

- 5) Reliability Reports

- 6) Product Characterization Reports

- 7) Application Notes for this product

- 8) Design Solutions for this product

|                                                                                                                                                                                                          | Sol                                                   | ved by                             |                                                                                                                                                                                                            |                                                                                         |                                                                                                                                                                    |                                                                    | Engl                                                  | ish                | 中文                                                                 | Part Nu                                                                                                        | Adva<br>mber                                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-------------------------------------------------------|--------------------|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

|                                                                                                                                                                                                          |                                                       |                                    |                                                                                                                                                                                                            |                                                                                         |                                                                                                                                                                    |                                                                    |                                                       | Ρ                  | artnerNet                                                          | Keyword                                                                                                        | d Sea                                                    |

| Home                                                                                                                                                                                                     | Products                                              | Support                            | Contact Us                                                                                                                                                                                                 | About Us                                                                                | News                                                                                                                                                               | Inve                                                               | stors                                                 | Ca                 | reers                                                              |                                                                                                                |                                                          |

| Pro                                                                                                                                                                                                      | duct Lines                                            | SI                                 | P6340 prod                                                                                                                                                                                                 | uct details                                                                             | s You are                                                                                                                                                          | here :                                                             | Home                                                  | : Pr               | oducts :                                                           | Supervi                                                                                                        | sors                                                     |

| Power M                                                                                                                                                                                                  | lanagement                                            | Dı                                 | al micropow                                                                                                                                                                                                | ver supervi                                                                             | sory circu                                                                                                                                                         | it with                                                            | watch                                                 | ndo                | g Qui                                                              | ck Link                                                                                                        | s                                                        |

|                                                                                                                                                                                                          | t Regulators                                          |                                    |                                                                                                                                                                                                            |                                                                                         |                                                                                                                                                                    |                                                                    |                                                       |                    | •                                                                  | Downlo                                                                                                         | bad                                                      |

|                                                                                                                                                                                                          | Regulators                                            | Fe                                 | atures                                                                                                                                                                                                     |                                                                                         |                                                                                                                                                                    |                                                                    |                                                       |                    |                                                                    | Datash                                                                                                         | eet                                                      |

| <ul> <li>Linea</li> <li>Powe</li> <li>PWM</li> <li>Refe</li> <li>Supe</li> <li>USB</li> <li>Interfac</li> <li>Multi</li> <li>RS22</li> <li>RS42</li> <li>RS44</li> <li>USB</li> <li>Optical 9</li> </ul> | iprotocol<br>32<br>22<br>35<br>Storage<br>anced Power | es<br>Co<br>res<br>SP<br>J-(<br>de | Low operat<br>Monitors up<br>Reset asser<br>2% accurac<br>Open Drain<br>4 Reset Tin<br>400 ms<br>Watch Dog<br>Independer<br>6 Pin TSOT<br>ntact factory<br>6330EK1-xxx<br>C, or SP6330I<br>vice is the sup | nt Open Dra<br>package<br>for availabili<br>ptions. For sa<br>[ SP6330Ek<br>EK1-L-Z-J-C | of 20uA typ<br>es simultan<br>o 0.9V<br>perature ra<br>output<br>ls: 50ms, 1<br>ionality<br>in Watchdo<br>ty of partic<br>ampling, pl<br>(1-L-W-G-C<br>] for evalu | nge<br>00ms,<br>g Outp<br>ular th<br>ease re<br>c , or S<br>ation. | 200ms<br>ut<br>reshold<br>equest<br>P6330E<br>The SP6 | and<br>K1-<br>533( | 1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | Check<br>Availab<br>ign-In<br>Email:<br>Superv<br>Selecto<br>Applica<br>Evalua<br>Quality<br>Part No<br>SP6340 | Tech<br>Tech<br>visors<br>or<br>ations<br>tion<br>v Info |

|                                                                                                                                                                                                          | o Detector IC                                         |                                    | e family.<br><b>dering Part</b> l                                                                                                                                                                          | Number                                                                                  |                                                                                                                                                                    |                                                                    |                                                       |                    |                                                                    |                                                                                                                |                                                          |

|                                                                                                                                                                                                          |                                                       | Pa                                 | art Number                                                                                                                                                                                                 |                                                                                         | Package<br>Code                                                                                                                                                    | RoHS                                                               | MIN.<br>Temp.<br>C)                                   | (° )               | MAX.<br>Temp.(°<br>C)                                              | Status                                                                                                         | Buy                                                      |

|                                                                                                                                                                                                          |                                                       |                                    | <b>P6340</b> EK1-L<br>JPERVISORS I                                                                                                                                                                         | DUAL                                                                                    |                                                                                                                                                                    |                                                                    |                                                       |                    |                                                                    |                                                                                                                |                                                          |

|                                                                                                                                                                                                          |                                                       | FA                                 | P <b>6340</b> : CON<br>ACTORY FOR N<br>PTIONSNew!                                                                                                                                                          |                                                                                         | TSOT6                                                                                                                                                              | •                                                                  | -40                                                   |                    | 85                                                                 | CF_                                                                                                            |                                                          |

### Part Status Legend

$\ensuremath{\textbf{Active}}$  - the part is released for sale, standard product.

EOL (End of Life) - the part is no longer being manufactured, there may or may not be inventory still in stock.

**CF (Contact Factory)** - the part is still active but customers should check with the factory for availability. Longer lead-times may apply. **PRE (Pre-introduction)** - the part has not been introduced or the part number is an early version available for sample only.

OBS (Obsolete) - the part is no longer being manufactured and may not be ordered.

NRND (Not Recommended for New Designs) - the part is not recommended for new designs.

Home | Site Map | Term of Use | Privacy Policy | Contact Us

All rights reserved, Sipex 2007

B A REV.

By: J\_

| L Date:   | ickaging , |           | <b>N</b>  | z | θ1    | , R1  | עד    | L2        | L1        |       | e1       | e        | E1       | Ē        | D        | с     | р     | A2    | A1    | A     |     | SYMBOLS                  | 6 Pin     |   | DRAWING      | DRAWING     |             |             |

|-----------|------------|-----------|-----------|---|-------|-------|-------|-----------|-----------|-------|----------|----------|----------|----------|----------|-------|-------|-------|-------|-------|-----|--------------------------|-----------|---|--------------|-------------|-------------|-------------|

| 09/13,    | Approval:  | 3         | Solved by |   | 4     | 0.10  | 0.10  |           | 0         | 0.30  | _        | 0        | <u>-</u> | 2        | 2        | 0.08  | 0.30  | 0.70  | 0.00  |       | MIN | DIMENSIONS<br>(Control   | TSOT      |   | FORMAT N     | ORIGINATION | DISCRIPTION |             |

| 3/06      |            | ž         | 2         | 6 | 10° + | ;     |       | 0.25 BSC  | 0.60 REF  | 0.45  | 1.90 BSC | 0.95 BSC | .60 BSC  | 2.80 BSC | 2.90 BSC |       |       | 0.90  |       |       | NON | IENSIONS I<br>(Control U | JEDEC     |   | MODIFICATION | N           |             | RE          |

| Revision: | Drawing    | 6 PIN     | SIP       |   | 12°   | 0.25  |       | Ô         | <u> </u>  | 0.60  | C        | C        | C        | С        | C        | 0.20  | 0.50  | 1.00  | 0.10  | 1.10  | MAX | Unit)                    | M0-       |   | NOI.         |             |             | REVISION HI |

| on: B     | ng No:     | N TSOT    | EX (      |   | 4     | 0.004 | 0.004 | 0         | 0         | 0.012 | 0        | C        | 0        | C        | 0.       | 0.003 | 0.012 | 0.028 | 0.000 |       | MIN | DIMENSIONS<br>(Reference | 193 Vo    |   |              |             |             | HISTORY     |

|           | ە<br>م     | T PACKAGE | CORP      | 6 | 10°   | ;     |       | 0.010 BSC | 0.024 REF | 0.018 | 0.075 B  |          | 0.063 B  | 0.110 B  | 114      |       |       | 0.036 |       | -     | MON | (U                       | Variation |   | 09/1         | 10/0        | DATE        |             |

| Sheet:    | -PIN T     |           | ORA       |   | 12°   | 0.010 |       | Ő         | μ,        | 0.024 | BSC      | BSC      | BSC      | BSC      | BSC      | 0.008 | 0.020 | 0.039 | 0.004 | 0.043 | MAX | IN INCH<br>Unit)         | AA        |   | 09/13/06     | 10/03/05    | ĨE          |             |

| 1 OF 1    | TSOT       | OUTLINE   | ATION     |   |       |       |       | 1         | 1         | LI    |          |          |          |          | 1        |       |       |       |       |       |     |                          |           | - | ٦L           | JL          | APP'D       |             |

# Understanding and Selecting a Multi-Voltage Supervisor Featuring the SP6330 Family

# Introduction

The primary function of a microprocessor ( $\mu$ P) supervisor circuit is to ensure that the input supply voltage of a microprocessor is at proper levels during power up, power down and brownout conditions. If the input supply voltage to a microprocessor is below its required operating range, it could cause codeexecution errors, memory corruption and latch up. The supervisor will constantly monitor the input supply to the microprocessor, and in the event this supply voltage falls below a certain threshold, the RESET output will be asserted. Many of today's power products require several different voltage rails for powering various components. The microprocessor itself can have a separate core voltage and logic voltage. Other components such as DSPs, ASICs and microcontrollers can have their own unique voltage requirements. To service this demand of monitoring multi-voltage systems, Sipex has developed the SP6330 family. The SP6330 family is a series of multi-voltage supervisors that offer monitoring of up to 4 separate supplies and are equipped with specialized features. A complete listing of products and features are listed in Figure 4 at the end of this note.

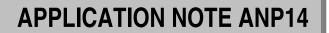

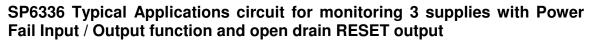

SP6332 typical applications circuit for monitoring 4 supplies with Master Reset, Watchdog input and CMOS Reset output

# Inputs to the SP6330 Family

The SP6330 family has the ability to monitor up to 4 different voltages. Two of these inputs (V1 and V2) have precision factory-set thresholds while the remaining two inputs (V3 and V4) are adjustable. V3 and V4 inputs allow the user to customize two additional supply thresholds by means of an external divider. The threshold for V3 and V4 inputs is 0.5Volts. The V1 input supplies power to the device and will have the highest threshold for a given application; its minimum operating voltage for is 1.8V. The factory set threshold range for V1 and V2 inputs are shown in Figure 1.

| V1        | V2        |

|-----------|-----------|

| Typical   | Typical   |

| Threshold | Threshold |

| 4.625     | 2.313     |

| 4.375     | 2.188     |

| 3.075     | 1.665     |

| 2.925     | 1.575     |

| 2.625     | 1.388     |

| 2.320     | 1.313     |

| 2.190     | 1.110     |

| 1.670     | 1.050     |

| 1.580     | 0.833     |

|           | 0.788     |

| Figu      | ire 1     |

Reset Output – RST or RSTB

The reset output can be either active low or active high depending on each device. The reset output can also be either open-drain or push-pull outputs. The open drain output requires an external pull-up resistor to V1 for normal operation. The output high voltage (VOH) of the reset output will be approximately equal to the V1 input voltage.

# Reset Timeout Period

The reset timeout period is a built-in time delay for the reset output. This timeout period is activated at power up or when all monitored voltages have risen above their respective thresholds. Reset timeout period for the SP6330 family is offered in four different time intervals: 50ms, 100ms, 200ms and 400ms. The actual selection of timeout period depends on the applications requirements of the system voltage settle time. The reset timeout period is used to ensure that all voltage rails and system clocks have stabilized prior to executing code to prevent errors or data corruption.

# Manual Reset Input (Active Low) – MRIB

The manual reset input allows the user to manually trigger a reset when monitored voltages are within tolerance. This is useful for resetting the microprocessor when it locks up due to software issues. A push-button type switch can be used to allow the user to trigger a reset externally. However, since a push button switch will bounce several times, a debounce element is needed. The manual reset input signal may also be a logic signal from an I/O line, watchdog timer or a power fail output.

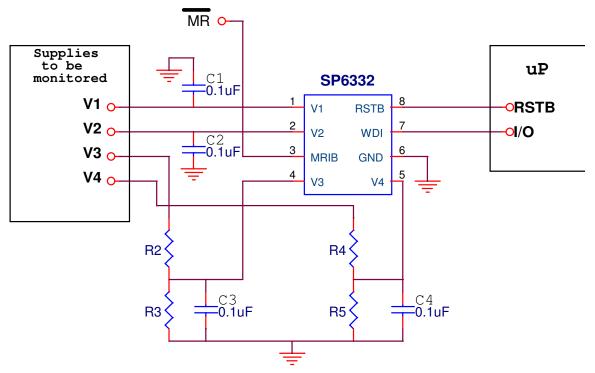

# Watchdog Input – WDI

The watchdog checks for proper software execution. If the software locks up or enters into an unwanted, loop the watchdog timer can either assert a reset output or a watchdog output. Some members of the SP6330 family offer a watchdog output while others do not. The watchdog has an internal timer that has a typical watchdog timeout period of 1.6 seconds. If the watchdog input (WDI) does not detect a transition within 1.6 seconds, a reset or watchdog output (WDO) will be generated. The watchdog input is usually connected to an I/O line for monitoring software activity. The watchdog circuit is useful for generating a reset or Non-Maskable Interrupt (NMI) signal during software lock up conditions without human intervention. Floating the WDI will disable the watchdog feature.

# Watchdog Output (Active Low) – WDOB

The Watchdog output is active low and can be either an open drain or push-pull output. If WDI remains at "HIGH" or "LOW" logic level for longer than the watchdog timeout period, the internal watchdog timer overflows and the WDOB will be asserted. Additionally, if the reset output is asserted due to an undervoltage condition, at any voltage input the WDOB would also be asserted. Floating WDI will not disable the watchdog timer in devices with dedicated WDOB output.

# Power Fail Input (PFI)

The power fail input is used to monitor the unregulated DC voltage or other upstream voltage and to alert the system that a brownout or power failure is imminent. When the PFI input is tripped, it can inform the system to start a power-down routine in order to save important data before a reset output is asserted. The power fail input has a threshold of 0.5V. By using a voltage divider the user can monitor any upstream voltage. Connect PFI to V1 or GND if not used.

Jun 27-06

# Power Fail Output (Active Low) - PFOB

The PFOB pin is an open drain, active low output. When the input voltage at PFI is <0.5V, PFOB will be asserted.

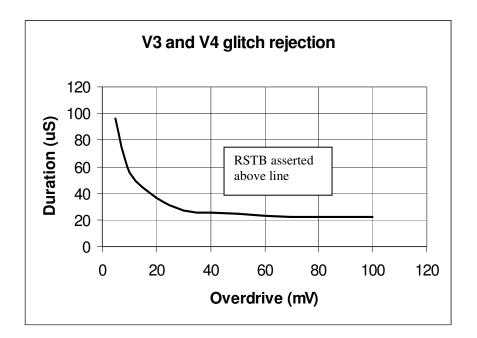

# Glitch Immunity at Voltage Inputs

The V1, V2, V3 and V4 inputs have a built-in glitch immunity feature that prevents nuisance resets during normal operation. Noise and normal voltage transients can cause these unwanted resets without some type of glitch immunity. Figure 2 shows the combination of voltage overdrive and duration that will not cause a reset for V1 and V2 inputs. Figure 3 shows the same data as applied to the V3 and V4 inputs. Adding a small bypass capacitor to voltage inputs can improve glitch rejection for very harsh environments.

Figure 2

Figure 3

# SP633X Features

- Quad, triple or dual supply monitoring

- Very low operating voltage down to 1.6V

- Low 20µA typical operating current

- Adjustable inputs monitor down to 0.5V

- Open drain or CMOS reset outputs

- 4 reset timeout periods: 50ms, 100ms, 200ms and 400ms

- Glitch immunity inputs

- Tiny 6 pin or 8 pin TSOT package

| P/N    | V1 | V2 | V3 | V4 | Reset  | Reset  | MRIB | WDI | WDOB | WDOB | PFI | PFOB | Package |

|--------|----|----|----|----|--------|--------|------|-----|------|------|-----|------|---------|

|        |    |    |    |    | Output | Active |      |     | OD   | CMOS |     |      |         |

| SP6330 | Х  | Х  | Х  | Х  | OD     | LOW    | Х    | Х   |      |      |     |      | 8-TSOT  |

| SP6332 | Х  | Х  | Х  | Х  | CMOS   | LOW    | Х    | Х   |      |      |     |      | 8-TSOT  |

| SP6334 | Х  | Х  | Х  | Х  | CMOS   | HIGH   | Х    | Х   |      |      |     |      | 8-TSOT  |

| SP6331 | Х  | Х  | Х  | Х  | OD     | LOW    |      |     |      |      |     |      | 6-TSOT  |

| SP6333 | Х  | Х  | Х  | Х  | CMOS   | LOW    |      |     |      |      |     |      | 6-TSOT  |

| SP6335 | Х  | Х  | Х  | Х  | CMOS   | HIGH   |      |     |      |      |     |      | 6-TSOT  |

| SP6336 | Х  | Х  | Х  |    | OD     | LOW    |      | Х   |      |      | Х   | х    | 8-TSOT  |

| SP6337 | Х  | Х  | Х  |    | CMOS   | LOW    |      | Х   |      |      | Х   | Х    | 8-TSOT  |

| SP6338 | Х  | Х  | Х  |    | CMOS   | HIGH   |      | Х   |      |      | Х   | х    | 8-TSOT  |

| SP6339 | Х  | Х  | Х  |    | OD     | LOW    | Х    | Х   | Х    |      |     |      | 8-TSOT  |

| SP6341 | Х  | Х  | Х  |    | CMOS   | LOW    | Х    | Х   |      | х    |     |      | 8-TSOT  |

| SP6340 | Х  | Х  |    |    | OD     | LOW    |      | Х   | Х    |      |     |      | 6-TSOT  |

| SP6342 | Х  | Х  |    |    | CMOS   | LOW    |      | Х   |      | Х    |     |      | 6-TSOT  |

# FAQ

# SP6330 - SP6342

Dual/Triple/Quad μPower Supervisory Circuit Family

### FEATURES

- Low operating voltage of 1.8V

- Low operating current of 20μA typical

- Monitors up to four supplies simultaneously

- Adjustable inputs monitor down to 0.5V

- Reset asserted down to 0.9V

- 2% accuracy over temperature range

- Power Fail function

- Open Drain (OD) or CMOS RSTB output or CMOS RST output

- 200ms Reset Timeout Period

- Watch Dog Timer Function

- Independent Open Drain Watchdog Output

- Manual Reset Input

- SOT23-6/8 packages

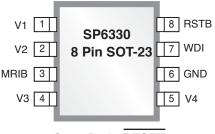

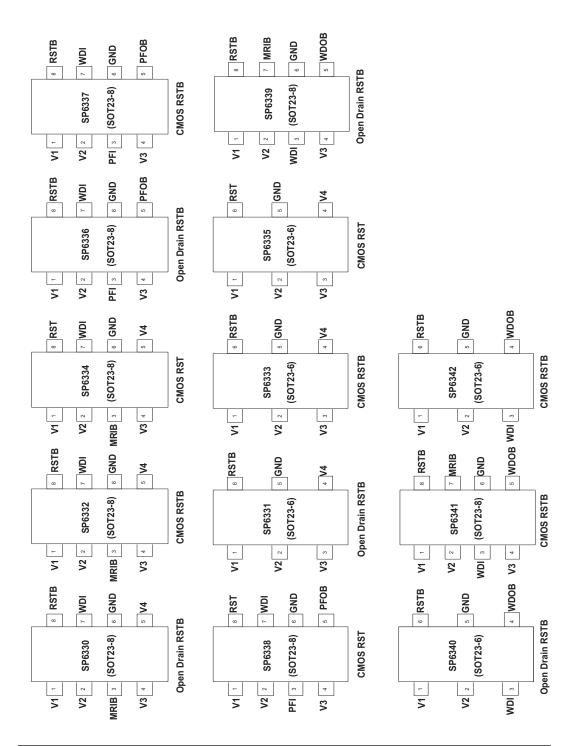

**Open Drain RESET**

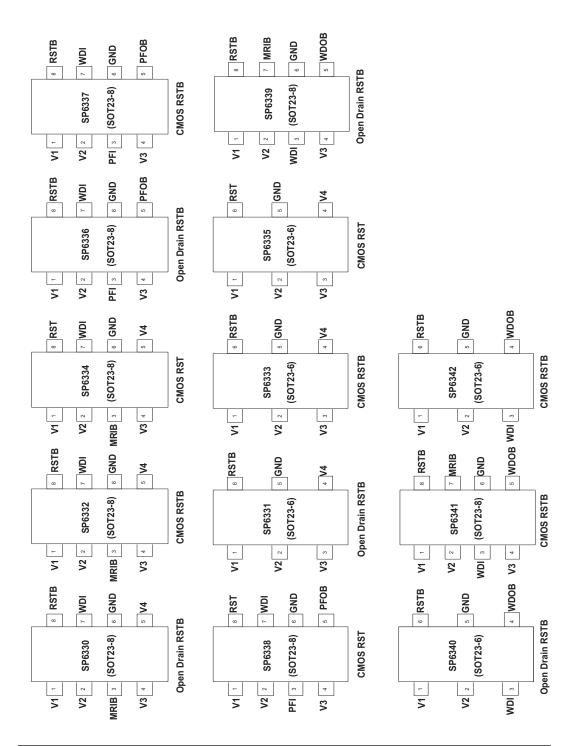

# SEE PAGE 3 FOR OTHER AVAILABLE PINOUTS

Available in Lead Free Packaging

# DESCRIPTION

SP6330-SP6342 Dual/Triple/Quad Power Supervisory Circuit Family is a family of microprocessor reset supervisory circuits with multiple reset voltages. The SP6330 family provides low voltage monitoring ability for up-to four supplies with two precision factory-set thresholds and two user defined custom thresholds. These circuits perform a single function: if any of the input supply voltages drops below its associated threshold, reset outputs are asserted. Some of the products in the family offer manual reset, power fail and watchdog functionalities. The SP63XX family includes a low-voltage precision bandgap reference, four precision comparators, an oscillator, a digital counter chain, a logic control block, trimmed resistor divider chains and additional supporting circuitry. V1 and V2 supply inputs have their resistor dividers on the chip. Their trip thresholds are factory trimmed. V3 and V4 inputs allow user to customize two additional supply thresholds to be monitored by means of external resistor dividers. Some members of the family are furnished with manual reset, power fail indication, watchdog functionalities.SP6330 thru SP6342 are housed in a 6-pin or 8-pin SOT23 package. All devices are fully specified over -40°C to +85°C temperature range.

# FEATURE MAPPING DIAGRAM

| PART<br>NUMBER | ۲۱            | V2                      | V3                      | V4           | Reset            | Manual<br>Reset<br>Input BAR | WatchDog<br>Input | WatchDog<br>Output BAR | Power<br>Fail<br>Input | Power Fail<br>Output<br>BAR | # of<br>Pins | Data-<br>sheet<br>Group |

|----------------|---------------|-------------------------|-------------------------|--------------|------------------|------------------------------|-------------------|------------------------|------------------------|-----------------------------|--------------|-------------------------|

| SP6330         | ~             | $\mathbf{F}$            | <b>1</b>                | •            | OD Active Low    | $\wedge$                     | $\checkmark$      |                        |                        |                             | ω            | ۰.                      |

| SP6331         | $\overline{}$ | $\mathbf{F}$            | $\mathbf{F}$            | $\checkmark$ | OD Active Low    |                              |                   |                        |                        |                             | 9            | 5                       |

| SP6332         | $^{\wedge}$   | $\mathbf{r}$            | $\overline{\mathbf{A}}$ |              | CMOS Active Low  | $\wedge$                     | $\wedge$          | •                      |                        | •                           | ω            | Ļ                       |

| SP6333         | ~             | ~                       | $\overline{}$           | ~            | CMOS Active Low  |                              |                   |                        |                        |                             | 9            | 5                       |

| SP6334         | $\checkmark$  | $\checkmark$            | $\overline{}$           | •            | CMOS Active High | $\wedge$                     | $\checkmark$      |                        |                        |                             | 8            | ۰                       |

| SP6335         | $\checkmark$  | $\overline{\mathbf{A}}$ | $\overline{}$           | $\checkmark$ | CMOS Active High |                              |                   |                        |                        |                             | 9            | 5                       |

| SP6336         | $\wedge$      | $\checkmark$            | $\checkmark$            | •            | OD Active Low    | •                            | $\wedge$          | •                      | $\wedge$               | $\checkmark$                | 8            | 2                       |

| SP6337         | $\checkmark$  | $\overline{\mathbf{A}}$ | $\overline{}$           |              | CMOS Active Low  |                              | $\checkmark$      |                        | $\checkmark$           | $\checkmark$                | 8            | 2                       |

| SP6338         | $\wedge$      | $\checkmark$            | $\mathbf{r}$            | •            | CMOS Active High | •                            | $\wedge$          | •                      | $\checkmark$           | $\checkmark$                | 8            | 2                       |

| SP6339         | ~             | $\mathbf{\hat{z}}$      | $\overline{}$           | •            | OD Active Low    | $\checkmark$                 | $\checkmark$      | OD Active Low          |                        |                             | ω            | 3                       |

| SP6340         | ~             | $\mathbf{\hat{z}}$      | •                       | •            | OD Active Low    |                              | $\checkmark$      | OD Active Low          |                        |                             | 9            | 4                       |

| SP6341         | $\wedge$      | $\checkmark$            | $\checkmark$            | •            | CMOS Active Low  | $\wedge$                     | $\wedge$          | CMOS Active Low        | •                      | •                           | 8            | 3                       |

| SP6342         | $\checkmark$  | <b>1</b>                | •                       | •            | CMOS Active Low  |                              | $\checkmark$      | CMOS Active Low        |                        |                             | 9            | 4                       |

SP6330-SP6342 Dual/Triple/Quad Power Supervisory Circuit Family

# FAQ

# SP6330 - SP6342

Dual/Triple/Quad μPower Supervisory Circuit Family

### FEATURES

- Low operating voltage of 1.8V

- Low operating current of 20μA typical

- Monitors up to four supplies simultaneously

- Adjustable inputs monitor down to 0.5V

- Reset asserted down to 0.9V

- 2% accuracy over temperature range

- Power Fail function

- Open Drain (OD) or CMOS RSTB output or CMOS RST output

- 200ms Reset Timeout Period

- Watch Dog Timer Function

- Independent Open Drain Watchdog Output

- Manual Reset Input

- SOT23-6/8 packages

**Open Drain RESET**

# SEE PAGE 3 FOR OTHER AVAILABLE PINOUTS

Available in Lead Free Packaging

# DESCRIPTION

SP6330-SP6342 Dual/Triple/Quad Power Supervisory Circuit Family is a family of microprocessor reset supervisory circuits with multiple reset voltages. The SP6330 family provides low voltage monitoring ability for up-to four supplies with two precision factory-set thresholds and two user defined custom thresholds. These circuits perform a single function: if any of the input supply voltages drops below its associated threshold, reset outputs are asserted. Some of the products in the family offer manual reset, power fail and watchdog functionalities. The SP63XX family includes a low-voltage precision bandgap reference, four precision comparators, an oscillator, a digital counter chain, a logic control block, trimmed resistor divider chains and additional supporting circuitry. V1 and V2 supply inputs have their resistor dividers on the chip. Their trip thresholds are factory trimmed. V3 and V4 inputs allow user to customize two additional supply thresholds to be monitored by means of external resistor dividers. Some members of the family are furnished with manual reset, power fail indication, watchdog functionalities.SP6330 thru SP6342 are housed in a 6-pin or 8-pin SOT23 package. All devices are fully specified over -40°C to +85°C temperature range.

# FEATURE MAPPING DIAGRAM

|        | 5                       | V2            | V3                      | V4                          | Reset            | Manual<br>Reset<br>Input BAR | WatchDog<br>Input | WatchDog<br>Output BAR | Power<br>Fail<br>Input | Power Fail<br>Output<br>BAR | # of<br>Pins | Data-<br>sheet<br>Group |

|--------|-------------------------|---------------|-------------------------|-----------------------------|------------------|------------------------------|-------------------|------------------------|------------------------|-----------------------------|--------------|-------------------------|

| SP6330 | ~                       | >             | ~                       |                             | OD Active Low    | ~                            | ~                 |                        |                        |                             | ω            | -                       |

| SP6331 | ~                       | >             | $\checkmark$            | $\mathbf{\hat{\mathbf{z}}}$ | OD Active Low    |                              | •                 |                        |                        |                             | 9            | ъ                       |

| SP6332 | ~                       | ~             | $\overline{\mathbf{v}}$ |                             | CMOS Active Low  | $^{\wedge}$                  | $\wedge$          |                        |                        |                             | ω            | -                       |

| SP6333 | ~                       | $\mathbf{r}$  | $\checkmark$            | $\checkmark$                | CMOS Active Low  | •                            | •                 | •                      |                        |                             | 9            | ഹ                       |

| SP6334 | $^{\prime}$             | $\checkmark$  | $\wedge$                | •                           | CMOS Active High | $\wedge$                     | $\wedge$          | •                      |                        |                             | 8            | -                       |

| SP6335 | $\overline{\mathbf{A}}$ | $\overline{}$ | $\checkmark$            | $\checkmark$                | CMOS Active High | •                            | •                 |                        |                        |                             | 9            | 2                       |

| SP6336 |                         | $\mathbf{r}$  | $\checkmark$            |                             | OD Active Low    | •                            | $\wedge$          | •                      | $\checkmark$           | $\checkmark$                | 8            | 2                       |

| SP6337 | $\overline{}$           | $\overline{}$ | $\overline{}$           |                             | CMOS Active Low  |                              | $\wedge$          |                        | $\checkmark$           | $\checkmark$                | 8            | 2                       |

| SP6338 | $\wedge$                | $\checkmark$  | $\checkmark$            | •                           | CMOS Active High | •                            | $\wedge$          | •                      | $\checkmark$           | $\checkmark$                | 8            | 2                       |

| SP6339 | ~                       | $\mathbf{r}$  | $\checkmark$            |                             | OD Active Low    | $\wedge$                     | $\wedge$          | OD Active Low          | •                      |                             | 8            | ю                       |

| SP6340 | $^{\wedge}$             | $\checkmark$  |                         | •                           | OD Active Low    | •                            | $\wedge$          | OD Active Low          | •                      | •                           | 9            | 4                       |

| SP6341 | $^{\wedge}$             | $\checkmark$  | $\checkmark$            | •                           | CMOS Active Low  | $\wedge$                     | $\wedge$          | CMOS Active Low        | •                      | •                           | 8            | 3                       |

| SP6342 | ~                       | $\mathbf{r}$  |                         |                             | CMOS Active Low  |                              | $\checkmark$      | CMOS Active Low        |                        |                             | 9            | 4                       |

SP6330-SP6342 Dual/Triple/Quad Power Supervisory Circuit Family

# Reliability and Qualification Report

# SP6330

Prepared by: G. West Manager, Quality Assurance Date: April 7, 2006 Reviewed by: Fred Claussen VP Quality & Reliability Date: April 7, 2006

# **Table Of Contents**

| Title Page                | I  |

|---------------------------|----|

| Table of Contents         |    |

| Device Description        | II |

| Block Diagram             |    |

| Manufacturing Information |    |

| Package Information       | II |

| Reliability Test Summary  |    |

| Life Test Data            | IV |

| FIT Data Calculations     | V  |

| MTBF Data Calculations    | V  |

# **Device Description:**

SP6330-SP6332- SP6334 Quad Power Supervisory Circuit Family is a family of microprocessor reset supervisory circuits with multiple reset voltages. The family provides low voltage monitoring ability for up-to four supplies with two precision factory-set thresholds and two user defined custom thresholds. These circuits perform a single function: if any of the input supply voltages drops below its associated threshold, reset outputs are asserted. The SP6330, SP6332, and SP6334 are packaged in an 8-pin TSOT package. All devices are fully specified over -40<sub>o</sub>C to +85<sub>o</sub>C temperature range.

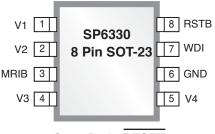

# SP6330 Pin Out

# Manufacturing Information:

| Products:              | SP6330                               |

|------------------------|--------------------------------------|

| Description:           | Quad Power Supervisory Circuit       |

| Mask Set(s):           | MS1512AZ                             |

| Process:               | CMOS                                 |

| Process Name:          | PBC4                                 |

| Wafer Manufacturer:    | Polar Semiconductor, Inc.            |

| Assembly Location:     | Carsem – Malaysia                    |

| Qualification Lot #'s: | 3522A001A.11, 3638A001.8, 3638A001.6 |

# **Package Information:**

| Package Type: | 8 pin TSOT  |

|---------------|-------------|

| Die Size:     | 45 x 67 mil |

# **Reliability Qualification Test Summary:**

| Stress Level | Device | Burn-In Temp | Sample Size | No. Fail |

|--------------|--------|--------------|-------------|----------|

| 168Hrs       | SP6330 | 125 °C       | 240         | 0        |

| 500Hrs       | SP6330 | 125 °C       | 240         | 0        |

| 1000Hrs      | SP6330 | 125 °C       | 240         | 0        |

# Life Test

Life testing is conducted to determine if there are any fundamental reliability related failure mechanism(s) present in the device.

These failure mechanisms can be divided roughly into four groups:

- 1. Process or die related failures, such as oxide-related defects, metalization-related defects and diffusion-related defects.

- 2. Assembly-related defects such as chip mount wire bond or package-related failures.

- 3. Design related defects.

- 4. Miscellaneous, undetermined or application-induced failures.

# Life Test Results

As part of the Sipex design qualification program, the Engineering group had subjected 80 parts from each of 3 lots of SP6330 for a 1000 hour reliability life test at 125° C.

# 168 hour Life test

240 parts of SP6330 parts were subjected to the life test profile and completed 168hr the test without any part failures.

# 500 hour Life test

The 240 parts of SP6330 we reintroduced to the second phase of the test, where the parts again showed successfully completing the 500-hour life test without any failures.

# 1000 hour Life test

The 240 parts of the SP6330 were reintroduced to the final phase of the test, where the parts again successfully completed 1000-hour life test without any shift on the process parameters.

# FIT Rate Calculations

The FIT (failures in time) rate is the predicted number of failures per billion devicehours. This predicted value is based upon the:

- 1. Life Test conditions (time and temperature, device quantity and number of failures) are summarized under HTOL test table.

- 2. Activation Energy  $(E_a)$  of the potential failure modes.

The weighted Activation Energy,  $E_a$ , of observed failure mechanisms of Sipex products has been determined to be 0.8 eV.

Based on the above criteria, the FIT rates at 25°, 55° and 70°C operation at both 60% and 90% confidence levels for the **SP6330** product lines have been calculated and are listed below.

|                  | 1104400 |       |       |

|------------------|---------|-------|-------|

| Confidence Level | +25°C   | +55°C | +70°C |

| 60%              | 1.6     | 26.6  | 90.8  |

| 90%              | 4.1     | 68.4  | 233.1 |

# FIT Failure Rates SP6330 Product

1 FIT = 1 Failure per Billion Device-Hours

### **MTBF Calculation for SP6330 Product**

| Confidence Level | +25°C    | +55°C    | +70°C    |

|------------------|----------|----------|----------|

| 60%              | 6.30E+08 | 3.75E+07 | 1.10E+07 |

| 90%              | 2.46E+08 | 1.46E+07 | 4.29E+06 |

# ESD Testing

**HBM ESD Testing** - 5 units from each of three lots were subjected to 4000 V Human Body Model (HBM) ESD stress. Each pin was subjected to three positive and three negative pulses with respect to ground. All units passed testing after ESD stress.

**Latch-up Testing -** 5 units from each of three lots were subjected to latch-up testing at +/-100mA. All units passed.