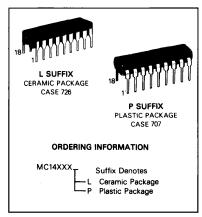

# MOTOROLA SEMICONDUCTOR TECHNICAL DATA

#### BASIC TIME SLOT ASSIGNER CIRCUIT (TSAC)

The MC14417 is a per channel Time Slot Assigner Circuit (TSAC) that produces 8-bit receive and transmit time slots for a PCM Codec. The pins D0 to D5 are the time slot data inputs which can be either hardwired on the printed circuit board for fixed time slot assignment, or externally programmed through the use of these pins and the latch enable function. The receive and transmit frame syncs and enables are independent. In addition, a T/R (TXE/RXE swap) input is provided which allows a simplified switching mechanism for a small systems architecture (i.e., key systems).

The MC14417 can operate from a single 5-volt supply for TTL levels or up to 16-volts for CMOS levels. The MC14417 is fabricated using the CMOS technology for reliable low-power performance.

- TTL and CMOS Level Compatibility

- 5 to 16 Volt Operation

- Low Operating Power Consumption

- For Use With Up to 2.56 MHz Clocks

- Independent Transmit and Receive Frame Syncs and Enables

- Up to 64 Time Slots Per Frame

- Compatible with MC14400/01/02/03/05 PCM Mono-Circuits

- Allows Swapping of Transmit Enable (TXE) and Receive Enable (RXE) Signals

- CMOS Metal Gate for High Reliability

#

# MC14417

### **CMOS LSI**

(LOW-POWER COMPLEMENTARY MOS)

TSAC TIME SLOT ASSIGNER CIRCUIT

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high-impedance circuit. For proper operation it is recommended that V<sub>in</sub> and V<sub>out</sub> be constrained to the range V<sub>SS</sub>  $\leq$  (V<sub>in</sub> or V<sub>out</sub>)  $\leq$  V<sub>DD</sub>.

Unused inputs must always be tied to an appropriate logic voltage level (e.g., either VSS or VDD).

#### MAXIMUM RATINGS (Voltages referenced to VSS)

| Rating                                        | Symbol                               | Value                                                        | Unit |

|-----------------------------------------------|--------------------------------------|--------------------------------------------------------------|------|

| DC Supply Voltage                             | V <sub>DD</sub>                      | -0.5 to 18                                                   | V    |

| Level Shift Voltage                           | Vcc                                  | -0.5 to V <sub>DD</sub>                                      | ٧    |

| Input Voltage Inputs Referenced to VDD to VCC | V <sub>in1</sub><br>V <sub>in2</sub> | -0.5 to V <sub>DD</sub> +0.5<br>-0.5 to V <sub>DD</sub> +0.5 | ٧    |

| DC Current Drain per Pin                      | · I                                  | 10                                                           | mA   |

| Operating Temperature Range                   | TA                                   | -40 to +85                                                   | °C   |

| Storage Temperature Range                     | T <sub>sta</sub>                     | -65 to +165                                                  | °C   |

## ELECTRICAL CHARACTERISTICS (TA = 25°C)

| Characteristic                                                                  | Symbol             | VDD           | Min          | Тур        | Max               | Unit |

|---------------------------------------------------------------------------------|--------------------|---------------|--------------|------------|-------------------|------|

| DC Supply Voltage, VSS = 0 V                                                    | VDD                | _             | 4.5          | 12         | 16                | ٧    |

| DC Supply Voltage, VSS = 0 V                                                    | Vcc                | -             | 4.5          | 5          | ۷DD               | V    |

| Output Current TXE, RXE, ST (V <sub>OL</sub> = 0.4 V) (V <sub>OL</sub> = 1.0 V) | lor                | 5<br>12       | 0.51<br>2.0  | -<br>4.0   | -                 | mA   |

| $(V_{OH} = 4.6 \text{ V})$<br>$(V_{OH} = 11.0 \text{ V})$                       | ЮН                 | 5<br>12       | -0.2<br>-2.0 | -<br>-4.0  | 1 1               | mA   |

| Input Voltage (CMOS) FST, FSR, DC1, DC2, NDC "C                                 | " V <sub>IL</sub>  | 5<br>12       | _            | -          | 1.0<br>2.4        | ٧    |

| "1                                                                              | " V <sub>IH</sub>  | 5<br>12       | 4.0<br>9.6   | -          | -                 | ٧    |

| Input Voltage (TTL) D0-D5, LE, $T/\overline{R}$ , $V_{CC} = 5 \text{ V}$ "C     | ., VIL             | 5<br>12<br>16 | -            | -          | 0.8<br>0.8<br>0.7 | ٧    |

|                                                                                 | 1″ V <sub>IH</sub> | 5<br>12       | 2.0<br>2.0   | -          | -                 | ٧    |

| Total Supply Current (Outputs Unloaded) DC1 at 2.048 MHz                        | IŢ                 | 5<br>12       | -            | 1.5<br>2.5 | _                 | mA   |

## **SWITCHING CHARACTERISTICS** ( $C_L = 50 \text{ pF}$ , $T_A = 25 \,^{\circ}\text{C}$ , Unless Otherwise Noted)

| Characteristic                                                           | Symbol            | ν <sub>DD</sub> | Min           | Тур        | Max           | Unit |

|--------------------------------------------------------------------------|-------------------|-----------------|---------------|------------|---------------|------|

| Output Rise Time, TXE, RXE, ST                                           | t <sub>r</sub>    | 5<br>12         | 1 1           | 100<br>50  | 200<br>100    | ns   |

| Output Fall Time, TXE, RXE, ST                                           | tf                | 5<br>12         | 1 1           | 100<br>50  | 200<br>100    | ns   |

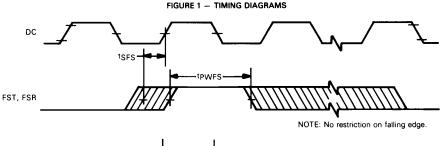

| Frame Sync Setup Time (See Figure 1)                                     | tSFS              | 5<br>12         | - 150<br>- 75 | 1 1        | + 150<br>+ 75 | ns   |

| Frame Sync Pulse Width                                                   | tpWFS             | 5<br>12         | 200<br>100    | 1 1        | 1 1           | ns   |

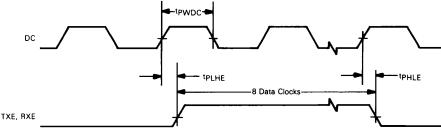

| Propagation Delay (Note 1) DC1 to TXE, DC2 to RXE, $C_L = 20 \text{ pF}$ | tPHLE,<br>tPLHE   | 5<br>12         | 1 1           | 130<br>80  | 180<br>125    | ns   |

| Data Clock Frequency                                                     | fDC               | 5<br>12         | -             | _          | 2.048<br>2.6  | MHz  |

| Data Clock Pulse Width at fDC (Max)                                      | tPWDC             | 5<br>12         | 200<br>140    | 244<br>192 | 293<br>260    | ns   |

| LE Pulse Width                                                           | <sup>t</sup> PWLE | 5<br>12         | 1             | - 1        |               | μS   |

| NDC to ST Propagation Delay                                              |                   | 5<br>12         | -             |            | 120<br>80     | ns   |

| FST to ST Propagation Delay                                              |                   | 5<br>12         | -             | _          | 200<br>130    | ns   |

NOTE 1: For time slot 0, tPHLE and tPLHE are measured from the leading edge of DC or FST (FSR), whichever occurs last.

#### PIN DESCRIPTIONS

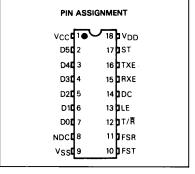

**V<sub>CC</sub>** (Positive Supply) — The V<sub>CC</sub> power supply controls the inputs LE, D0-D5 and  $T/\overline{R}$ . It can be supplied by any voltage from 4.5 to V<sub>DD</sub>. In typical usage, V<sub>CC</sub> is 5 volts for TTL or microprocessor compatibility of the control inputs to the TSAC while V<sub>DD</sub> and V<sub>SS</sub> are connected to the Codec supplies.

**D5-D0 (Parallel Time Slot Data Inputs)** — The six inputs to the input-storage latch are the time-slot data. D0 is the least-significant bit while D5 is the most-significant. The binary word at this input represents the number of 8 bit time slots from FST and FSR where TXE and RXE will occur, respectively. These can be 5-volt input compatible with TTL and are internally level shifted to the  $V_{DD}$  supply.

LE (Latch Enable Input with Internal Pull-Up) — This input allows the data D0 through D5 and  $T\bar{R}$  bits to be latched in the input-storage latch. If LE is held high, then the inputs to the latch are combinational and directly applied to the compare circuits. When LE is pulled low, the input values applied at D0 through D5 and  $T\bar{R}$  are latched and held in the storage latch.

$T/\overline{R}$  (TXE/RXE Swap Input with Internal Pull-Up) — This input allows the TXE and RXE inputs to be swapped. When T/R is a one, the TXE output is derived from FST and RXE from FSR. If  $T/\overline{R}$  is a zero, the derivation is reversed. If FST and FSR are eight data clocks apart, then two TSAC channels programmed to the same D0 through D5 and different  $T/\overline{R}$  bits will create a completed conversation. This feature is intended for use in simplifying small-key systems.

DC (Data Clock Input) — The data clock input establishes the bit rate for the TSAC. This is typically 1.544 or 2.048 MHz but can be any frequency up to 2.56 MHz. The data clock is divide-by-8 for both transmit- and receive-time slots. The data clock input is a CMOS compatible input between Vpp and Vss.

FST (Frame Sync Transmit Input) — This input identifies the beginning of the zero-transmit time slot by resetting the divide-by-8 and divide-by-64 counters. FST is a CMOS compatible input between Vpp and Vss. The TXE output will begin and end on one 8-bit word boundary which is synchronized with the FST input. The FST signal should be aligned with the leading edge of data clock and is typically 8 kHz

FSR (Frame Sync Receive Input) — The FSR input provides the same functions for the RXE output as FST did for TXE. The FSR and FST inputs can be any number of data clocks different, or can be the same.

TXE, RXE (Transmit-Enable and Receive-Enable Outputs) — These outputs are used to control the transmitting and receiving of data words to and from Codecs. Each output swings from VDD to VSS and is eight data clocks long. TXE and RXE go high at the beginning of the programmed time slot and low at the end. TXE is derived from FST and RXE is derived from FSR, provided the T/R bit is high.

ST (Strobe Output) — The strobe output is provided to allow simplified input data storage or off-hook multiplexing control. ST is the logical AND of an enable signal (NDC) and the TXE time slot period. Thus, ST can only be high during a programmed TXE time slot. Since no other TSAC in a bank can have the same TXE programming, the ST output on any TSAC can be used to uniquely identify that TSAC by a pulse input on NDC. In many applications ST is used to control the LE input.

NDC (New Data Clock Input with Internal Pull-Up) — This input can be used in conjunction with ST to strobe data into a TSAC bank. NDC can be used to enable the strobe output.

$\mbox{VDD, VSS}$  — The TSAC will operate from any single supply from 4.5 to 16 volts. The TSAC can be used in a 5-volt-only system by making both VCC and VDD 5 volts.

- Rcv Data - Rcv Sync - Data Clock MC14401 MC14417 RSI  $V_{DD}$  $v_{\text{CC}}$  $V_{DD}$  $v_{AG}$ Analog Gnd -RDD FSR D0 Analog Out 🔫 Rxo RCE RXE Rxo Time RDC DC D2 Slot TxI TDC NDC D3 Analog In > 10 k Data 10 k -Tx TDD ST D4 TXE D5 Mu/A TDE PDI FST T/Ř MSI ٧ss LE Vss  $V_{LS}$ Latch - Tx Data - Tx Sync - Gnd --5V

FIGURE 2 - MOTOROLA MONO-CIRCUIT/TSAC COMBINATIONS

The MC14417 TSAC offers simple flexible time slot assignment for the PCM mono-circuit. Assignments are wired or latched into the data port. The MC14401 offers supply flexibility of  $\pm 5,\,\pm 6,\,+12,$  or +10 V with 18 pin packages and TTL compatibility.