# MOS INTEGRATED CIRCUIT $\mu$ PD482234, 482235

# 2M-Bit Dual Port Graphics Buffer 256K-WORD BY 8-BIT

#### Description

The  $\mu$ PD482234 and  $\mu$ PD482235 have a random access port and a serial access port. The random access port has a 2M-bit (262, 144 words  $\times$  8 bits) memory cell array structure. The serial access port can perform clock operations of up to 55 MHz from the 4K-bit data register (512 words  $\times$  8 bits).

To simplify the graphics system design, the split data transfer function and binary boundary jump function have been adopted so that the number of split data registers can be programmed with the software during serial read/write operations.

The  $\mu$ PD482235 is provided with the hyper page mode, an improved version of the fast page mode of the  $\mu$ PD482234. The random access port can input and output data by  $\overline{\text{CAS}}$  clock operations of up to 33 MHz.

#### **Features**

Dual port structure (Random access port, Serial access port)

• Random access port (262, 144-word × 8-bit structure)

#### μ**PD482234**

|                           | μPD482234-60 | μPD482234-70 |

|---------------------------|--------------|--------------|

| RAS access time           | 60 ns (MAX.) | 70 ns (MAX.) |

| Fast page mode cycle time | 40 ns (MIN.) | 45 ns (MIN.) |

#### μPD482235

|                            | μPD482235-60 | μPD482235-70 |

|----------------------------|--------------|--------------|

| RAS access time            | 60 ns (MAX.) | 70 ns (MAX.) |

| Hyper page mode cycle time | 30 ns (MIN.) | 35 ns (MIN.) |

- · Flash write function Note

- · Block write function (4 columns)Note

- · Mask write (Write-per-bit function)

- · 512 refresh cycles /8 ms

- · CAS before RAS refresh, RAS only refresh, Hidden refresh

Note Write-per-bit can be specified.

The information in this document is subject to change without notice.

- Serial access port (512 words × 8 bits organization)

- · Serial read/write cycle time

| μPD482234-60, 482235-60 | μPD482234-70, 482235-70 |

|-------------------------|-------------------------|

| 18 ns (MIN.)            | 22 ns (MIN.)            |

- · Serial data read/write

- · Split buffer data transfer

- · Binary boundary jump function

#### Version B, A, F, and E

There are four versions, B, A, F, and E, to both the  $\mu$ PD482234 and  $\mu$ PD482235. This data sheet can be applied to the versions B and A.

#### · How to identify each version

Each version is identified with its lot number (Refer to 7. Example of Stamping).

#### **Ordering Information**

| Part Number    | Number RAS Access Time ns (MAX.) Package |                             | Page Mode       |

|----------------|------------------------------------------|-----------------------------|-----------------|

| μPD482234LE-60 | 60                                       | 40-pin plastic SOJ (400mil) | Fast page mode  |

| μPD482234LE-70 | 70                                       |                             |                 |

| μPD482234G5-60 | 60                                       | 44-pin plastic TSOP (II)    |                 |

| μPD482234G5-70 | 70                                       | (400mil)                    |                 |

| μPD482235LE-60 | 60                                       | 40-pin plastic SOJ (400mil) | Hyper page mode |

| μPD482235LE-70 | 70                                       |                             |                 |

| μPD482235G5-60 | 60                                       | 44-pin plastic TSOP (II)    |                 |

| μPD482235G5-70 | 70                                       | (400mil)                    |                 |

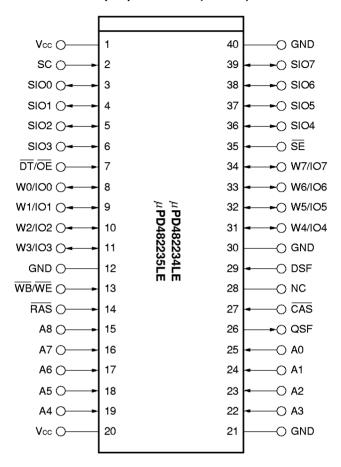

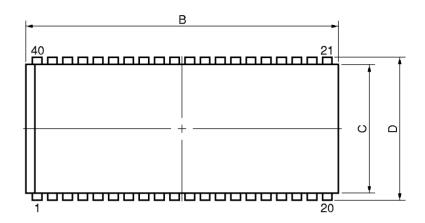

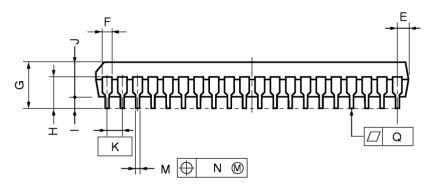

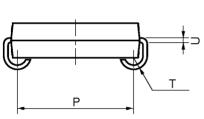

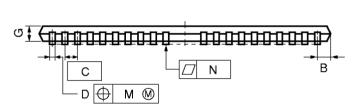

#### Pin Configurations (Marking Side)

#### 40-pin plastic SOJ (400 mil)

A0 to A8 : Address inputs

W0 to W7/IO0 to IO7 : Mask data selects/Data inputs and outputs

SIO0 to SIO7 : Serial data inputs and outputs

RAS

: Row address strobe

CAS

: Column address strobe

DT/OE

: Data transfer/Output enable

WB/WE

: Write-per-bit/Write enable

SE

: Serial data input/Output enable

SC : Serial clock

QSF : Special function output

DSF : Special function enable

Vcc : Power supply voltage

GND : Ground NC No connection

Note Some signals can be applied because this pin is not connected to the inside of the chip.

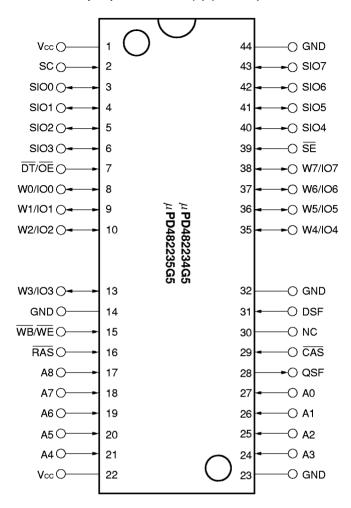

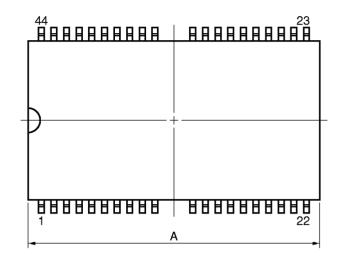

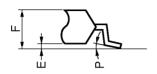

#### 44-pin plastic TSOP (II) (400 mil)

A0 to A8 : Address inputs

W0 to W7/IO0 to IO7 : Mask data selects/Data inputs and outputs

SIO0 to SIO7 : Serial data inputs and outputs

RAS

: Row address strobe

CAS

: Column address strobe

DT/OE

: Data transfer/Output enable

WB, WE

: Write-per-bit/Write enable

SE

: Serial data input/Output enable

SC : Serial clock

QSF : Special function output

DSF : Special function enable

Vcc : Power supply voltage

GND : Ground

NCNote : No connection

Note Some signals can be applied because this pin is not connected to the inside of the chip.

[MEMO]

#### **Block Diagram**

# Contents (1/2)

| 1. | Pin  | Functions                                                      | 9  |

|----|------|----------------------------------------------------------------|----|

| 2. | Ran  | dom Access Port Operations                                     | 12 |

|    | 2.1  | Random Read Cycle                                              | 13 |

|    |      | 2.1.1 Extended Read Data Output (µPD482235)                    | 13 |

|    | 2.2  | Random Write Cycle (Early Write, Late Write)                   | 14 |

|    |      | 2.2.1 Early Write Cycle                                        |    |

|    |      | 2.2.2 Late Write Cycle                                         | 14 |

|    | 2.3  | Read Modify Write Cycle                                        | 14 |

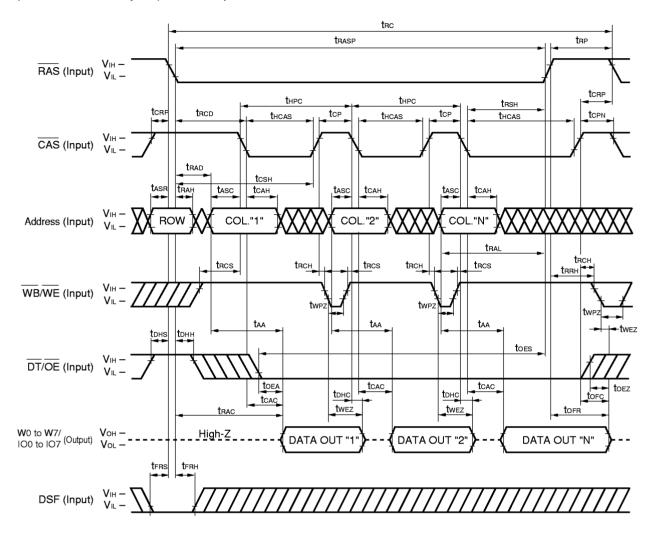

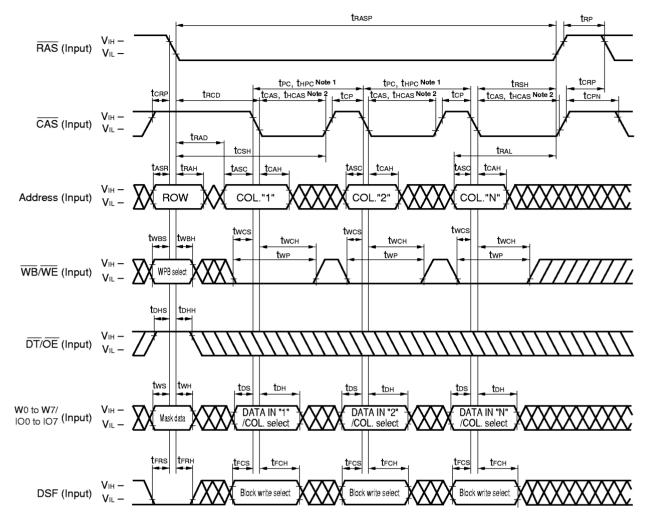

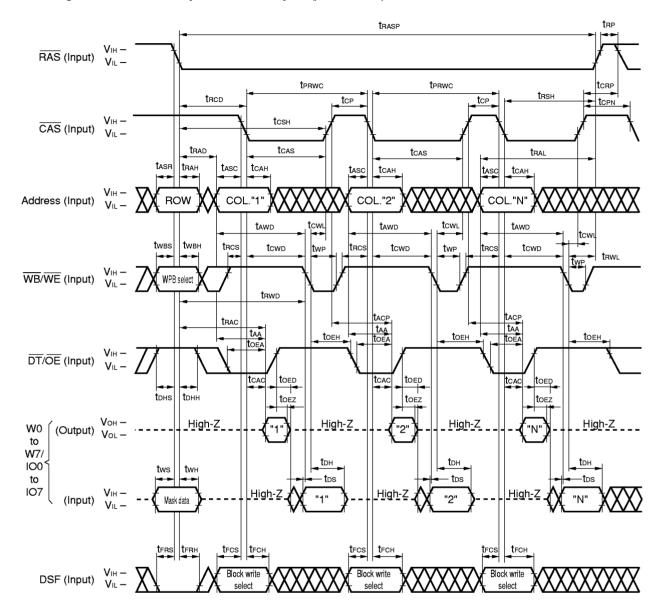

|    | 2.4  | Fast Page Mode Cycle (µPD482234)                               | 15 |

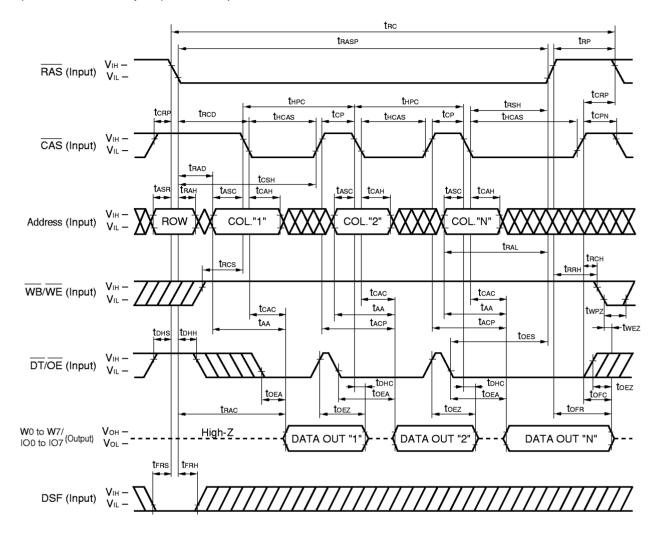

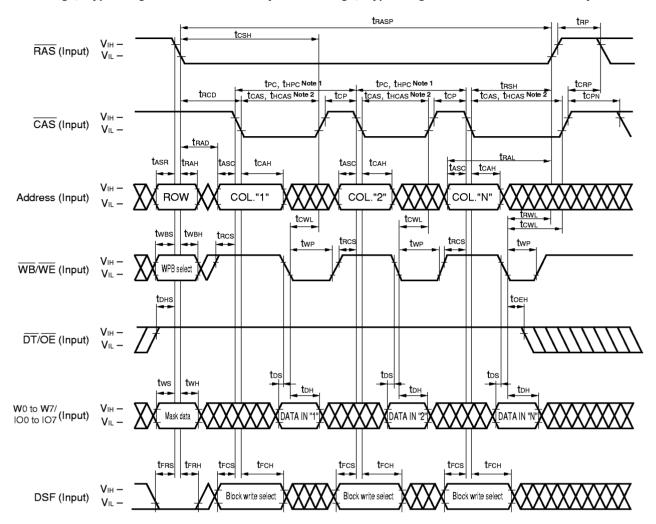

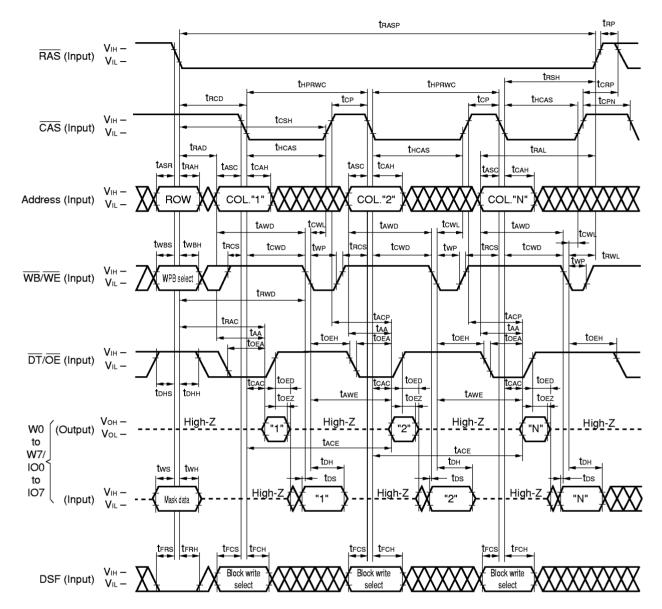

|    | 2.5  | Hyper Page Mode Cycle (μPD482235)                              | 15 |

|    |      | 2.5.1 Setting the Output to the High Impedance State           | 15 |

|    | 2.6  | Flash Write Cycle                                              | 17 |

|    |      | 2.6.1 Execution of Flash Write Cycle                           | 17 |

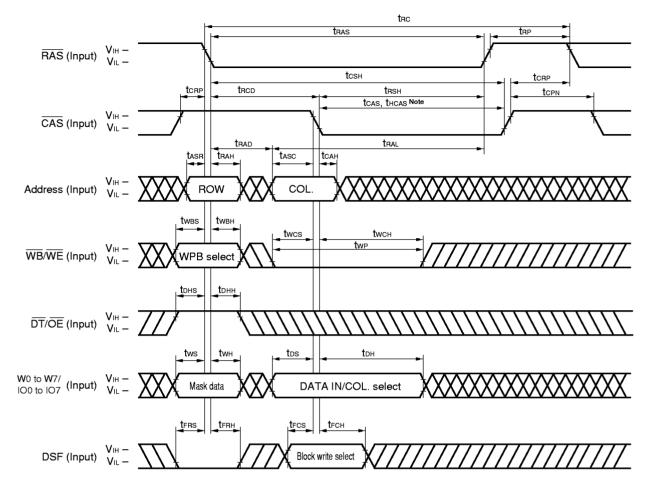

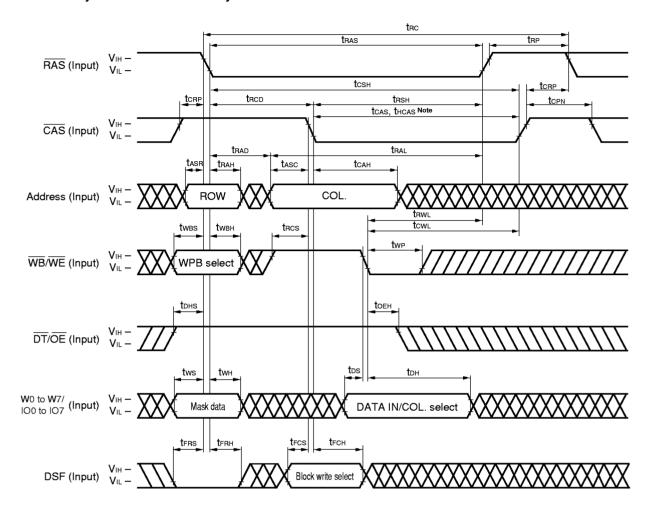

|    | 2.7  | Block Write Cycle                                              | 18 |

|    |      | 2.7.1 Free Column Selection                                    | 18 |

|    |      | 2.7.2 Column Select Data                                       | 18 |

|    |      | 2.7.3 Execution of Block Write Cycle                           | 18 |

|    | 2.8  | Register Set Cycle (Color Register, Write Mask Register)       | 19 |

|    | 2.9  | Mask Write Cycle                                               | 20 |

|    |      | 2.9.1 Write-Per-Bit Function                                   | 20 |

|    |      | 2.9.2 Selecting Mask Data                                      | 20 |

|    |      | 2.9.3 Execution of Mask Write Cycle                            | 20 |

|    | 2.10 | Refresh Cycle                                                  | 21 |

|    |      | 2.10.1 Refresh Cycle Using External Address Input              |    |

|    |      | (RAS Only Refresh and Read/Write Refresh)                      | 21 |

|    |      | 2.10.2 CAS Before RAS Refresh Cycle (Including Hidden Refresh) | 21 |

| 3. | Ser  | al Access Port Operations                                      | 22 |

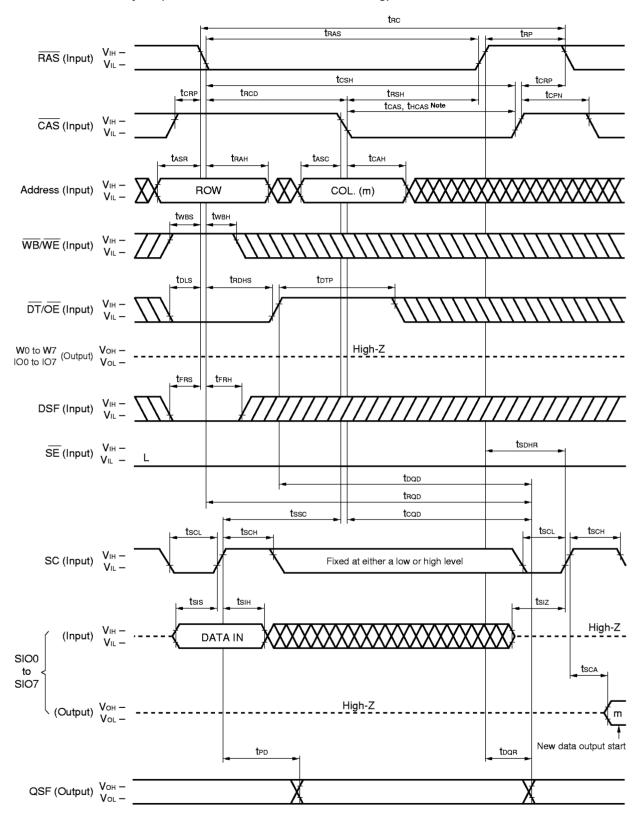

|    | 3.1  | Single Data Transfer Method                                    | 23 |

|    |      | 3.1.1 Single Read Data Transfer Cycle                          | 23 |

|    |      | 3.1.2 Single Mask Write Data Transfer Cycle                    | 24 |

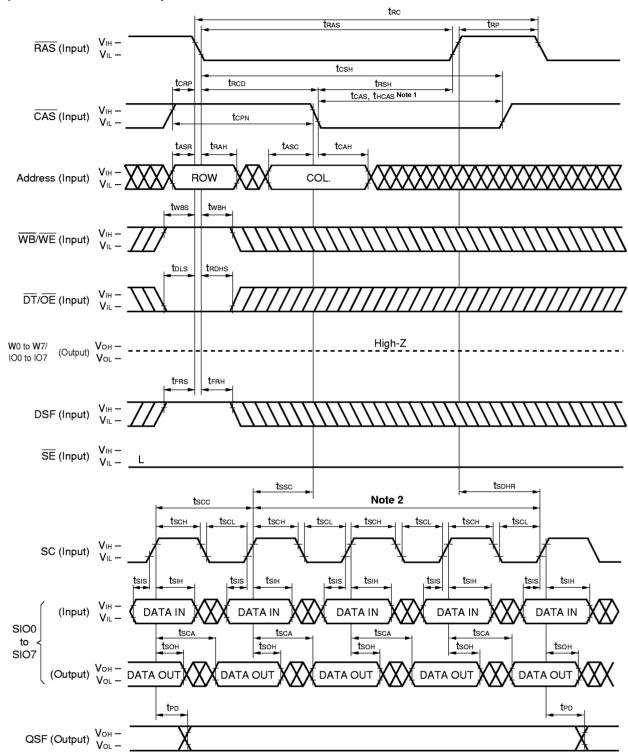

|    | 3.2  | Split Data Transfer Method                                     | 25 |

|    |      | 3.2.1 Split Read Data Transfer Cycle                           | 25 |

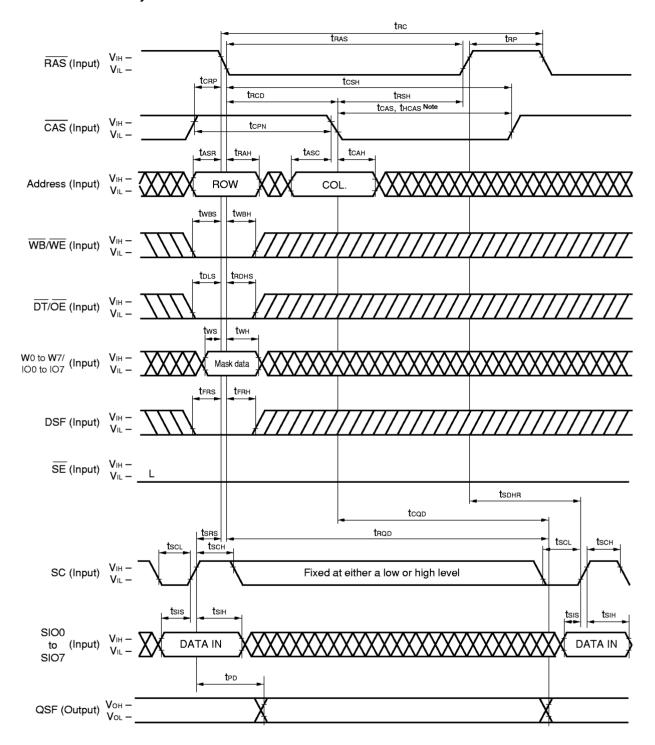

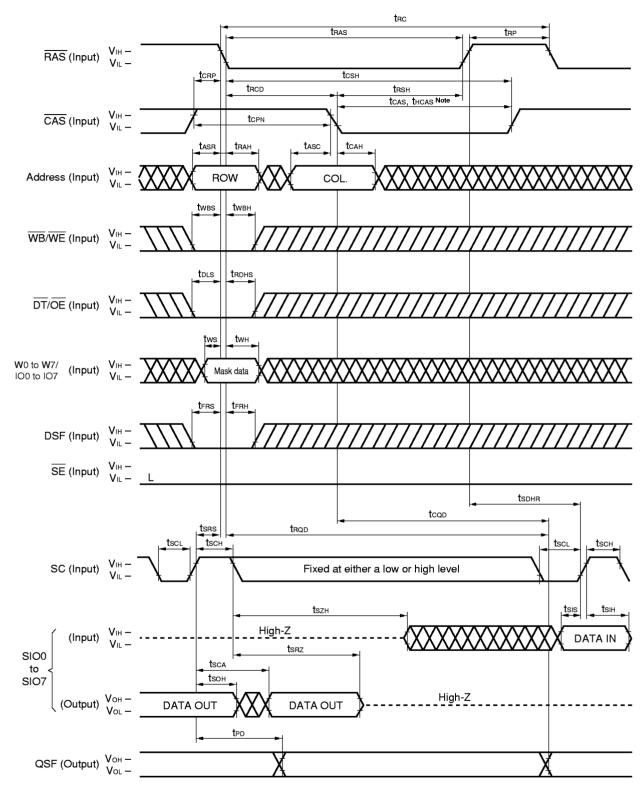

|    |      | 3.2.2 Split Mask Write Data Transfer Cycle                     | 26 |

|    | 3.3  | Serial Read/Write                                              | 27 |

|    |      | 3.3.1 Serial Read Cycle                                        | 28 |

|    |      | 3.3.2 Serial Write Cycle                                       | 28 |

|    |      | 3.3.3 QSF Pin Output                                           | 28 |

|    | 3.4  | TAP (Top Access Point) Register                                | 29 |

|    |      | 3.4.1 Setting of TAP Register                                  | 29 |

|    | 3.5  | STOP Register                                                  | 29 |

|    |      | 3.5.1 Setting of STOP Register                                 | 29 |

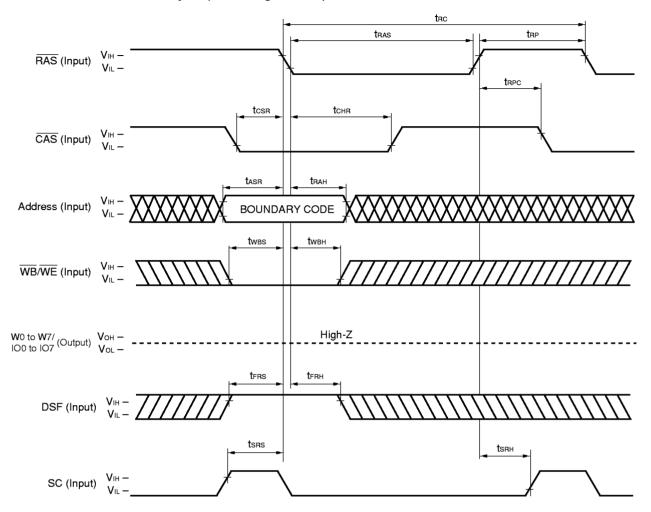

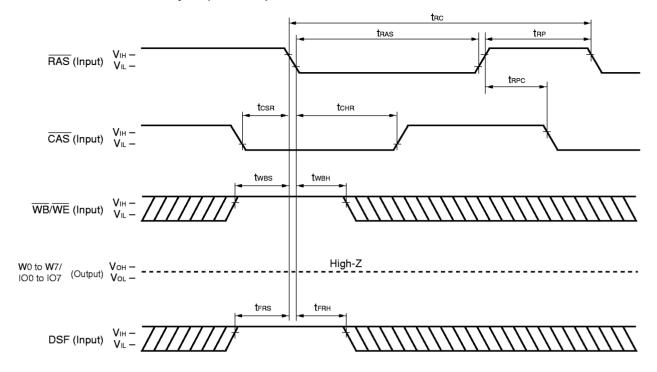

|    | 3.6  | Binary Boundary Jump Function                                  | 30 |

|    |      | 3.6.1 Usage of Binary Boundary Jump Function                   | 30 |

## Contents (2/2)

|    | 3.7 | Specia  | al Operations                 | 31 |

|----|-----|---------|-------------------------------|----|

|    |     | 3.7.1   | Serial Address Set Operations | 31 |

|    |     | 3.7.2   | Lap Around Operations         | 31 |

|    |     | 3.7.3   | Cycle After Power On          | 31 |

| 4. | Ele | ctrical | Characteristics               | 32 |

| 5. | Pac | kage E  | Orawings                      | 80 |

|    |     | Ū       |                               |    |

| 6. | Rec | omme    | nded Soldering Conditions     | 83 |

| 7. | Exa | mple c  | of Stamping                   | 83 |

#### 1. Pin Functions

This product is equipped with the  $\overline{RAS}$ ,  $\overline{CAS}$ ,  $\overline{WB}/\overline{WE}$ ,  $\overline{DT}/\overline{OE}$ , A0 to A8, DSF, SC,  $\overline{SE}$  inputs, QSF output, and W0 to W7/IO0 to IO7, SIO0 to SIO7 input/output pins.

(1/3)

|                                   | Input/ | (113)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|-----------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin Name                          | Output | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| RAS<br>(Row address strobe)       | Input  | This signal latches the row addresses (A0 to A8), selects the corresponding word line, and activates the sense amplifier. It also refreshes the memory cell array of the one line (4,096 bits) selected from the row addresses (A0 to A8).                                                                                                                                                                                                                                                                                                                                |  |  |

|                                   |        | It also serves as the signal which selects the following operations.  • Write-per-bit  • CAS before RAS refresh  • Split data transfer                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| CAS<br>(Column address<br>strobe) |        | This signal latches the column addresses (A0 to A8), selects the digit line connecting the sense amplifier, and activates the output circuit which outputs data to the random access port.                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|                                   |        | It also serves as the signal which selects the following operations.  • Read/write  • Block write  • Color register set  • Mask register set                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| A0 to A8<br>(Address inputs)      |        | These are the address input pins, TAP register input pins, and S register input pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|                                   |        | Address input  This is a 9-bit address bus. It inputs a total of 18 bits of the address signal, starting from the upper 9 bits (row address) and then followed by the lower 9 bits (column bits) (address multiplex method). Using these, one word memory cells (8 bits) are selected from the 262,144 words × 8 bits memory cell array.  During use, specify the row address, activate the RAS signal, latch the row address, switch to the column address, and activate the CAS signal. After activating the RAS and CAS signals, each address signal is taken into the |  |  |

|                                   |        | device. For this reason, the address input setup time (tash, tasc) and hold time (trah, tcah) are specified for activating the RAS and CAS signals.                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|                                   |        | TAP Register Input In the data transfer cycle, this TAP register input pin functions as the address input pin which selects the memory cell for transferring (9 bits are latched at the falling edge of RAS) and the TAP register data input pin which specifies the start addresses of the serial read/write operation after data transfer (9 bits are latched at the falling edge of the CAS).                                                                                                                                                                          |  |  |

|                                   |        | STOP Register Input This pin functions as the STOP register input pin when the STOP register is set (STOP register data (9 bits) are latched at the falling edge of the RAS.)                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

(2/3)

| Pin Name                                                            | Input/           | Function                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|---------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                     | Output           |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| DT/OE<br>(Data transfer/<br>output enable)                          | Input            | These are the data transfer control signal and read operation control signal respectively. They have different functions in the data transfer cycle and read cycle.                                                                                                                                                                                                                                                                                 |  |

|                                                                     |                  | Data transfer control signal (In data transfer cycle)  The data transfer cycle is initiated when a low level is input to this pin at the falling edge of RAS.                                                                                                                                                                                                                                                                                       |  |

|                                                                     |                  | Read operations control signal (In read cycle) Read operation is performed when this signal, and the RAS and CAS signals are activated. The input/output pin is high impedance when this signal is not activated. When the WB/WE signal is activated while the DT/OE signal is activated, the DT/OE signal is invalid in the memory and read operations cannot be performed.                                                                        |  |

| WB/WE (Write-per-bit/ Write enable)                                 |                  | These are the write operation control signal and mask write cycle (write-perbit function) mask data input control signal, respectively.  When this signal, RAS and CAS signals are activated, write operations or mask write can be performed. These mode are determined by the level of WB/WE at the falling edge of RAS.  High level 8-bit write cycle  Low level Mask write cycle (Write-per-bit)                                                |  |

| DSF<br>(Special function<br>enable)                                 |                  | This signal controls the selection of functions.  The selection of functions is determined by the level of this signal at the falling edge of the RAS and CAS. The functions will change as follows when this signal is high level.  The data transfer cycle changes to a split data transfer cycle.  The read/write cycle of each RAS clock changes to the flash write cycle.  The write cycle of each CAS clock changes to the block write cycle. |  |

| W0 to W7/IO0 to IO7<br>(Mask data selects/<br>Data inputs, outputs) | Input/<br>Output | These are normally 8-bit data bus and are used for inputting and outputting data. (IO0 to IO7).  Function as the mask data input pins (W0 to W7) in the mask write cycle (write-per-bit function).  Write operations can be performed only for W0 to W7 that are input with a high level at the falling edge of RAS (new mask data).  Functions as the column selection data input pin in the block write cycle.                                    |  |

(3/3)

|                                                  | †                | †                                                                                                                                                                                                                                                                                                              |  |

|--------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin Name                                         | Input/<br>Output | Function                                                                                                                                                                                                                                                                                                       |  |

| SC Input (Serial clock)                          |                  | This pin inputs the clock which controls the serial access port operation.  Serial Read                                                                                                                                                                                                                        |  |

|                                                  |                  | The data of the data register which is synchronized with the rising edge of the SC are output from the SIO0 to SIO7 pins and kept until the next SC rising edge.                                                                                                                                               |  |

|                                                  |                  | Serial Write The data from the SIO0 to SIO7 pins are latched at the rising edge of the SC and written in the data register.                                                                                                                                                                                    |  |

| SE<br>(Serial data input/<br>output enable)      |                  | This is a control pin for the serial access port input/output buffer. It controls data output during serial reading and controls data input during serial writing.  By inputting the serial clock, the serial pointer will operate even if SE has not been activated (high level input).                       |  |

| SIO0 to SIO7<br>(Serial data inputs/<br>outputs) | Input/<br>Output | These are the serial data input and output pins of the serial access port.                                                                                                                                                                                                                                     |  |

| QSF<br>(Special function<br>output)              | Output           | This is a position discrimination pin of the serial pointer (upper side or lower side).  Which side is being serial accessed (upper side or lower side) can be discriminated according to the output of this pin.  • High level Upper side (Addresses 256 to 511)  • Low level Lower side (Addresses 0 to 255) |  |

#### 2. Random Access Port Operations

The operation mode is determined by the  $\overline{CAS}$ ,  $\overline{DT}/\overline{OE}$ ,  $\overline{WB}/\overline{WE}$ , and DSF level at the falling edge of  $\overline{RAS}$  and DSF level at the falling edge of  $\overline{CAS}$ .

CAS RAS Falling Edge Falling Edge Operation Mode CAS DT/OE WB/WE DSF DSF L Read cycle X X Н L L Н Н Write cycle Cycle Н Н Block write cycle Н L Н L Mask write cycle (New mask/Old mask)Note 1 Н Н L L Read/Write Block mask write cycle (New mask/Old mask)Note 1 Н Н L L Н Н Н Н Н Color register set cycle Н Н Н Н L Write mask register set cycle Flash write cycle (New mask/Old mask)Note 1 Н Н Н L × Cycle Н L Н L Single read data transfer cycle × Transfer ( Н Н Split read data transfer cycle Н L × Single write data transfer cycle (New mask/Old mask)Note 1 L L L × Data | Split write data transfer cycle (New mask/Old mask)Note 1 Н L L Н × Cycle CAS before RAS refresh cycle (Option reset)Note 1, 2 L × L × CAS before RAS refresh cycle (No reset) L Н Н × × CAS before RAS refresh cycle (STOP register set)Note 2 L L Н × × Н L RAS only refresh cycle ×

Table 2-1. Operation Mode

Notes 1. Observe the following conditions when using the new mask data or old mask data in these cycles.

#### (1) Old mask data

Can be used after setting the mask data using the write mask register set cycle.

#### (2) New mask data

Can be used after setting the mask data using the  $\overline{CAS}$  before  $\overline{RAS}$  refresh cycle (Option reset cycle).

2. The STOP register is set to "FFH (11111111)" by the optional reset cycle.

Remark H: High level, L: Low level, x: High level or low level

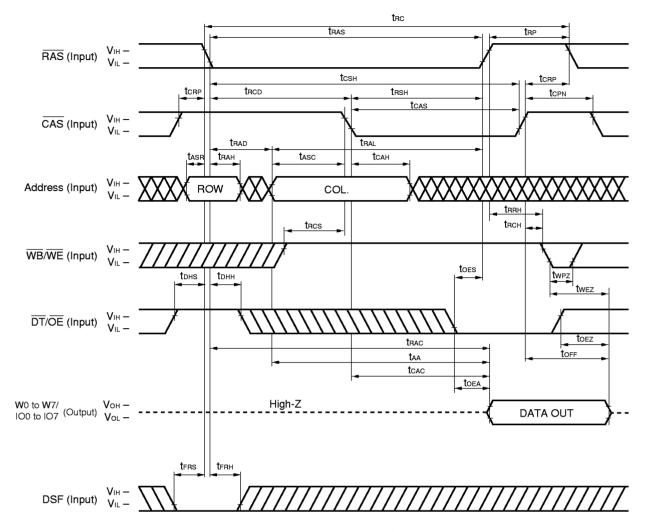

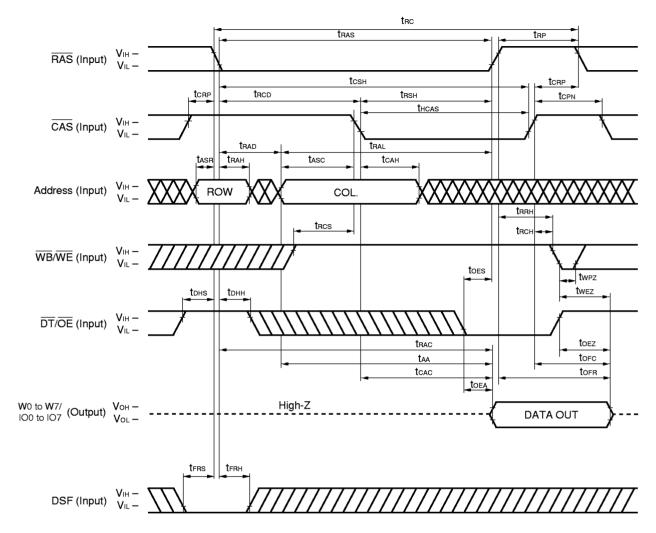

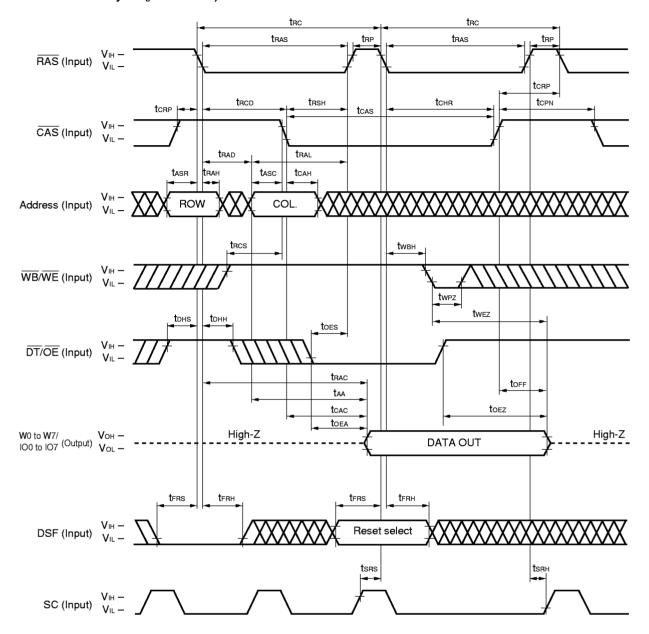

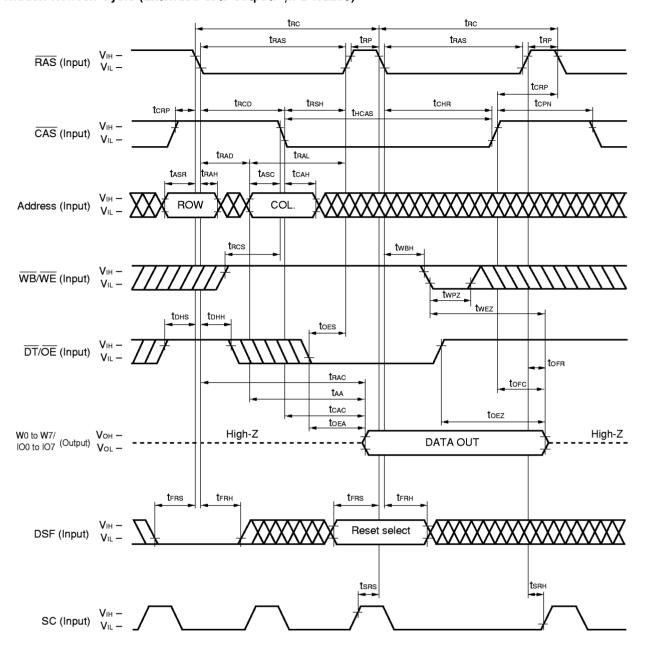

#### 2.1 Random Read Cycle

This product has a common 8-bit input/output pin. To output data, specify the address using the  $\overline{RAS}$  and  $\overline{CAS}$  clocks and then set  $\overline{DT/OE}$  to low level.

The data output will be kept until one of the following conditions is set.

- (1) Set RAS and CAS to high level

- (2) Set  $\overline{\rm DT}/\overline{\rm OE}$  to high level

- (3) Set WB/WE to low level

The read cycle and data transfer cycle are differentiated according to the level of  $\overline{DT}/\overline{OE}$  at the falling edge of the  $\overline{RAS}$  clock. If  $\overline{DT}/\overline{OE}$  is set to low level at the falling edge of the  $\overline{RAS}$  clock, data transfer cycle operations will be initiated. Therefore, to set the read cycle, input a high level above tohe (MIN.) to  $\overline{DT}/\overline{OE}$  from the falling edge of the  $\overline{RAS}$  clock, and then input a low level.

Caution Set the DSF to low level at the falling edge of RAS. If set to high level, the memory cell data cannot be output.

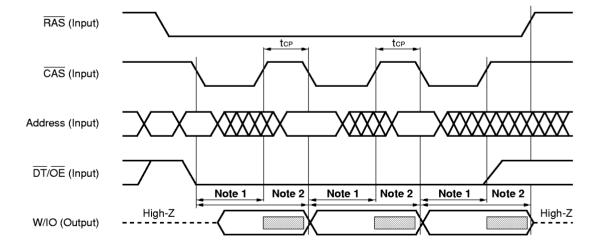

#### 2.1.1 Extended Read Data Output (µPD482235)

The  $\mu$ PD482235 adopt the hyper page mode cycle which is a faster read/write cycle than the fast page mode of the  $\mu$ PD482234 (Hyper page mode cycle time: 30 ns (MIN.)).

With this cycle, the read data output can be kept until the next  $\overline{CAS}$  cycle, and because the output is extended, the minimum cycle can easily be used. For example, by fixing  $\overline{DT}/\overline{OE}$  at low level after dropping  $\overline{RAS}$  and executing the hyper page read cycle, each time the column address is latched at the falling edge of  $\overline{CAS}$ , the data output will be updated and kept until the next falling edge of  $\overline{CAS}$ . As a result, the output will be extended only during  $\overline{CAS}$  precharge time (tcp) as compared to the normal fast page mode.

Figure 2-1. Extended Data Output of Hyper Page Mode

Notes 1. Time during which the output data is kept in the fast page read cycle.

2. Time during which the output data is kept in the hyper page read cycle ( part: Extended data output).

#### 2.2 Random Write Cycle (Early Write, Late Write)

There are three types of random write cycles-the early write and late write. To use these cycles, activate the  $\overline{RAS}$  and  $\overline{CAS}$  clocks and set  $\overline{WB/WE}$  to low level.

The WB/WE also controls the mask data for the write-per-bit function (mask write cycle). Therefore, when performing the normal write cycle which does not use the write-per-bit function, set this pin to high level at the falling edge of the RAS clock.

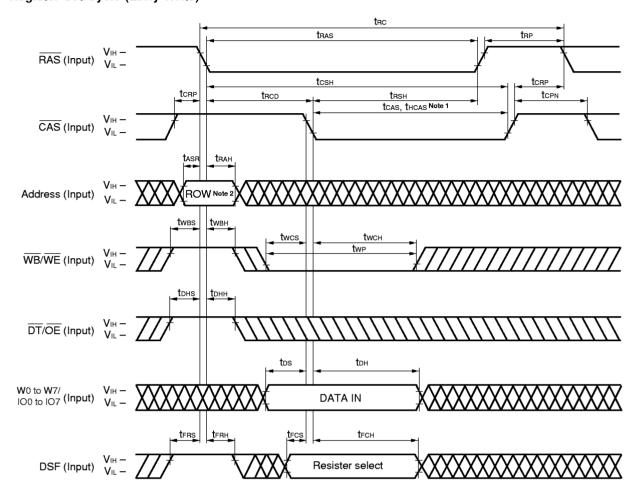

#### 2.2.1 Early Write Cycle

The early write cycle controls data writing according to the  $\overline{\text{CAS}}$  clock.

To execute this cycle, set  $\overline{\text{WB}}/\overline{\text{WE}}$  to low level earlier than the  $\overline{\text{CAS}}$  clock. The write data is taken into the device at the falling edge of the  $\overline{\text{CAS}}$  clock.

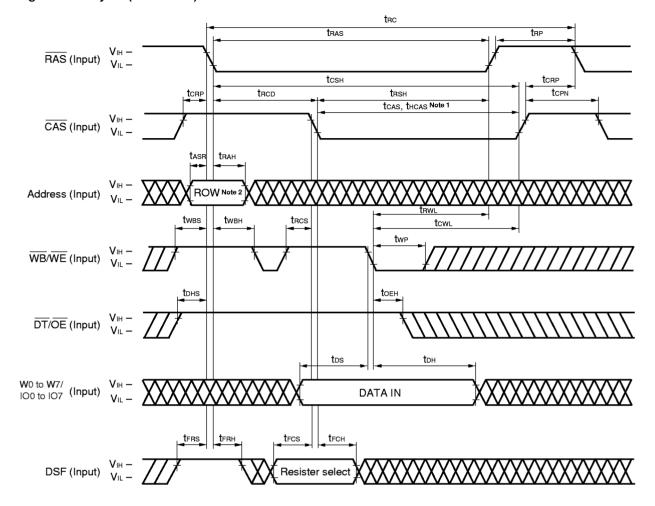

#### 2.2.2 Late Write Cycle

The late write cycle controls data writing according to the  $\overline{\text{WE}}$  clock.

To execute this cycle, set  $\overline{\text{WB}/\text{WE}}$  to low level later than the  $\overline{\text{CAS}}$  clock. The write data is taken into the device at the falling edge of  $\overline{\text{WB}/\text{WE}}$ . To set the output to high impedance at this time, keep  $\overline{\text{DT}/\text{OE}}$  at high level until  $\overline{\text{WB}}/\overline{\text{WE}}$  is input.

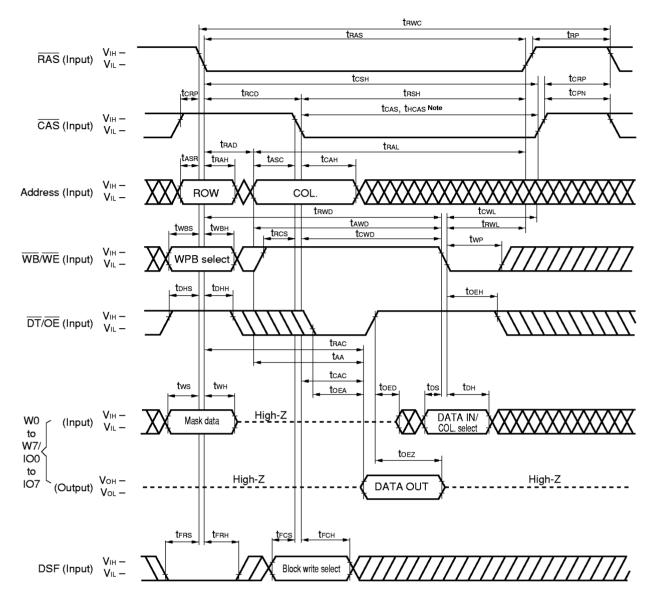

#### 2.3 Read Modify Write Cycle

The read modify write cycle performs data reading and writing in one RAS and CAS cycle.

To execute this cycle, delay  $\overline{\text{WB/WE}}$  from the late write cycle by trwo (MIN.), tcwo (MIN.), and tawo (MIN.). Follow the toez and toed specifications so that the output data and input data do not clash in the data bus. The data after modification can be input after more than toed (MIN.) from the rising edge of  $\overline{\text{DT/OE}}$ .

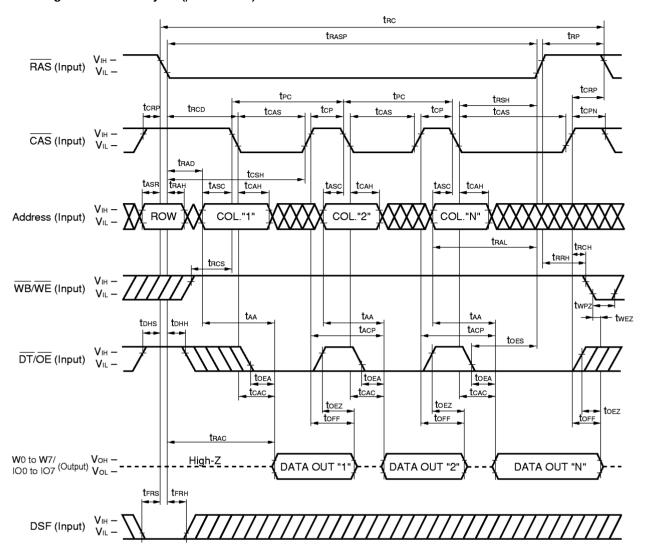

#### 2.4 Fast Page Mode Cycle (μPD482234)

The  $\mu$ PD482234 adopt the fast page mode. This mode accesses memory cells in the same row array in about 1/3 of the time taken by the normal random read/write cycle. This fast page mode cycle is executed by repeating the  $\overline{\text{CAS}}$  clock cycle more than two times while the  $\overline{\text{RAS}}$  clock is being activated. In this mode read, write and read modify write cycles are available for each of the consecutive  $\overline{\text{CAS}}$  cycles within the same  $\overline{\text{RAS}}$  cycle.

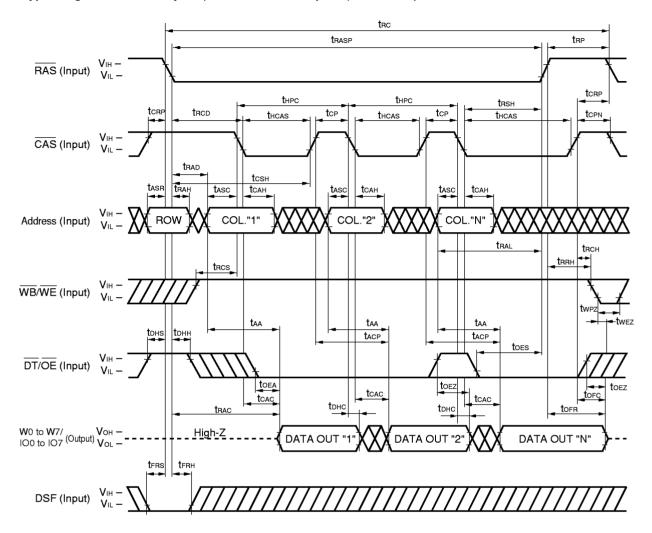

#### 2.5 Hyper Page Mode Cycle (µPD482235)

The  $\mu$ PD482235 adopt a hyper page mode cycle which is a faster read/write cycle than the fast page mode of the  $\mu$ PD482234 (Hyper page mode cycle time: 30 ns (MIN.)).

In this cycle, because the read data output is kept until the following  $\overline{\text{CAS}}$  cycle and as a result, the output is extended, the minimum cycle can easily be used. The output is extended compared to the normal fast page mode of  $\mu\text{PD482234}$ . Refer to **2.1.1 Extended Read Data Output**.

#### 2.5.1 Setting the Output to the High Impedance State

The hyper page mode can use one of three methods of setting the output pin to the high impedance state depending on the version; these methods are  $\overline{\text{WE}}$  control and  $\overline{\text{OE}}$  control (latched control).

#### (1) WE control

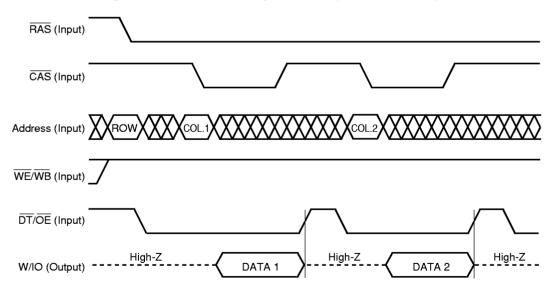

After a high level is input to  $\overline{CAS}$ , when a pulse conforming to the twez specification is supplied to the  $\overline{WE}$  pin ( $\overline{WE}$  = enable) during the same  $\overline{CAS}$  cycle, the W/IO pin is held in the high impedance state until the next  $\overline{CAS}$  cycle.

RAS (Input)

CAS (Input)

Address (Input)

ROW

COL.1

COL.2

WE/WB (Input)

DT/OE (Input)

High-Z

DATA 1

High-Z

DATA 2

High-Z

Figure 2-2. WE Control Output Control

#### (2) OE control (latched control)

After a high level is input to  $\overline{CAS}$ , when a high level is supplied to the  $\overline{OE}$  pin ( $\overline{OE}$  = disable) during the same  $\overline{CAS}$  cycle, the W/IO pin is held in the high impedance state until the next  $\overline{CAS}$  cycle. This specification enables efficient use of  $\overline{OE}$  interleaving during parallel connection.

Figure 2-3. OE Control Output Control (Latched Control)

#### 2.6 Flash Write Cycle

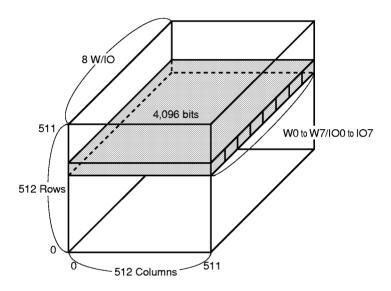

This cycle writes the color register data in a 4,096-bit memory cell in one cycle. The memory cell range for one flash write cycle is 512 columns on the same row address (512-column  $\times$  8  $\cdot$  IO = 4,096 bits).

#### 2.6.1 Execution of Flash Write Cycle

To execute the flash write cycle, set  $\overline{\text{WB}/\text{WE}}$  to low level at the falling edge of  $\overline{\text{RAS}}$ .

By using the write-per-bit function (new mask data/old mask data), only the required W/IO can be selected and written.

Figure 2-4. Memory Cell Range That Can be Written with Flash Write Cycle

**Remark** is the memory cell range that can be written in one flash write cycle.

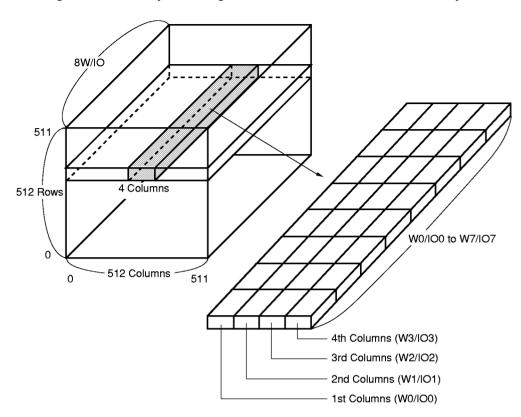

#### 2.7 Block Write Cycle

This cycle writes the color register data in 32-bit memory cell in one cycle. The memory cell range in which data can be written in one block write cycle is four continuous columns on one row address (4-column  $\times$  8  $\cdot$  IO = 32 bits).

Any column of the four columns can be selected and writing prohibited. Determine whether to write or prohibit writing according to the data selected for column.

#### 2.7.1 Free Column Selection

Determine which column to select according to the W/IO pin to which the data selected for the column is to be input.

The four columns (1st to 4th) correspond to W0 to W3/IO0 to IO3 to which the data selected for column will be input (The following table shows the 1st to 4th columns specified by A0 and A1 and the corresponding W/IO pins to which the data selected will be input.).

#### 2.7.2 Column Select Data

Input column select data for every four columns at the 32 bits (4-column  $\times$  8  $\cdot$  IO). The data will be written if the column select data is "1". Writing will be prohibited if the column select data is "0".

#### 2.7.3 Execution of Block Write Cycle

At the falling edge of the slowest signal ( $\overline{CAS}$ ,  $\overline{WB}/\overline{WE}$ ), input the "1" column select data or "0" column select data to W0 to W3/IO0 to IO3 corresponding to columns 1st to 4th.

By using the write-per-bit (new mask data/old mask data) function, only the required W/IO can be selected and written.

Table 2-2. I/O Pins Input with Column Select Data Corresponding to Columns 1st to 4th

| Selected 4 Columns | Column Address and Corresponding<br>W/IO Pin |            |     | Column Select Data | Writing |

|--------------------|----------------------------------------------|------------|-----|--------------------|---------|

|                    | A1                                           | <b>A</b> 0 | 10  |                    |         |

| 1st column         | 0                                            | 0          | 100 | 1                  | Yes     |

|                    |                                              |            |     | 0                  | No      |

| 2nd column         | 0                                            | 1          | 101 | 1                  | Yes     |

|                    |                                              |            |     | 0                  | No      |

| 3rd column         | 1                                            | 0          | 102 | 1                  | Yes     |

|                    |                                              |            |     | 0                  | No      |

| 4th column         | 1                                            | 1          | 103 | 1                  | Yes     |

|                    |                                              |            |     | 0                  | No      |

Figure 2-5. Memory Cell Range That Can be Written in Block Write Cycle

**Remarks 1.** is the memory cell range that can be written in one block write cycle.

2. ( ) is the W/IO pin input with the column select data.

#### 2.8 Register Set Cycle (Color Register, Write Mask Register)

This cycle writes data in the color register and write mask register. To execute the register set cycle, set  $\overline{CAS}$ ,  $\overline{DT/OE}$ ,  $\overline{WB/WE}$  and DSF to high level at the falling edge of  $\overline{RAS}$ . Determine which register to select according to the DSF level at the falling edge of  $\overline{CAS}$ .

The register set cycle also serves as the  $\overline{RAS}$  only refresh cycle.

Table 2-3. Register Selection

| DSF level at CAS falling edge | Selected register   |

|-------------------------------|---------------------|

| High level                    | Color register      |

| Low level                     | Write mask register |

Caution After selecting the write mask register and writing the mask data, the write-per-bit function in the mask write cycle will be set for the old mask register. Refer to 2.9.1 Write-Per-Bit Function.

#### 2.9 Mask Write Cycle

Cycles that use the write-per-bit function during the random write cycle, flash write cycle, block write cycle, write data transfer cycle, are called mask write cycles. In the fast page/hyper page mode write cycle, the mask data cannot be changed during the  $\overline{\text{CAS}}$  cycle.

#### 2.9.1 Write-Per-Bit Function

The write-per-bit function writes data using the mask data only in the required IO-pin. It writes when the mask data is "1" and prohibits writing when the data is "0".

Table 2-4. Mask Data Selection

| <b>W</b> Pin | Mask Data | Writing |

|--------------|-----------|---------|

| W0 to W7     | 1         | Yes     |

|              | 0         | No      |

#### 2.9.2 Selecting Mask Data

There are two ways of selecting mask data. One is the new mask data method and the other is the old mask data method.

With the new mask data method, new mask data is set in the cycle writing. With the old mask data, mask data set in the write mask register is used.

#### (1) New Mask Data Method

This method is usable in all versions.

To switch to the mode using new mask data, set the DSF to low level at the falling edge of  $\overline{CAS}$  in the  $\overline{CAS}$  before  $\overline{RAS}$  refresh cycle.

As a result, the write-per-bit function can be used using the old mask data from the next mask write cycle.

#### (2) Old Mask Data Method

To switch to the mode using old mask data, set the DSF to low level at the falling edge of  $\overline{CAS}$  in the write mask register set cycle, and write the mask data in the write mask register.

As a result, the write-per-bit function can be used using the old mask data from the next mask write cycle.

#### 2.9.3 Execution of Mask Write Cycle

To execute the write-per-bit function, select the new mask data method or old mask data method, and set  $\overline{\text{WB/WE}}$  to low level at the falling edge of  $\overline{\text{RAS}}$  of each write cycle. At this time, input the mask data to the W pin in the write cycle using the new mask data. In the write cycle using the old mask data, as the mask data set to the write mask register will be used, there is no need to input the mask data to the W pin.

This function is valid only at the falling edge of  $\overline{RAS}$ . In the fast page/hyper page mode write cycle, the mask data determined in the first  $\overline{RAS}$  cycle for moving onto the next fast page/hyper page mode will be valid while the fast page/hyper page mode write cycle continues.

#### 2.10 Refresh Cycle

The refresh cycle of this product consists of the  $\overline{CAS}$  before  $\overline{RAS}$  refresh cycle and refresh cycle using external address inputs ( $\overline{RAS}$  only refresh and read/write refresh). The refresh period is the same as the DRAM (Standard), 512 cycles/8 ms.

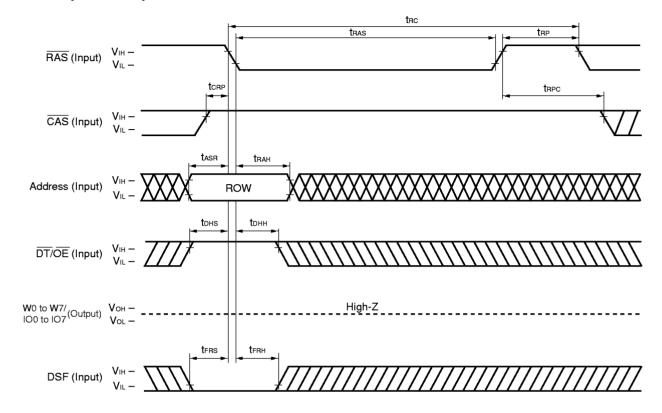

#### 2.10.1 Refresh Cycle Using External Address Input (RAS Only Refresh and Read/Write Refresh)

By specifying the row address using the 9 bits between A0 to A8 at the falling edge of  $\overline{RAS}$ , setting  $\overline{CAS}$  and  $\overline{DT/OE}$  to high level, and keeping  $\overline{CAS}$  at high level while  $\overline{RAS}$  is low level, the memory cells on the specified row address (512  $\times$  8 bits) can be refreshed. At this time, refresh is executed, W0 to W7/IO0 to IO7 pins are kept at high impedance, and information such as memory contents, register data, function settings, etc. are all also kept.

At the falling edge of  $\overline{RAS}$ , all cycles whose  $\overline{CAS}$  are high level input the external address. Therefore, in addition to the read/write cycle operations, etc. refresh operations similar to the  $\overline{RAS}$  only refresh operations will be performed. For this reason, in systems in which addresses in the memory are always increased or decreased, it may not be necessary to perform refresh again.

When several devices exist on one bus, data will clash in the bus during the above read/write operations unless each device is equipped with a buffer. Consequently, as it is necessary to set the I/O line to high impedance beforehand during refresh, normally the  $\overline{RAS}$  only refresh operation is used.

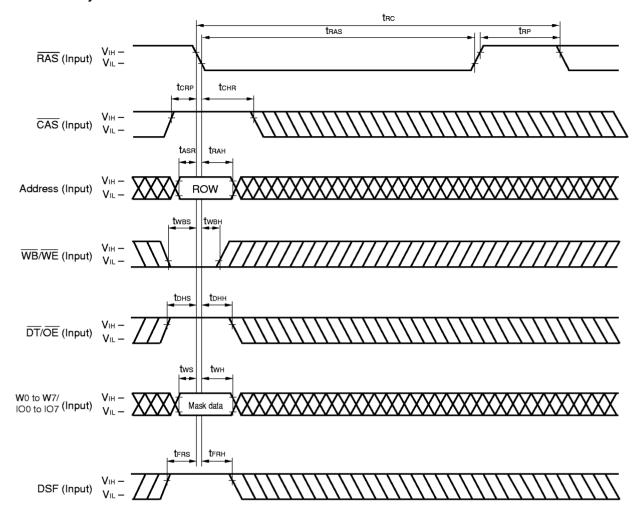

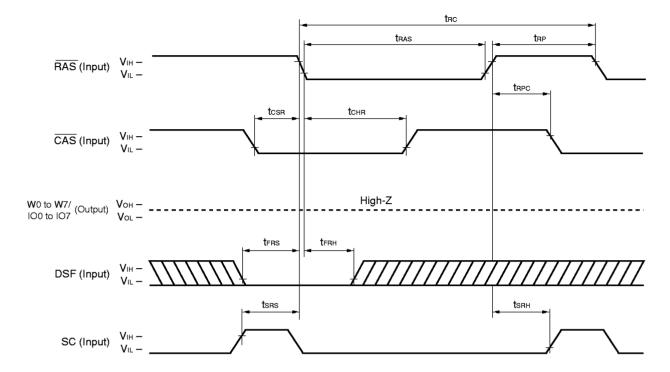

#### 2.10.2 CAS Before RAS Refresh Cycle (Including Hidden Refresh)

When  $\overline{\text{CAS}}$  is set to low level at the falling edge of  $\overline{\text{RAS}}$ , the refresh address is supplied from the internal refresh address counter. The internal refresh address counter is increased automatically each time this refresh cycle is executed.

During this refresh cycle, functions of random access port and serial access port are selected as follows according to the DSF and  $\overline{\text{WB}}/\overline{\text{WE}}$  levels at the falling edge of  $\overline{\text{RAS}}$ .

#### (1) When DSF is low level: Optional reset

All STOP register data become "1" and the mask write cycle switches to the new mask data method.

#### (2) When DSF is high level and WB/WE is low level: STOP register set

The STOP register data is input from the A0 to A7 pins at the falling edge of RAS.

#### (3) When DSF, WB/WE is high level: No reset

Only refresh operations are performed and the function selection state is kept.

In all cases, the W/IO pin is kept at high impedance. When  $\overline{CAS}$  and  $\overline{DT/OE}$  are kept low level while the mode is changed to the  $\overline{CAS}$  before  $\overline{RAS}$  refresh cycle following the read cycle, and  $\overline{RAS}$  is activated, the hidden refresh cycle will be initiated. In this cycle, the W/IO pin does not become high impedance and the data read in the former read cycle will be kept as it is.

Because internal memory operations are equivalent to  $\overline{CAS}$  before  $\overline{RAS}$  refresh, no external addresses are required.

Like  $\overline{\text{CAS}}$  before  $\overline{\text{RAS}}$  refresh, in the hidden cycle, functions will be selected according to the level of DSF,  $\overline{\text{WB}}/\overline{\text{WE}}$  at the falling edge of  $\overline{\text{RAS}}$ . Operations are guaranteed when DSF is low level and when DSF,  $\overline{\text{WB}}/\overline{\text{WE}}$  are high level.

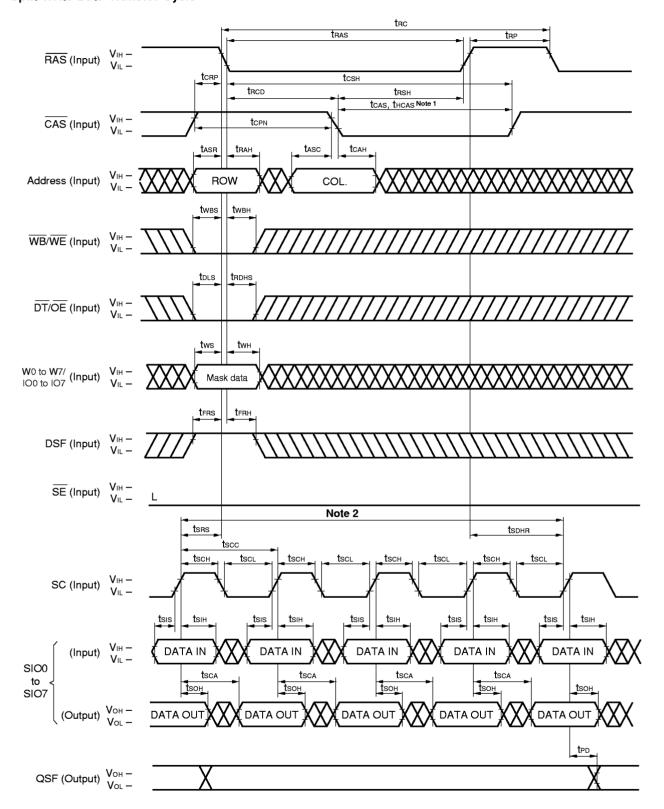

#### 3. Serial Access Port Operations

There are two types of data transfer cycles-data transfer from the random access port to the serial access port (read data transfer) and data transfer from the serial access port to the random access port (write data transfer). There are also two types of data transfer methods-single data transfer and split data transfer.

To set the data transfer cycle, input high level to  $\overline{CAS}$  and input low level to  $\overline{DT}/\overline{OE}$  at the falling edge of  $\overline{RAS}$ . The data transfer type differs according to the input levels of  $\overline{WB}/\overline{WE}$ , and DSF at the falling edge of  $\overline{RAS}$ .

Table 3-1. Serial Access Port Operation Mode

| At RAS Falling Edge |       |       | je  |                                                 | Transfer Direction               |                         |  |  |

|---------------------|-------|-------|-----|-------------------------------------------------|----------------------------------|-------------------------|--|--|

| CAS                 | DT/OE | WB/WE | DSF | Data Transfer Type                              | Transfer Source                  | Transfer<br>Destination |  |  |

| Н                   | L     | Н     | L   | Single read data transfer                       | ad data transfer Random access S |                         |  |  |

| Н                   | L     | Н     | Н   | Split read data transfer                        | port                             | port                    |  |  |

| Н                   | L     | L     | L   | Single mask write data transfer <sup>Note</sup> | Serial access                    | Random access           |  |  |

| Н                   | L     | L     | Н   | Split mask write data transfer <sup>Note</sup>  | port                             | port                    |  |  |

Note Write-per-bit function can be specified.

Remark H: High level, L: Low level

#### 3.1 Single Data Transfer Method

With this method,  $512 \text{ words} \times 8 \text{ bits}$  (whole memory range of serial access port) data is transferred at one time. This method can be used in both write data transfer and read data transfer.

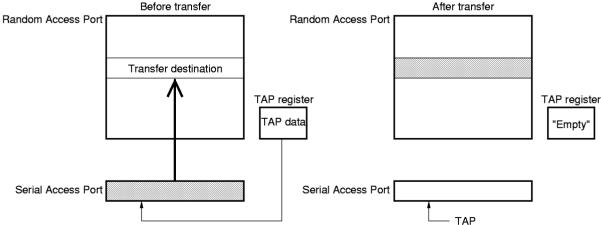

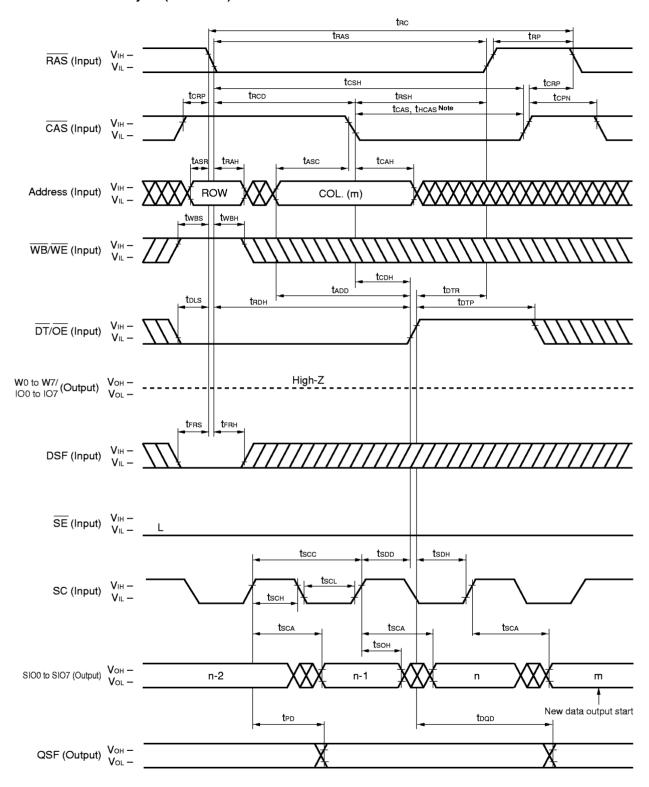

#### 3.1.1 Single Read Data Transfer Cycle

This cycle transfers the 4K-bit (512 words  $\times$  8 bits) data of the random access port to the serial access port in one cycle.

#### (a) Setting of Single Read Data Transfer Cycle

To set the data transfer cycle, input a high level to  $\overline{CAS}$  and  $\overline{WB}/\overline{WE}$  and low level to  $\overline{DT}/\overline{OE}$  and DSF at the falling edge of  $\overline{RAS}$ .

Using the row address input to A0 to A8 at the falling edge of  $\overline{RAS}$ , the memory cells (512 words  $\times$  8 bits) of the transfer source of the random access port can be selected. The address data input to A0 to A8 at the falling edge of  $\overline{CAS}$  will be latched as the TAP register data of serial access port. Refer to 3.4 TAP Register.

#### (b) Execution of Single Read Data Transfer Cycle

To execute the data transfer cycle, set the single read data transfer cycle and then input a high level to  $\overline{\text{DT}}/\overline{\text{DE}}$  and  $\overline{\text{BAS}}$ .

When SC is active (edge control), data transfer will be executed at the rising edge of  $\overline{DT/OE}$ . When SC is inactive (self control), it will be executed at the rising edge of  $\overline{RAS}$ . At the same time, the serial address pointer jumps to the start column (TAP) of the next serial read cycle, and the TAP register will be set the empty state.

After the transfer is completed, the new serial access port data is output after tsca following the rise of the SC clock that occurs after tsdh if the SC is active, and after tsdh if SC is inactive.

Caution When the single read data transfer cycle is executed while the serial access port is performing serial write operations, the serial access port will start serial read operations at the rising edge of RAS. Refer to 4. Electrical Characteristics Read Data Transfer Cycle (Serial Write → Serial Read Switching) Timings.

#### 3.1.2 Single Mask Write Data Transfer Cycle

This cycle transfers 4K-bit (512 words  $\times$  8 bits) data of the serial access port to the random access port in one cycle. Because WB/WE is low level at the falling edge of RAS, the write-per-bit function always functions in this transfer cycle. Refer to 2.9 Mask Write Cycle.

#### (a) Setting of Single Mask Write Data Transfer Cycle

To set this cycle, latch the data to be transferred to the serial access port, and then input a high level to CAS and low level to DT/OE, WB/WE, and DSF at the falling edge of RAS. Because the write-per-bit function functions in this transfer operation, for the new mask data method, the mask data must be supplied to W0 to W7 at the falling edge of RAS, and for the old mask data method, there is no need to control the mask

The memory cells (512 words × 8 bits) of the transfer destination of the random access port are selected using the row address input to A0 to A8 at the falling edge of RAS. The address data input to A0 to A8 at the falling edge of CAS is input as the TAP register data of serial access port. Refer to 3.4 TAP Register.

#### (b) Execution of Single Mask Write Data Transfer Cycle

To execute this cycle, set the single write data transfer cycle and then input high level to RAS. Data will be transferred at the rising edge of RAS. At the same time, the serial address pointer jumps to the start column (TAP) of the next serial write cycle, and the TAP register will be set the empty state.

After the transfer is completed, the new serial access port data is latched at the rising edge of the SC clock that occurs after tsphr.

- Caution 1. When the single mask write data transfer cycle is executed while the serial access port is performing serial read operations, the serial access port will start serial write operations at the rising edge of RAS. Refer to 4. Electrical Characteristics Write Data Transfer Cycle (Serial Read → Serial Write Switching) Timings.

- 2. Always make CAS low level in the write data transfer cycle and latch TAP. If write data transfer is performed without setting TAP, serial access port operations cannot be ensured until either one of the following points. If the SC clock is input during this time, the serial register value also cannot be guaranteed.

- Until the falling edge of CAS during the write data transfer cycle

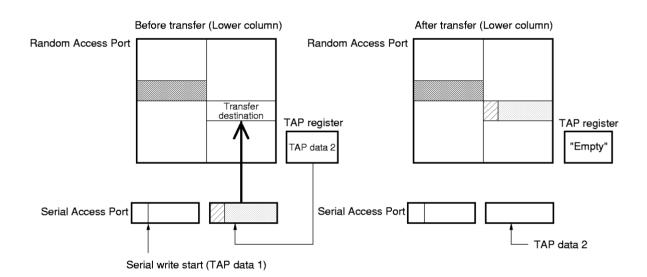

Figure 3-1. Single Write Data Transfer and TAP Operation

· Until the read data transfer cycle is executed again

Before transfer Random Access Port

#### 3.2 Split Data Transfer Method

With this method, the 512 words  $\times$  8 bits (whole memory range of serial access port) data is divided into the lower column (0 to 255) and upper column (256 to 511), each consisting of 256 words  $\times$  8 bits.

Because the columns are divided into upper and lower columns with this method, data transfer can be performed on lower column (or upper column) while performing read/write operations in the upper column (or lower column). For this reason, transfer timing design is easy. This transfer method can be used in both write data transfer and read data transfer.

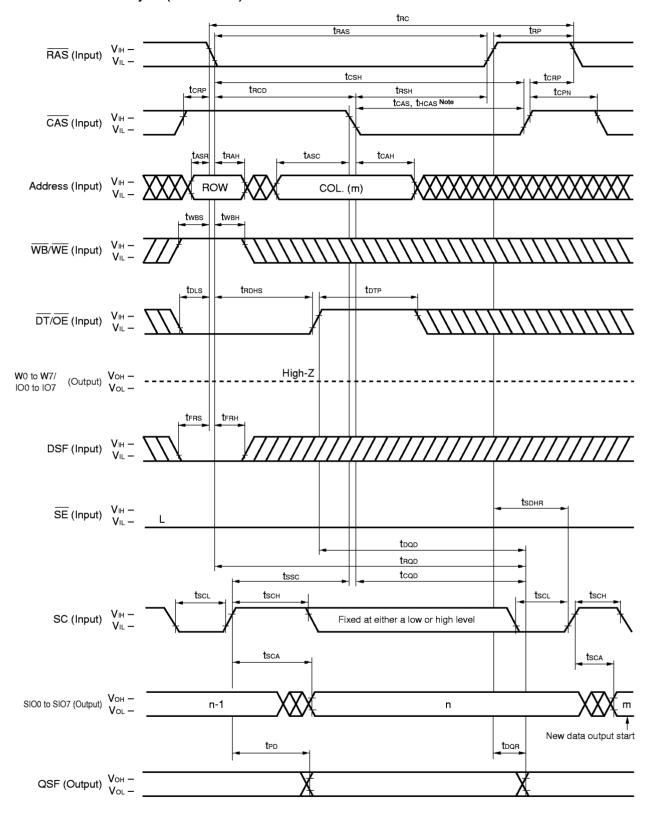

#### 3.2.1 Split Read Data Transfer Cycle

This cycle divides the 4K-bit (512 words  $\times$  8 bits) data of the random access port into the lower and upper columns and transfers them to the serial access port.

In this cycle, the serial read/write can be performed in the columns to which data is not transfer.

#### (a) Setting of Split Read Data Transfer Cycle

To set this cycle, input a high level to  $\overline{CAS}$ ,  $\overline{WB/WE}$  and DSF, and low level to  $\overline{DT/OE}$  at the falling edge of  $\overline{RAS}$ .

The memory cells (512 words  $\times$  8 bits) of the transfer source of the random access port are selected using the row address input to A0 to A8 at the falling edge of  $\overline{RAS}$ . And the address data input to A0 to A7 at the falling edge of  $\overline{CAS}$  is latched as the TAP register data of serial access port. Refer to **3.4 TAP Register**. There is no need to control address data input to A8).

#### (b) Execution of Split Read Data Transfer Cycle

To execute this cycle, set the split read data transfer cycle and then input the high level to  $\overline{RAS}$ . Data will be transferred at the rising edge of  $\overline{RAS}$ . Data is transferred from the random access port to the serial access port automatically at the column side (Column not pointed to by the serial address pointer) where serial access port is inactive. To confirm the transferred column side, check the output state of the QSF pin. Refer to 3.3.3 QSF Pin Output.

When the serial address pointer comes to the jump source address specified by the STOP register, the serial address pointer jumps to the start column (TAP) of the serial read/write cycle at the inactive column side, and the TAP register will be set the empty state.

#### 3.2.2 Split Mask Write Data Transfer Cycle

This cycle divides the 4K-bit (512 words  $\times$  8 bits) data of the serial access port into the lower and upper columns and transfers them to the random access port.

In this cycle, serial read/write can be performed for columns to which data is not transferred.

Because WB/WE is low level at the falling edge of RAS, the write-per-bit function always functions in this transfer cycle. Refer to 2.9 Mask Write Cycle.

#### (a) Setting of Split Mask Write Data Transfer Cycle

To set this data transfer cycle, input a high level to  $\overline{CAS}$  and DSF and low level to  $\overline{DT}/\overline{OE}$ ,  $\overline{WB}/\overline{WE}$  at the falling edge of  $\overline{RAS}$ . Because the write-per-bit function functions in this transfer operation, for the new mask data method, the mask data must be supplied to W0 to W7 at the falling edge of  $\overline{RAS}$ , and for the old mask data method, there is no need to control the mask data.

The memory cells (512 words  $\times$  8 bits) of the transfer destination of the random access port are selected using the row address input to A0 to A8 at the falling edge of  $\overline{\text{RAS}}$ . The address data input to A0 to A7 at the falling edge of  $\overline{\text{CAS}}$  is input as the TAP register data. Refer to **3.4 TAP Register**. There is no need to control address data input to A8.

#### (b) Execution of Split Mask Write Data Transfer Cycle

To execute this cycle, set the split write data transfer cycle and then input high level to  $\overline{RAS}$ . Data will be transferred at the rising edge of  $\overline{RAS}$ . Data is transferred from the serial access port to the random access port automatically at the column side (Column not pointed to by the serial address pointer) where the serial access port is inactive. To confirm the transferred column side, check the output state of the QSF pin. Refer to 3.3.3 QSF Pin Output.

When the serial address pointer comes to the jump source address specified by the STOP register, the serial address pointer jumps to the start column (TAP) of the serial read/write cycle at the inactive column side, and the TAP register will be set the empty state.

Random Access Port

Transfer destination

TAP register

TAP data 1

Serial Access Port

Serial write start

TAP data 1

TAP data 1

Serial write start

Figure 3-2. Split Mask Write Data Transfer and TAP Operations

#### 3.3 Serial Read/Write

The serial access port (512 words  $\times$  8 bits) is independent from the random access port and can perform read and write operations. The serial access port performing single data transfer and split data transfer can not perform read and write operations independently.

Caution When the power is turned on, the serial access port sets into the input (write) mode and the SIO pin is the high impedance state.

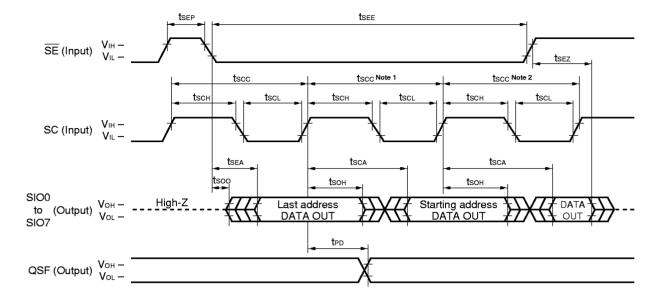

#### 3.3.1 Serial Read Cycle

To set the serial read cycle, perform the single read data transfer cycle (The mode will not change in the split read data transfer cycle.).

Execute the single read data transfer cycle and latch the data and TAP data. By inputting a clock signal to the SC pin and inputting a low level to the  $\overline{\text{SE}}$  pin, data will be output from the serial address pointer specified by TAP register. The data synchronizes with the rising edge of the SC clock and is output from the SIO0 to SIO7 pin, and the data is kept until the next rising edge of the SC clock.

#### (a) Reading-Jump

The  $\overline{SE}$  pin controls the SIO pin output buffer independently from the SC clock. By setting the  $\overline{SE}$  pin to high level even while inputting the SC clock, SIO0 to SIO7 pins become high impedance. But the operations of serial address pointer will be continued while the SC clock is being input even though reading has been prohibited from  $\overline{SE}$  pin. Reading-jump of the column can be performed using this function.

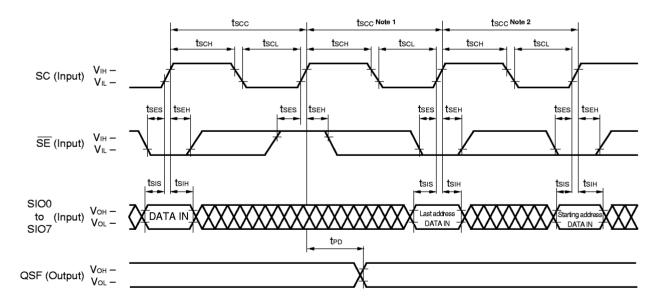

#### 3.3.2 Serial Write Cycle

To set the serial write cycle, perform the single write data transfer cycle (The mode will not change in the split write data transfer cycle.). To prevent the transfer data from being written in the memory cell of the random access port, set all bits of the mask data to "0" and control the mask data.

Execute the single write data transfer cycle and set the serial write cycle. By inputting the clock signal to the SC pin and inputting a low level to the  $\overline{\text{SE}}$  pin, data can be latched from the serial address pointer specified by TAP register. The data synchronizes with the rising edge of the SC clock and is input from SIO0 to SIO7 pins. Be sure to follow the specifications for the setup time (tses) and hold time (tseh) of  $\overline{\text{SE}}$  pin for the SC clock.

#### (a) Writing-Jumps (Intermittent Writing)

The  $\overline{SE}$  pin controls writing operations independently from the SC clock. By setting the  $\overline{SE}$  pin to high level even while inputting the SC clock, writing will not be executed. But the operations of serial address pointer will be continued while the SC clock is being input even though writing has been prohibited from  $\overline{SE}$  pin. These functions enable writing-jumps (intermittent writing) to be performed. The masked data is kept as the old data.

#### 3.3.3 QSF Pin Output

QSF pin determines whether the serial address pointer is at the upper column side (addresses 256 to 511) or the lower column side (addresses 0 to 255) at the rising edge of the following SC clock during serial read or write. In other words, it outputs the uppermost bit (A8) of the column address of the serial address pointer.

During split data transfer cycle, data is transferred at the column side where serial access port is inactive. The following table shows the QSF pin output state and the access pointer of following SC clocks.

| QSF Output | Access Address of Following SC clock | Transfer Destination<br>(Split Data Transfer Method) |

|------------|--------------------------------------|------------------------------------------------------|

| Low level  | Addresses 0 to 255                   | Addresses 256 to 511                                 |

| High level | Addresses 256 to 511                 | Addresses 0 to 255                                   |

#### 3.4 TAP (Top Access Point) Register

The TAP register is a data register which specifies the start address (first serial address point = TAP) of the serial read or serial write.

Set data to this register each time a transfer cycle is executed.

#### 3.4.1 Setting of TAP Register

The data input to A0 to A8 (A0 to A7: Split data transfer) at the falling edge of  $\overline{\text{CAS}}$  during the setting of a transfer cycle is set as the TAP register data. By executing the transfer cycle, the start address of the following serial read (or write) operations is specified by the data of the TAP register and the TAP register will be kept in the empty state until the TAP register is set again.

In the split data transfer cycle, because the inactive serial access port column addresses are specified by the data of the TAP register automatically, there is no need to control the A8 data.

Caution When the TAP register is empty, the address following the 511 serial address point will be 0. In addition, because the serial address pointer will not jump to the column specified by the STOP register, the binary boundary jump function cannot be used. Refer to 3.6 Binary Boundary Jump Function.

#### 3.5 STOP Register

The STOP register is a data register which determines the column of the jump source when jumping to a different column side (lower column or upper column) in the split data transfer cycle. Five types of columns can be selected for starting jump (jumping is possible at 2, 4, 8, 16, and 32 points). The following table shows the correspondence between the column at the jump source and data of the STOP register.

Once set, the STOP register data is kept until it is set again.

#### 3.5.1 Setting of STOP Register

To set the STOP register, set WB/WE to low level at the falling edge of RAS in the CAS before RAS refresh cycle. The data input to A0 to A7 will be input as the STOP register data.

STOP Register Data Divi-Bit Jump Source Bit Column (Decimal Number) Width sion A4 A3 to A0 A6 A5 | 255 1 1 1/2 256 511 127, 255 0 1 1/4 128 1 383, 511 63, 127, 191, 255 0 0 1 1 1 1/8 64 319, 383, 447, 511 31, 63, 95, 127, 159, 191, 223, 255 0 0 0 1/16 1 1 32 287, 319, 351, 383, 415, 447, 479, 511 15, 31, 47, 63, 79, 95, 111, 127, 143, 159, 175, 191, 207, 223, 239, 255 0 0 0 0 1 1/32 16 271, 287, 303, 319, 335, 351, 367, 383, 399, 415, 431, 447, 463, 479, 495, 511

Table 3-2. STOP Register Data and Jump Source Column

Remark A8: Don't care.

Caution When the power is supplied, all STOP register data will be undefined.

#### 3.6 Binary Boundary Jump Function

This function causes the serial address pointer jump to the TAP specified by the TAP register when the pointer moves to a column specified by the STOP register (split data transfer).

This function cannot be used when the jump destination address is not set (TAP register is empty).

This function facilitates tile map application which divides the screen into tiles and manages data for each tile.

#### 3.6.1 Usage of Binary Boundary Jump Function

After setting the STOP register, execute the single read (or write) data transfer and initialize the serial access port. The initialization process will switch the serial access port read (or write) operations, set TAP, set the serial access port data, and set the TAP register to empty. By inputting the serial clock in this state, the serial access port will read (or write) operations from TAP in ascending order of address. Because the TAP register is in the empty state, the address at the jump source set by the STOP register will be ignored, and the serial address pointer will move on.

When the column to be jumped approaches, execute split data transfer and set new TAP data in the TAP register. The serial pointer will jump at the desired jump source address. Jump can be controlled freely by repeating these operations.

#### 3.7 Special Operations

#### 3.7.1 Serial Address Set Operations

Because the serial address counter is undefined when the power up, the serial access port operations when the SC clock is input are not guaranteed. Execute single read (or write) transfer after turning on the power. The serial access port will be initialized, enabling serial access port operations to be performed.

#### 3.7.2 Lap Around Operations

If all the data of the register is read (write) during data transfer while the serial read (write) cycle is being executed, the serial pointer will repeat 0 to 511.

#### 3.7.3 Cycle After Power On

After supplying power, initialize the internal circuitry by waiting for at least 100  $\mu$ s after Vcc  $\geq$  4.5 V, then supplying at least 8  $\overline{RAS}$  clock cycles. The  $\overline{RAS}$  clock only requires that the, that, and the are satisfied; there is no problem if other signals are in any state. Note however that if the signal supplied to  $\overline{RAS}$ ,  $\overline{CAS}$ ,  $\overline{DT/OE}$ , and  $\overline{WB/WE}$  is high at power-on, the serial access port and each register have the following values.

• Serial access port ...... Input mode, SIO: High impedance

● Color register ...... Undefined

● Mask register ...... All "1"

● TAP register ...... Undefined

● STOP register ...... Undefined

#### 4. Electrical Characteristics

#### **Absolute Maximum Ratings**

| Parameter                     | Symbol           | Rating       | Unit |

|-------------------------------|------------------|--------------|------|

| Pin voltage                   | V⊤               | -1.0 to +7.0 | ٧    |

| Supply voltage                | Vcc              | -1.0 to +7.0 | ٧    |

| Output current                | lo               | 50           | mA   |

| Power dissipation             | Po               | 1.5          | W    |

| Operating ambient temperature | Та               | 0 to 70      | °C   |

| Storage temperature           | T <sub>stg</sub> | -55 to +125  | °C   |

Caution Exposing the device to stress above those listed in Absolute Maximum Ratings could cause permanent damage. The device is not meant to be operated under conditions outside the limits in the operational sections of this characteristics. Exposure to Absolute Maximum rating conditions for extended periods may affect device reliability.

#### **Recommended Operating Conditions**

| Parameter                     | Symbol | MIN. | TYP. | MAX. | Unit |

|-------------------------------|--------|------|------|------|------|

| Supply voltage                | Vcc    | 4.5  | 5.0  | 5.5  | ٧    |

| High level input voltage      | VIH    | 2.4  |      | 5.5  | ٧    |

| Low level input voltage       | VIL    | -1.0 |      | +0.8 | ٧    |

| Operating ambient temperature | Та     | 0    |      | 70   | °C   |

#### DC Characteristics 1 (Recommended operating conditions unless otherwise noted)

| Parameter                                    | Symbol          | Test conditions                                         | MIN. | TYP. | MAX. | Unit        |

|----------------------------------------------|-----------------|---------------------------------------------------------|------|------|------|-------------|

| Input leakage current                        | lı∟             | V <sub>IN</sub> = 0 V to 5.5 V,<br>Other inputs are 0 V | -10  |      | +10  | μΑ          |

| Output leakage current                       | loL             | W/IO, SIO, QSF are inactive,<br>Vout = 0 V to 5.5 V     | -10  |      | +10  | μΑ          |

| Random access port high level output voltage | <b>V</b> он (R) | lон (R) = −1.0mA                                        | 2.4  |      |      | <b>&gt;</b> |

| Random access port low level output voltage  | Vol (R)         | lo <sub>L</sub> (R) = 2.1mA                             |      |      | 0.4  | ٧           |

| Serial access port high level output voltage | Voн (S)         | lон (S) = −1.0mA                                        | 2.4  |      |      | ٧           |

| Serial access port low level output voltage  | Vol (S)         | loL (S) = 2.1mA                                         |      |      | 0.4  | V           |

## Capacitance (T<sub>A</sub> = 25 $^{\circ}$ C, f = 1MHz)

| Parameter                | Symbol | Test conditions                     |  | Test conditions MIN. TYP. |   | MAX. | Unit |

|--------------------------|--------|-------------------------------------|--|---------------------------|---|------|------|

| Input Capacitance        | Cıı    | RAS, CAS, WB/WE, DT/OE, DSF, SE, SC |  |                           | 8 | рF   |      |

|                          | C12    | A0 to A8                            |  |                           | 5 |      |      |

| Input/Output Capacitance | Сю     | W/IO (0 to 7), SIO (0 to 7)         |  |                           | 7 | рF   |      |

| Output Capacitance       | Со     | QSF                                 |  |                           | 7 | pF   |      |

# DC Characteristics 2 (Recommended operating conditions unless otherwise noted) $^{\text{Note 1}}$ ( $\mu$ PD482234)

|                                                           | Serial Acco | ess Port |                  | μPD48 | 2234-60 | μPD482234-70 |      |      |            |

|-----------------------------------------------------------|-------------|----------|------------------|-------|---------|--------------|------|------|------------|

| Random Access Port                                        | Standby     | Active   | Symbol           | MIN.  | MAX.    | MIN.         | MAX. | Unit | Conditions |

| Random Read/Write Cycle RAS, CAS cycle,                   | 0           |          | Icc <sub>1</sub> |       | 110     |              | 130  | mA   | Note 2     |

| tro = tro (MIN.), lo = 0mA                                |             | 0        | Icc7             |       | 155     |              | 195  |      |            |

| Standby RAS = CAS = V <sub>IH</sub> ,                     | 0           |          | Icc2             |       | 10      |              | 10   | mA   |            |

| Dout = high impedance                                     |             |          |                  |       | 1       |              | 1    | mA   | Note 3     |

|                                                           |             | 0        | Іссв             |       | 55      |              | 70   | mA   |            |

| RAS only refresh cycle RAS cycle, CAS = V <sub>IH</sub> , | 0           |          | Іссз             |       | 110     |              | 115  | mA   | Note 4     |

| trc = trc (MIN.)                                          |             | 0        | Icc9             |       | 155     |              | 180  |      |            |

| Fast page mode cycle RAS = VIL, CAS cycle,                | 0           |          | Icc4             |       | 100     |              | 100  | mA   | Note 5     |

| tpc = tpc (MIN.)                                          |             | 0        | Icc10            |       | 145     |              | 165  |      |            |

| CAS before RAS refresh cycle trc = trc (MIN.)             | 0           |          | Iccs             |       | 110     |              | 90   | mA   |            |

| the = the (MIIIV.)                                        |             | 0        | Icc11            |       | 155     |              | 155  |      |            |

| Data transfer cycle                                       | 0           |          | Icc6             |       | 120     |              | 140  | mA   |            |

| tac = tac (MIN.)                                          |             | 0        | loc12            |       | 165     |              | 205  |      |            |

| Color/Mask write register set cycle                       | 0           |          | ICC13            |       | 100     |              | 120  | mA   |            |

| tre = tre (MIN.)                                          |             | 0        | Icc14            |       | 145     |              | 185  |      |            |

| Flash write cycle                                         | 0           |          | loc15            |       | 100     |              | 120  | mA   |            |

| tre = tre (MIN.)                                          |             | 0        | Icc16            |       | 145     |              | 185  |      |            |

| Block write cycle                                         | 0           |          | loc17            |       | 120     |              | 130  | mA   |            |

| tre = tre (MIN.)                                          |             | 0        | Icc18            |       | 165     |              | 195  | 1    |            |

| Fast page mode block write cycle                          | 0           |          | Icc19            |       | 100     |              | 110  | mA   |            |

| tpc = tpc (MIN.)                                          |             | 0        | Icc20            |       | 130     |              | 175  |      | Note 5     |

- **Notes 1.** No load on W/IO, SIO, QSF. The current consumption actually used depends on the output load and operating frequency of each pin.

- 2. A change in row addresses must not occur more than once in tRC = tRC (MIN.).

- 3.  $\overline{RAS}$ ,  $\overline{CAS}$ , and  $\overline{SE}$  remain at  $V_{IH} \ge V_{CC} 0.2$  V, and A0 to A8,  $\overline{WB/WE}$ ,  $\overline{DT/OE}$ , DSF, SC remain at  $V_{IH} \ge V_{CC} 0.2$  V or  $V_{IL} \le GND + 0.2$  V.

- **4.** When the address input is set to  $V_{IH}$  or  $V_{IL}$  during the tras period.

- 5. Value when the address in tpc one cycle is changed once when tpc = tpc (MIN.).

# DC Characteristics 2 (Recommended operating conditions unless otherwise noted) $^{\text{Note 1}}$ ( $\mu$ PD482235)

|                                                           | Serial Acc | ess Port |        | μPD482 | 2235-60 | μPD482235-70 |      |      |            |

|-----------------------------------------------------------|------------|----------|--------|--------|---------|--------------|------|------|------------|

| Random Access Port                                        | Standby    | Active   | Symbol | MIN.   | MAX.    | MIN.         | MAX. | Unit | Conditions |

| Random Read/Write Cycle RAS, CAS cycle,                   | 0          |          | Icc1   |        | 110     |              | 130  | mA   | Note 2     |

| trc = trc (MIN.), lo = 0mA                                |            | 0        | Icc7   |        | 155     |              | 195  |      |            |

| Standby RAS = CAS = V <sub>IH</sub> ,                     | 0          |          | lcc2   |        | 10      |              | 10   | mA   |            |

| Dout = high impedance                                     |            |          |        |        | 1       |              | 1    | mA   | Note 3     |

|                                                           |            | 0        | Іссв   |        | 55      |              | 70   | mA   |            |

| RAS only refresh cycle RAS cycle, CAS = V <sub>IH</sub> , | 0          |          | Іссз   |        | 110     |              | 115  | mA   | Note 4     |

| trc = trc (MIN.)                                          |            | 0        | Icc9   |        | 155     |              | 180  |      |            |

| Hyper page mode cycle RAS = Vil, CAS cycle,               | 0          |          | Icc4   |        | 120     |              | 130  | mA   | Note 5     |

| the = the (MIN.)                                          |            | 0        | Icc10  |        | 155     |              | 195  |      |            |

| CAS before RAS refresh cycle trc = trc (MIN.)             | 0          |          | Іссь   |        | 110     |              | 90   | mA   |            |

| THE = THE (IMITY.)                                        |            | 0        | Icc11  |        | 155     |              | 155  |      |            |

| Data transfer cycle trc = trc (MIN.)                      | 0          |          | Icc6   |        | 120     |              | 140  | mA   |            |

| IRC = IRC (MIIN.)                                         |            | 0        | lcc12  |        | 165     |              | 205  |      |            |

| Color/Mask write register set cycle trc = trc (MIN.)      | 0          |          | Icc13  |        | 100     |              | 120  | mA   |            |

| THE = THE (MITN.)                                         |            | 0        | Icc14  |        | 145     |              | 185  |      |            |

| Flash write cycle                                         | 0          |          | Icc15  |        | 100     |              | 120  | mA   |            |

| trc = trc (MIN.)                                          |            | 0        | ICC16  |        | 145     |              | 185  |      |            |

| Block write cycle                                         | 0          |          | Icc17  |        | 120     |              | 130  | mA   |            |

| trc = trc (MIN.)                                          |            | 0        | ICC18  |        | 165     |              | 195  |      |            |

| Hyper page mode block write cycle thec = thec (MIN.)      | 0          |          | Icc19  |        | 140     |              | 135  | mA   |            |

| THPC = THPC (MITN.)                                       |            | 0        | Icc20  |        | 190     |              | 200  |      | Note 5     |

- **Notes 1.** No load on W/IO, SIO, QSF. The current consumption actually used depends on the output load and operating frequency of each pin.