#### AMI Semiconductor, Inc.

IMD - Medical Business Unit 670 North McCarthy Blvd. Suite 220 Milpitas, CA 95035 PH: 408-935-7777, FAX: 408-935-7770

### N256S0818HDA/N256S0830HDA Advance Information

# 256Kb Low Power Serial SRAMs

## 32K × 8 bit Organization

#### Overview

The AMI Semiconductor serial SRAM family includes several integrated memory devices including this 256Kb serially accessed Static Random Access Memory, internally organized as 32K words by 8 bits. The devices are designed and fabricated using AMI Semiconductor's advanced CMOS technology to provide both high-speed performance and low power. The devices operate with a single chip select (CS) input and use a simple Serial Peripheral Interface (SPI) serial bus. A single data in and data out line is used along with a clock to access data within the devices. The N256S08xxHDA devices include a HOLD pin that allows communication to the device to be paused. While paused, input transitions will be ignored. The devices can operate over a wide temperature range of -40°C to +85°C and can be available in several standard package offerings.

#### **Features**

- Power Supply Options 1.8V and 3.3V

- Very low standby current Typical Isb as low as 200nA

- Very low operating current As low as 3mA

- Simple memory control

Single chip select (CS)

Serial input (SI) and serial output (SO)

- Flexible operating modes

Word read and write

Page mode (32 word page)

Burst mode (full array)

- Organization 32K x 8 bit

- · Self timed write cycles

- · Built-in write protection (CS high)

- HOLD pin for pausing communication

- High reliability

Unlimited write cycles

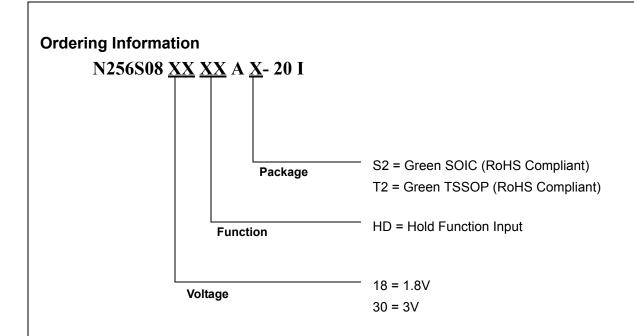

- RoHS Compliant Packages

Green SOIC and TSSOP

#### **Device Options**

| Part Number  | Density | Power<br>Supply (V) | Speed<br>(MHz) | Feature | Typical<br>Standby<br>Current | Read/Write<br>Operating Current |

|--------------|---------|---------------------|----------------|---------|-------------------------------|---------------------------------|

| N256S0818HDA | 256Kb   | 1.8                 | 20             | HOLD    | 200nA                         | 2 m / @ 1Mbz                    |

| N256S0830HDA | 250KD   | 3.0                 | 20             | HOLD    | 1uA                           | 3 mA @ 1Mhz                     |

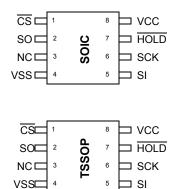

#### **Pin Names**

| Pin Name        | Pin Function       |

|-----------------|--------------------|

| CS              | Chip Select Input  |

| SCK             | Serial Clock Input |

| SI              | Serial Data Input  |

| SO              | Serial Data Output |

| HOLD            | Hold Input         |

| NC              | No Connect         |

| V <sub>CC</sub> | Power              |

| V <sub>SS</sub> | Ground             |

# **Package Configurations**

2

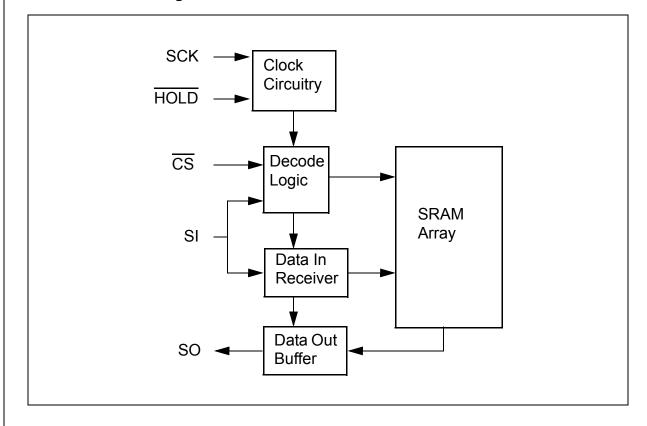

# **Functional Block Diagram**

# Absolute Maximum Ratings<sup>1</sup>

| Item                                            | Symbol              | Rating                       | Unit |

|-------------------------------------------------|---------------------|------------------------------|------|

| Voltage on any pin relative to V <sub>SS</sub>  | $V_{IN,OUT}$        | -0.3 to V <sub>CC</sub> +0.3 | V    |

| Voltage on $V_{CC}$ Supply Relative to $V_{SS}$ | V <sub>CC</sub>     | -0.3 to 4.5                  | V    |

| Power Dissipation                               | $P_{D}$             | 500                          | mW   |

| Storage Temperature                             | T <sub>STG</sub>    | -40 to 125                   | °C   |

| Operating Temperature                           | T <sub>A</sub>      | -40 to +85                   | °C   |

| Soldering Temperature and Time                  | T <sub>SOLDER</sub> | 260°C, 10sec                 | °C   |

Stresses greater than those listed above may cause permanent damage to the device. This is a stress rating only and functional

operation of the device at these or any other conditions above those indicated in the operating section of this specification is not

implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

# **Operating Characteristics (Over Specified Temperature Range)**

| Item                         | Symbol           | Test Conditions                                                                                   | Min.                  | Typ <sup>1</sup> | Max                  | Unit |

|------------------------------|------------------|---------------------------------------------------------------------------------------------------|-----------------------|------------------|----------------------|------|

| Supply Voltage               | V <sub>CC</sub>  | 1.8V Device                                                                                       | 1.7                   |                  | 1.95                 | V    |

| Supply Voltage               | V <sub>CC</sub>  | 3V Device                                                                                         | 2.7                   |                  | 3.6                  | ٧    |

| Input High Voltage           | V <sub>IH</sub>  |                                                                                                   | 0.7 x V <sub>CC</sub> |                  | V <sub>CC</sub> +0.3 | V    |

| Input Low Voltage            | $V_{IL}$         |                                                                                                   | -0.3                  |                  | 0.8                  | V    |

| Output High Voltage          | V <sub>OH</sub>  | I <sub>OH</sub> = -0.4mA                                                                          | V <sub>CC</sub> -0.5  |                  |                      | V    |

| Output Low Voltage           | V <sub>OL</sub>  | I <sub>OL</sub> = 1mA                                                                             |                       |                  | 0.2                  | V    |

| Input Leakage Current        | ILI              | $\overline{\text{CS}} = \text{V}_{\text{CC}}, \text{V}_{\text{IN}} = 0 \text{ to V}_{\text{CC}}$  |                       |                  | 0.5                  | μА   |

| Output Leakage Current       | I <sub>LO</sub>  | $\overline{\text{CS}} = \text{V}_{\text{CC}}, \text{V}_{\text{OUT}} = 0 \text{ to V}_{\text{CC}}$ |                       |                  | 0.5                  | μА   |

|                              | I <sub>CC1</sub> | F = 1MHz, I <sub>OUT</sub> = 0                                                                    |                       |                  | 3                    | mA   |

| Read/Write Operating Current | I <sub>CC2</sub> | F = 10MHz, I <sub>OUT</sub> = 0                                                                   |                       |                  | 6                    | mA   |

| Current                      | I <sub>CC3</sub> | F = 20MHz, I <sub>OUT</sub> = 0                                                                   |                       |                  | 10                   | mA   |

|                              |                  | 1.8V Device                                                                                       |                       | 200              | 500                  | nA   |

| Standby Current              | I <sub>SB</sub>  | $\overline{\text{CS}} = V_{\text{CC}}, V_{\text{IN}} = V_{\text{SS}} \text{ or } V_{\text{CC}}$   |                       |                  |                      |      |

| Standay Sanont               | .90              | $\frac{3V \text{ Device}}{CS} = V_{CC}, V_{IN} = V_{SS} \text{ or } V_{CC}$                       |                       | 1                | 4                    | μΑ   |

<sup>1.</sup> Typical values are measured at Vcc=Vcc Typ.,  $T_A$ =25°C and are not 100% tested.

# Capacitance<sup>1</sup>

| Item              | Symbol           | Test Condition                                         | Min | Max | Unit |

|-------------------|------------------|--------------------------------------------------------|-----|-----|------|

| Input Capacitance | C <sub>IN</sub>  | V <sub>IN</sub> = 0V, f = 1 MHz, T <sub>A</sub> = 25°C |     | 7   | pF   |

| I/O Capacitance   | C <sub>I/O</sub> | V <sub>IN</sub> = 0V, f = 1 MHz, T <sub>A</sub> = 25°C |     | 7   | pF   |

<sup>1.</sup> These parameters are verified in device characterization and are not 100% tested

Stock No. 23476-F

3

# **Timing Test Conditions**

| Item                                     |                                           |

|------------------------------------------|-------------------------------------------|

| Input Pulse Level                        | 0.1V <sub>CC</sub> to 0.9 V <sub>CC</sub> |

| Input Rise and Fall Time                 | 5ns                                       |

| Input and Output Timing Reference Levels | 0.5 V <sub>CC</sub>                       |

| Output Load                              | CL = 100pF                                |

| Operating Temperature                    | -40 to +85 °C                             |

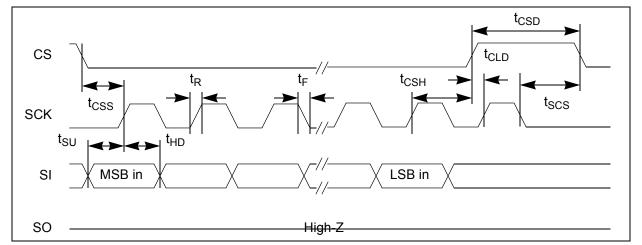

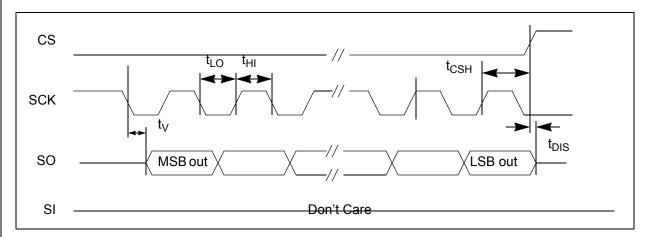

# **Timing**

| M                           | 0                | 1.8V I | Device | 3V D | evice | Units |

|-----------------------------|------------------|--------|--------|------|-------|-------|

| Item                        | Symbol           | Min.   | Max.   | Min. | Max.  | Units |

| Clock Frequency             | f <sub>CLK</sub> |        | 20     |      | 20    | MHz   |

| Clock Rise Time             | t <sub>R</sub>   |        | 2      |      | 2     | us    |

| Clock Fall Time             | t <sub>F</sub>   |        | 2      |      | 2     | us    |

| Clock High Time             | t <sub>HI</sub>  | 25     |        | 25   |       | ns    |

| Clock Low Time              | t <sub>LO</sub>  | 25     |        | 25   |       | ns    |

| Clock Delay Time            | t <sub>CLD</sub> | 25     |        | 25   |       | ns    |

| CS Setup Time               | t <sub>CSS</sub> | 25     |        | 25   |       | ns    |

| CS Hold Time                | t <sub>CSH</sub> | 50     |        | 50   |       | ns    |

| CS Disable Time             | t <sub>CSD</sub> | 25     |        | 25   |       | ns    |

| SCK to CS                   | t <sub>SCS</sub> | 5      |        | 5    |       | ns    |

| Data Setup Time             | t <sub>SU</sub>  | 10     |        | 10   |       | ns    |

| Data Hold Time              | t <sub>HD</sub>  | 10     |        | 10   |       | ns    |

| Output Valid From Clock Low | t <sub>V</sub>   |        | 25     |      | 25    | ns    |

| Output Hold Time            | t <sub>HO</sub>  | 0      |        | 0    |       | ns    |

| Output Disable Time         | t <sub>DIS</sub> |        | 20     |      | 20    | ns    |

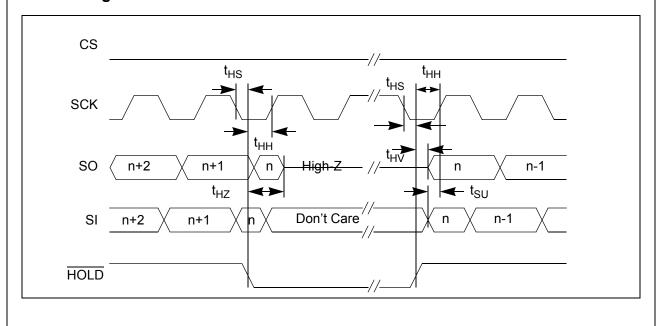

| HOLD Setup Time             | t <sub>HS</sub>  | 10     |        | 10   |       | ns    |

| HOLD Hold Time              | t <sub>HH</sub>  | 10     |        | 10   |       | ns    |

| HOLD Low to Output High-Z   | t <sub>HZ</sub>  | 10     |        | 10   |       | ns    |

| HOLD High to Output Valid   | t <sub>HV</sub>  |        | 50     |      | 50    | ns    |

# **Serial Input Timing**

## **Serial Output Timing**

# **Hold Timing**

### **Control Signal Descriptions**

| Signal | Name            | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------|-----------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CS     | Chip Select     | I   | A low level selects the device and a high level puts the device in standby mode. If $\overline{CS}$ is brought high during a program cycle, the cycle will complete and then the device will enter standby mode. When $\overline{CS}$ is high, SO is in high-Z. $\overline{CS}$ must be driven low after power-up prior to any sequence being started.                                                                                                                                                                                                                                                                                                           |

| SCK    | Serial Clock    |     | Synchronizes all activities between the memory and controller. All incoming addresses, data and instructions are latched on the rising edge of SCK. Data out is updated on SO after the falling edge of SCK.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| SI     | Serial Data In  |     | Receives instructions, addresses and data on the rising edge of SCK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| SO     | Serial Data Out | 0   | Data is transferred out after the falling edge of SCK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| HOLD   | Hold            |     | A high level is required for normal operation. Once the device is selected and a serial sequence is started, this input may be taken low to pause serial communication without resetting the serial sequence. The pin must be brought low while SCK is low for immediate use. If SCK is not low, the Hold function will not be invoked until the next SCK high to low transition. The device must remain selected during this sequence. SO is high-Z during the Hold time and SI and SCK are inputs are ignored. To resume operations, HOLD must be pulled high while the SCK pin is low.  Lowering the HOLD input at any time will take to SO output to High-Z. |

### **Functional Operation**

#### **Basic Operation**

The 256Kb serial SRAM is designed to interface directly with a standard Serial Peripheral Interface (SPI) common on many standard micro-controllers. It may also interface with other non-SPI ports by programming discrete I/O lines to operate the device.

The serial SRAM contains an 8-bit instruction register and is accessed via the SI pin. The  $\overline{CS}$  pin must be low and the  $\overline{HOLD}$  pin must be high for the entire operation. Data is sampled on the first rising edge of SCK after  $\overline{CS}$  goes low. If the clock line is shared, the user can assert the  $\overline{HOLD}$  input and place the device into a Hold mode. After releasing the  $\overline{HOLD}$  pin, the operation will resume from the point where it was held.

The following table contains the possible instructions and formats. All instructions, addresses and data are transferred MSB first and LSB last.

#### Instruction Set

| Instruction | Instruction Format | Description                                        |

|-------------|--------------------|----------------------------------------------------|

| READ        | 0000 0011          | Read data from memory starting at selected address |

| WRITE       | 0000 0010          | Write data to memory starting at selected address  |

| RDSR        | 0000 0101          | Read status register                               |

| WRSR        | 0000 0001          | Write status register                              |

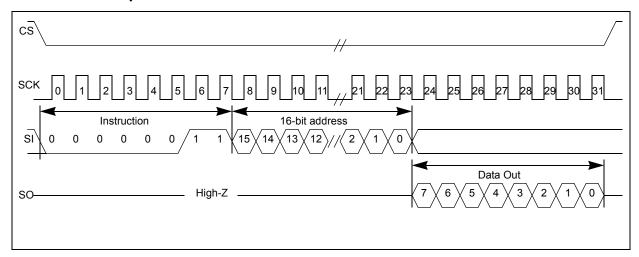

#### **READ Operations**

The serial SRAM READ is selected by enabling  $\overline{CS}$  low. First, the 8-bit READ instruction is transmitted to the device followed by the 16-bit address with the MSB being a don't care. After the READ instruction and addresses are sent, the data stored at that address in memory is shifted out on the SO pin after the output valid time from the clock edge.

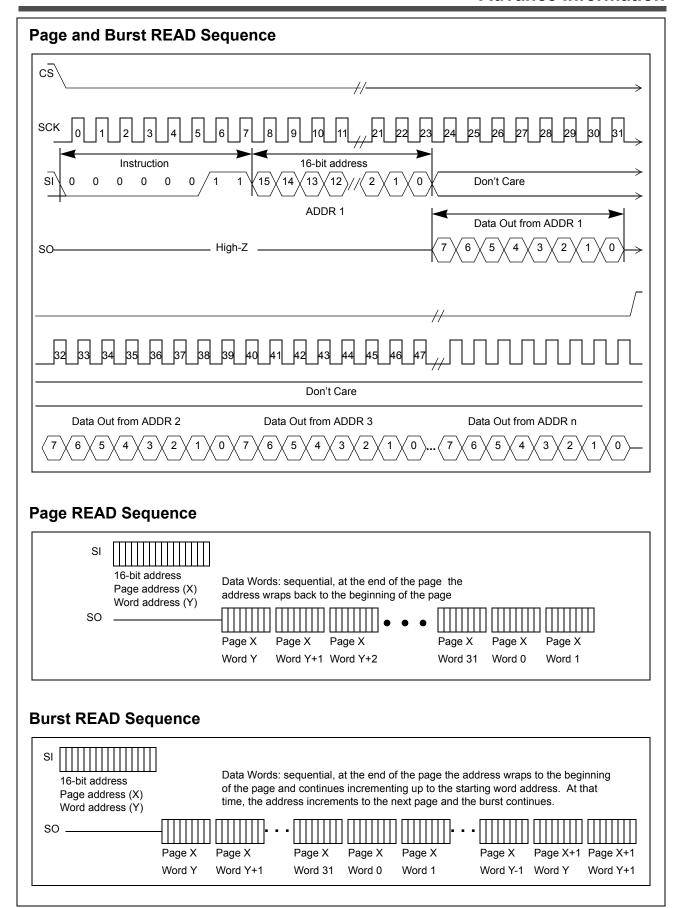

If operating in page mode, after the initial word of data is shifted out, the data stored at the next memory location on the page can be read sequentially by continuing to provide clock pulses. The internal address pointer is automatically incremented to the next higher address on the page after each word of data is read out. This can be continued for the entire page length of 32 words long. At the end of the page, the addresses pointer will be wrapped to the 0 word address within the page and the operation can be continuously looped over the 32 words of the same page.

If operating in burst mode, after the initial word of data is shifted out, the data stored at the next memory location can be read sequentially by continuing to provide clock pulses. The internal address pointer is automatically incremented to the next higher address after each word of data is read out. This can be continued for the entire array and when the highest address is reached (7FFFh), the address counter wraps to the address 0000h. This allows the burst read cycle to be continued indefinitely.

All READ operations are terminated by pulling  $\overline{\text{CS}}$  high.

#### **Word READ Sequence**

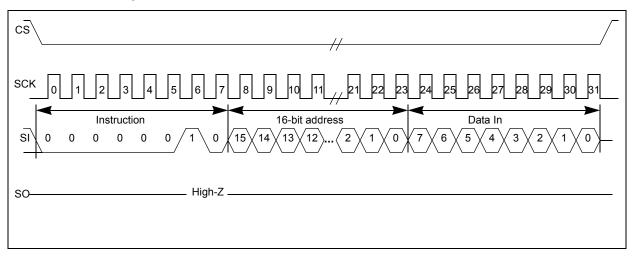

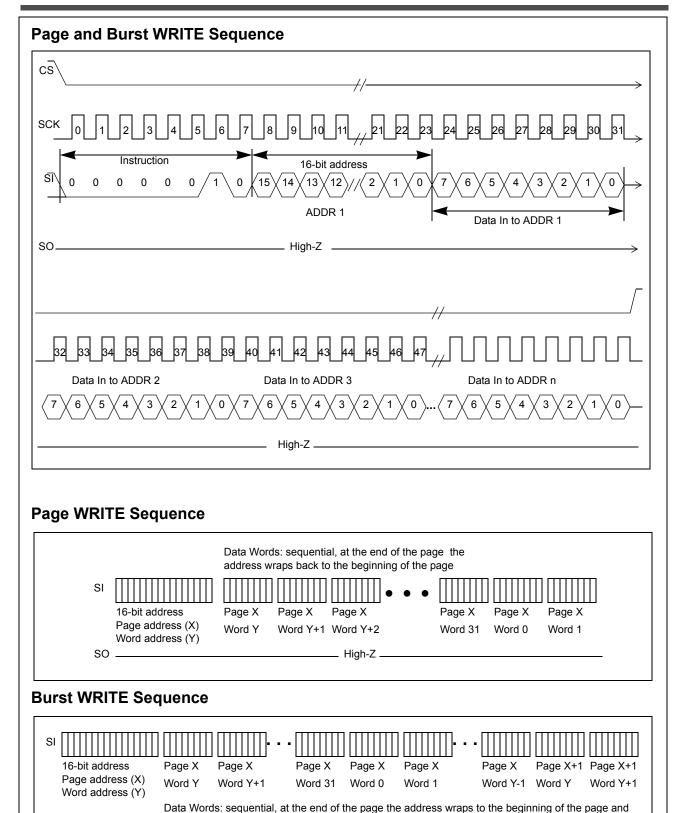

#### **WRITE Operations**

The serial SRAM WRITE is selected by enabling  $\overline{\text{CS}}$  low. First, the 8-bit WRITE instruction is transmitted to the device followed by the 16-bit address with the MSB being a don't care. After the WRITE instruction and addresses are sent, the data to be stored in memory is shifted in on the SI pin.

If operating in page mode, after the initial word of data is shifted in, additional data words can be written as long as the address requested is sequential on the same page. Simply write the data on SI pin and continue to provide clock pulses. The internal address pointer is automatically incremented to the next higher address on the page after each word of data is written in. This can be continued for the entire page length of 32 words long. At the end of the page, the addresses pointer will be wrapped to the 0 word address within the page and the operation can be continuously looped over the 32 words of the same page. The new data will replace data already stored in the memory locations.

If operating in burst mode, after the initial word of data is shifted in, additional data words can be written to the next sequential memory locations by continuing to provide clock pulses. The internal address pointer is automatically incremented to the next higher address after each word of data is read out. This can be continued for the entire array and when the highest address is reached (7FFFh), the address counter wraps to the address 0000h. This allows the burst write cycle to be continued indefinitely. Again, the new data will replace data already stored in the memory locations.

All WRITE operations are terminated by pulling  $\overline{\text{CS}}$  high.

### **Word WRITE Sequence**

continues incrementing up to the starting word address. At that time, the address increments to the

\_\_\_\_\_ High-Z \_\_\_

next page and the burst continues.

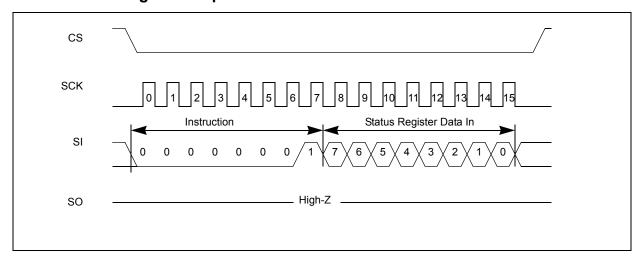

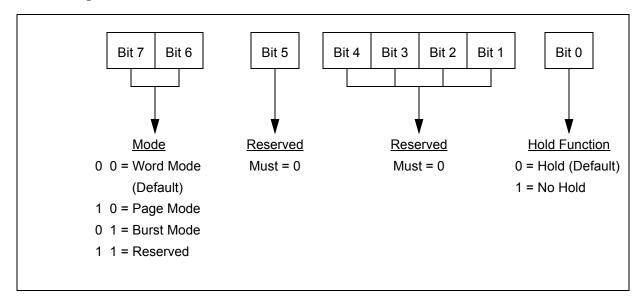

### **WRITE Status Register Instruction (WRSR)**

This instruction provides the ability to write the status register and select among several operating modes. Several of the register bits must be set to a low '0' if any of the other bits are written. The timing sequence to write to the status register is shown below, followed by the organization of the status register.

#### **WRITE Status Register Sequence**

### **Status Register**

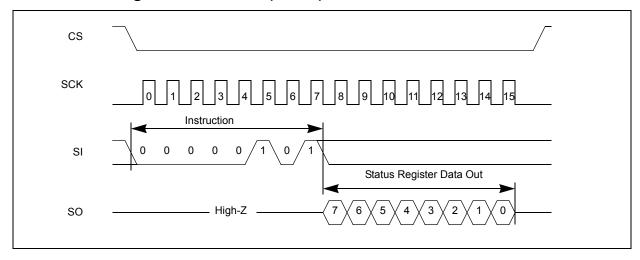

### **READ Status Register Instruction (RDSR)**

This instruction provides the ability to read the Status register. The register may be read at any time by performing the following timing sequence.

#### **READ Status Register Instruction (RDSR)**

# **Power-Up State**

The serial SRAM enters a know state at power-up time. The device is in low-power standby state with  $\overline{CS}$  = 1. A low level on  $\overline{CS}$  is required to enter a active state.

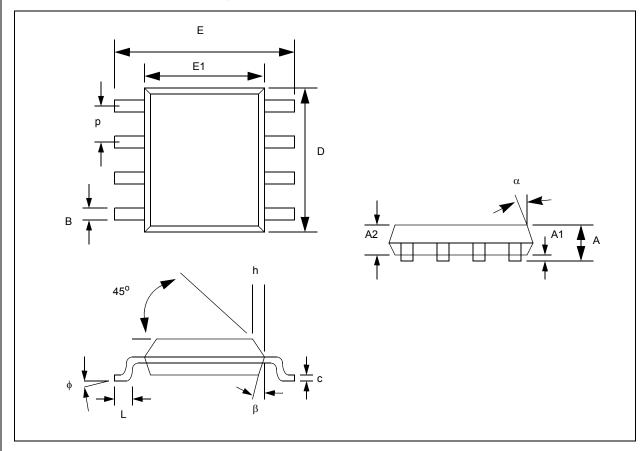

# 8-Lead Plastic Small Outline, 150mil SOIC

| Parameter                | Sym | Min  | Nom  | Max  |

|--------------------------|-----|------|------|------|

| Pin Pitch                | р   |      | 1.27 |      |

| Overall height           | Α   | 1.35 | 1.55 | 1.75 |

| Molded Package Thickness | A2  | 1.32 | 1.42 | 1.55 |

| Standoff                 | A1  | 0.10 | 0.18 | 0.25 |

| Overall Width            | E   | 5.79 | 6.02 | 6.20 |

| Molded Package Width     | E1  | 3.71 | 3.91 | 3.99 |

| Overall Length           | D   | 4.80 | 4.90 | 5.00 |

| Chamfer Distance         | h   | 0.25 | 0.38 | 0.51 |

| Foot Length              | L   | 0.48 | 0.62 | 0.76 |

| Foot Angle               | ф   | 0    | 4    | 8    |

| Lead Thickness           | С   | 0.20 | 0.23 | 0.25 |

| Lead Width               | В   | 0.33 | 0.42 | 0.51 |

| Mold Draft Angle Top     | α   | 0    | 12   | 15   |

| Mold Draft Angle Bottom  | β   | 0    | 12   | 15   |

#### Note:

- 1. All dimensions in Millimeters

- 2. Package dimensions exclude mold flash and protusions.

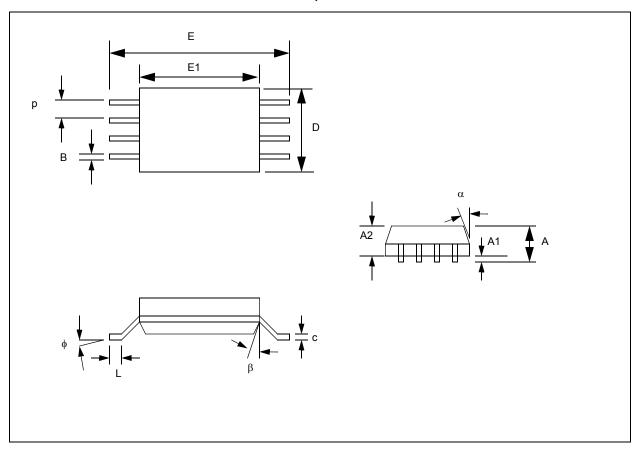

# 8-Lead Plastic Thin Shrink Small Outline, 4.4 mm TSSOP

| Parameter                | Sym | Min  | Nom  | Max  |

|--------------------------|-----|------|------|------|

| Pin Pitch                | р   |      | 0.65 |      |

| Overall height           | Α   |      |      | 1.10 |

| Molded Package Thickness | A2  | 0.85 | 0.90 | 0.95 |

| Standoff                 | A1  | 0.05 | 0.10 | 0.15 |

| Overall Width            | E   | 6.25 | 6.38 | 6.50 |

| Molded Package Width     | E1  | 4.30 | 4.40 | 4.50 |

| Overall Length           | D   | 2.90 | 3.00 | 3.10 |

| Foot Length              | L   | 0.50 | 0.60 | 0.70 |

| Foot Angle               | ф   | 0    | 4    | 8    |

| Lead Thickness           | С   | 0.09 | 0.15 | 0.20 |

| Lead Width               | В   | 0.19 | 0.25 | 0.30 |

| Mold Draft Angle Top     | α   | 0    | 5    | 10   |

| Mold Draft Angle Bottom  | β   | 0    | 5    | 10   |

- 1. All dimensions in Millimeters

- 2. Package dimensions exclude mold flash and protusions.

Stock No. 23476-F The specification is ADVANCE INFORMATION and subject to change without notice.

### **Revision History**

| Revision # | Date           | Change Description                                                         |

|------------|----------------|----------------------------------------------------------------------------|

| Α          | October 2005   | Initial advance release                                                    |

| В          | January 2006   | Separated density, removed write protection and added page and burst modes |

| С          | January 2006   | Changed packages to green type                                             |

| D          | January 2006   | Changed TSSOP pinout to match SOIC                                         |

| E          | September 2006 | Split x8 and x16 devices<br>Converted to AMI Semiconductor                 |

| F          | May 2007       | Updated DC parameters                                                      |

© 2006-2007 AMI Semiconductor, Inc. All rights reserved.

AMI Semiconductor, Inc. ("AMIS") reserves the right to change or modify the information contained in this data sheet and the products described therein, without prior notice. AMIS does not convey any license under its patent rights nor the rights of others. Charts, drawings and schedules contained in this data sheet are provided for illustration purposes only and they vary depending upon specific applications.

AMIS makes no warranty or guarantee regarding suitability of these products for any particular purpose, nor does AMIS assume any liability arising out of the application or use of any product or circuit described herein. AMIS does not authorize use of its products as critical components in any application in which the failure of the AMIS product may be expected to result in significant injury or death, including life support systems and critical medical instruments.