#### Universal Active Filter

#### Features

| • | industry | Standard | Pinout |

|---|----------|----------|--------|

|   |          |          |        |

- Clock to Center Frequency Ratio Accuracy ±2%

- Filter Cutoff Frequency Stability Directly Dependent on External Clock Quality

- Separate High-pass (or Notch or All-Pass), Band-Pass, Low-pass Outputs

- . fo x Q Range up to 50kHz Minimum

- Operates to f<sub>Q</sub> = 20KHz Minimum

- Specifications Guaranteed for T<sub>A</sub> from -55°C to +125°C

## **Applications**

- General Purpose Audio-Band Filtering

- · Real-Time Programming

- ► Prototyping ► Dynamic Reconfiguration

- High Q Applications

- Precision Filtering at Low Q

- Precision Oscillators

- Extended Temperature

- · Voice Response Systems

- ► Modems ► Tone Generators

Filters (Directly Cascadable)

Data Acquisition SystemsBuilding Block for Precision Higher-Order

#### Description

The HF-10 consists of two fully independent second order switched capacitor CMOS filter sections. Each second order section is a modified state-variable filter. In each section there are three operational amplifiers and an additional "summing node". The extra summing node is a direct benefit of the switched capacitor design approach. This provides increased versatility as compared to the classical continuous-time active filter. The transfer function of each section is tailored by the user's choice of feedback configuration, external resistor values, and external clock rate.

The HF-10 topology is very useful since it produces three different, but related, transfer functions simultaneously. Each transfer function has the same pole locations but different zero locations. One of the outputs is either a notch, all-pass, or high-pass signal, depending on the feedback configuration chosen by the user; the other outputs are band-pass and low-pass signals. The center frequency of the complex pole pair, f<sub>0</sub>, is determined by the external clock frequency and the state of the "50-100 CL" input. This value can also be scaled by a function of the external resistor values depending on the feedback configuration. The other important filter characteristics, such as gain, Q, etc. are determined by functions of external resistor values. Any of the classical filter configurations (Butterworth, Bessel, Cauer Elliptic, Chebyshey, etc.) can be realized.

The second order sections can be used separately with the constraint that the clock input for each section be driven by signals of the same level (i.e., either TTL or CMOS logic levels), and that the two clock signals share the same digital ground. If it is desired that a fourth order function be realized, the two sections can be cascaded. The "L Sh" (level shift) input is used in conjunction with the clock inputs to allow compatibility with either TTL or CMOS clock levels.

The HF-10 can be powered-down by connecting the " $50/100 \cdot \text{CL}$ " input to V<sub>D</sub>-. This disables the reference current generators for the operational amplifiers and the clock level shifters.

The HF-10 provides a number of advantages over other universal active filters: higher accuracy at frequency extremes; superior clock feedthrough supression: significantly lower crosstalk, better performance over -55°C to +125°C; drives smaller impedance to higher peak output voltage, and capable of precision oscillator applications (phase is continuous when frequency is changed).

The device is available in a 20 pin ceramic package with temperature ranges of 0°C to +75°C and -55°C to +125°C. Application Note 578 is available

#### **Pinout** TOP VIEW LPA [ 20 🗖 LPB 19 **5** BPB BPA 🗆 N AP HPA 3 18 N. AP-HPB INVA 4 17 NVB HF-ID 16 5 SIB [UAF] 15 AGND SA-B VA+ VD+ [ 13 🗖 VD-LSn [ 12 🗖 50-100-CL 1) CLKB CLK. [

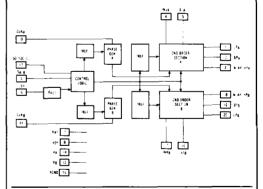

## System Block Diagram

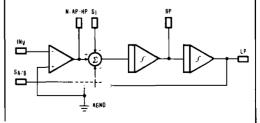

## Filter Block Diagram

# Absolute Maximum Ratings

| A DOOLATO MAXIMAN MANAGO              |                                   |

|---------------------------------------|-----------------------------------|

| Supply Voltages                       | Operating Temperature Ranges      |

| Power Dissipation 300mW               | HF-10-2, -855°C to +125°C         |

| Lead Temperature (Soldering, 10 Sec.) | HF-10-5, -70°C to +75°C           |

| Output Loading                        | HF-10-940°C to +85°C              |

| CLOAD <100pF                          | Storage Temperature65°C to +150°C |

| Junction Temperature 175°C            |                                   |

Specifications HF-10

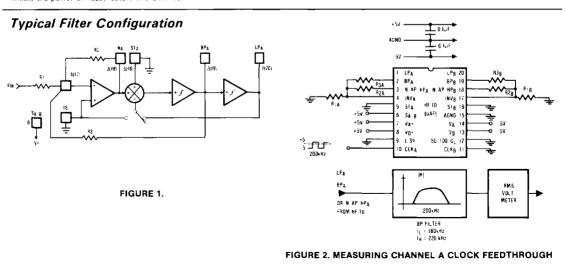

## **Electrical Specifications** (Complete Filter) $\pm 4.5 \text{V} < \text{V}_{\text{S}} < \pm 5.5 \text{V}$ , (Note 1) Refer to Figure 1.

| PARAMETER                              | CONDITIONS                                                                                | MIN | TYP | МАХ         | UNITS  |

|----------------------------------------|-------------------------------------------------------------------------------------------|-----|-----|-------------|--------|

| Frequency Range                        | f <sub>O</sub> XQ < 50kHz                                                                 | 50  |     | 20 <b>K</b> | Hz     |

| Clock to Center Frequency              |                                                                                           | ļ   | ļ   | l .         |        |

| Ratio                                  |                                                                                           |     |     |             |        |

| f <sub>CLK</sub> /f <sub>O</sub> = 50  | Pin 12 - V <sub>D</sub> +, Q = 10                                                         | 1   |     | =2%         |        |

| <b>32</b> 3                            | $f_0 XQ < 50 \text{kHz}$                                                                  | 1   |     |             |        |

| f <sub>CLK</sub> /f <sub>o</sub> = 100 | Pin 12 = AGND, Q = 10                                                                     |     |     | ±2%         |        |

| <b>52</b> /1 5                         | $f_{\Omega} XQ < 50 \text{kHz}$                                                           |     |     |             |        |

| Q Range                                | $f_0 XQ < 50 \text{kHz}$                                                                  | 0.5 |     | 100         |        |

| Q Accuracy (Q Deviation from           |                                                                                           | 1   | ł   |             |        |

| an Ideal Continuous Filter)            |                                                                                           | 1   |     |             |        |

| fCl K/fo = 50                          | Pin 12 = $V_D^+$ , $Q \le 20$                                                             | 1   | 1   | ±40,0       |        |

| 02                                     | $f_0 XQ < 50 kHz$                                                                         | 1   |     |             | 1      |

| f <sub>CLK</sub> /f <sub>0</sub> = 100 | Pin 12 = AGND, Q ≤ 20                                                                     |     |     | ±3%         |        |

| 02.11                                  | $f_0 XQ < 50 \text{kHz}$                                                                  | 1   | 1   | 1           |        |

| fo XQ Product                          |                                                                                           | 50K |     | ł           | Hz     |

| fo Temperature Coefficient             |                                                                                           |     |     |             |        |

| fCLK/fo = 50                           | T <sub>A</sub> = 25°C                                                                     |     |     | ±100        | ppm/OC |

| 02.1. 0                                | Pin 12 = $V_D$ +, $f_O$ XQ $<$ 50kHz                                                      |     |     |             |        |

|                                        | External Clock Temperature Independent                                                    |     |     |             |        |

| f <sub>CLK</sub> /f <sub>o</sub> = 100 | Pin 12 = AGND, f <sub>O</sub> XQ < 50kHz                                                  |     | ì   | ±100        | ppm/00 |

| OZIV O                                 | External Clock Temperature Independent                                                    |     |     |             |        |

| Q Temperature Coefficient              | T <sub>A</sub> = 25°C                                                                     |     |     | ±500        | ppm/00 |

| •                                      | f <sub>O</sub> XQ < 50kz, Q Setting                                                       |     | l   |             |        |

|                                        | Resistors Temperature Independent                                                         |     |     |             |        |

| Crosstalk                              | INVA - 0dBm @ 1kHz                                                                        |     | -60 |             | ₫B     |

|                                        | INV <sub>B</sub> = 0V                                                                     |     |     |             |        |

| Clock Feedthrough                      | See Figure 2                                                                              |     | 2   | 5           | mVrms  |

| Clock Frequency                        | Min @ f <sub>CLK</sub> /f <sub>0</sub> = 50, Max @ f <sub>CLK</sub> /f <sub>0</sub> = 100 | 2.5 |     | 2048        | kHz    |

| Power Supply Current                   | T <sub>A</sub> = 25°C                                                                     |     | 13  |             | mA     |

| Standby Current                        | Pin 12 = V <sub>A</sub> -                                                                 |     | 500 | l           | μA     |

## $\textbf{Electrical Specifications} \qquad \text{(Internal Operational Amplifiers)} \\ \pm 4.5 \text{V} < \text{V}_{\text{S}} < \pm 5.5 \text{V}, \text{(Note 1) Refer to Figure 1} \\$

| PARAMETER                                | CONDITIONS                | MIN  | TYP | MAX | UNITS |

|------------------------------------------|---------------------------|------|-----|-----|-------|

| Voltage Swing (Pins 1, 2, 3, 18, 19, 20) | R <sub>LOAD</sub> - 3.5KΩ | ±3.5 | _   |     | v     |

| Op Amp Gain-BW Product                   |                           | 2 5  | 3.8 |     | MHz   |

| Op Amp Slew Rate                         |                           | 5    | 15  | l   | V.μs  |

| Power Supply Rejection Ratio (PSRR)      | DC Only                   | 40   | ı   |     | dB    |

NOTE 1. Unless Otherwise Specified, typical parameters are at \*25°C, min-max parameters are over operating temperature range.

## Die Characteristics

| Transistor Count       |               | 464           |

|------------------------|---------------|---------------|

| Die Dimensions88       |               | 88 x 127      |

| Substrate Potential    |               | +V            |

| Process                | S             | SAJI CMOS     |

| Thermal Constants (°C) | $\theta_{ja}$ | $\theta_{jC}$ |

| Ceramic DIP            | 81            | 24            |

| Ceramic LCC            | 76            | 19            |

## Pin Assignments

| SYMBOL                              | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LP. BP.<br>N/AP/HP (A or B)         | Low-pass, band-pass, notch or all-pass or high-pass outputs of each second order section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| INV (A or B)                        | Inverting input of the summing op amp of each filter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| S1 (A or B)                         | Inverting summing input pin used in most filter configurations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| S <sub>A/B</sub>                    | Activates a switch connecting one of the inputs of the filter's second summer to either analog ground $(S_{A/B}$ low to $V_{A^+})$ or to the low-pass output of the circuit $(S_{A/B}$ high to $V_{A^+})$ . This allows flexibility in the various modes of operation of the 1. C.                                                                                                                                                                                                                                                                                                                                                                                                              |

| VA+, VD+*                           | Analog positive supply and digital positive supply. These pins are internally connected through the I.C. substrate and therefore, V <sub>A</sub> + and V <sub>D</sub> + should be derived from the same power supply source. They have been brought out separately so they can be bypassed by separate capacitors, if desired. They can be externally tied together and bypassed by a single capacitor.                                                                                                                                                                                                                                                                                         |

| ν <sub>Α</sub> -, ν <sub>D</sub> -* | Analog and digital negative supply, respectively. The same comments as for $V_A^+$ , $V_D^+$ apply here, except $V_{A^-}$ and $V_{D^-}$ are not tied together internally.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| L Sh                                | Level shift pin. Accommodates various clock levels with dual or single supply operation. With dual ±5V supplies, the HF-10 can be driven with CMOS clock levels (±5V), and the "L Sh" pin should be tied either to the system ground or to the negative supply pin. If the same supplies as above are used and TTL clock levels, derived from a 0V to 5V supply, are used, the "L Sh" pin should be tied to the system ground. For single supply operation (0V and 10V), the VD- and VA- pins should be connected to the system ground, the AGND pin should be biased at 5V, and the "L Sh" pin should also be tied to the system ground. This will accommodate both CMOS and TTL clock levels. |

| CLK (A or B)                        | Clock inputs for each switched capacitor filter building block. Should both be of the same level (TTL or CMOS). The level shift (L Sh) pin description discusses how to accommodate their levels. The duty cycle of the clock should preferably be close to 50%, especially when clock frequencies above 200kHz are used. This allows the maximum time for the op amps to settle, yielding optimum filter operation.                                                                                                                                                                                                                                                                            |

| 50/100/CL                           | By tying this pin to $V_D$ +, a 50:1 clock to filter center frequency operation is obtained. Tying at mid-supplies (i.e., analog ground with dual supplies) allows the filter to operate at a 100:1 clock to center frequency ratio. When field to $VD$ -, a simple current limiting circuit is triggered to limit the overall supply current. The filtering action is then aborted. This pin also acts as a power up reset when pulled to $V_D$ - after power is applied.                                                                                                                                                                                                                      |

| AGND                                | Analog ground pin. Should be connected to the system ground for dual supply operation or biased at mid-<br>supply for single supply operation. The Non-inverting inputs of the filter op amps are connected to the<br>AGND pin so a "clean" ground is mandatory.                                                                                                                                                                                                                                                                                                                                                                                                                                |

NOTE: All pins are protected against static discharge

'To initiate the internal power-on reset feature of the HF-10, V\* and V- should be brought up at the same time, or V- should be brought up first. An alternative to power supply sequencing is to strobe Pin 12 (50, 100, CL) to V- after power is applied, regardless of power supply sequencing. This will also initiate the power-on reset feature of the HF-10.