FOR DETAILED INFORMATION SEE THE LATEST ISSUE OF HANDBOOK ICOG OR DATA SHEET

# PHASE-LOCKED-LOOP WITH LOCK DETECTOR

## **FEATURES**

- Low power consumption

- Centre frequency up to 17 MHz (typ.) at V<sub>CC</sub> = 4.5. V

- Choice of two phase comparators: EXCLUSIVE-OR; edge-triggered JK flip-flop;

- Excellent VCO frequency linearity

- VCO-inhibit control for ON/OFF keying and for low standby power consumption

- Minimal frequency drift

- Operation power supply voltage range:

VCO section 3.0 to 6.0 V digital section 2.0 to 6.0 V

- Zero voltage offset due to op-amp buffering

- · Output capability: standard

- I<sub>CC</sub> category: MSI

| SYMBOL         | PARAMETER                                 | CONDITIONS                                       | TYPICAL |     | UNIT |

|----------------|-------------------------------------------|--------------------------------------------------|---------|-----|------|

|                |                                           |                                                  | нс      | нст | UNII |

| f <sub>o</sub> | VCO centre frequency                      | C1 = 40 pF<br>R1 = 3 kΩ<br>V <sub>CC</sub> = 5 V | 19      | 19  | MHz  |

| Cl             | input capacitance (pin 5)                 |                                                  | 3.5     | 3.5 | pF   |

| CPD            | power dissipation capacitance per package | notes 1 and 2                                    | 24      | 24  | рF   |

GND = 0 V; T<sub>amb</sub> = 25 °C

### Note

- 1. Applies to the phase comparator section only (VCO disabled).

For power dissipation of VCO and demodulator sections see Figs 20, 21 and 22.

- 2. CpD is used to determine the dynamic power dissipation (PD in  $\mu$ W):

$P_D = C_{PD} \times V_{CC}^2 \times f_i + \Sigma (C_L \times V_{CC}^2 \times f_o)$  where:

$f_i$  = input frequency in MHz  $f_0$  = output frequency in MHz

**PACKAGE OUTLINES**

$f_0$  = output frequency in irriz  $\Sigma (C_L \times V_{CC}^2 \times f_0)$  = sum of outputs

16-lead DIL; plastic (SOT38CP). 16-lead mini-pack; plastic (SO16; SOT109 A). CL = output load capacitance in pF

VCC = supply voltage in V

**GENERAL DESCRIPTION**

The 74HC/HCT7046 are high-speed Si-gate CMOS devices and are specified in compliance with JEDEC standard no. 7.

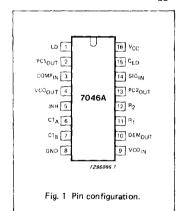

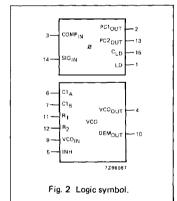

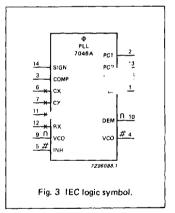

The 74HC/HCT7046 are phase-locked-loop circuits that comprise a linear voltage-controlled oscillator (VCO) and two different phase comparators (PC1 and PC2) with a common signal input amplifier and a common comparator input.

A lock detector is provided and this gives a HIGH level at pin 1 (LD) when the PLL is locked. The lock detector capacitor must be connected between pin 15 (CLD)

and pin 8 (GND). The value of the C<sub>LD</sub> capacitor can be determined, using information supplied in Fig. 32. The input signal can be directly coupled to large voltage signals, or indirectly coupled (with a series capacitor) to small voltage signals. A self-bias input circuit keeps small voltage signals within the linear region of the input amplifiers. With a passive low-pass filter, the "7046" forms a second-order loop PLL. The excellent VCO linearity is achieved by the use of linear op-amp techniques. (continued on next page)

# APPLICATIONS

- FM modulation and demodulation

- Frequency synthesis and multiplication

- Frequency discrimination

- Tone decoding

- Data synchronization and conditioning

- Voltage-to-frequency conversion

- Motor-speed control