# MA7001 RADIATION HARD 512 x 9 BIT FIFO

The MA7001 512 x 9 FIFO is manufactured using GPS's CMOS-SOS high performance, radiation hard,  $3\mu m$  technology.

The GPS Silicon-on-Sapphire process provides significant advantages over bulk silicon substrate technologies in addition to very good total dose hardness and neutron hardness >1015n/cm², the GPS technology provides very high transient gamma and single event upset performance without compromising speed of operation The Sapphire substrate also eliminates latch-up giving greater flexibility of use in electrically severe environments.

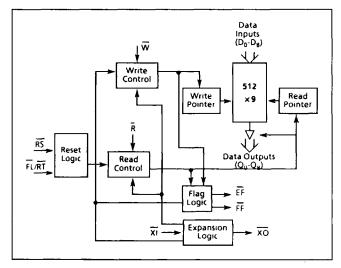

The MA7001 implements a First-In First-Out algorithm that reads and writes data on a first-in first-out basis. The dual-port static RAM memory is organised as 512 words of 9 bits (8 bit data and 1 bit for parity or control purposes).

Sequential read and write accesses are achieved using a ring pointer architecture that requires no external addressing information. Data is toggled in and out of the device by using the WRITE  $(\overline{W})$  and READ  $(\overline{R})$  pins.

Full and Empty status flags prevent data overflow and underflow. Expansion logic on the device allows for unlimited expansion capability in both word size and depth. A RETRANSMIT (RT) feature allows for reset of the read pointer to its initial position to allow retransmission of data.

The device is designed for applications requiring asynchronous and simultaneous read/write in multiprocessing and rate buffering (sourcing and sinking data at different rates eg. interfacing fast processors and slow peripherals).

#### **FEATURES**

- Radiation Hard CMOS-SOS Technology

- Fast Access Time 60ns Typical

- Single 5V Supply

- Inputs Fully TTL and CMOS Compatible

- -55°C to +125°C Operation

Figure 1: Block Diagram

#### DC CHARACTERISTICS AND RATINGS

| Symbol          | Parameter             | Min. | Max.                 | Units |

|-----------------|-----------------------|------|----------------------|-------|

| V <sub>DD</sub> | Supply Voltage        | -0.5 | 7.0                  | ν     |

| V <sub>IN</sub> | Input Voltage         | -0.3 | V <sub>DD</sub> +0.3 | V     |

| TA              | Operating Temperature | 55   | 125                  | ∘c    |

| Ts              | Storage Temperature   | -65  | 150                  | •c    |

Figure 2: Absolute Maximum Ratings

Stresses above those listed may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these conditions, or at any other condition above those indicated in the operations section of this specification, is not Implied Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

The following D.C. and A.C. electrical characteristics apply to pre-radiation at  $T_A$  = -55°C to +125°C,  $V_{DD}$  = 5V ±10% and post 100kRad(Si) total dose radiation at  $T_A$  = 25°C,  $V_{DD}$  = 5V ±10%. GROUP A SUBGROUP 1, 2, 3.

| Symbol              | Parameter                                             | Conditions                                                                             | Min. | Тур. | Max. | Unit |

|---------------------|-------------------------------------------------------|----------------------------------------------------------------------------------------|------|------|------|------|

| V <sub>IH</sub>     | Input logic '1' voltage                               |                                                                                        | 2.0  | -    | -    | V    |

| VIL                 | Input logic '0' voltage                               |                                                                                        | -    | -    | 0.8  | l v  |

| l <sub>iL</sub>     | Input leakage current (any input) (Note 4)            | Note 1                                                                                 | -10  | -    | 10   | μA   |

| loL                 | Output leakage current (Note 4)                       | Note 2                                                                                 | -50  | -    | 50   | μА   |

| $V_{OH}$            | Output logic '1' voltage                              | I <sub>OUT</sub> = -1mA                                                                | 2.4  | -    | -    | V    |

| VOL                 | Output logic '0' voltage                              | I <sub>OUT</sub> = 2mA                                                                 | -    | -    | 0.4  | ٧    |

| $I_{DD1}$           | Average V <sub>DD</sub> power supply current (Note 3) | Freq = 10MHz                                                                           | -    | 70   | 100  | mA   |

| I <sub>DD2</sub>    | Average standby current (Note 3)                      | $\overline{R} = \overline{W} = \overline{RS} = \overline{FL}/\overline{RT} = V_{DD}/2$ | -    | 8    | 15   | mA   |

| I <sub>DD3(L)</sub> | Powerdown current (Note 3)                            | All Inputs = V <sub>DD</sub> -0.2V                                                     | -    | -    | 3.0  | mA   |

#### NOTES:

- 1. Measurements with  $V_{SS} \le V_{IN} \le V_{DD}$

- 2.  $\overline{R} > V_{IH}$ ,  $V_{SS} \le V_{OUT} \le V_{DD}$

- 3.  $I_{DD}$  measurements are made with outputs open,  $V_{DD} = 5.5V$

- 4. Guaranteed but not measured at -55°C

Figure 3a: DC Electrical Characteristics

## **AC CHARACTERISTICS**

Characteristics apply to pre-radiation at  $T_A$  = -55°C to +125°C,  $V_{DD}$  = 5V ±10% and post 100kRad(Si) total dose radiation at  $T_A$  = 25°C,  $V_{DD}$  = 5V ±10%. GROUP A SUBGROUP 9, 10, 11.

| Symbol           | Parameter                                      | T    | Т.   |       |

|------------------|------------------------------------------------|------|------|-------|

|                  | L grannerei                                    | Min. | Max. | Units |

| t <sub>AC</sub>  | Read Cycle Time                                | 110  | -    | ns    |

| t <sub>A</sub>   | Access Time                                    |      | 100  | ns    |

| t <sub>RR</sub>  | Read Recovery Time                             | 25   |      | ns    |

| t <sub>RPW</sub> | Read Pulse Width (Note 2)                      | 85   |      | ns    |

| t <sub>RLZ</sub> | Read Pulse Low to Data Bus at Low Z (Note 3)   | 10   | _    | ns    |

| t <sub>ov</sub>  | Data Valid from Read Pulse High                | 25   | .    | ns    |

| t <sub>RHZ</sub> | Read Pulse High to Data Bus at High Z (Note 3) |      | 30   | ns    |

| twc              | Write Cycle Time                               | 100  | -    | ns    |

| twew             | Write Pulse Width (Note 2)                     | 80   | -    | ns    |

| twe              | Write Recovery Time                            | 20   | _    | ns    |

| t <sub>DS</sub>  | Data Setup Time                                | 40   |      | ns    |

| t <sub>DH</sub>  | Data Hold Time                                 | 10   |      | ns    |

| t <sub>RSC</sub> | Reset Cycle Time                               | 100  | .    | ns    |

| t <sub>AS</sub>  | Reset Pulse Width (Note 2)                     | 80   | _    | ns    |

| t <sub>RSR</sub> | Reset Recovery Time                            | 20   | _    | ns    |

| t <sub>RTC</sub> | Retransmit Cycle Time                          | 100  | _    | ns    |

| t <sub>RT</sub>  | Retransmit Pulse Width (Note 2)                | 80   | -    | ns .  |

| t <sub>ATR</sub> | Retransmit Recovery Time                       | 20   |      | ns    |

| t <sub>EFL</sub> | Reset to Empty Flag Low                        | -    | 100  | ns    |

| t <sub>REF</sub> | Read Low to Empty Flag Low                     |      | 90   | ns    |

| t <sub>RFF</sub> | Read High to Full Flag High                    |      | 70   | ns    |

| t <sub>wef</sub> | Write High to Empty Flag High                  |      | 70   | ns    |

| twee             | Write Low to Full Flag Low                     | -    | 90   | ns    |

| t <sub>EFR</sub> | EF High to Valid Read                          | 10   |      | ns    |

| t <sub>RPI</sub> | Read Protect Indeterminant (Note 3)            | -    | 35   | ns    |

| t <sub>FFW</sub> | FF High to Valid Write                         | 10   | - 1  | ns    |

| t <sub>wei</sub> | Write Protect Indeterminant (Note 3)           | _    | 35   | ns    |

#### NOTES:

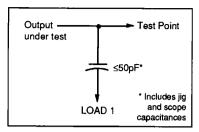

- 1. Timings referenced as in A.C. Test Conditions, figure 5

- 2. Pulse widths less than minimum values are not allowed

- 3. Values guaranteed by design, not currently tested

Figure 3b: AC Characteristics

| Symbol | Parameter     | Conditions                                                                                                                                                                                                         |

|--------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FT     | Functionality | $V_{DD}$ = 3-6V, FREQ = 100kHz - 9MHz<br>$V_{IL}$ = $V_{SS}$ , $V_{IH}$ = $V_{DD}$ , $V_{OL}$ $\leq$ 1.5V, $V_{OH}$ $\geq$ 1.5V<br>TEMP = -55 to +125°C, RADIATION 1MRAD TOTAL DOSE<br>GROUP A SUBGROUPS 7, 8A, 8B |

Figure 3b: Functionality

| Subgroup | Definition                                                 |

|----------|------------------------------------------------------------|

| 1        | Static characteristics specified in Table 3a at +25°C      |

| 2        | Static characteristics specified in Table 3a at +125°C     |

| 3        | Static characteristics specified in Table 3a at -55°C      |

| 7        | Functional characteristics specified in Table 3c at +25°C  |

| 8A       | Functional characteristics specified in Table 3c at +125°C |

| 8B       | Functional characteristics specified in Table 3c at -55°C  |

| 9        | Switching characteristics specified in Table 3b at +25°C   |

| 10       | Switching characteristics specified in Table 3b at +125°C  |

| 11       | Switching characteristics specified in Table 3b at -55°C   |

Figure 4: Definition of Subgroups

| Input Pulse Levels            | GND to 3.0V  |

|-------------------------------|--------------|

| Input Rise and Fall Times     | 5ns          |

| Input Timing Reference Levels | 1.5V         |

| Output Reference Levels       | 1.5V         |

| Output Load                   | See Figure 7 |

|                               |              |

Figure 5: AC Test Conditions

Figure 7: Output Load

| Symbol           | Parameter                                                     | Conditions            | Max. | Unit |

|------------------|---------------------------------------------------------------|-----------------------|------|------|

| C <sub>IN</sub>  | Input Capacitance (Note 1) Output Capacitance (Notes 1 and 2) | V <sub>IN</sub> = 0V  | 7    | pF   |

| C <sub>OUT</sub> |                                                               | V <sub>OUT</sub> = 0V | 12   | pF   |

#### NOTES:

- 1. Characterized values, not currently tested.

- 2. With output deselected.

Figure 6: Capacitance

## **TRUTH TABLES**

| Operation   |     |    | Input |    |    | Output |    |       | Poi       | Pointer   |  |

|-------------|-----|----|-------|----|----|--------|----|-------|-----------|-----------|--|

|             | R   | W  | RS    | RT | Χï | EF     | FF | Data  | Read      | Write     |  |

| Reset       | 1   | 1  | 0     | х  | 0  | 0      | 1  | z     | Zero      | Zero      |  |

| Retransmit* | 1   | 1  | 1     | 0  | 0  | 1      | 1  | z     | Zero      | N/C       |  |

| Read        | 1→0 | x  | 1     | 1  | 0  | 1      | 1  | valid | Increment | N/C       |  |

| Read        | x   | x  | 1     | 1  | 0  | 0      | 1  | z     | N/C       | N/C       |  |

| Write       | x   | 10 | 1     | 1  | 0  | x      | 1  | x l   | N/C       | Increment |  |

| Write       | ×   | х  | 1     | 1  | 0  | 1      | 0  | ×     | N/C       | N/C       |  |

<sup>\*</sup> Only available if less than 512 writes since last reset.

Figure 8: Single Device or Width Expansion: Read, Write, Reset and Retransmit

| Operation                 | input |   |    |    |    | Outpu | ıt | Pointer |              |              |

|---------------------------|-------|---|----|----|----|-------|----|---------|--------------|--------------|

|                           | R     | W | RS | FL | XI | EF    | FF | Data    | Read         | Write        |

| Reset First<br>Reset Rest | 1     | 1 | 0  | 0  | 1  | 0     | 1  | Z<br>Z  | Zero<br>Zero | Zero<br>Zero |

#### NOTES:

- 1. See Modes of Operation for connections of  $\overline{XI}$  and  $\overline{XO}$  in depth expansion mode.

- 2.  $\overline{\text{XI}}$  is connected to  $\overline{\text{XO}}$  of previous device (Figure 12).

Figure 9: Depth Expansion: Reset and First Load

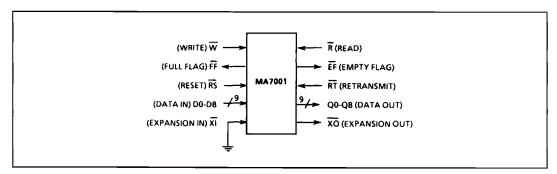

#### SIGNAL DESCRIPTIONS

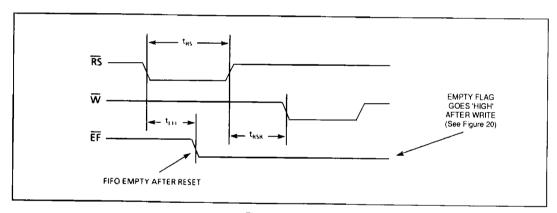

#### Reset (RS)

Reset occurs when  $\overline{\rm RS}$  is in a low state, setting both read and write pointers to the first location in memory. Reset is required prior to the first write. Both READ ( $\overline{\rm R}$ ) and WRITE ( $\overline{\rm W}$ ) signals must be in high states during reset.

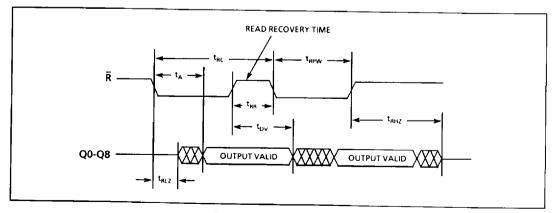

#### Read Enable (R):

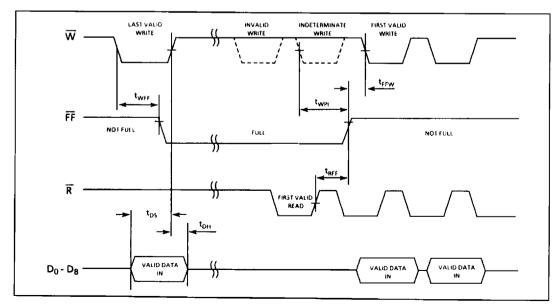

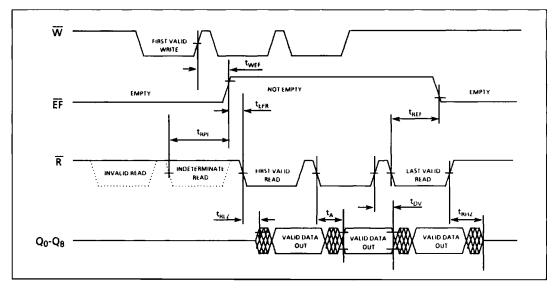

Providing the EMPTY FLAG (EF) is not set, i.e. there is still data to be read, a read cycle commences on the falling edge of R, (see Figure 16). Data is read in a First-In First-Out manner independent of write operations. When reads are disabled data outputs (Q0 - Q8) are in a high impedance state. Reading the last available memory location sets the EMPTY FLAG (EF), which is cleared following a write cycle.

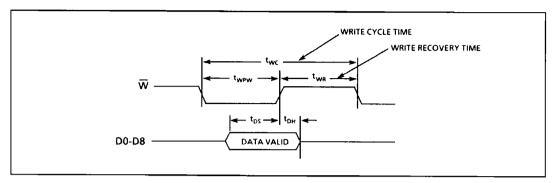

#### Write Enable (W):

Providing the FULL FLAG ( $\overline{FF}$ ) is not set, i.e. there exists at least one memory location for writing, a write cycle commences on the falling edge of ( $\overline{W}$ ), (see Figure 17). Data is written into consecutive memory locations independent of read operations on the rising edge of W. Data set up and hold times are with respect to the rising edge of  $\overline{W}$ .

#### Expansion in $(\overline{XI})$ :

There are two possible modes of operation for the FIFO. One with  $\overline{XI}$  grounded in which the device is in singledevice mode, the other is a depth expension mode or daisy chain configuration. In the latter mode  $\overline{XI}$  inputs come from EXPANSION OUT  $(\overline{XO})$  outputs of the device preceding it in the chain.

#### Expansion Out (XO):

In depth expansion mode  $\overline{XO}$  from one device signals the next device in the chain that the last location in its memory has been accessed.

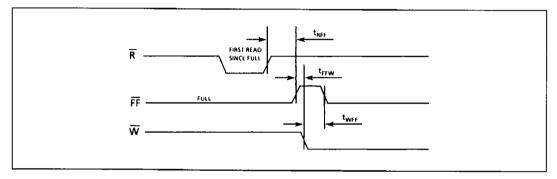

## Full Flag (FF):

FF becomes active when the last available memory location has been written to, (see Figure 18). In general, this occurs whenever the write pointer coincides with the read pointer following a write cycle. Writes are inhibited while FF is active, and may only proceed after a read cycle has occured.

FF will go high t<sub>RFF</sub> after completion of a valid READ operation. FF will go low t<sub>WFF</sub> from the beginning of a subsequent WRITE operation, provided that a second READ has not been completed. Writes beginning t<sub>FFW</sub> after FF goes high, are valid. Writes beginning after FF goes low and ending more than t<sub>WFI</sub> before FF goes high, are invalid (ignored). Writes beginning less than twpl before FF goes high and less than t<sub>FFW</sub> later, may or may not occur (be valid) depending on the internal flag status (see Figure 19).

If a Write to the last but one physical location completes while the last location (511th) is being Read, the FF will not be activated. The next Read should start after the last Write has completed.

As a WRITE operation is being performed to the last physical memory location (511th) whilst the READ pointer is waiting at the 510th physical location the FULL flag is activated for a duration less than 20ns.

Note: The last physical location (511th) is accessed after 511 WRITE or READ operations after RESET.

#### Empty Flag (EF):

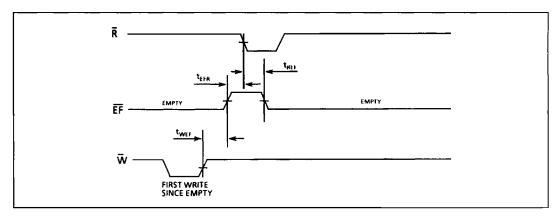

Following an initial RESET EF is active, becoming inactive after the first write cycle, (see Figure 20). EF becomes active once the read and write pointers are coincident following a read cycle. Reading will not take place whilst EF is active, and may only proceed once a write cycle has occured.

EF will go high twer after completion of a valid WRITE operation. EF will again go low tree from the beginning of a subsequent READ operation, provided that a second WRITE has not been completed. Reads beginning terra after EF goes high, are valid. Reads begun after EF goes low and ending more than tree before EF goes high, are invalid (ignored). Reads beginning less than tree before EF goes high and less than tree later, may or may not occur (be valid) depending on the internal flag status (See Figure 21). If a Read to the last but one physical location completes while the last location (511th) is being written, the EF will not be activated. The next Read should be activated after the last Write has completed.

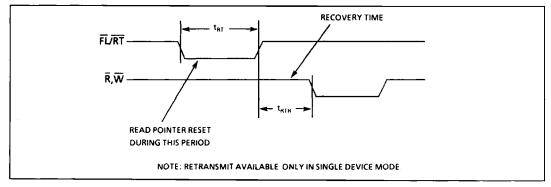

#### First Load/Retransmit (FL/RT):

This is a dual purpose input depending on the mode of operation of the device. In single device mode  $\overline{X}I=0$  data may be retransmitted, i.e. it may be re-read. In depth expansion mode  $\overline{FL}$  signifies the first device in the chain. When  $\overline{RT}$  is pulsed low the read pointer is set to the first memory location. The write pointer is unaffected. This feature is disabled in depth expansion mode, and can only be applied when  $\overline{R}$  and  $\overline{W}$  are inactive (See Figure 22).

Data Inputs (D0 - D8): Data inputs, 9 bit word, for write operations.

#### Data Outputs (Q0 - Q8):

Data outputs, 9 bit word, for read operations. When  $\overline{\bf R}$  is inactive these outputs are in a high impedance state.

#### MODES OF OPERATION

#### Single Device Mode:

The single device mode is used with  $\overline{\rm XI}$  grounded. (See Figure 10). In this mode the retransmit facility may be used to re-read the data when less than 512 have been performed between resets.

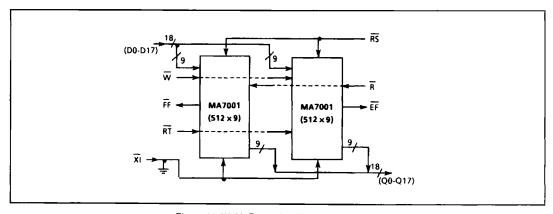

#### Width Expansion Mode:

In this mode two or more devices are used, depending on the word length required, with the same control inputs applied to each. The same operations are applied to all devices, thus warning flags EF and FF are available from any or all of the devices. Output Signals from devices in this mode should not be merged. Figure 11 illustrates two devices configured in width expansion mode to give an 18 bitword, (512 x 18).

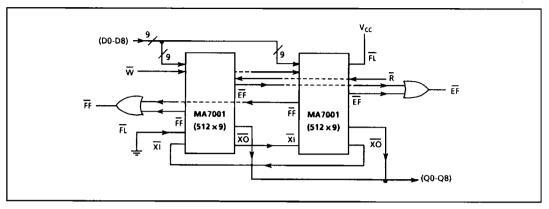

#### Depth Expansion Mode:

This has applications where more than 512 words are required. The RETRANSMIT facility is not available in this mode.

Two or more devices are organised in a daisy chain. The first device in the chain has  $\overline{FL}$  grounded, all others have  $\overline{FL}$  in high states.  $\overline{XO}$  of each device is connected to  $\overline{XI}$  of the next device in the chain.

The same read, write and reset signals are applied to each device. External logic is required to form new empty and full flags, i.e. all EF's are ORed together and all FF's are ORed together to form new empty and full flags respectively.

Figure 12 illustrates depth expansion of 2 devices (1024 x 9).

Figure 10: Single Device Mode (512 x 9 bits)

Figure 11: Width Expansion Mode (512 x 18 bits)

Figure 12: Depth Expansion Mode (1024 x 9 bits)

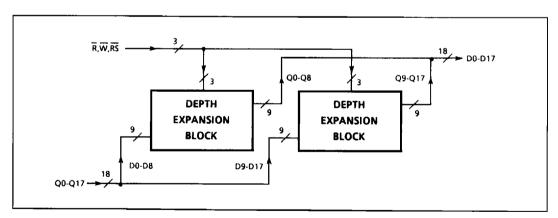

## Compound Expansion Mode:

Both width and depth expansion can be implemented into the same expansion block. Note that no control signals are in conflict in either of the two expansion modes, i.e. width or depth expansion modes. Utilising compound expansion large FIFO arrays are possible. Figure 13 illustrates the use of compound expansion.

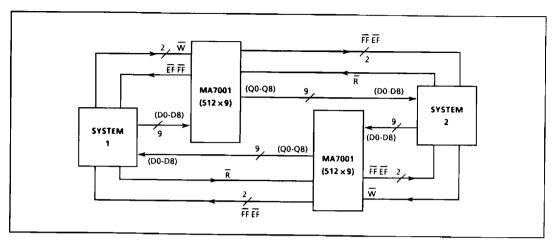

#### Bidirectional Mode:

The FIFO is a unidirectional device, i.e. one system reads, another writes. In cases where full communication is required between two or more systems, two or more groups of devices can be used. These groups can utilise any or all of the expansion modes already mentioned. Figure 14 illustrates 2 systems connected so that each can transmit data to and recieve data from each other, (see Modes of Operation for connection of control and data signals).

Figure 13: Compound Expansion

Figure 14: Bidirectional Mode (512 x 9 bits each way)

Figure 15: Reset

Figure 16: Asynchronous Read

Figure 17: Asynchronous Write

Figure 18: Read/Write to Full Flag

Figure 19: Write and Full Flag

Figure 20: Write/Read to Empty Flag

Figure 21: Read and Empty Flag

Figure 22: Retransmit Timing

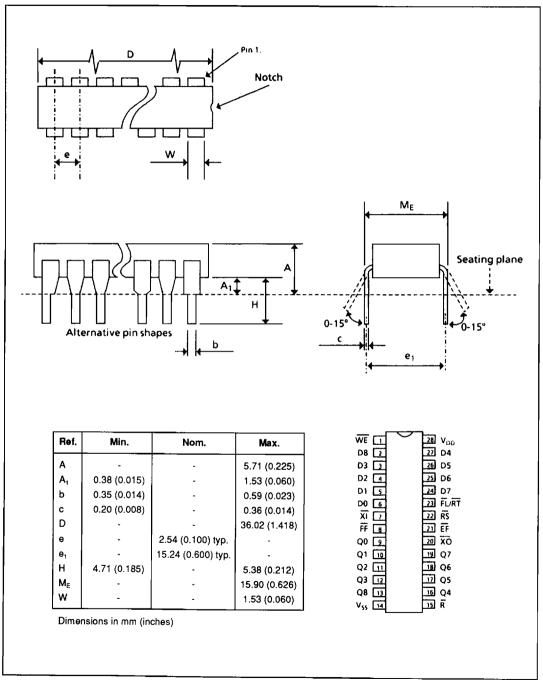

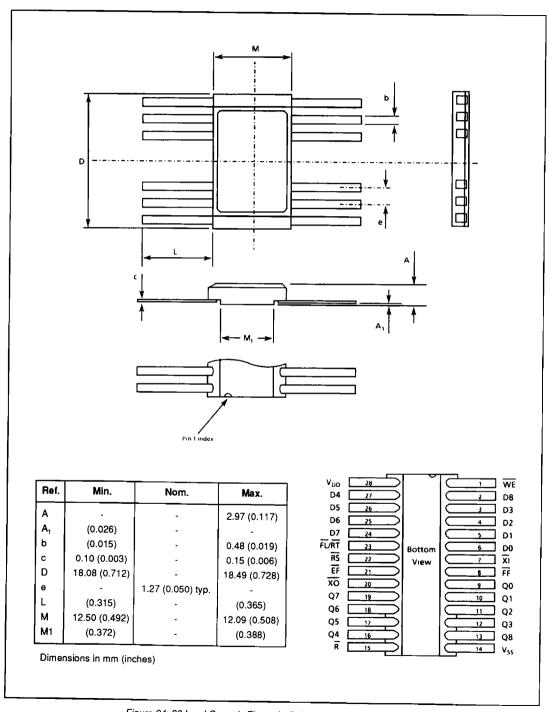

## **OUTLINES AND PIN ASSIGNMENTS**

Figure 23: 28 Lead Ceramic DIL (Solder Seal) - Package Style C

Figure 24: 28 Lead Ceramic Flatpack (Solder Seal) - Package Style F

## **RADIATION TOLERANCE**

#### **Total Dose Radiation Testing**

For product procured to guaranteed total dose radiation levels, each wafer lot will be approved when all sample devices from each lot pass the total dose radiation test.

The sample devices will be subjected to the total dose radiation level (Cobalt-60 Source), defined by the ordering code, and must continue to meet the electrical parameters specified in the data sheet. Electrical tests, pre and post irradiation, will be read and recorded.

GEC Plessey Semiconductors can provide radiation testing compliant with MIL-STD-883 test method 1019, lonizing Radiation (Total Dose).

| Total Dose (Function to specification)       | 1x10⁵ Rad(Si)                              |

|----------------------------------------------|--------------------------------------------|

| Transient Upset (Survivability)              | 5 x 10 <sup>10</sup> Rad(Si)/sec           |

| Neutron Hardness (Function to specification) | >10 <sup>15</sup> Neutrons/cm <sup>2</sup> |

| Single Event Upset (GSO 10% worst case)      | 10 <sup>-10</sup> errors/bitday            |

| Latch-up                                     | Not possible                               |

Figure 25: Radiation Hardness Parameters

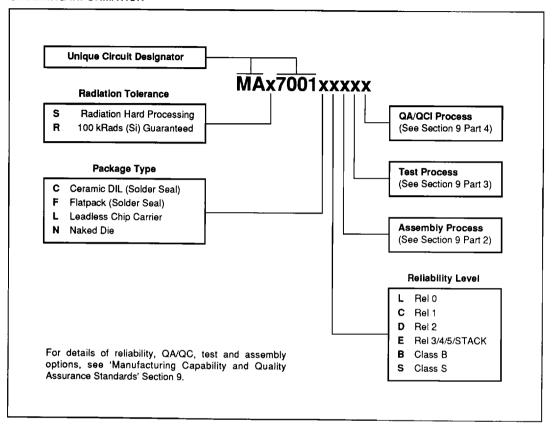

## ORDERING INFORMATION