Make sure the next Card you purchase has... Board

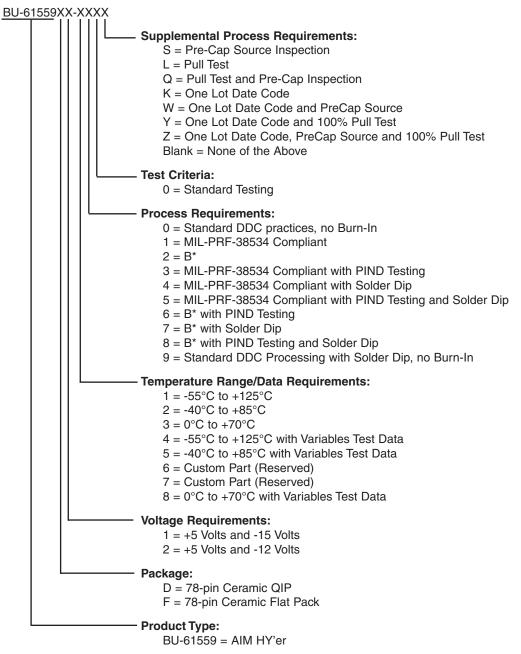

# BU-61559 SERIES MIL-STD-1553B NOTICE 2 AIM-HY'ER

# DESCRIPTION

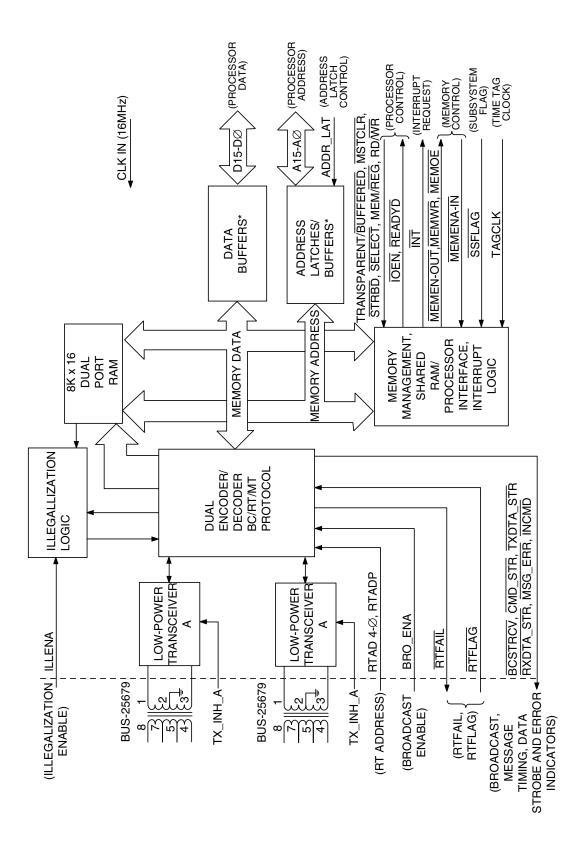

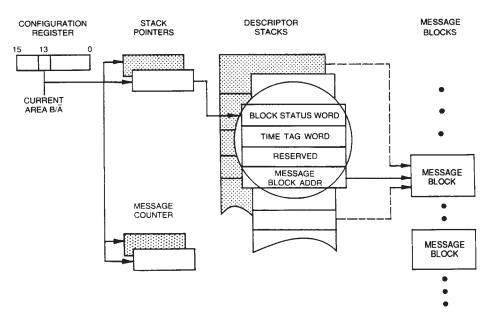

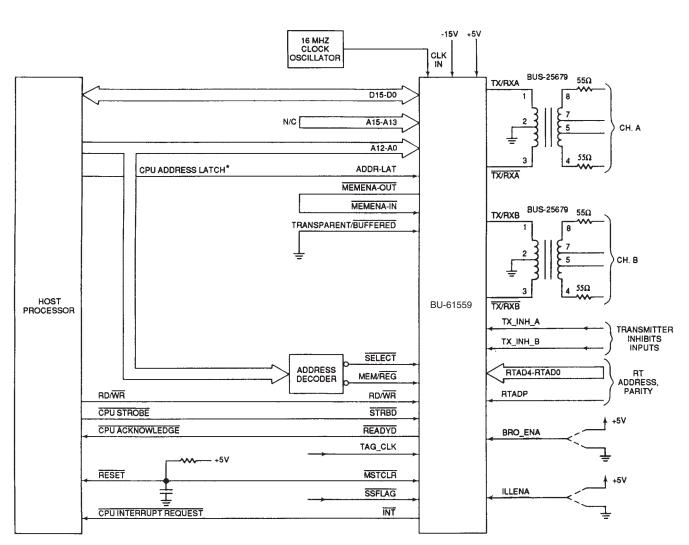

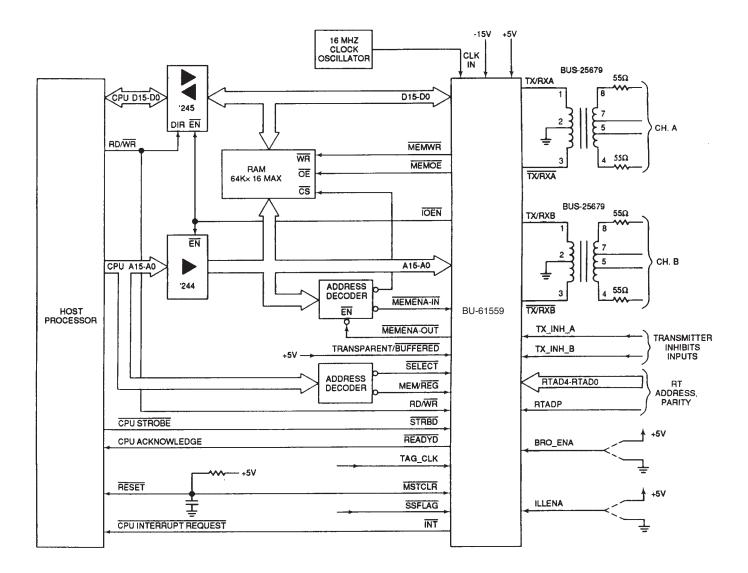

DDC's BU-61559 series of Advanced Integrated Mux Hybrids with enhanced RT Features (AIM-HY'er) comprise a complete interface between a microprocessor and a MIL-STD-1553B Notice 2 bus, implementing Bus Controller (BC), Remote Terminal (RT), and Monitor Terminal (MT) modes. Packaged in a single 78-pin DIP or flat package, the BU-61559 series contains dual low-power transceivers and encoder/decoders, complete BC/RT/MT protocol logic, memory management and interrupt logic, 8K x 16 of shared static RAM, and a direct, buffered interface to a host processor bus.

The BU-61559 includes a number of advanced features that support MIL-STD-1553B Notice 2 and STANAG 3838. Other salient features of the BU-61559 serve to provide the benefits of reduced board space requirements, enhanced software flexibility, and reduced host processor overhead.

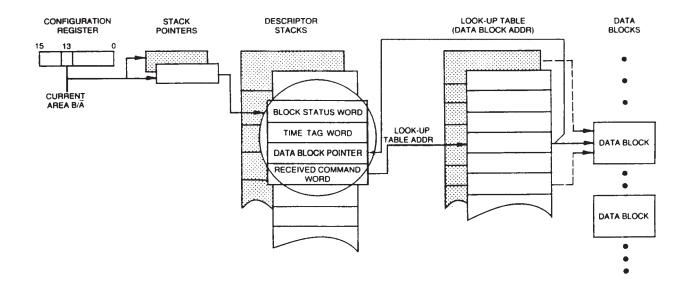

The BU-61559 contains internal address latches and bidirectional data buffers to provide a direct interface to a host processor bus. Alternatively, the buffers may be operated in a fully transparent mode in order to interface to up to 64K words of external shared RAM and/or connect directly to a component set supporting the 20 MHz STANAG 3910 bus.

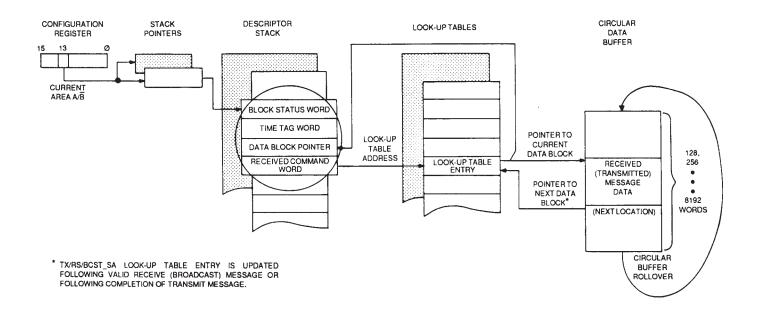

The memory management scheme for RT mode provides an option for separation of broadcast data, in compliance with 1553B Notice 2. A circular buffer option for RT message data blocks offloads the host processor for bulk data transfer applications.

The BU-61559 series hybrids operate over the full military temperature range of -55 to +125°C and MIL-PRF-38534 processing is available. The hybrids are ideal for demanding military and industrial microprocessor-to-1553 applications.

Data Device Corporation 105 Wilbur Place Bohemia, New York 11716 631-567-5600 Fax: 631-567-7358 www.ddc-web.com

# **FEATURES**

- Complete Integrated 1553B Notice 2

Interface Terminal

- Direct Replacement for BUS-61559

AIM-HY'er Series

- Functional Superset of BUS-61553 AIM-HY Series

- Internal Address and Data Buffers for Direct Interface to Processor Bus

- RT Subaddress Circular Buffers to Support Bulk Data Transfers

- Optional Separation of RT Broadcast

Data

- Internal Interrupt Status and Time Tag Registers

- Internal Command Illegalization

- MIL-PRF-38534 Processing Available

- Transmitter Inhibit Control for Individual Bus Channels

FOR MORE INFORMATION CONTACT:

Technical Support: 1-800-DDC-5757 ext. 7771

© 2002 Data Device Corporation

| TABLE 1. BU-61559 SPECIFICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                           |                                                                                                                         |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|--|--|--|

| PARAMETER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | UNITS                                     | VALUE                                                                                                                   |  |  |  |

| ABSOLUTE MAXIMUM RATINGS<br>Supply Voltage<br>• Logic +5V<br>• Transceiver +5V<br>• -15V (BU-61559X1)<br>• -12V (BU-61559X2)<br>Receiver Differential Voltage<br>Logic<br>• Voltage Input Range                                                                                                                                                                                                                                                                                                                                                      | V<br>V<br>V<br>Vp-p<br>V                  | -0.5 to 7.0<br>-0.5 to 7.0<br>+0.3 to -18.0<br>+0.3 to -18.0<br>40 max<br>-0.5 to 7.0                                   |  |  |  |

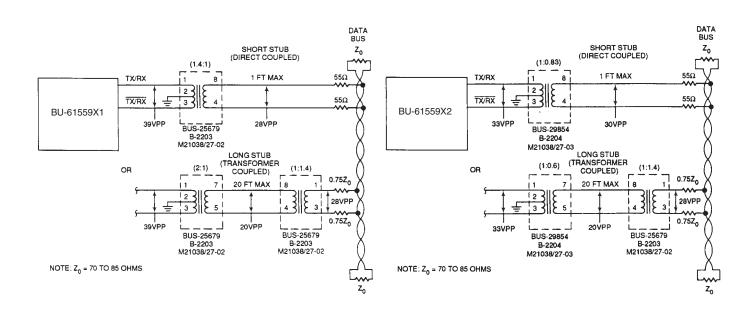

| RECEIVER<br>Differential Input Voltage<br>Differential Input Resistance (see<br>notes 1-6)<br>Differential Input Capacitance (see<br>notes 1-6)<br>Threshold Voltage, Transformer cou-<br>pled, measured on stub<br>CMRR<br>• (BU-61559X1, through BUS-25679<br>transformer at 1MHz)<br>• (BU-61559X2, through BUS-29854<br>transformer at 1MHz)                                                                                                                                                                                                     | Vp-p<br>k Ohms<br>pF<br>Vp-p<br>dB<br>dB  | 40 max<br>11 min<br>10 max<br>0.70 min, 0.86 max<br>50 min<br>50 min                                                    |  |  |  |

| TRANSMITTER<br>Differential Output Voltage<br>• Direct coupled across 35 Ohms,<br>measured on bus<br>• Transformer coupled, measured on<br>stub (for 20 Vp-p min. stub voltage,<br>consult factory)<br>For -601 Reliability Grade (note 7)<br>Output noise, differential (direct cou-<br>pled)<br>Output offset Voltage, direct coupled<br>across 35 Ohms<br>Rise/Fall time                                                                                                                                                                          | Vp-p<br>Vp-p<br>mVp-p,<br>diff<br>V<br>ns | 6 min., 9 max<br>18 min, 20 typ, 27 max<br>20 min, 21 typ, 27 max<br>10 max.<br>±90 max<br>100 min, 150 typ,<br>300 max |  |  |  |

| LOGIC<br>Vih<br>Vil                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | V<br>V                                    | 2.0 min<br>0.8 max                                                                                                      |  |  |  |

| lih (Vcc = 5.5V, Vih = 2.7V)<br>• D15 through D0, A15 through A0,<br>MEM/REG, STRBD, RD/WR,<br>MSTCLR, SELECT, TX_INH_A,<br>TX_INH_B, SSFLAG,<br>TRANSPARENT/BUFFERED,<br>ADDR_LAT, TAGCLK<br>RTAD4 through RTAD0, RTADP<br>BRO_ENA, RTFLAG, ILLENA<br>MEMENA-IN, CLK_IN<br>lil (Vcc = 5.5V, Vil = 0.4V)<br>• D15 through D0, A15 through A0,<br>MEM/REG, STRBD, RD/WR,<br>MSTCLR, SELECT, TX_INH_A,<br>TX_INH_B, SSFLAG,<br>TRANSPARENT/BUFFERED,<br>ADDR_LAT, TAGCLK<br>RTAD4 through RTAD0, RTADP<br>BRO_ENA, RTFLAG, ILLENA<br>MEMENA-IN, CLK_IN | μΑ                                        | -346 min, -42 max<br>-397 min, -50 max                                                                                  |  |  |  |

# TABLE 1. BU-61559 SPECIFICATIONS (CONT)

| PARAMETERUNITSVALUELOGIC (CONT)<br>Voh (Vcc-4.5V, Vih=2.7V, Vil=0.4V)V3.7 minVoh (Vcc-4.5V, Vih=2.7V, Vil=0.4V)V3.7 minIb5 through D0, A15 through A0V3.7 min(Ioh3.4 mA)V3.7 minMEMOE, INCMD, BCSTROV,<br>MSG_ERR, CMD_STR,<br>TXDTA_STR, RXDTA_STRV2.4 min(Ioh6.4 mA)V0.4 max00 (Iol=2.0 mA)V0.4 max(Iol=-6.8 mA)V0.4 max01 (Iol=-6.8 mA)V0.4 max01 (I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | TABLE T. BU-01559 SPEC                      |       |                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|-------|--------------------------|

| Voh (Vcc=4.5V, Vih=2.7V, Vil=0.4V)         V         3.7 min           • (loh=-6.8 mA)         V         3.7 min           D15 through D0, A15 through A0         V         3.7 min           • (loh=-3.4 mA)         V         3.7 min           • (loh=-0.4 mA)         V         3.7 min           • (loh=-0.4 mA)         V         2.4 min           • (lol=-0.4 mA)         V         2.4 min           • (lol=-0.4 mA)         V         2.4 min           • (lol=-0.4 mA)         V         0.4 max           • (lol=-0.4 mA)         V         0.4 max           • (lol=-0.4 mA)         V         0.4 max           • (lol=-2.0 mA)         V         0.4 max           • (lol=-3.8 mA)         V         0.4 max           • (lol=-3.8 mA)         V         0.4 max           • (lol=-3.8 mA)         V         0.4 max           • (lol=-4.8 mA)         V         0.4 max           • (lol=-3.8 mA)         V         0.4 max           • (lol=-3.4 mA)         V         0.4 max           • (lol=-4.0 mA)         V         0.4 max           • (lol=-4.0 mA)         V         0.4 max           Co (f=1 MHz)         pF         50 max <th>PARAMETER</th> <th>UNITS</th> <th>VALUE</th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | PARAMETER                                   | UNITS | VALUE                    |

| Voh (Vcc=4.5V, Vih=2.7V, Vil=0.4V)         V         3.7 min           • (loh=-6.8 mA)         V         3.7 min           D15 through D0, A15 through A0         V         3.7 min           • (loh=-3.4 mA)         V         3.7 min           • (loh=-0.4 mA)         V         3.7 min           • (loh=-0.4 mA)         V         2.4 min           • (lol=-0.4 mA)         V         2.4 min           • (lol=-0.4 mA)         V         2.4 min           • (lol=-0.4 mA)         V         0.4 max           • (lol=-0.4 mA)         V         0.4 max           • (lol=-0.4 mA)         V         0.4 max           • (lol=-2.0 mA)         V         0.4 max           • (lol=-3.8 mA)         V         0.4 max           • (lol=-3.8 mA)         V         0.4 max           • (lol=-3.8 mA)         V         0.4 max           • (lol=-4.8 mA)         V         0.4 max           • (lol=-3.8 mA)         V         0.4 max           • (lol=-3.4 mA)         V         0.4 max           • (lol=-4.0 mA)         V         0.4 max           • (lol=-4.0 mA)         V         0.4 max           Co (f=1 MHz)         pF         50 max <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                             |       |                          |

| <ul> <li>(loh=-6.8 mA)</li> <li>(loh=-6.8 mA)</li> <li>(loh=-3.4 mA)</li> <li>(loh=-3.4 mA)</li> <li>(loh=-6.3 mA)</li> <li>(loh=-0.4 mA)</li> <li>(loh=-6.8 mA)</li> <li>(loh=-6.</li></ul>                                                                                                                                                                                                                                                                       |                                             |       |                          |

| D15         through D0, A15         through A0           • (loh3.4 mA)         V         3.7 min           MEMMOE, MEMENA-OUT,<br>MEMWR, INT, IOEN, READYD         V         2.4 min           • (loh0.4 mA)         V         2.4 min           MTFAIL, INCMD, BCSTRCV,<br>MSG_ERR, CMD_STR,<br>TXDTA_STR, RXDTA_STR         V         0.4 max           Vol. (Vcc=4.5V, Vin=2.7V, Vil=0.4V)         V         0.4 max           • (lol=-6.8 mA)         V         0.4 max           TXDTA_STR, RXDTA_STR         V         0.4 max           MTFAIL, INCMD, BCSTRCV,<br>MSG_ERR, CMD_STR         V         0.4 max           • (lol=-4.0 mA)         V         0.4 max           TXDTA_STR, RXDTA_STR         V         0.4 max           TXDTA_STR, RXDTA_STR         V         0.4 max           Co (f=1 MHz)         pF         50 max           D15 through D0, A15 through A0         V         4.5 min, 5.5 max           • +5V (Ch A, Ch B)         V         4.5 min, 5.5 max           • +5V (BU-61559X1)         V         4.5 min, 5.5 max           • 12V (BU-61559X1)         V         4.5 min, 5.0 max           • 15V (BU-61559X1)         V         4.5 min, 5.0 max           100% Duty Cycle         mA         5 typ, 170 max                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                             | v     | 2.7 min                  |

| <ul> <li>(loh=-3.4 mA)</li> <li>W</li> <li>3.7 min</li> <li>MEMOVE, MEMENA-OUT,<br/>MEMWR, INT, IOEN, READYD</li> <li>(loh=-0.4 mA)</li> <li>(loh=-0.4 mA)</li> <li>RTFAIL, INCMD, BCSTRCV,<br/>MSG_ERR, CMD_STR,<br/>TXDTA_STR, RXDTA_STR</li> <li>V</li> <li>2.4 min</li> <li>RTKDTA_STR, RXDTA_STR</li> <li>V</li> <li>0.4 max</li> <li>0.4 max</li> <li>(lol=-8.8 mA)</li> <li>V</li> <li>0.4 max</li> <li>(lol=-2.0 mA)</li> <li>(lol=-2.0 mA)</li> <li>RTKDTA_STR, RXDTA_STR</li> <li>(lol=-3.4 mA)</li> <li>V</li> <li>0.4 max</li> <li>(lol=-3.4 mA)</li> <li>V</li> <li>0.4 max</li> <li>(memory of the second sec</li></ul>                                                   |                                             | v     | 3.7 11111                |

| MEMOE,<br>MEMVR, INT, IOEN, READYDV2.4 min• (loh=-0.4 mA)<br>RTFAIL, INCMD, BCSTRCV,<br>MSG_ERR, CMD_STR,<br>TXDTA_STR, RXDTA_STR<br>Vol. (vcc=4.5W, vlh=2.7V, vl=0.4V)V0.4 max• (lol=-6.8 mA)<br>D15 through D0, A15 through A0V0.4 max• (lol=2.0 mA)<br>RTFAIL, INCMD, BCSTRCV,<br>MSG_ERR, CMD_STRV0.4 max• (lol=2.0 mA)<br>TXDTA_STR, RXDTA_STRV0.4 max• (lol=2.0 mA)<br>TXDTA_STR, TXDTA_STRV0.4 max• (lol=4.0 mA)<br>TXDTA_STR, RXDTA_STRV0.4 maxCi (f=1 MHz)<br>D15 through D0, A15 through A0pF50 maxFOWER SUPPLY REQUIREMENTS<br>Voltages/Tolerances(see note 7)Voltages/Tolerances<br>• +5V (Logic)V4.5 min, 5.5 max• 15V (BU-61559X1)<br>IdleV-15.75 min, -14.25 max• 15V (BU-61559X1)<br>IdleV-12.6 min, -11.4 max25% Duty Cycle<br>10% Duty CyclemA5 min, 40 typ, 80 max<br>25% Duty CyclePOWER DISSIPATION<br>10% Duty Cycle(see note 7)Total Hybrid<br>• BU-61559X1<br>IdleMA5 min, 40 typ, 80 max<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                             | V     | 0.7 min                  |

| MEMWR, INT, IOEN, READYDV2.4 min• (Ioh0.4 mA)W2.4 minMTFAIL, INCMD, BCSTRCV,<br>MSG_ERR, CMD_STRV0.4 maxVoL (Vcc=4.5V, Vih=2.7V, Vil=0.4V)V0.4 max• (Iol=-6.8 mA)V0.4 maxD15 through D0, A15 through A0V0.4 max• (Iol=-6.8 mA)V0.4 maxmTFAIL, INCMD, BCSTRCV,<br>MSG_ERR, CMD_STRV0.4 max• (Iol=3.4 mA)V0.4 max• (Iol=4.0 mA)V0.4 maxCi (I=1 MHz)pF50 maxCi (I=1 MHz)pF10 maxCi (I=1 MHz)pF50 maxD15 through D0, A15 through A0V4.5 min, 5.5 max• +5V (Ch A, Ch B)V4.5 min, 5.5 max• +5V (BU-61559X1)V-15.75 min, -14.25 max• -12V (BU-61559X1)V-12.6 min, -11.4 maxCurrent DrainmA5 min, 40 typ, 80 max• +5V (BU-61559X1)mA5 min, 200 typ, 200 max100% Duty CyclemA5 min, 200 typ, 200 max50% Duty CyclemA5 min, 200 typ, 200 max100% Duty CyclemA5 min, 200 typ, 200 max60WER DISSIPATION(see note 7)Total Hybrid• BU-61559X1IdleIdleW1.025 typ, 2.050 max25% Duty CyclemA50% Duty CycleW00% Duty CycleW1.325 typ, 2.500 max50% Duty CycleW1.325 typ, 2.500 max50% Duty CycleW1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                             | v     | 3.7 min                  |

| • (Ioh=-0.4 mA)<br>RTFAIL, INCMD, BCSTRCV,<br>MSG_ERR, CMD_STR,<br>TXDTA_STR, RXDTA_STRV2.4 minVol. (Vcc=4.5V, Vih=2.7V, Vil=0.4V)<br>• (Iol=-6.8 mA)<br>D15 through D0, A15 through A0<br>• (Iol=2.0 mA)<br>RTFAIL, INCMD, BCSTRCV,<br>MSG_ERR, CMD_STR<br>• (Iol=3.4 mA)<br>(Iol=4.0 mA)V0.4 max• (Iol=2.0 mA)<br>RTFAIL, INCMD, BCSTRCV,<br>MSG_ERR, CMD_STR<br>• (Iol=4.0 mA)<br>(Iol=4.0 mA)V0.4 max• (Iol=3.4 mA)<br>MEMOE, MEMENA-OUT,<br>MEMOR, INT, IOEN, READYD<br>• (Iol=4.0 mA)<br>(Iol=4.0 mA)V0.4 max• (Iol=3.4 mA)<br>MEMOR, INT, IOEN, READYD<br>• (Iol=4.0 mA)<br>TXDTA_STR, RXDTA_STRV0.4 maxCi (f=1 MHz)<br>Cio (f=1 MHz)<br>D15 through D0, A15 through A0PF50 maxPOWER SUPPLY REQUIREMENTS<br>Voltages/Tolerances<br>• +5V (ChA, Ch B)<br>• 15V (BU-61559X1)<br>IdleV4.5 min, 5.5 max• 12V (BU-61559X1)<br>IdleV-15.75 min, -14.25 max• 12V (BU-61559X1)<br>IdleV-12.6 min, -11.4 maxCurrent Drain<br>• +5VmA85 typ, 170 max• 15V (BU-61559X1)<br>IdlemA5 min, 40 typ, 80 max25% Duty Cycle<br>IdlemA5 min, 20 byp, 135 max100% Duty CycleW1.025 typ, 2.050 max100% Duty Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                             |       |                          |

| TTFAIL, INCMD, BCSTRCV,<br>MSG_ERR, CMD_STR,<br>TXDTA_STR, RXDTA_STRVVol. (vcc=4.5V, Vih=2.7V, Vil=0.4V)<br>• (lol=-6.8 mA)V0.4 maxD15 through D0, A15 through A0<br>• (lol=2.0 mA)V0.4 maxTTFAIL, INCMD, BCSTRCV,<br>MSG_ERR, CMD_STRV0.4 max• (lol=2.0 mA)<br>TXDTA_STR, RXDTA_STRV0.4 max• (lol=2.4 mA)V0.4 max• (lol=2.4 mA)V0.4 max• (lol=4.0 mA)<br>TXDTA_STR, RXDTA_STRV0.4 maxCi (f=1 MHz)<br>D15 through D0, A15 through A0V0.4 maxPOWER SUPPLY REQUIREMENTS<br>Voltages/Tolerances(see note 7)Voltages/TolerancesV4.5 min, 5.5 max• +5V (Logic)V4.5 min, 5.5 max• 12V (BU-61559X1)V-15.75 min, -14.25 max• 15V (BU-61559X1)V-15.75 min, -14.25 max• +5V (BU-61559X1)mA5 min, 40 typ, 80 max25% Duty CyclemA5 min, 120 typ, 130 max50% Duty CyclemA5 min, 200 typ, 280 max25% Duty CyclemA5 min, 40 typ, 80 max25% Duty CyclemA5 min, 200 typ, 280 max25% Duty CyclemA25 min, 90 typ, 135 max100% Duty CycleW1.025 typ, 2.050 max100% Duty CycleW1.325 typ, 2.500 max100% Duty CycleW1.325 typ, 2.500 max100% Dut                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                             | v     | 0.4 min                  |

| MSG_ERR, CMD_STR,<br>TXDTA_STR, RXDTA_STR         V         0.4 max           Vol. (Vcc=4.5V, Vih=2.7V, Vil=0.4V)         V         0.4 max           viloi=-6.8 mA)         V         0.4 max           DT5 through D0, A15 through A0         V         0.4 max           RTFAIL, INCMD, BCSTRCV,<br>MSG_ERR, CMD_STR         V         0.4 max           • (loi=3.4 mA)         V         0.4 max           mEMOE, MEMENA-OUT,<br>MEMWR, INT, IOEN, READYD         V         0.4 max           • (loi=4.0 mA)         V         0.4 max           TXDTA_STR, RXDTA_STR         V         0.4 max           Co (f=1 MHz)         pF         50 max           Co (f=1 MHz)         pF         10 max           D15 through D0, A15 through A0         V         4.5 min, 5.5 max           +5V (Logic)         V         4.5 min, 5.5 max           +15V (BU-61559X1)         V         -15.75 min, -14.25 max           +12V (BU-61559X2)         V         -15.75 min, 30 typ, 130 max           Current Drain         mA         85 typ, 170 max           * 15V (BU-61559X1)         mA         85 typ, 130 max           Idle         mA         5 min, 40 typ, 80 max           25% Duty Cycle         mA         85 min, 20 typ, 130 max <t< td=""><td></td><td>v</td><td>2.4 11111</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                             | v     | 2.4 11111                |

| TXDTA_STR, RXDTA_STRVoL (Vcc=4.5V, Vil=2.7V, Vil=0.4V)• (lol=6.8 mA)D15 through D0, A15 through A0• (lol=2.0 mA)• (lol=2.0 mA)WSG_ERR, CMD_STR• (lol=3.4 mA)• (lol=3.4 mA)• (lol=4.0 mA)• (lol=4.0 mA)• (lol=4.0 mA)• (lol=4.0 mA)• (lol=4.0 mA)• (lol=4.0 mA)• (lol=5.4 mA)• (lol=4.0 mA)• (lol=4.0 mA)• TXDTA_STR, RXDTA_STRCi (f=1 MHz)Co (f=1 MHz)D15 through D0, A15 through A0POWER SUPPLY REQUIREMENTSVoltages/Tolerances• +5V (Logic)• +5V (Logic)V• 15V (BU-61559X1)V• 15V (BU-61559X1)V• 15V (BU-61559X1)Idle25% Duty CyclemA25% Duty CyclemA50% Duty CyclemA25% Duty CyclemA50% Duty CyclemA50% Duty CyclemA25% Duty CyclemA50% Duty CyclemA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                             |       |                          |

| Vol. (Vcc=4.5V, Vih=2.7V, Vil=0.4V)         V         0.4 max           (lol=-6.8 mA)         V         0.4 max           D15 through D0, A15 through A0         V         0.4 max           (lol=2.0 mA)         V         0.4 max           RTFAIL, INCMD, BCSTRCV,<br>MSG_ERR, CMD_STR         V         0.4 max           (lol=3.4 mA)         V         0.4 max           mEMOE, MEMENA-OUT,<br>MEMWR, INT, IOEN, READYD         V         0.4 max           (lol=4.0 mA)         V         0.4 max           TXDTA_STR, RXDTA_STR         PF         50 max           Ci (f=1 MHz)         pF         50 max           D15 through D0, A15 through A0         V         4.5 min, 5.5 max           +5V (Logic)         V         4.5 min, 5.5 max           +15V (BU-61559X1)         V         4.5 min, 5.5 max           +15V (BU-61559X1)         V         -12.6 min, -11.4 max           Current Drain         mA         85 typ, 170 max           +5V (BU-61559X1)         mA         5 min, 40 typ, 80 max           100% Duty Cycle         mA         5 min, 20 typ, 130 max           100% Duty Cycle         mA         5 min, 20 typ, 306 max           25% Duty Cycle         mA         5 min, 20 typ, 30 max                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                             |       |                          |

| <ul> <li>(Iol=-6.8 mA)<br/>D15 through D0, A15 through A0</li> <li>(Iol=2.0 mA)<br/>RTFAIL, INCMD, BCSTRCV,<br/>MSG_ERR, CMD_STR</li> <li>(Iol=3.4 mA)</li> <li>V</li> <li>0.4 max</li> <li>0 max</li></ul>                                                                                                                                                                                                                                                                                                                                                |                                             |       |                          |

| D15 through D0, A15 through A0V0.4 max• (Iol=2.0 mA)<br>RTFAIL, INCMD, BCSTRCV,<br>MSG_ERR, CMD_STRV0.4 max• (Iol=3.4 mA)<br>MEMWR, INT, IOEN, READYDV0.4 max• (Iol=4.0 mA)<br>TXDTA_STR, RXDTA_STRV0.4 maxCi (f=1 MHz)<br>Co (f=1 MHz)<br>D15 through D0, A15 through A0V0.4 maxPOWER SUPPLY REQUIREMENTSVoltages/Tolerances<br>• +5V (Logic)V4.5 min, 5.5 max<br>4.5 min, 5.5 max• 15V (BU-61559X1)<br>Udred E1559X1)V4.5 min, 5.1 max<br>4.5 min, 5.5 max<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | · · · · · · · · · · · · · · · · · · ·       | v     | 0.4 max                  |

| • (Iol=2.0 mÅ)         V         0.4 max           RTFAIL, INCMD, BCSTRCV,<br>MSG_ERR, CMD_STR         V         0.4 max           • (Iol=3.4 mA)         V         0.4 max           • (Iol=4.0 mA)         V         0.4 max           Co (f=1 MHz)         pF         50 max           Co (f=1 MHz)         pF         50 max           D15 through D0, A15 through A0         V         4.5 min, 5.5 max           +5V (Logic)         V         4.5 min, 5.5 max           +5V (Ch A, Ch B)         V         4.5 min, 5.5 max           •15V (BU-61559X1)         V         -12.6 min, -11.4 max           Current Drain         mA         85 typ, 170 max           •15V (BU-61559X1)         mA         85 min, 200 typ, 180 max           100% Duty Cycle         mA         5 min, 40 typ, 80 max           25% Duty Cycle         mA         5 min, 90 typ, 130 max           100% Duty Cycle         mA         5 min, 90 typ, 135 max           100% Duty Cycle         mA         5 min,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                             | v     | 0.4 max                  |

| THEAL, INCMD, BCSTRCV,<br>MSG_ERR, CMD_STRV0.4 max• (Iol=3.4 mA)V0.4 max• (Iol=3.4 mA)V0.4 max• (Iol=4.0 mA)V0.4 max• (Iol=4.0 mA)V0.4 max• (Iol=4.0 mA)V0.4 max• (Iol=4.0 mA)PF50 max• (Iol=1 MHz)pF10 max• (Iol=1 MHz)pF10 max• (Iol=1 MHz)pF50 max• Iol (I=1 MHz)pF50 max• Iol (I=1 MHz)pF10 max• Iol (I=1 MHz)V4.5 min, 5.5 max• Iol (I=1 MHz)V4.5 min, 5.5 max• Iol (I=1 MHz)V4.5 min, 5.5 max• Iol (I=1 MHz)V-15.75 min, -14.25 max• Iol (I=1 MHz)V-12.6 min, -11.4 max• Iol (III (I=1 MIz))V-12.6 min, -11.4 max• Iol (III (III (III (III (III (III (III                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                             | v     | 0.4 max                  |

| MSG_ERR, CMD_STR         V         0.4 max           • (Iol=3.4 mA)         V         0.4 max           MEMOE, MEMENA-OUT,<br>MEMWR, INT, IOEN, READYD         V         0.4 max           • (Iol=4.0 mA)         V         0.4 max           TXDTA_STR, RXDTA_STR         pF         50 max           Co (f=1 MHz)         pF         10 max           D15 through D0, A15 through A0         pF         50 max           POWER SUPPLY REQUIREMENTS           Voltages/Tolerances         V         4.5 min, 5.5 max           • +5V (Logic)         V         4.5 min, 5.5 max           • 15V (BU-61559X1)         V         -12.6 min, -11.4 max           Current Drain         v         -12.6 min, -11.4 max           25% Duty Cycle         mA         85 typ, 170 max           • 15V (BU-61559X1)         mA         5 min, 40 typ, 80 max           100% Duty Cycle         mA         5 min, 40 typ, 80 max           25% Duty Cycle         mA         5 min, 40 typ, 80 max           25% Duty Cycle         mA         5 min, 40 typ, 80 max           25% Duty Cycle         mA         5 min, 40 typ, 80 max           25% Duty Cycle         mA         5 min, 40 typ, 80 max           25% Duty Cycle         m                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                             | v     | 0.4 max                  |

| <ul> <li>(Iol=3.4 mA)</li> <li>V</li> <li>0.4 max</li> <li>MEMOE, MEMENA-OUT,<br/>MEMWR, INT, IOEN, READYD</li> <li>(Iol=4.0 mA)<br/>TXDTA_STR, RXDTA_STR</li> <li>Ci (f=1 MHz)</li> <li>Co (f=1 MHz)</li> <li>D15 through D0, A15 through A0</li> <li>POWER SUPPLY REQUIREMENTS</li> <li>V</li> <li>4.5 V (Logic)</li> <li>V</li> <li>4.5 V (Ch A, Ch B)</li> <li>V</li> <li>4.5 V (Ch Ch A, Ch B)</li> <li>V</li> <li>4.5 V (Ch Ch A, Ch B)</li> <li>V</li> <li>4.5 V (Ch Ch A, Ch B)</li> <li>V</li> <li>4.5 V (Ch 4. Ch B)</li> <li>V</li> <li>4.5 V (BU-61559X1)</li> <li>V</li> <li>4.5 V (BU-61559X1)</li> <li>V</li> <li>4.5 V (BU-61559X1)</li> <li>V</li> <li>4.5 V (BU-61559X1)</li> <li>V</li> <li>1.5 V (BU-61559X1)</li> <li>Idle</li> <li>mA</li> <li>5 min, 40 typ, 80 max</li> <li>25% Duty Cycle</li> <li>mA</li> <li>5 min, 40 typ, 80 max</li> <li>25% Duty Cycle</li> <li>mA</li> <li>5 min, 40 typ, 80 max</li> <li>25% Duty Cycle</li> <li>mA</li> <li>5 min, 40 typ, 80 max</li> <li>25% Duty Cycle</li> <li>mA</li> <li>7 max</li> <li>1.12 V (BU-61559X2)</li> <li>Idle</li> <li>mA</li> <li>100% Duty Cycle</li> <li>mA</li> <li>100% Duty Cycle</li> <li>mA</li> <li>100% Duty Cycle</li> <li>mA</li> <li>1025 typ, 2.050 max</li> <li>25% Duty Cycle</li> <li>mA</li> <li>1.025 typ, 2.050 max</li> <li>25% Duty Cycle</li> <li>W</li> <li>1.025 typ, 2.050 max</li> <li>1.026 typ, 2.170 max</li> <li>50% Duty Cycle</li> <li>W</li> <li>0.905 typ, 1.810 max</li> <li>25% Duty Cycle</li> <li>W<td></td><td></td><td></td></li></ul>                                                                                                                                                                                                                                                        |                                             |       |                          |

| MEMOE, MEMENA-OUT,<br>MEMWR, INT, IOEN, READYDV0.4 max* (lol=4.0 mA)<br>TXDTA_STR, RXDTA_STRV0.4 maxCi (f=1 MHz)<br>Co (f=1 MHz)<br>D15 through D0, A15 through A0pF10 maxPOWER SUPPLY REQUIREMENTS<br>Voltages/Tolerances(see note 7)* +5V (Logic)V4.5 min, 5.5 max* +5V (BU-61559X1)V4.5 min, 5.5 max* +5V (BU-61559X2)V-12.6 min, -11.4 maxCurrent DrainmA85 typ, 170 max* +5VbUty CyclemA25% Duty CyclemA5 min, 40 typ, 80 max25% Duty CyclemA5 min, 90 typ, 135 max100% Duty CyclemA5 min, 90 typ, 135 max100% Duty CycleW1.025 typ, 2.050 max10% Duty CycleW1.025 typ, 2.170 max10% Duty CycleW1.025 typ, 2.170 max10% Duty CycleW1.025 typ, 2.170 max10% Duty Cycl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                             | v     | 0.4 may                  |

| MEMWR, INT, IOEN, READYD         V         0.4 max           '(Iol=4.0 mA)         PF         50 max           Ci (f=1 MHz)         pF         10 max           Co (f=1 MHz)         pF         50 max           Co (f=1 MHz)         pF         50 max           D15 through D0, A15 through A0         PF         50 max           POWER SUPPLY REQUIREMENTS         (see note 7)           Voltages/Tolerances         +5V (Logic)         V           +5V (Logic)         V         4.5 min, 5.5 max           -15V (BU-61559X1)         V         -12.6 min, -11.4 max           Current Drain         mA         85 typ, 170 max           +15V (BU-61559X1)         mA         5 min, 40 typ, 80 max           25% Duty Cycle         mA         5 min, 200 typ, 280 max           50% Duty Cycle         mA         5 min, 200 typ, 180 max           100% Duty Cycle         mA         5 min, 135 typ, 180 max           100% Duty Cycle         mA         5 min, 135 typ, 185 max           100% Duty Cycle         mA         5 min, 135 typ, 185 max           100% Duty Cycle         mA         5 min, 135 typ, 185 max           100% Duty Cycle         W         1.025 typ, 2.050 max           100% Duty Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                             | ľ     | 0. <del>-</del> 110A     |

| · (Iol=4.0 mA)<br>TXDTA_STR, RXDTA_STR         V         0.4 max           Ci (f=1 MHz)<br>Co (f=1 MHz)<br>D15 through D0, A15 through A0         pF         50 max           POWER SUPPLY REQUIREMENTS<br>Voltages/Tolerances         pF         50 max           +5V (Logic)         V         4.5 min, 5.5 max           +5V (Ch A, Ch B)         V         -15.75 min, -14.25 max           -15V (BU-61559X1)         V         -15.75 min, -14.25 max           -12V (BU-61559X2)         V         -15.75 min, -14.25 max           Current Drain         mA         85 typ, 170 max           +5V (BU-61559X1)         W         -15.75 min, 40 typ, 80 max           25% Duty Cycle         mA         5 min, 40 typ, 80 max           50% Duty Cycle         mA         5 min, 40 typ, 80 max           100% Duty Cycle         mA         5 min, 40 typ, 80 max           25% Duty Cycle         mA         5 min, 120 typ, 135 max           100% Duty Cycle         mA         5 min, 320 typ, 305 max           100% Duty Cycle         mA         5 min, 230 typ, 305 max           100% Duty Cycle         W         1.025 typ, 2.050 max           100% Duty Cycle         W         1.625 typ, 2.950 max           100% Duty Cycle         W         1.625 typ, 2.950 max                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | MEMUE, MEMENA-001,<br>MEMWB INT IOEN BEADYD |       |                          |

| TXDTA_STR, RXDTA_STR         pF         50 max           Ci (f=1 MHz)         pF         10 max           Cio (f=1 MHz)         pF         10 max           D15 through D0, A15 through A0         pF         50 max           POWER SUPPLY REQUIREMENTS         (see note 7)           Voltages/Tolerances         +5V (Logic)         V           +5V (BU-61559X1)         V         4.5 min, 5.5 max           -15V (BU-61559X2)         V         -15.75 min, -14.25 max           -12V (BU-61559X1)         V         -15.75 min, -14.25 max           -15V (BU-61559X1)         V         -12.6 min, -11.4 max           Current Drain         mA         85 typ, 170 max           +5V         BU-61559X1)         mA         5 min, 40 typ, 80 max           25% Duty Cycle         mA         5 min, 200 typ, 130 max           50% Duty Cycle         mA         5 min, 40 typ, 80 max           25% Duty Cycle         mA         5 min, 40 typ, 80 max           25% Duty Cycle         mA         5 min, 120 typ, 135 max           100% Duty Cycle         mA         5 min, 230 typ, 305 max           100% Duty Cycle         mA         5 min, 230 typ, 305 max           100% Duty Cycle         W         1.025 typ, 2.050 max </td <td></td> <td>v</td> <td>0.4 max</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                             | v     | 0.4 max                  |

| Ci (f=1 MHz)         pF         50 max           Co (f=1 MHz)         pF         10 max           Cio (f=1 MHz)         pF         50 max           D15 through D0, A15 through A0         pF         50 max           POWER SUPPLY REQUIREMENTS           Voltages/Tolerances         V         4.5 min, 5.5 max           +5V (Logic)         V         4.5 min, 5.5 max           +5V (BU-61559X1)         V         -15.75 min, -14.25 max           -12V (BU-61559X2)         V         -15.75 min, -14.25 max           Current Drain         mA         85 typ, 170 max           +5V (BU-61559X1)         mA         5 min, 40 typ, 80 max           100% Duty Cycle         mA         5 min, 40 typ, 80 max           25% Duty Cycle         mA         5 min, 40 typ, 80 max           100% Duty Cycle         mA         5 min, 40 typ, 80 max           25% Duty Cycle         mA         5 min, 90 typ, 135 max           100% Duty Cycle         mA         5 min, 135 typ, 185 max           100% Duty Cycle         mA         5 min, 230 typ, 305 max           POWER DISSIPATION         (see note 7)         1.025 typ, 2.050 max           100% Duty Cycle         W         1.025 typ, 2.050 max           100% Dut                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                             | v     | 0. <del>4</del> max      |

| Co (f=1 MHz)<br>Cio (f=1 MHz)<br>D15 through D0, A15 through A0         pF<br>pF         10 max<br>50 max           POWER SUPPLY REQUIREMENTS<br>Voltages/Tolerances         (see note 7)           Voltages/Tolerances         V         4.5 min, 5.5 max           +5V (Logic)         V         4.5 min, 5.5 max           +5V (Ch A, Ch B)         V         4.5 min, 5.5 max           -15V (BU-61559X1)         V         15.75 min, -14.25 max           -12V (BU-61559X2)         V         12.6 min, -11.4 max           Current Drain         mA         85 typ, 170 max           * -15V (BU-61559X1)         mA         85 typ, 170 max           100% Duty Cycle         mA         5 min, 40 typ, 80 max           25% Duty Cycle         mA         5 min, 200 typ, 280 max           100% Duty Cycle         mA         5 min, 40 typ, 80 max           25% Duty Cycle         mA         5 min, 30 typ, 135 max           100% Duty Cycle         mA         5 min, 30 typ, 135 max           100% Duty Cycle         mA         5 min, 30 typ, 135 max           100% Duty Cycle         mA         5 min, 200 typ, 2050 max           100% Duty Cycle         mA         5 min, 30 typ, 305 max           POWER DISSIPATION         (see note 7)           Total Hybrid         U <td>_ / _</td> <td>nF</td> <td>50 may</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | _ / _                                       | nF    | 50 may                   |

| Cio (f=1 MHz)<br>D15 through D0, A15 through A0         pF         50 max           POWER SUPPLY REQUIREMENTS<br>Voltages/Tolerances         (see note 7)           Voltages/Tolerances         V         4.5 min, 5.5 max           ++5V (Logic)         V         4.5 min, 5.5 max           ++5V (Ch A, Ch B)         V         4.5 min, 5.5 max           -15V (BU-61559X1)         V         -15.75 min, -14.25 max           -12V (BU-61559X2)         V         -15.75 min, -14.25 max           Current Drain         mA         85 typ, 170 max           +5V         mA         85 typ, 170 max           -15V (BU-61559X1)         mA         5 min, 40 typ, 80 max           25% Duty Cycle         mA         5 min, 200 typ, 280 max           100% Duty Cycle         mA         5 min, 200 typ, 280 max           100% Duty Cycle         mA         5 min, 40 typ, 80 max           25% Duty Cycle         mA         5 min, 200 typ, 280 max           100% Duty Cycle         mA         5 min, 200 typ, 280 max           25% Duty Cycle         mA         5 min, 200 typ, 205 max           100% Duty Cycle         mA         5 min, 200 typ, 305 max           100% Duty Cycle         W         1.025 typ, 2.050 max           100% Duty Cycle         W <td>· · · · · · · · · · · · · · · · · · ·</td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | · · · · · · · · · · · · · · · · · · ·       |       |                          |

| D15 through D0, A15 through A0         Image: Constraint of the system of the syst |                                             |       |                          |

| POWER SUPPLY REQUIREMENTS         (see note 7)           Voltages/Tolerances         V         4.5 min, 5.5 max           ++5V (Logic)         V         4.5 min, 5.5 max           -+5V (BU-61559X1)         V         4.5 min, 5.5 max           -15V (BU-61559X2)         V         -15.75 min, -14.25 max           -12V (BU-61559X2)         V         -12.6 min, -11.4 max           Current Drain         mA         85 typ, 170 max           +5V         mA         25 min, 80 typ, 130 max           50% Duty Cycle         mA         25 min, 200 typ, 280 max           50% Duty Cycle         mA         5 min, 40 typ, 80 max           100% Duty Cycle         mA         5 min, 40 typ, 80 max           100% Duty Cycle         mA         5 min, 90 typ, 135 max           100% Duty Cycle         mA         5 min, 90 typ, 135 max           100% Duty Cycle         mA         5 min, 200 typ, 280 max           50% Duty Cycle         mA         5 min, 90 typ, 135 max           100% Duty Cycle         mA         5 min, 200 typ, 2050 max           100% Duty Cycle         W         1.025 typ, 2.050 max           100% Duty Cycle         W         1.325 typ, 2.500 max           100% Duty Cycle         W         1.225 typ, 3.850 ma                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                             | P     | oo max                   |

| Voltages/Tolerances         V         4.5 min, 5.5 max           ++5V (Logic)         V         4.5 min, 5.5 max           ++5V (Ch A, Ch B)         V         4.5 min, 5.5 max           -15V (BU-61559X1)         V         -15.75 min, -14.25 max           -12V (BU-61559X2)         V         -12.6 min, -11.4 max           Current Drain         mA         85 typ, 170 max           +5V         mA         5 min, 40 typ, 80 max           25% Duty Cycle         mA         5 min, 120 typ, 130 max           50% Duty Cycle         mA         45 min, 120 typ, 180 max           100% Duty Cycle         mA         5 min, 40 typ, 80 max           25% Duty Cycle         mA         45 min, 120 typ, 180 max           100% Duty Cycle         mA         5 min, 90 typ, 135 max           100% Duty Cycle         mA         5 min, 90 typ, 135 max           100% Duty Cycle         mA         5 min, 230 typ, 305 max           100% Duty Cycle         mA         85 min, 230 typ, 2.050 max           100% Duty Cycle         W         1.025 typ, 2.050 max           100% Duty Cycle         W         1.625 typ, 2.950 max           100% Duty Cycle         W         1.625 typ, 2.950 max           100% Duty Cycle         W <t< td=""><td><b>.</b> . <b>.</b></td><td></td><td></td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <b>.</b> . <b>.</b>                         |       |                          |

| • +5V (Logic)       V       4.5 min, 5.5 max         • +5V (Ch A, Ch B)       V       4.5 min, 5.5 max         • -15V (BU-61559X1)       V       -15.75 min, -14.25 max         • -12V (BU-61559X2)       V       -12.6 min, -11.4 max         Current Drain       mA       85 typ, 170 max         • +5V       mA       5 min, 40 typ, 80 max         25% Duty Cycle       mA       5 min, 120 typ, 130 max         50% Duty Cycle       mA       45 min, 120 typ, 180 max         100% Duty Cycle       mA       5 min, 40 typ, 80 max         100% Duty Cycle       mA       5 min, 200 typ, 280 max         100% Duty Cycle       mA       5 min, 90 typ, 135 max         100% Duty Cycle       mA       5 min, 90 typ, 135 max         100% Duty Cycle       mA       85 min, 230 typ, 305 max         100% Duty Cycle       mA       85 min, 230 typ, 305 max         100% Duty Cycle       W       1.025 typ, 2.050 max         100% Duty Cycle       W       1.325 typ, 2.050 max         100% Duty Cycle       W       1.625 typ, 2.950 max         100% Duty Cycle       W       1.625 typ, 2.950 max         100% Duty Cycle       W       1.625 typ, 2.950 max         100% Duty Cycle       W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                             |       | (see note 7)             |

| • +5V (Ch A, Ch B)       V       4.5 min, 5.5 max         • -15V (BU-61559X1)       V       -15.75 min, -14.25 max         • -12V (BU-61559X2)       V       -12.6 min, -11.4 max         Current Drain       mA       85 typ, 170 max         • +5V       mA       5 min, 40 typ, 80 max         25% Duty Cycle       mA       5 min, 120 typ, 130 max         50% Duty Cycle       mA       45 min, 120 typ, 180 max         100% Duty Cycle       mA       5 min, 40 typ, 80 max         100% Duty Cycle       mA       5 min, 200 typ, 280 max         1dle       mA       5 min, 200 typ, 280 max         25% Duty Cycle       mA       5 min, 90 typ, 135 max         100% Duty Cycle       mA       5 min, 200 typ, 280 max         100% Duty Cycle       mA       5 min, 90 typ, 135 max         100% Duty Cycle       mA       85 min, 230 typ, 305 max         100% Duty Cycle       mA       85 min, 230 typ, 305 max         100% Duty Cycle       W       1.025 typ, 2.050 max         100% Duty Cycle       W       1.325 typ, 2.950 max         100% Duty Cycle       W       1.625 typ, 2.950 max         100% Duty Cycle       W       1.625 typ, 2.950 max         100% Duty Cycle       W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0                                           |       |                          |

| • -15V (BU-61559X1)       V       -15.75 min, -14.25 max         • -12V (BU-61559X2)       V       -12.6 min, -11.4 max         Current Drain       mA       85 typ, 170 max         • +5V       mA       5 min, 40 typ, 80 max         25% Duty Cycle       mA       25 min, 80 typ, 130 max         50% Duty Cycle       mA       45 min, 120 typ, 180 max         100% Duty Cycle       mA       85 min, 200 typ, 280 max         • -12V (BU-61559X2)       mA       25 min, 90 typ, 135 max         100% Duty Cycle       mA       25 min, 90 typ, 135 max         50% Duty Cycle       mA       25 min, 90 typ, 135 max         50% Duty Cycle       mA       85 min, 230 typ, 305 max         100% Duty Cycle       mA       85 min, 230 typ, 305 max         100% Duty Cycle       mA       85 min, 230 typ, 305 max         100% Duty Cycle       mA       85 min, 230 typ, 305 max         100% Duty Cycle       W       1.025 typ, 2.050 max         100% Duty Cycle       W       1.325 typ, 2.500 max         50% Duty Cycle       W       1.625 typ, 2.950 max         100% Duty Cycle       W       2.225 typ, 3.850 max         100% Duty Cycle       W       2.225 typ, 1.810 max         100% Duty Cycle </td <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                             |       |                          |

| • -12V (BU-61559X2)       V       -12.6 min, -11.4 max         Current Drain       mA       85 typ, 170 max         • +5V       mA       85 typ, 170 max         • -15V (BU-61559X1)       mA       5 min, 40 typ, 80 max         1dle       mA       5 min, 80 typ, 130 max         50% Duty Cycle       mA       45 min, 120 typ, 180 max         100% Duty Cycle       mA       85 min, 200 typ, 280 max         • -12V (BU-61559X2)       mA       55 min, 40 typ, 80 max         1dle       mA       5 min, 40 typ, 80 max         25% Duty Cycle       mA       85 min, 200 typ, 280 max         50% Duty Cycle       mA       5 min, 90 typ, 135 max         50% Duty Cycle       mA       85 min, 230 typ, 305 max         100% Duty Cycle       mA       85 min, 230 typ, 305 max         100% Duty Cycle       mA       85 min, 230 typ, 305 max         100% Duty Cycle       W       1.025 typ, 2.050 max         1dle       W       1.025 typ, 2.050 max         25% Duty Cycle       W       1.325 typ, 2.950 max         100% Duty Cycle       W       1.225 typ, 2.950 max         100% Duty Cycle       W       2.225 typ, 3.850 max         100% Duty Cycle       W       2.225 typ, 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                             |       |                          |

| Current Drain       Image: Amount of the second of the secon         |                                             |       | <i>'</i>                 |

| • +5V       mA       85 typ, 170 max         • -15V (BU-61559X1)       mA       5 min, 40 typ, 80 max         1dle       mA       5 min, 40 typ, 80 max         25% Duty Cycle       mA       25 min, 80 typ, 130 max         50% Duty Cycle       mA       45 min, 120 typ, 180 max         100% Duty Cycle       mA       85 min, 200 typ, 280 max         • -12V (BU-61559X2)       mA       5 min, 40 typ, 80 max         1dle       mA       5 min, 40 typ, 80 max         25% Duty Cycle       mA       25 min, 90 typ, 135 max         50% Duty Cycle       mA       45 min, 135 typ, 135 max         50% Duty Cycle       mA       85 min, 230 typ, 305 max         100% Duty Cycle       mA       85 min, 230 typ, 305 max         100% Duty Cycle       W       1.025 typ, 2.050 max         * BU-61559X1       U       1.325 typ, 2.500 max         10le       W       1.325 typ, 2.500 max         50% Duty Cycle       W       1.625 typ, 2.950 max         50% Duty Cycle       W       2.225 typ, 3.850 max         100% Duty Cycle       W       2.225 typ, 1.810 max         1dle       W       0.905 typ, 1.810 max         25% Duty Cycle       W       1.025 typ, 2.170 max                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ,                                           | V     | -12.6 min, -11.4 max     |

| • -15V (BU-61559X1)       mA       5 min, 40 typ, 80 max         25% Duty Cycle       mA       25 min, 80 typ, 130 max         50% Duty Cycle       mA       45 min, 120 typ, 180 max         100% Duty Cycle       mA       85 min, 200 typ, 280 max         • -12V (BU-61559X2)       mA       5 min, 40 typ, 80 max         1dle       mA       5 min, 40 typ, 80 max         25% Duty Cycle       mA       5 min, 90 typ, 135 max         50% Duty Cycle       mA       5 min, 90 typ, 135 max         50% Duty Cycle       mA       85 min, 230 typ, 305 max         100% Duty Cycle       mA       85 min, 230 typ, 305 max         POWER DISSIPATION       (see note 7)         Total Hybrid       9       1.025 typ, 2.050 max         9% Duty Cycle       W       1.325 typ, 2.500 max         100% Duty Cycle       W       1.325 typ, 2.950 max         100% Duty Cycle       W       2.225 typ, 3.850 max         100% Duty Cycle       W       2.225 typ, 1.810 max         100% Duty Cycle       W       1.025 typ, 2.170 max         10le       W       0.905 typ, 1.810 max         102% Duty Cycle       W       1.025 typ, 2.470 max         10% Duty Cycle       W       1.025 typ, 2.470 max </td <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                             |       |                          |

| Idle       mA       5 min, 40 typ, 80 max         25% Duty Cycle       mA       25 min, 80 typ, 130 max         50% Duty Cycle       mA       45 min, 120 typ, 180 max         100% Duty Cycle       mA       85 min, 200 typ, 280 max         • -12V (BU-61559X2)       mA       5 min, 40 typ, 80 max         Idle       mA       5 min, 40 typ, 80 max         25% Duty Cycle       mA       5 min, 40 typ, 80 max         50% Duty Cycle       mA       25 min, 90 typ, 135 max         50% Duty Cycle       mA       45 min, 135 typ, 185 max         50% Duty Cycle       mA       85 min, 230 typ, 305 max         POWER DISSIPATION       (see note 7)         Total Hybrid        1.025 typ, 2.050 max         9% Duty Cycle       W       1.325 typ, 2.500 max         100% Duty Cycle       W       1.625 typ, 2.950 max         100% Duty Cycle       W       1.625 typ, 2.950 max         100% Duty Cycle       W       2.225 typ, 3.850 max         • BU-61559X2       W       1.625 typ, 2.170 max         idle       W       0.905 typ, 1.810 max         25% Duty Cycle       W       1.025 typ, 2.170 max         50% Duty Cycle       W       1.025 typ, 2.470 max <tr< td=""><td>-</td><td>mA</td><td>85 typ, 170 max</td></tr<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -                                           | mA    | 85 typ, 170 max          |