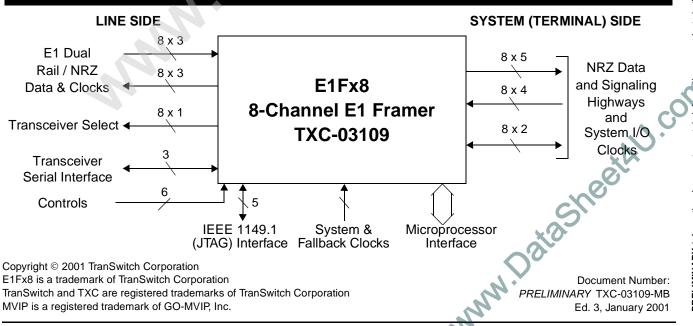

# E1Fx8 Device 8-Channel E1 Framer TXC-03109

# DATA SHEET PRELIMINARY

# **FEATURES**

- Eight-channel offline framer supports standard and frame hold-off frame alignment with CRC-4 multiframe check, selectable out of frame criteria and change of frame alignment alarm, plus transparent non-framing mode

- Frame alignment detection and loss of frame declaration comply with ITU-T G.706 /ETS 300 011

- Dual unipolar (HDB3/AMI) or NRZ line interface

- Fractional E1; gapped clock or marker and aux. Tx Input

Clock data and frame pulse can be manifered for any 51

- Clock, data, and frame pulse can be monitored for any E1

Two-frame slip buffers in both receive and transmit directions with delay measurements

- Supports Time Slot 16 CCS/CAS signaling (CAS debounced /processor-forced on a per time slot basis)

- Detects and forces Time Slots 0 and 16 RAI and AIS; detects LOS, OOF, OOMF, OOMF16, and AUX pattern

- Detects, counts and forces line code errors (BPVs and excess zeros), CRC-4 errors, frame word errors, and CRC errors (E-bits, 2 Sa6 code counters)

- Motorola/Intel-compatible microprocessor interface

- Auxiliary port with TSI for ITU-T G.964/5 (V5.1/2)

- One-second interrupt input latches counter values and line events into shadow registers

- Local, line remote, payload remote and time slot loopbacks with ANSI T1.231 Fractional T1 compatible loopback support

- Per framer PRBS/code word generator and analyzer for E1 and N x time slot testing

- Four system interface options: Transmission, Data, MVIP, and H-MVIP/H.100 plus dual reference clock outputs

- ETS 300 011, 300 233 and ITU-T I.431 ISDN support

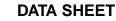

- Boundary scan capability (IEEE 1149.1)

- Single +3.3V power supply; 5 volt tolerant TTL inputs

- 208-lead or 256-lead plastic ball grid array package

# DESCRIPTION

The E1Fx8 is an eight-channel E1 (2048 kbit/s) framer designed with extended features for voice and data communications applications. AMI and HDB3 line codes are supported with full alarm detection and generation per ITU-T G.703, G.775 and I.431. Integral receive dual unipolar rail dejitter buffers (ITU-T G.735-739 and G.823) are provided. The transmit and receive sections of each of the eight framers are independent, including framing, with individual slip buffers to allow operation in a wide range of switching and transmission products. Framing algorithm support for ITU-T G.704, G.706 and ETS 300 011 is included. Access and control for signaling and data are provided via a Motorola/Intel-compatible microprocessor interface. For HDLC link applications, each framer supplies a full duplex HDLC controller with dual 128-byte FIFOs (for Sa4-Sa8 access) in addition to onboard latching of all performance parameters, requiring minimal software overhead. Word-wide National bit read/write access is provided, with full Sa6 code support. Diagnostic, test, and maintenance functions are integrated, including E1 and per time slot local and remote loopback modes, per channel PRBS/code word generator/analyzer and boundary scan (IEEE 1149.1).

# **APPLICATIONS**

- SDH terminal or add/drop multiplexers supporting E1 bytesynchronous operation or E1 monitoring with G.706 annex C

- DCS, digital central office or remote digital terminals (exchange terminations and access nodes)

- E1 multiplexers

- E1 and fractional E1 CSUs

- ATM products with integrated E1 interfaces

- LAN routers with integrated E1 interfaces

- Multichannel E1 test equipment

- Internet access equipment with E1 and Fractional E1 ports

TranSwitch Corporation • 3 Enterprise Drive • Shelton, Connecticut 06484 • USA Tel: 203-929-8810 • Fax: 203-926-9453 • www.transwitch.com PRELIMINARY information documents contain information on products in the sampling, pre-production or early production phases of the product life cycle. Proprietar Characteristic data and other specifications are subject to change. Contact TranSwitch Applications Engineering for current information on this product.

# TABLE OF CONTENTS

| Section                                                | Page |

|--------------------------------------------------------|------|

| List of Figures                                        | 3    |

| Overview                                               | 5    |

| Features                                               | 7    |

| Reference Documents                                    | 14   |

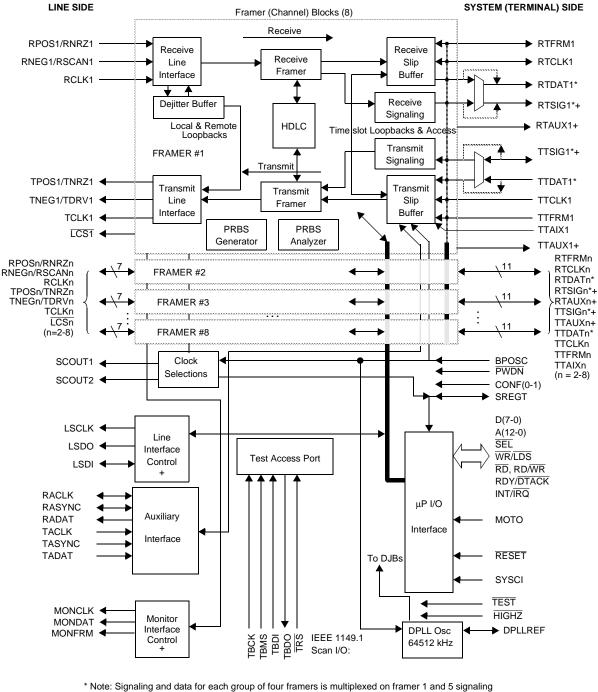

| Block Diagram                                          | 15   |

| Block Diagram Description                              | 16   |

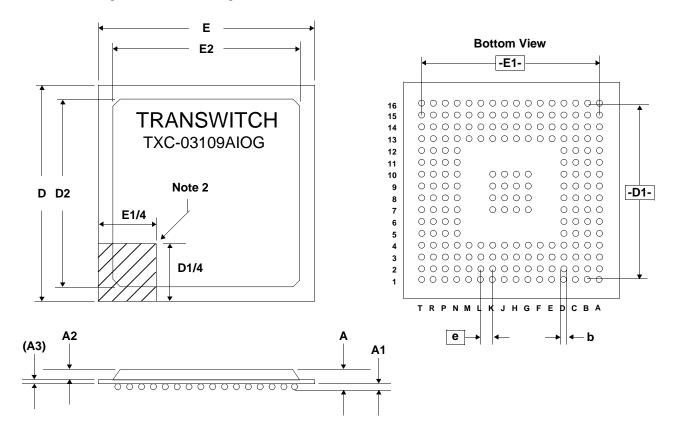

| Lead Diagram For 208-lead PBGA Package                 | 22   |

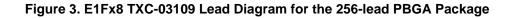

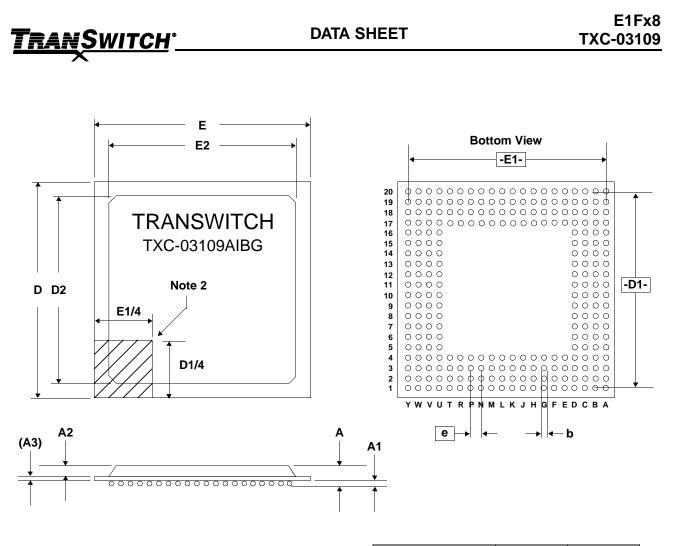

| Lead Diagram For 256-lead PBGA Package                 | 23   |

| Lead Descriptions                                      | 24   |

| Absolute Maximum Ratings and Environmental Limitations | 42   |

| Thermal Characteristics                                | 42   |

| Power Requirements                                     | 42   |

| Input, Output and Input/Output Parameters              | 43   |

| Timing Characteristics                                 | 45   |

| Operation                                              | 79   |

| Line Interface Selection                               | 79   |

| Receive Dejitter Buffer                                | 81   |

| Line Interface Control                                 | 84   |

| Monitor Mode                                           | 85   |

| System Interface                                       | 86   |

| Transmission Mode                                      | 87   |

| Data Mode                                              | 93   |

| MVIP Mode                                              | 97   |

| H-MVIP/H.100 Mode                                      | 100  |

| Framing                                                | 102  |

| Frame Alignment                                        | 103  |

| Transmit Framer                                        | 108  |

| Slip Buffers                                           | 115  |

| Delay                                                  | 118  |

| Signaling                                              | 118  |

| Clocking and Synchronization                           | 124  |

| AIS Generation and Detection                           | 126  |

| Auxiliary Pattern Generation and Detection             | 126  |

| HDLC Channel                                           | 126  |

| Global Microprocessor Controls and Alarms              | 130  |

| Maintenance                                            | 133  |

| PRBS Generator and Analyzer                            | 139  |

| E1 Tandem Framing Monitoring Function                  | 145  |

| Auxiliary Port                                         | 145  |

| Boundary Scan                                          | 147  |

| Reset Procedure                                        |      |

| Memory Map                                             |      |

| Common Registers                                       |      |

| Per Channel Control and Status Indication Registers    |      |

| Spare and Reserved Registers                           |      |

# **TABLE OF CONTENTS (continued)**

| Section                                 | Page |

|-----------------------------------------|------|

| Memory Map Descriptions                 | 179  |

| Common Registers                        | 179  |

| Per Channel Registers                   | 195  |

| Application Diagrams                    | 272  |

| Package Information                     | 273  |

| Ordering Information                    | 275  |

| Related Products                        | 275  |

| Standards Documentation Sources         | 277  |

| List of Data Sheet Changes              | 279  |

| Documentation Update Registration Form* | 283  |

\* Please note that TranSwitch provides documentation for all of its products. Customers who are using a TranSwitch Product, or planning to do so, should register with the TranSwitch Marketing Department to receive relevant updated and supplemental documentation as it is issued. They should also contact the Applications Engineering Department to ensure that they are provided with the latest available information about the product, especially before undertaking development of new designs incorporating the product.

# **LIST OF FIGURES**

| Figu | ire Pa                                                                           | age  |

|------|----------------------------------------------------------------------------------|------|

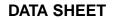

| 1.   | E1Fx8 TXC-03109 Block Diagram                                                    | . 15 |

| 2.   | E1Fx8 TXC-03109 Lead Diagram for the 208-lead PBGA Package                       | . 22 |

| 3.   | E1Fx8 TXC-03109 Lead Diagram for the 256-lead PBGA Package                       | . 23 |

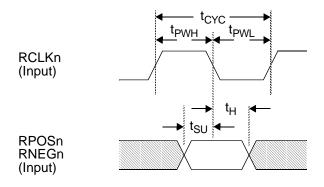

| 4.   | Dual Unipolar (RAIL) Receive Interface Timing                                    | . 45 |

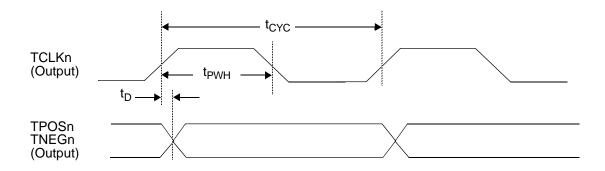

| 5.   | Dual Unipolar (RAIL) Transmit Interface Timing                                   | . 46 |

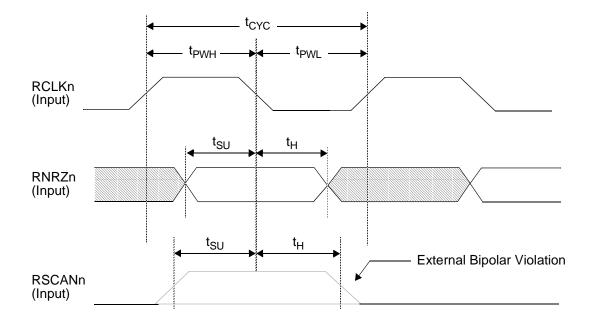

| 6.   | NRZ Receive Interface Timing (External Transceiver)                              |      |

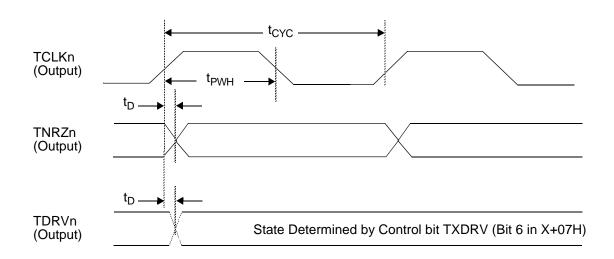

| 7.   | NRZ Transmit Interface Timing (External Transceiver)                             | . 48 |

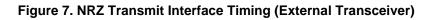

| 8.   | NRZ Receive Interface Timing (Fast Sync Mode)                                    | . 49 |

| 9.   | NRZ Transmit Interface Timing (Fast Sync Mode)                                   | . 50 |

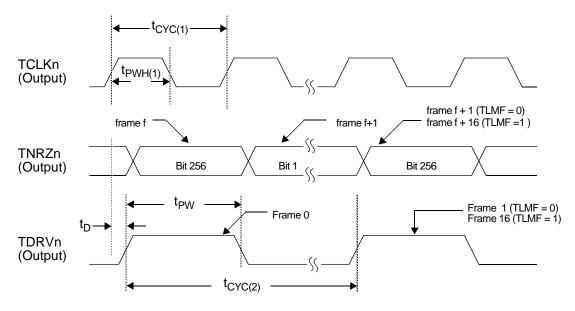

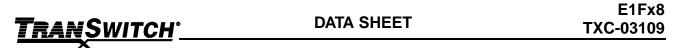

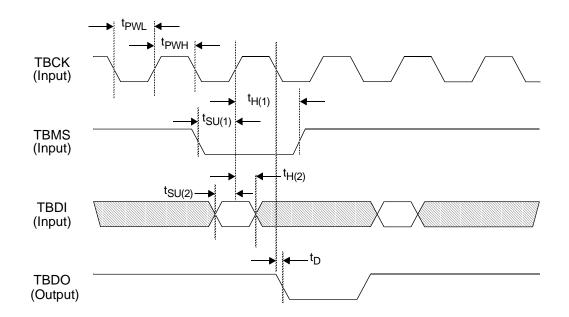

| 10.  | Serial Port Write Timing                                                         | . 51 |

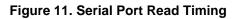

| 11.  | Serial Port Read Timing                                                          | . 52 |

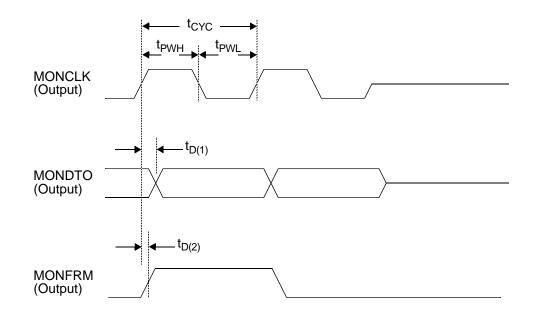

| 12.  | Monitor Mode Timing                                                              | . 53 |

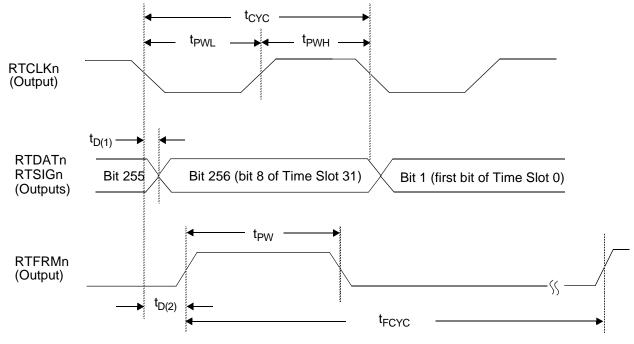

| 13.  | Receive Highway Timing - Transmission Mode (Recovered Receive Line Clock)        | . 54 |

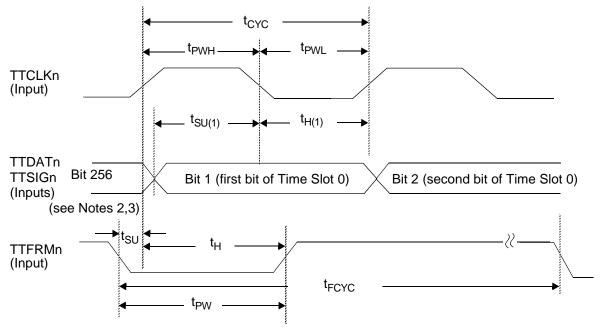

| 14.  | Receive Highway Timing - Transmission Mode (System Clock)                        | . 55 |

| 15.  | Transmit Highway Timing - Transmission Mode                                      | . 56 |

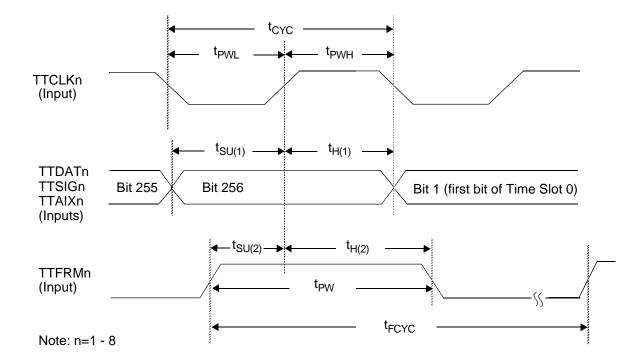

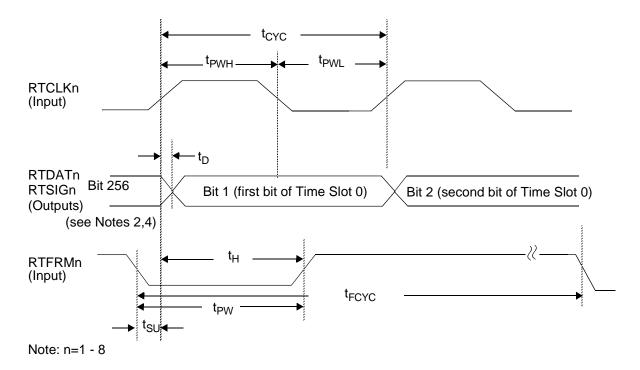

| 16.  | Receive Highway Timing - Data Mode (Recovered Receive Line Clock)                | . 57 |

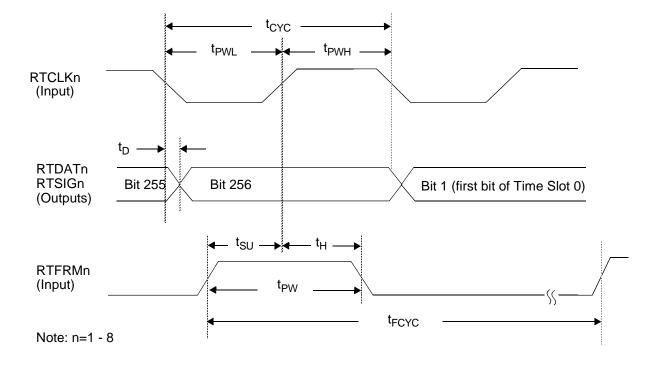

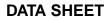

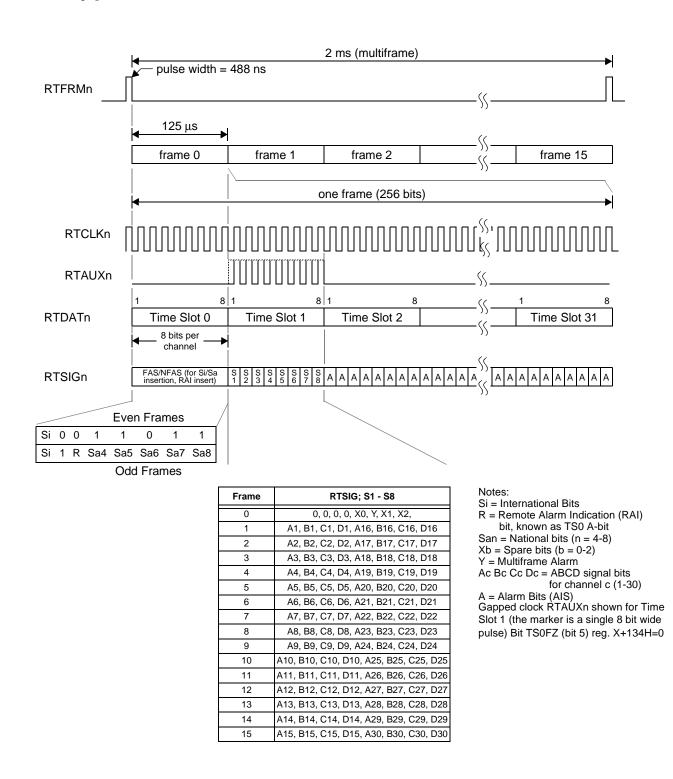

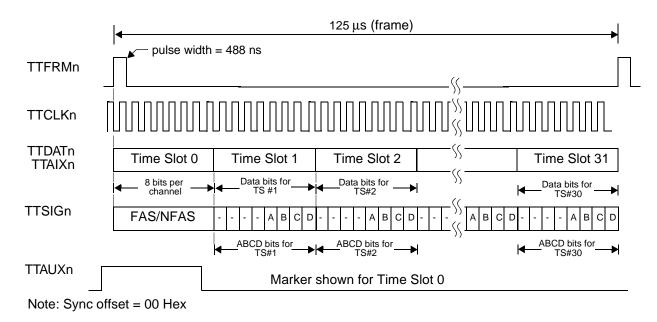

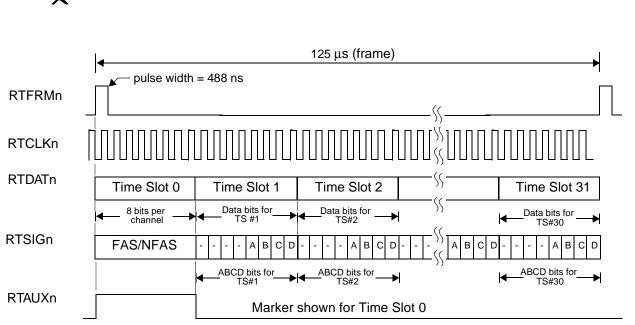

| 17.  | Receive Highway Timing - Data Mode (System Clock)                                | . 58 |

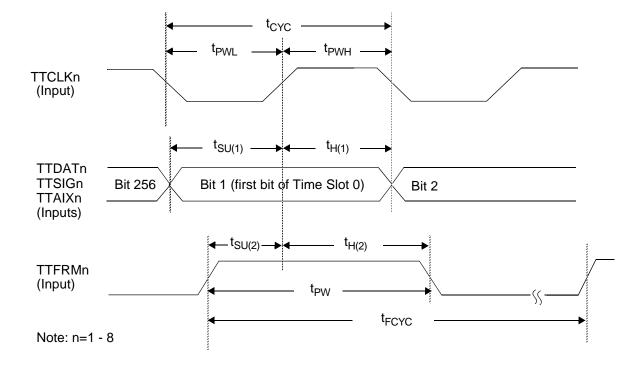

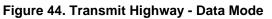

| 18.  | Transmit Highway Timing - Data Mode                                              | . 59 |

| 19.  | Receive Highway Timing - MVIP Mode                                               | . 60 |

| 20.  | Transmit Highway Timing - MVIP Mode                                              | . 61 |

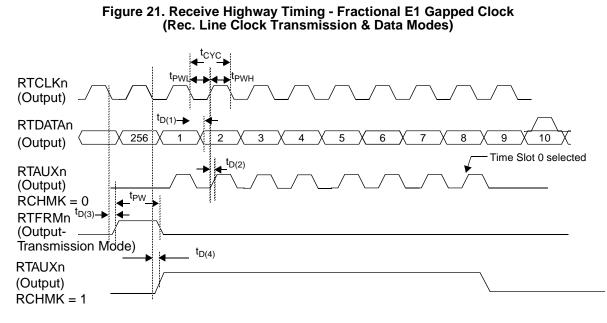

| 21.  | Receive Highway Timing - Fractional E1 Gapped Clock                              |      |

|      | (Rec. Line Clock Transmission & Data Modes)                                      | . 62 |

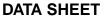

| 22.  | Receive Highway Timing - Fractional E1 Gapped Clock                              |      |

| ~~   | (System Clock Transmission & Data Modes)                                         |      |

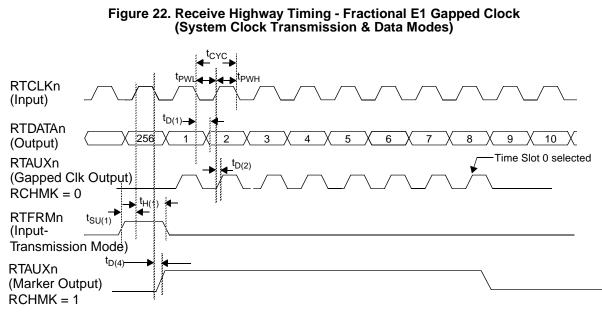

| 23.  | Transmit Highway Timing - Fractional E1 Gapped Clock (Transmission & Data Modes) |      |

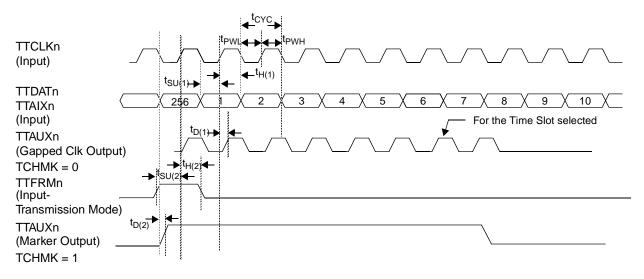

| 24.  | Receive Highway Timing - 8 Mbit/s H-MVIP/ H.100 Mode                             |      |

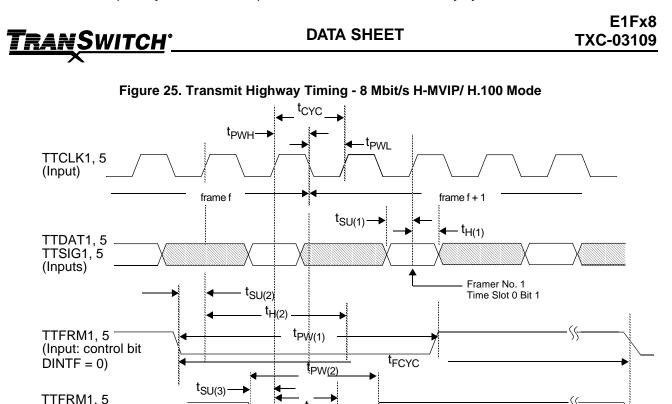

| 25.  | Transmit Highway Timing - 8 Mbit/s H-MVIP/ H.100 Mode                            | . 66 |

# LIST OF FIGURES (continued)

| 26.       Shadow Register Timing       67         77.       DPLL Reference Input/Output Timing       67         88.       Intel Microprocessor Read Cycle Timing       68         90.       Intel Microprocessor Write Cycle Timing       70         11.       Motorola Microprocessor Write Cycle Timing       70         23.       Clock Reference Timing       71         24.       Auxiliary Port Receive Timing (Clock Master)       75         35.       Auxiliary Port Receive Timing (Clock Master)       76         36.       Auxiliary Port Transmit Timing (Clock Master)       76         37.       Auxiliary Port Transmit Timing (Clock Master)       77         38.       Line Interface For NRZ Mode       81         40.       E1Fx8 Jitter Transfer Characteristics       83         41.       Transmit Highway - Transmission Mode       92         42.       Transmit Highway - Transmission Mode       92         43.       Receive Highway - Data Mode       94         44.       Transmit Highway - VIP Mode       98         47.       Receive Highway - NVIP Mode       98         48.       Transmit Highway - WIP Mode       98         47.       Receive Highway - MVIP Mode       98         4                                                                                         | Figu | Ire                                                                | Page |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------------------------------------------------------|------|

| 28.       Boundary Scan Timing       68         29.       Intel Microprocessor Read Cycle Timing       69         30.       Intel Microprocessor Write Cycle Timing       70         31.       Motorola Microprocessor Write Cycle Timing       71         32.       Clock Reference Timing       72         33.       Clock Reference Timing (Clock Slave)       75         34.       Auxiliary Port Receive Timing (Clock Master)       76         35.       Auxiliary Port Transmit Timing (Clock Master)       76         36.       Line Interface For NRZ Mode       81         40.       E1Fx8 Jitter Transfer Characteristics       83         41.       Transmit Highway - Transmission Mode       92         42.       Transmit Highway - Transmission Mode       92         43.       Receive Highway - Transmission Mode       94         44.       Transmit Highway - Data Mode       94         57.       Receive Highway - MVIP Mode       98         47.       Receive Highway - MVIP Mode       98         47.       Receive Jighuay - MVIP Mode       116         58.       Receive Signaling Buffer       116         59.       Shadow Register Operation       132         50.       Iransmit S                                                                                                  | 26.  | Shadow Register Timing                                             | 67   |

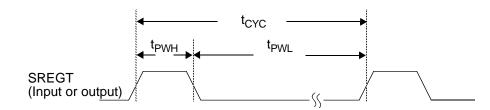

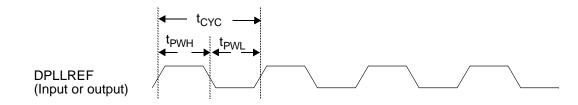

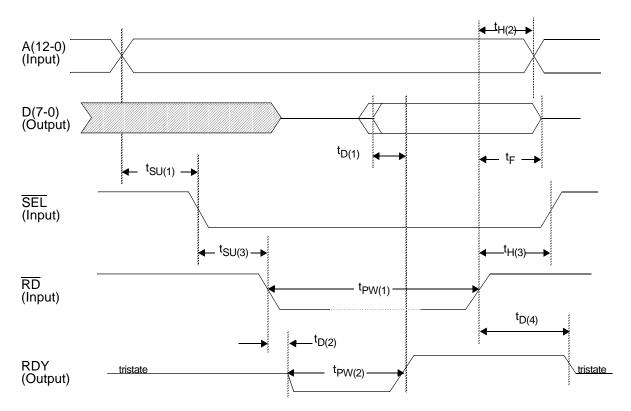

| 29.       Intel Microprocessor Read Cycle Timing       69         30.       Intel Microprocessor Write Cycle Timing       70         31.       Motorola Microprocessor Read Cycle Timing       71         32.       Clock Reference Timing       72         33.       Clock Reference Timing       74         44.       Auxiliary Port Receive Timing (Clock Slave)       75         55.       Auxiliary Port Transmit Timing (Clock Master)       76         64.       Auxiliary Port Transmit Timing (Clock Master)       77         74.       Auxiliary Port Transmit Timing (Clock Master)       77         75.       Auxiliary Port Transmit Timing (Clock Master)       78         10.       E1Fx8 Jitter Transfer Characteristics       83         31.       Transceiver Serial I/O Timing       84         42.       Transmit Highway - Transmission Mode       92         43.       Receive Highway - Transmission Mode       94         44.       Receive Highway - Data Mode       94         45.       Receive Highway - MVIP Mode       98         46.       Transmit Data and Signaling Highways - 8 Mbit/s H-MVIP/H.100 Modes       101         50.       Transmit Signaling Buffer       116         51.       Transmit Signaling Buffer                                                            | 27.  | DPLL Reference Input/Output Timing                                 | 67   |

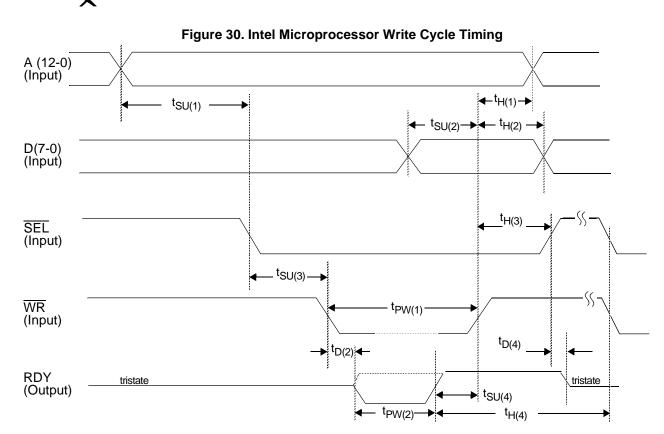

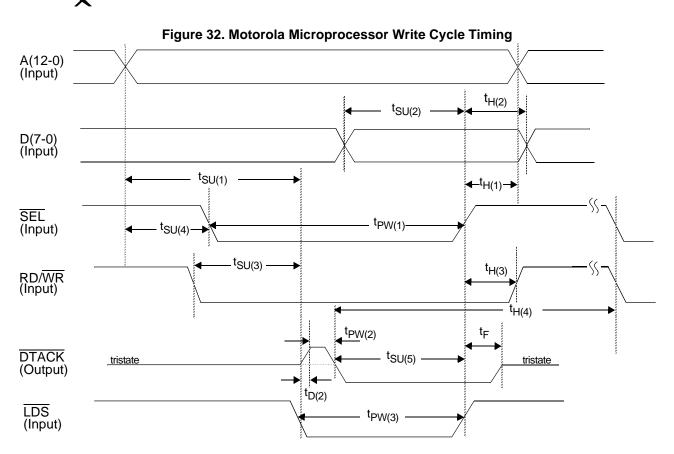

| 30.       Intel Microprocessor Write Cycle Timing       70         31.       Motorola Microprocessor Read Cycle Timing.       71         32.       Motorola Microprocessor Write Cycle Timing       72         33.       Cicck Reference Timing       74         34.       Auxiliary Port Receive Timing (Clock Slave)       75         35.       Auxiliary Port Transmit Timing (Clock Master)       76         36.       Auxiliary Port Transmit Timing (Clock Master)       78         38.       Line Interface For Dual Unipolar Mode       79         39.       Line Interface For NRZ Mode       81         40.       E1Fx8 Jitter Transfer Characteristics       83         41.       Transmit Highway - Transmission Mode       89         31.       Transmit Highway - Transmission Mode       92         42.       Transmit Highway - Transmission Mode       92         43.       Receive Highway - Data Mode       94         44.       Transmit Highway - Data Mode       94         45.       Receive Highway - Mode       98         46.       Transmit Highway - Mode       98         47.       Receive Bignaling Highways - 8 Mbit/s H-MVIP/H 100 Modes       101         54.       Receive Bigna Mig Buffer       116 <td>28.</td> <td>Boundary Scan Timing</td> <td> 68</td>                    | 28.  | Boundary Scan Timing                                               | 68   |

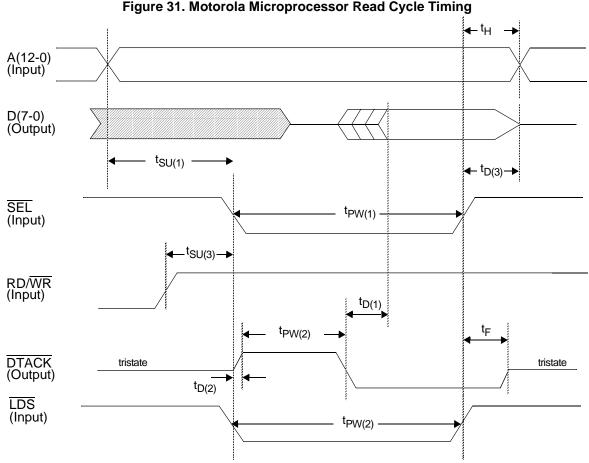

| 31.       Motorola Microprocessor Read Cycle Timing.       71         32.       Motorola Microprocessor Write Cycle Timing.       72         33.       Clock Reference Timing       74         44.       Auxiliary Port Receive Timing (Clock Slave).       75         55.       Auxiliary Port Receive Timing (Clock Master)       76         34.       Auxiliary Port Transmit Timing (Clock Master)       76         35.       Line Interface For Dual Unipolar Mode.       79         36.       Line Interface For NRZ Mode       81         40.       E1Fx8 Jitter Transfer Characteristics       83         41.       Transmit Highway - Transmission Mode       84         42.       Transmit Highway - Transmission Mode       92         43.       Receive Highway - Transmission Mode       94         44.       Transmit Highway - Data Mode       94         45.       Receive Highway - Data Mode       98         46.       Transmit Data and Signaling Highways - 8 Mbit/s H-MVIP/H.100 Modes       100         47.       Receive Highway - MVIP Mode       99         48.       Receive Bignaling Buffer       116         51.       Receive Signaling Buffer       121         52.       Shadow Register Operation       132                                                                       | 29.  | Intel Microprocessor Read Cycle Timing                             | 69   |

| 32.       Motorola Microprocessor Write Cycle Timing       72         33.       Clock Reference Timing (Clock Slave)       75         34.       Auxiliary Port Receive Timing (Clock Slave)       75         35.       Auxiliary Port Receive Timing (Clock Master)       76         36.       Auxiliary Port Transmit Timing (Clock Master)       77         37.       Auxiliary Port Transmit Timing (Clock Master)       78         38.       Line Interface For Dual Unipolar Mode.       79         39.       Line Interface For NRZ Mode.       81         41.       E1Fx8 Jitter Transfer Characteristics       83         42.       Transmit Highway - Transmission Mode       89         39.       Receive Serial I/O Timing       84         42.       Transmit Highway - Data Mode       92         43.       Receive Highway - Data Mode       94         44.       Receive Highway - MVIP Mode       98         47.       Rasmit Data and Signaling Highways - 8 Mbit/s H-MVIP/H.100 Modes       100         48.       Receive Lipt And Signaling Highways - 8 Mbit/s H-MVIP/H.100 Modes       101         50.       Transmit Signaling Highways - 8 Mbit/s H-MVIP/H.100 Modes       101         51.       Transmit Signaling Highways - 8 Mbit/s H-MVIP/H.100 Modes       101                         | 30.  | Intel Microprocessor Write Cycle Timing                            | 70   |

| 33.       Clock Reference Timing       74         34.       Auxiliary Port Receive Timing (Clock Slave)       75         35.       Auxiliary Port Transmit Timing (Clock Master)       76         36.       Auxiliary Port Transmit Timing (Clock Master)       77         77.       Auxiliary Port Transmit Timing (Clock Master)       78         38.       Line Interface For Dual Unipolar Mode.       79         39.       Line Interface For NRZ Mode.       81         40.       E1Fx8 Jitter Transfer Characteristics       83         41.       Transmit Highway - Transmission Mode       89         37.       Receive Highway - Transmission Mode       92         44.       Transmit Highway - Data Mode       94         57.       Receive Highway - Data Mode       96         66.       Transmit Highway - MVIP Mode       98         77.       Receive Highway - MVIP Mode       99         88.       Receive Highway - MVIP Mode       99         98.       Transmit Data and Signaling Highways - 8 Mbit/s H-MVIP/H.100 Modes       100         99.       Transmit Signaling Buffer       116         91.       Receive Signaling Buffer       112         92.       Transmit Signaling Buffer       122                                                                                          | 31.  | Motorola Microprocessor Read Cycle Timing                          | 71   |

| 34.       Auxiliary Port Receive Timing (Clock Slave)       75         35.       Auxiliary Port Receive Timing (Clock Master)       76         36.       Auxiliary Port Transmit Timing (Clock Master)       77         37.       Auxiliary Port Transmit Timing (Clock Master)       78         38.       Line Interface For Dual Unipolar Mode       79         39.       Line Interface For NRZ Mode       81         40.       E1Fx8 Jitter Transfer Characteristics       83         41.       Transmit Highway - Transmission Mode       89         42.       Transmit Highway - Transmission Mode       92         43.       Receive Highway - Data Mode       92         44.       Receive Highway - Data Mode       94         45.       Receive Highway - MVIP Mode       98         47.       Raceive Highway - MVIP Mode       98         47.       Receive Data and Signaling Highways - 8 Mbit/s H-MVIP/H.100 Modes       100         48.       Receive Data and Signaling Highways - 8 Mbit/s H-MVIP/H.100 Modes       101         59.       Transmit Slip Buffer       116         51.       Receive Slip Buffer       122         54.       HDLC Format       122         55.       Shadow Register Operation       132 <td>32.</td> <td>Motorola Microprocessor Write Cycle Timing</td> <td></td> | 32.  | Motorola Microprocessor Write Cycle Timing                         |      |

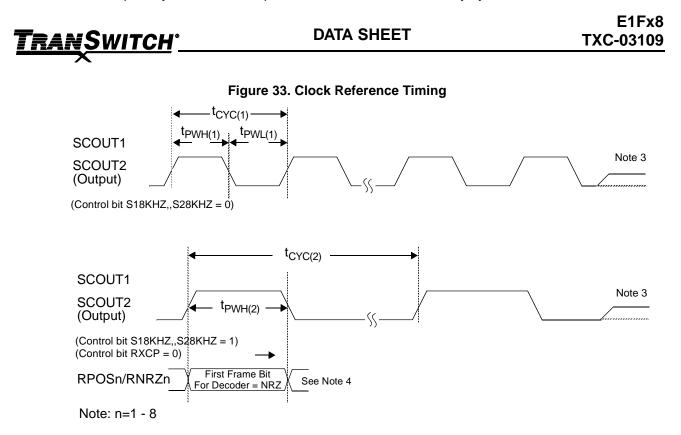

| 35.       Auxiliary Port Receive Timing (Clock Master)       76         36.       Auxiliary Port Transmit Timing (Clock Slave)       77         37.       Auxiliary Port Transmit Timing (Clock Master)       78         38.       Line Interface For Dual Unipolar Mode.       79         39.       Line Interface For NRZ Mode       81         40.       E1Fx8 Jitter Transfer Characteristics       83         41.       Transmit Highway - Transmission Mode       89         42.       Transmit Highway - Transmission Mode       92         43.       Receive Highway - Transmission Mode       94         44.       Receive Highway - Data Mode       94         45.       Receive Highway - MVIP Mode       98         46.       Transmit Highway - MVIP Mode       98         47.       Receive Highway - MVIP Mode       98         48.       Receive Highway - MVIP Mode       98         47.       Receive Bighuffer       110         51.       Receive Bignaling Highways - 8 Mbit/s H-MVIP/H.100 Modes       100         52.       Iransmit Signaling Highways - 8 Mbit/s H-MVIP/H.100 Modes       101         53.       Transmit Signaling Buffer       116         54.       HDLC Format       122 <t< td=""><td>33.</td><td>Clock Reference Timing</td><td></td></t<>                            | 33.  | Clock Reference Timing                                             |      |

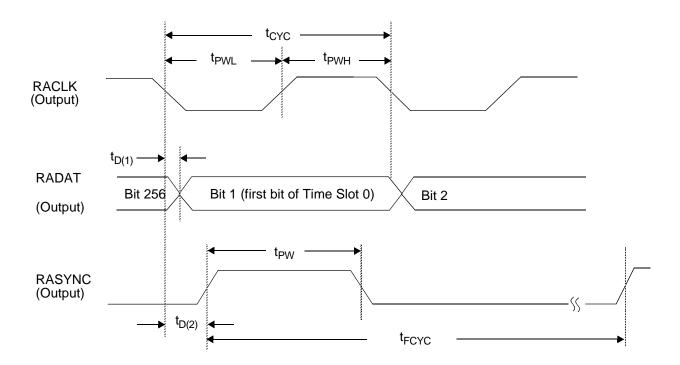

| 36.       Auxiliary Port Transmit Timing (Clock Slave)       77         37.       Auxiliary Port Transmit Timing (Clock Master)       78         38.       Line Interface For Dual Unipolar Mode.       79         39.       Line Interface For NRZ Mode       81         40.       E1Fx8 Jitter Transfer Characteristics       83         41.       Transceiver Serial I/O Timing       84         42.       Transmit Highway - Transmission Mode       92         43.       Receive Highway - Transmission Mode       92         44.       Transmit Highway - Data Mode       94         56.       Receive Highway - Data Mode       94         66.       Transmit Highway - Data Mode       98         77.       Receive Highway - WIP Mode       98         78.       Receive Highway - WIP Mode       99         77.       Receive Data and Signaling Highways - 8 Mbit/s H-MVIP/H.100 Modes       100         99.       Receive Bip Buffer       116         51.       Receive Bip Buffer       122         54.       HDLC Format       126         55.       Shadow Register Operation       132         56.       Local Loopback       133         57.       Remote Line Loopback       134                                                                                                                 | 34.  | Auxiliary Port Receive Timing (Clock Slave)                        | 75   |

| 37.       Auxiliary Port Transmit Timing (Clock Master)       78         38.       Line Interface For Dual Unipolar Mode.       79         39.       Line Interface For NRZ Mode       81         40.       E1Fx8 Jitter Transfer Characteristics       83         41.       Transmit Highway - Transmission Mode       89         42.       Transmit Highway - Transmission Mode       89         43.       Receive Highway - Transmission Mode       92         44.       Transmit Highway - Data Mode       94         45.       Receive Highway - Data Mode       96         46.       Transmit Highway - MVIP Mode       98         47.       Receive Highway - MVIP Mode       98         48.       Transmit Data and Signaling Highways - 8 Mbit/s H-MVIP/H.100 Modes       100         49.       Receive Bighway - MVIP Mode       99         40.       Transmit Silp Buffer       116         51.       Receive Data and Signaling Highways - 8 Mbit/s H-MVIP/H.100 Modes       100         40.       Transmit Silp Buffer       111         52.       Receive Signaling Buffer       122         53.       Stadow Register Operation       132         54.       HDLC Format       126         55. <td< td=""><td>35.</td><td>Auxiliary Port Receive Timing (Clock Master)</td><td></td></td<>            | 35.  | Auxiliary Port Receive Timing (Clock Master)                       |      |

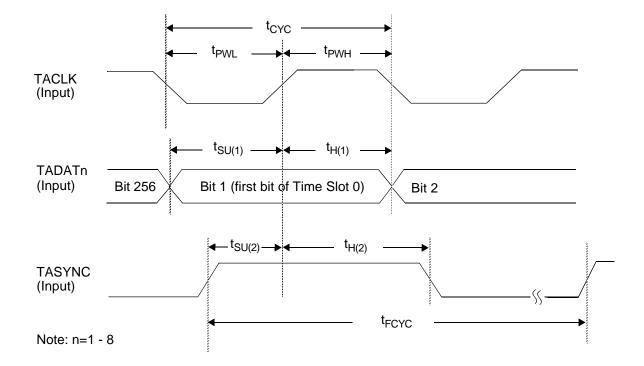

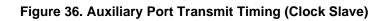

| 38.       Line Interface For Dual Unipolar Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 36.  | Auxiliary Port Transmit Timing (Clock Slave)                       | 77   |

| 39.       Line Interface For NRZ Mode       81         40.       E1Fx8 Jitter Transfer Characteristics       83         41.       Transceiver Serial I/O Timing       84         42.       Transmit Highway - Transmission Mode       89         43.       Receive Highway - Transmission Mode       92         44.       Transmit Highway - Data Mode       94         45.       Receive Highway - Data Mode       96         46.       Transmit Highway - MVIP Mode       98         47.       Receive Highway - MVIP Mode       98         48.       Transmit Data and Signaling Highways - 8 Mbit/s H-MVIP/H.100 Modes       100         49.       Receive Data and Signaling Highways - 8 Mbit/s H-MVIP/H.100 Modes       101         50.       Transmit Sip Buffer       116         51.       Receive Sip Buffer       112         52.       Receive Sip Buffer       122         54.       HDLC Format       126         55.       Shadow Register Operation       132         56.       Local Loopback       133         57.       Remote Line Loopback       134         58.       Di Transmit Sion Remote and Payload Loopbacks       135         60.       Transe Siot Remote and Payload Loopbacks <td>37.</td> <td>Auxiliary Port Transmit Timing (Clock Master)</td> <td></td>                       | 37.  | Auxiliary Port Transmit Timing (Clock Master)                      |      |

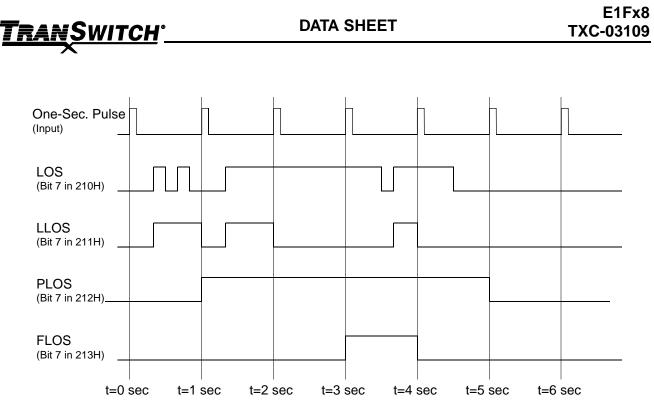

| 40.       E1Fx8 Jitter Transfer Characteristics       83         41.       Transceiver Serial I/O Timing       84         42.       Transmit Highway - Transmission Mode       89         43.       Receive Highway - Transmission Mode       92         44.       Transmit Highway - Data Mode       92         44.       Transmit Highway - Data Mode       94         45.       Receive Highway - Data Mode       96         46.       Transmit Highway - Data Mode       98         47.       Receive Highway - MVIP Mode       98         48.       Transmit Data and Signaling Highways - 8 Mbit/s H-MVIP/H.100 Modes       100         49.       Receive Data and Signaling Highways - 8 Mbit/s H-MVIP/H.100 Modes       101         50.       Transmit Slip Buffer       116         51.       Receive Signaling Buffer       122         54.       HDLC Format       126         55.       Shadow Register Operation       132         56.       Local Loopback       133         57.       Remote Line Loopback       134         58.       Di Crormat       136         61.       DSO remote Loopback       136         62.       PRBS/ Code Word Generator/ Analyzer Options with Loopbacks                                                                                                             | 38.  | Line Interface For Dual Unipolar Mode                              |      |

| 41.       Transceiver Serial I/O Timing       84         42.       Transmit Highway - Transmission Mode       89         43.       Receive Highway - Transmission Mode       92         44.       Transmit Highway - Data Mode       92         44.       Transmit Highway - Data Mode       94         45.       Receive Highway - Data Mode       96         46.       Transmit Highway - MVIP Mode       98         47.       Receive Highway - MVIP Mode       99         48.       Transmit Data and Signaling Highways - 8 Mbit/s H-MVIP/H.100 Modes       100         49.       Receive Data and Signaling Highways - 8 Mbit/s H-MVIP/H.100 Modes       101         50.       Transmit Slip Buffer       116         51.       Receive Data and Signaling Highways - 8 Mbit/s H-MVIP/H.100 Modes       101         52.       Receive Signaling Buffer       112         53.       Transmit Signaling Buffer       121         54.       HDLC Format       126         55.       Shadow Register Operation       132         56.       Local Loopback       133         57.       Remote Line Loopback       136         58.       Di Time Slot Remote and Payload Loopbacks       136         59.       Tim                                                                                                  | 39.  | Line Interface For NRZ Mode                                        | 81   |

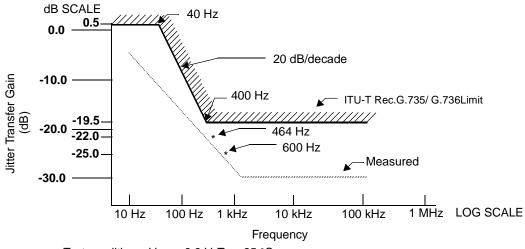

| 42.       Transmit Highway - Transmission Mode       89         43.       Receive Highway - Transmission Mode       92         44.       Transmit Highway - Data Mode       94         45.       Receive Highway - Data Mode       96         46.       Transmit Highway - MVIP Mode       98         47.       Receive Highway - MVIP Mode       99         48.       Transmit Data and Signaling Highways - 8 Mbit/s H-MVIP/H.100 Modes       100         49.       Receive Data and Signaling Highways - 8 Mbit/s H-MVIP/H.100 Modes       101         50.       Transmit Slip Buffer       116         51.       Receive Slip Buffer       117         52.       Receive Signaling Buffer       122         54.       HDLC Format       126         55.       Shadow Register Operation       132         56.       Local Loopback       133         57.       Remote Line Loopback       134         58.       Di remote and Payload Loopbacks       136         61.       DS0 remote Loopback Code Sequence Generator       136         62.       PRBS/ Code Word Generator/ Analyzer Options with Loopbacks       142         63.       Tandem Frame Monitoring with National Bit Insertion       145         64. <td>40.</td> <td>E1Fx8 Jitter Transfer Characteristics</td> <td> 83</td>                   | 40.  | E1Fx8 Jitter Transfer Characteristics                              | 83   |

| 43.       Receive Highway - Transmission Mode       92         44.       Transmit Highway - Data Mode       94         45.       Receive Highway - Data Mode       96         46.       Transmit Highway - MVIP Mode       98         47.       Receive Highway - MVIP Mode       99         48.       Transmit Data and Signaling Highways - 8 Mbit/s H-MVIP/H.100 Modes       100         49.       Receive Data and Signaling Highways - 8 Mbit/s H-MVIP/H.100 Modes       101         50.       Transmit Slip Buffer       116         51.       Receive Signaling Buffer       112         52.       Receive Signaling Buffer       122         54.       HDLC Format       126         55.       Shadow Register Operation       132         56.       Local Loopback       133         57.       Remote Line Loopback       134         58.       Bi-Directional Loopback       135         60.       Time Slot Remote and Payload Loopbacks       136         61.       DS0 remote Loopback       136         62.       PRBS/ Code Word Generator/ Analyzer Options with Loopbacks       142         63.       Tandem Frame Monitoring with National Bit Insertion       145         64.       Auxiliary P                                                                                                  | 41.  | Transceiver Serial I/O Timing                                      | 84   |

| 44.       Transmit Highway - Data Mode       94         45.       Receive Highway - Data Mode       96         45.       Transmit Highway - MVIP Mode       98         47.       Receive Highway - MVIP Mode       99         48.       Transmit Data and Signaling Highways - 8 Mbit/s H-MVIP/H.100 Modes       100         49.       Receive Data and Signaling Highways - 8 Mbit/s H-MVIP/H.100 Modes       101         50.       Transmit Slip Buffer       116         51.       Receive Signaling Buffer       121         52.       Receive Signaling Buffer       122         54.       HDLC Format       126         55.       Shadow Register Operation       132         56.       Local Loopback       133         57.       Remote Line Loopback       134         58.       Bi-Directional Loopback       134         59.       Time Slot Remote and Payload Loopbacks       135         60.       DS0 remote Loopback       136         61.       DS0 remote Loopback Code Sequence Generator       136         62.       PRBS/ Code Word Generator/ Analyzer Options with Loopbacks       142         63.       Tandem Frame Monitoring with National Bit Insertion       145         64.       Au                                                                                                  | 42.  | Transmit Highway - Transmission Mode                               | 89   |

| 45.       Receive Highway - Data Mode       96         46.       Transmit Highway - MVIP Mode       98         47.       Receive Highway - MVIP Mode       99         48.       Transmit Data and Signaling Highways - 8 Mbit/s H-MVIP/H.100 Modes       100         49.       Receive Data and Signaling Highways - 8 Mbit/s H-MVIP/H.100 Modes       101         50.       Transmit Slip Buffer       116         51.       Receive Signaling Buffer       121         53.       Transmit Signaling Buffer       122         54.       HDLC Format       126         55.       Shadow Register Operation       132         56.       Local Loopback       133         57.       Remote Line Loopback       134         58.       Di Perceional Loopback       136         61.       DS0 remote Loopback       136         62.       PRBS/ Code Word Generator/ Analyzer Options with Loopbacks       142         63.       Tandem Frame Monitoring with National Bit Insertion       145         64.       Auxiliary Port Connections       146         65.       Boundary Scan Schematic       148         66.       Boundary Scan Schematic       148         67.       E1Fx8 TXC-03109 208-Lead Plastic Ball                                                                                                   | 43.  | Receive Highway - Transmission Mode                                |      |

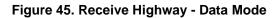

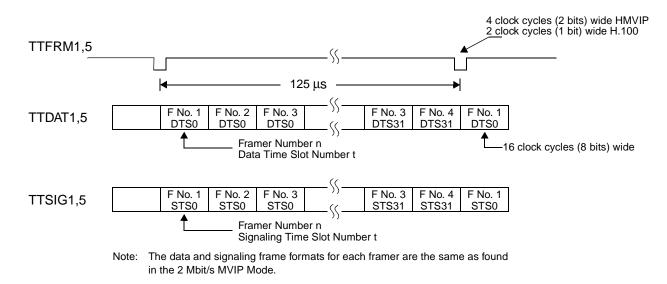

| 46.       Transmit Highway - MVIP Mode       98         47.       Receive Highway - MVIP Mode       99         48.       Transmit Data and Signaling Highways - 8 Mbit/s H-MVIP/H.100 Modes       100         49.       Receive Data and Signaling Highways - 8 Mbit/s H-MVIP/H.100 Modes       101         50.       Transmit Slip Buffer       116         51.       Receive Signaling Buffer       121         53.       Transmit Signaling Buffer       122         54.       HDLC Format       126         55.       Shadow Register Operation       132         56.       Local Loopback       133         57.       Remote Line Loopback       134         58.       Directional Loopback       135         60.       Time Slot Remote and Payload Loopbacks       136         61.       DS0 remote Loopback Code Sequence Generator       136         62.       PRBS/ Code Word Generator/ Analyzer Options with Loopbacks       142         63.       Tandem Frame Monitoring with National Bit Insertion       145         64.       Auxiliary Port Connections       146         65.       Boundary Scan Schematic       148         65.       Boundary Scan Schematic       148         65.       Boun                                                                                                  | 44.  | Transmit Highway - Data Mode                                       |      |

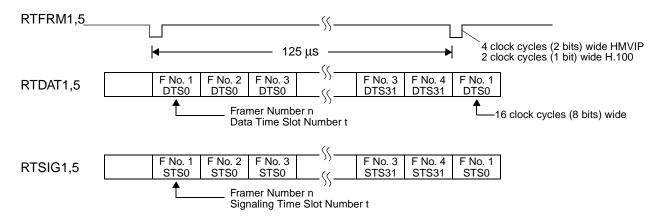

| 47.Receive Highway - MVIP Mode9948.Transmit Data and Signaling Highways - 8 Mbit/s H-MVIP/H.100 Modes10049.Receive Data and Signaling Highways - 8 Mbit/s H-MVIP/H.100 Modes10150.Transmit Slip Buffer11651.Receive Signaling Buffer11752.Receive Signaling Buffer12153.Transmit Signaling Buffer12254.HDLC Format12655.Shadow Register Operation13256.Local Loopback13357.Remote Line Loopback13458.Bi-Directional Loopback13661.DS0 remote Loopback13662.PRBS/ Code Word Generator/ Analyzer Options with Loopbacks14263.Tandem Frame Monitoring with National Bit Insertion14564.Auxiliary Port Connections14665.Boundary Scan Schematic14866.Typical Applications using the E1Fx827267.E1Fx8 TXC-03109 208-Lead Plastic Ball Grid Array Package Diagram273                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 45.  | Receive Highway - Data Mode                                        |      |

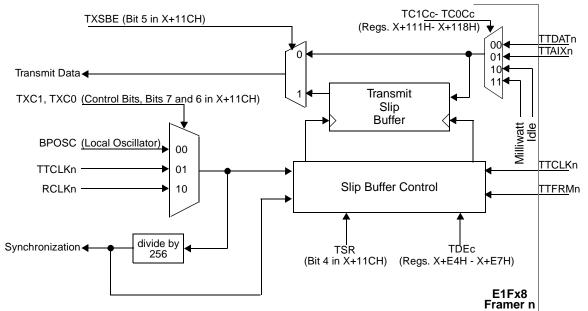

| 47.Receive Highway - MVIP Mode9948.Transmit Data and Signaling Highways - 8 Mbit/s H-MVIP/H.100 Modes10049.Receive Data and Signaling Highways - 8 Mbit/s H-MVIP/H.100 Modes10150.Transmit Slip Buffer11651.Receive Signaling Buffer11752.Receive Signaling Buffer12153.Transmit Signaling Buffer12254.HDLC Format12655.Shadow Register Operation13256.Local Loopback13357.Remote Line Loopback13458.Bi-Directional Loopback13661.DS0 remote Loopback13662.PRBS/ Code Word Generator/ Analyzer Options with Loopbacks14263.Tandem Frame Monitoring with National Bit Insertion14564.Auxiliary Port Connections14665.Boundary Scan Schematic14866.Typical Applications using the E1Fx827267.E1Fx8 TXC-03109 208-Lead Plastic Ball Grid Array Package Diagram273                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 46.  | Transmit Highway - MVIP Mode                                       |      |

| 49.       Receive Data and Signaling Highways - 8 Mbit/s H-MVIP/H.100 Modes       101         50.       Transmit Slip Buffer       116         51.       Receive Slip Buffer       117         52.       Receive Signaling Buffer       121         53.       Transmit Signaling Buffer       122         54.       HDLC Format       126         55.       Shadow Register Operation       132         56.       Local Loopback       133         57.       Remote Line Loopback       134         58.       Bi-Directional Loopback       135         60.       Time Slot Remote and Payload Loopbacks       136         61.       DS0 remote Loopback Code Sequence Generator       136         62.       PRBS/ Code Word Generator/ Analyzer Options with Loopbacks       142         63.       Tandem Frame Monitoring with National Bit Insertion       145         64.       Auxiliary Port Connections       146         65.       Boundary Scan Schematic       148         66.       Typical Applications using the E1Fx8       272         67.       E1Fx8 TXC-03109 208-Lead Plastic Ball Grid Array Package Diagram       273                                                                                                                                                                          | 47.  |                                                                    |      |

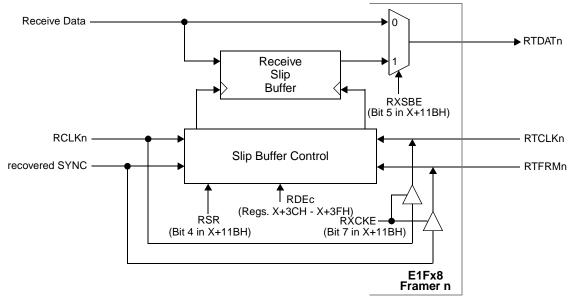

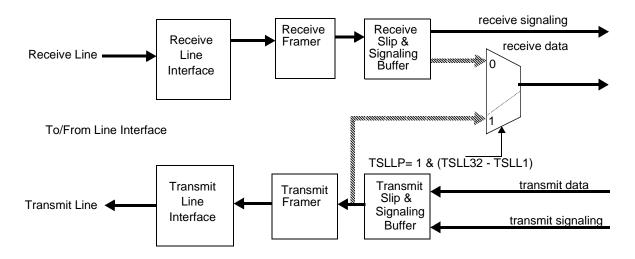

| 50.Transmit Slip Buffer11651.Receive Slip Buffer11752.Receive Signaling Buffer12153.Transmit Signaling Buffer12254.HDLC Format12655.Shadow Register Operation13256.Local Loopback13357.Remote Line Loopback13458.Bi-Directional Loopback13459.Time Slot Remote and Payload Loopbacks13560.Time Slot Local Loopback13661.DS0 remote Loopback Code Sequence Generator13662.PRBS/ Code Word Generator/ Analyzer Options with Loopbacks14263.Tandem Frame Monitoring with National Bit Insertion14564.Auxiliary Port Connections14665.Boundary Scan Schematic14866.Typical Applications using the E1Fx827267.E1Fx8 TXC-03109 208-Lead Plastic Ball Grid Array Package Diagram273                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 48.  | Transmit Data and Signaling Highways - 8 Mbit/s H-MVIP/H.100 Modes | 100  |

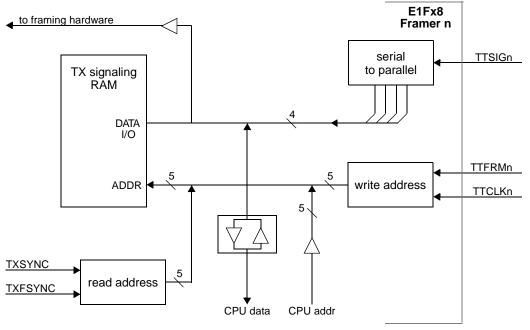

| 51.Receive Slip Buffer11752.Receive Signaling Buffer12153.Transmit Signaling Buffer12254.HDLC Format12655.Shadow Register Operation13256.Local Loopback13357.Remote Line Loopback13458.Bi-Directional Loopback13459.Time Slot Remote and Payload Loopbacks13560.Time Slot Local Loopback13661.DS0 remote Loopback Code Sequence Generator13662.PRBS/ Code Word Generator/ Analyzer Options with Loopbacks14263.Tandem Frame Monitoring with National Bit Insertion14564.Auxiliary Port Connections14665.Boundary Scan Schematic14866.Typical Applications using the E1Fx827267.E1Fx8 TXC-03109 208-Lead Plastic Ball Grid Array Package Diagram273                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 49.  | Receive Data and Signaling Highways - 8 Mbit/s H-MVIP/H.100 Modes  | 101  |

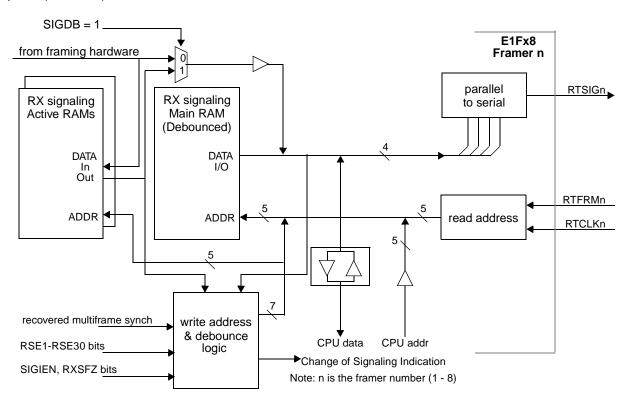

| 52.Receive Signaling Buffer12153.Transmit Signaling Buffer12254.HDLC Format12655.Shadow Register Operation13256.Local Loopback13357.Remote Line Loopback13458.Bi-Directional Loopback13459.Time Slot Remote and Payload Loopbacks13560.Time Slot Local Loopback13661.DS0 remote Loopback Code Sequence Generator13662.PRBS/ Code Word Generator/ Analyzer Options with Loopbacks14263.Tandem Frame Monitoring with National Bit Insertion14564.Auxiliary Port Connections14665.Boundary Scan Schematic14866.Typical Applications using the E1Fx827267.E1Fx8 TXC-03109 208-Lead Plastic Ball Grid Array Package Diagram273                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 50.  | Transmit Slip Buffer                                               | 116  |

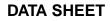

| 53.Transmit Signaling Buffer12254.HDLC Format12655.Shadow Register Operation13256.Local Loopback13357.Remote Line Loopback13458.Bi-Directional Loopback13459.Time Slot Remote and Payload Loopbacks13560.Time Slot Local Loopback13661.DS0 remote Loopback Code Sequence Generator13662.PRBS/ Code Word Generator/ Analyzer Options with Loopbacks14263.Tandem Frame Monitoring with National Bit Insertion14564.Auxiliary Port Connections14665.Boundary Scan Schematic14866.Typical Applications using the E1Fx827267.E1Fx8 TXC-03109 208-Lead Plastic Ball Grid Array Package Diagram273                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 51.  | Receive Slip Buffer                                                | 117  |

| 54.HDLC Format12655.Shadow Register Operation13256.Local Loopback13357.Remote Line Loopback13458.Bi-Directional Loopback13459.Time Slot Remote and Payload Loopbacks13560.Time Slot Local Loopback13661.DS0 remote Loopback Code Sequence Generator13662.PRBS/ Code Word Generator/ Analyzer Options with Loopbacks14263.Tandem Frame Monitoring with National Bit Insertion14564.Auxiliary Port Connections14665.Boundary Scan Schematic14866.Typical Applications using the E1Fx827267.E1Fx8 TXC-03109 208-Lead Plastic Ball Grid Array Package Diagram273                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 52.  | Receive Signaling Buffer                                           | 121  |

| 55.Shadow Register Operation13256.Local Loopback13357.Remote Line Loopback13458.Bi-Directional Loopback13459.Time Slot Remote and Payload Loopbacks13560.Time Slot Local Loopback13661.DS0 remote Loopback Code Sequence Generator13662.PRBS/ Code Word Generator/ Analyzer Options with Loopbacks14263.Tandem Frame Monitoring with National Bit Insertion14564.Auxiliary Port Connections14665.Boundary Scan Schematic14866.Typical Applications using the E1Fx827267.E1Fx8 TXC-03109 208-Lead Plastic Ball Grid Array Package Diagram273                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 53.  | Transmit Signaling Buffer                                          | 122  |

| 56.Local Loopback13357.Remote Line Loopback13458.Bi-Directional Loopback13459.Time Slot Remote and Payload Loopbacks13560.Time Slot Local Loopback13661.DS0 remote Loopback Code Sequence Generator13662.PRBS/ Code Word Generator/ Analyzer Options with Loopbacks14263.Tandem Frame Monitoring with National Bit Insertion14564.Auxiliary Port Connections14665.Boundary Scan Schematic14866.Typical Applications using the E1Fx827267.E1Fx8 TXC-03109 208-Lead Plastic Ball Grid Array Package Diagram273                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 54.  | HDLC Format                                                        | 126  |

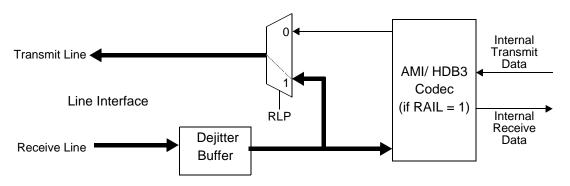

| 57.Remote Line Loopback.13458.Bi-Directional Loopback.13459.Time Slot Remote and Payload Loopbacks13560.Time Slot Local Loopback13661.DS0 remote Loopback Code Sequence Generator13662.PRBS/ Code Word Generator/ Analyzer Options with Loopbacks14263.Tandem Frame Monitoring with National Bit Insertion14564.Auxiliary Port Connections14665.Boundary Scan Schematic14866.Typical Applications using the E1Fx827267.E1Fx8 TXC-03109 208-Lead Plastic Ball Grid Array Package Diagram273                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 55.  | Shadow Register Operation                                          | 132  |

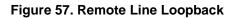

| 58.Bi-Directional Loopback.13459.Time Slot Remote and Payload Loopbacks13560.Time Slot Local Loopback13661.DS0 remote Loopback Code Sequence Generator13662.PRBS/ Code Word Generator/ Analyzer Options with Loopbacks14263.Tandem Frame Monitoring with National Bit Insertion14564.Auxiliary Port Connections14665.Boundary Scan Schematic14866.Typical Applications using the E1Fx827267.E1Fx8 TXC-03109 208-Lead Plastic Ball Grid Array Package Diagram273                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 56.  | Local Loopback                                                     | 133  |

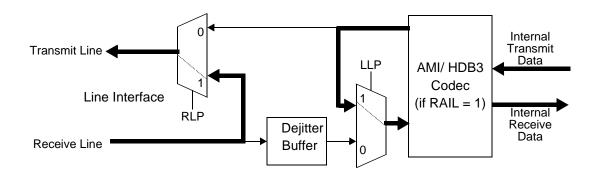

| 59.Time Slot Remote and Payload Loopbacks13560.Time Slot Local Loopback13661.DS0 remote Loopback Code Sequence Generator13662.PRBS/ Code Word Generator/ Analyzer Options with Loopbacks14263.Tandem Frame Monitoring with National Bit Insertion14564.Auxiliary Port Connections14665.Boundary Scan Schematic14866.Typical Applications using the E1Fx827267.E1Fx8 TXC-03109 208-Lead Plastic Ball Grid Array Package Diagram273                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 57.  | Remote Line Loopback                                               | 134  |

| 60.Time Slot Local Loopback13661.DS0 remote Loopback Code Sequence Generator13662.PRBS/ Code Word Generator/ Analyzer Options with Loopbacks14263.Tandem Frame Monitoring with National Bit Insertion14564.Auxiliary Port Connections14665.Boundary Scan Schematic14866.Typical Applications using the E1Fx827267.E1Fx8 TXC-03109 208-Lead Plastic Ball Grid Array Package Diagram273                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 58.  | Bi-Directional Loopback                                            | 134  |

| 60.Time Slot Local Loopback13661.DS0 remote Loopback Code Sequence Generator13662.PRBS/ Code Word Generator/ Analyzer Options with Loopbacks14263.Tandem Frame Monitoring with National Bit Insertion14564.Auxiliary Port Connections14665.Boundary Scan Schematic14866.Typical Applications using the E1Fx827267.E1Fx8 TXC-03109 208-Lead Plastic Ball Grid Array Package Diagram273                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 59.  | Time Slot Remote and Payload Loopbacks                             | 135  |

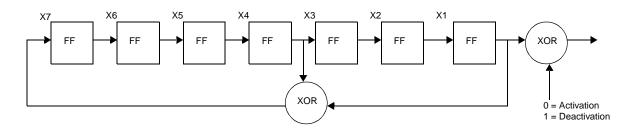

| 61.DS0 remote Loopback Code Sequence Generator13662.PRBS/ Code Word Generator/ Analyzer Options with Loopbacks14263.Tandem Frame Monitoring with National Bit Insertion14564.Auxiliary Port Connections14665.Boundary Scan Schematic14866.Typical Applications using the E1Fx827267.E1Fx8 TXC-03109 208-Lead Plastic Ball Grid Array Package Diagram273                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 60.  |                                                                    |      |

| 62.PRBS/ Code Word Generator/ Analyzer Options with Loopbacks14263.Tandem Frame Monitoring with National Bit Insertion14564.Auxiliary Port Connections14665.Boundary Scan Schematic14866.Typical Applications using the E1Fx827267.E1Fx8 TXC-03109 208-Lead Plastic Ball Grid Array Package Diagram273                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 61.  |                                                                    |      |

| 63.Tandem Frame Monitoring with National Bit Insertion.14564.Auxiliary Port Connections14665.Boundary Scan Schematic14866.Typical Applications using the E1Fx827267.E1Fx8 TXC-03109 208-Lead Plastic Ball Grid Array Package Diagram273                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 62.  |                                                                    |      |

| 64.Auxiliary Port Connections14665.Boundary Scan Schematic14866.Typical Applications using the E1Fx827267.E1Fx8 TXC-03109 208-Lead Plastic Ball Grid Array Package Diagram273                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 63.  |                                                                    |      |

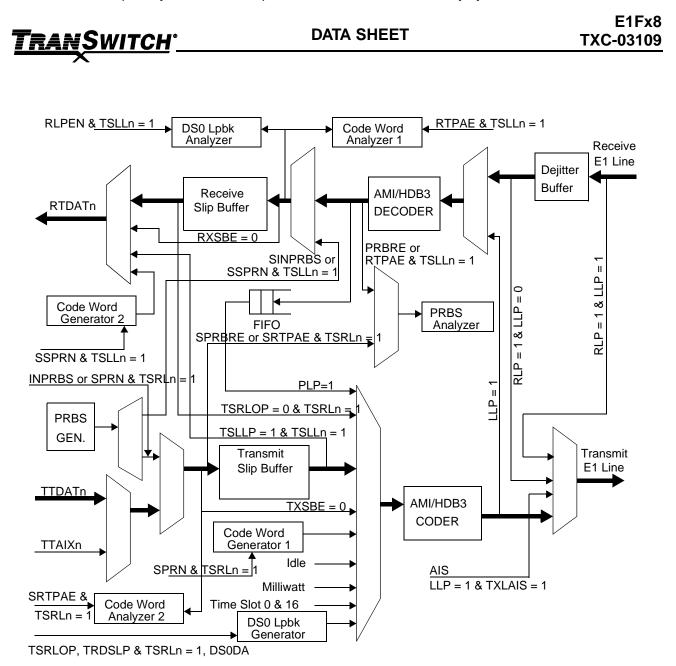

| 65.Boundary Scan Schematic14866.Typical Applications using the E1Fx827267.E1Fx8 TXC-03109 208-Lead Plastic Ball Grid Array Package Diagram273                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 64.  | -                                                                  |      |

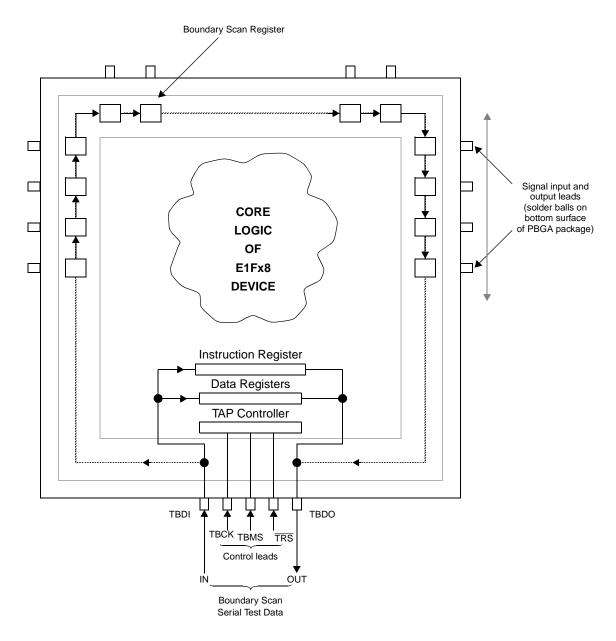

| <ul> <li>66. Typical Applications using the E1Fx8</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 65.  | -                                                                  |      |

| 67. E1Fx8 TXC-03109 208-Lead Plastic Ball Grid Array Package Diagram 273                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      | -                                                                  |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |                                                                    |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 68.  |                                                                    |      |

# OVERVIEW

The E1Fx8 provides the features of two QE1F-Plus devices complemented by independent per time slot local or remote loopbacks, a gapped clock/marker system interface option, a per-channel PRBS/code word generator analyzer, a per-channel time slot inband loopback activate/deactivate detector/generator (compatible with the T1Fx8 and ANSI T1.231), an internal selection option for the one-second clock, and frame pulse monitoring added to the E1 monitor function. The receive line interfaces are enhanced with dejitter buffers for loop timed applications and direct multiplexer interface applications. In addition, an intact mode for slip buffering unframed E1s, an auxiliary input for fractional E1 and CCS or ISDN D channel access, and independent transmit or receive framing have been incorporated. For multichannel ISDN or V5.1/V5.2 applications an Auxiliary E1 rate port is provided that can directly connect to a multichannel HDLC controller for access to any user time slots from any of the channels for a maximum of 32 total. Signaling debounce and a signaling change of state interrupt are incorporated along with certain alarms mapped to and from Time Slot 16 CAS codes to automatically support ITU-T G.732 alarm propagation. The HDLC FIFOs have been expanded to 128 bytes for each transmit and receive channel as well as being able to support back-to-back frames. A delay value register was added to the slip buffers and digital A-law or mu-law digital milliwatt or a programmable idle code is available per time slot. The System Interface options are the same as those of the T1Fx8 with both separate signaling, alternate data bit and full data inversion capability. The E1Fx8 is available in the same 208-lead and 256-lead plastic ball grid array packages as the T1Fx8. The E1Fx8 packages have the same power, ground and signal lead configurations as the corresponding T1Fx8 packages, except that some leads which are no-connect spares on the T1Fx8 are used for additional power, ground and signal functions on the E1Fx8. Reduced power consumption is an added benefit of the E1Fx8, which is powered from a 3.3 volt supply, but is still tolerant of inputs from 5 volt parts.

The E1Fx8 supports multiple applications, including SDH/PDH networks and data applications where multiple framing functions are required in a single board. The E1Fx8 contains many features which allow it to be used in SDH Add/Drop multiplexers, E1 multiplexers, E1 and fractional E1 CSUs, PBXs, ATM products, LAN routers with integrated E1 interfaces, E1 Internet access equipment, Primary Rate ISDN interfaces, multichannel E1 test equipment, repeaters, access nodes and switches. In addition, the E1Fx8 includes many advanced diagnostic, test, and maintenance features, including boundary scan (IEEE 1149.1) and both E1 and time slot level loopbacks. The E1Fx8 is well suited for embedded CSU/DSU functions in routers and bridges and for test instruments needing a high degree of data manipulation.

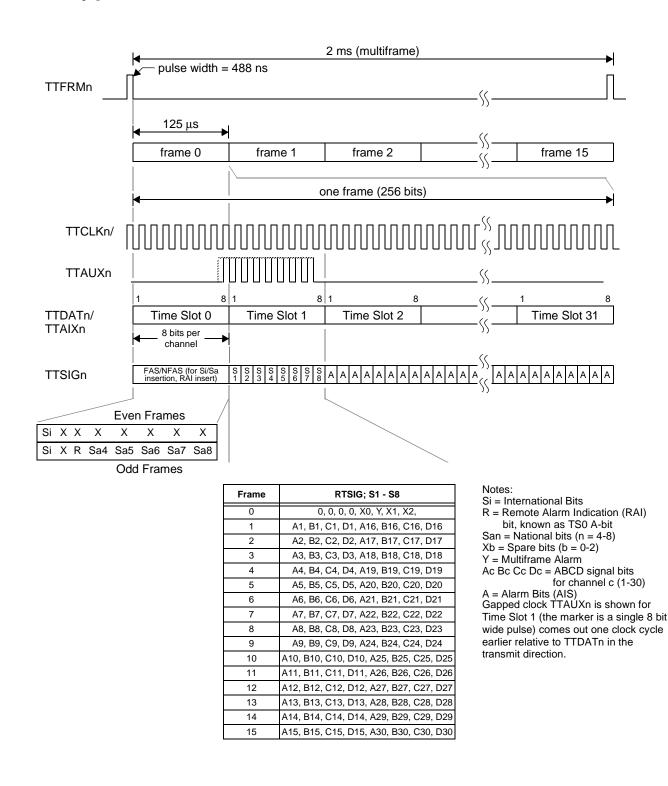

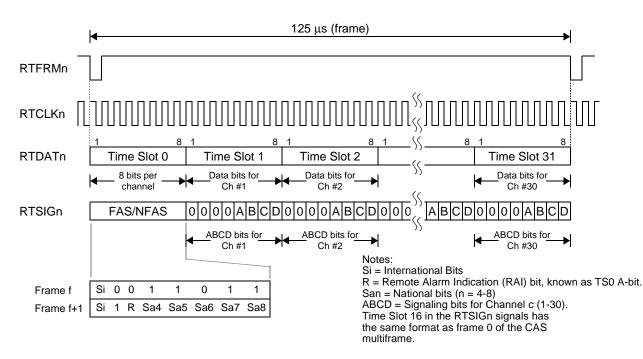

The E1Fx8 supports TS0/CRC-4 and TS16/Signaling Multiframes operating in an offine mode. Either Common Channel Signaling (CCS) or Channel Associated Signaling (CAS) is supported. The transmit and receive sections of each of the eight framers are independent, with individual slip buffers and independent framed or unframed operation to allow use in a wide range of switching and transmission products.

Each framer supplies a full duplex HDLC message controller with onboard transmit and receive FIFOs, and TSO National bit access, in addition to onboard latching of all required performance parameters, requiring minimal software overhead and microprocessor bandwidth to support HDLC protocols. The HDLC controller is enhanced to include deep FIFOs (128 bytes each way) and a back-to-back capability where a single flag can separate frames. When not used for HDLC functions, the National bits are accessible to transmit and receive code words, with full Sa6 bit functionality supporting ETS 300 233 for ISDN applications.

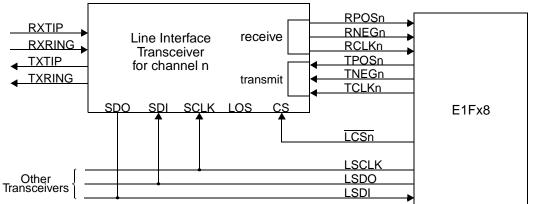

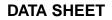

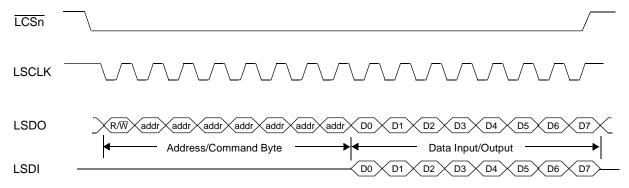

The E1 digital line interface port is extremely flexible, allowing the device to connect to any industry standard line interface device with no external glue logic. AMI, HDB3, and NRZ line codes are supported with full alarm detection and generation. An optional 64-bit dual rail dejitter buffer meeting ITU-T G.823 for jitter tolerance, G.735 and G.736 for jitter generation, and G.735/6/8/9 for jitter transfer is provided. Optional frame pulse or drive bit output is available in the NRZ mode. The NRZ mode allows the E1Fx8 to count externally detected code violations or to incorporate an external loss of clock/signal detector. The interface contains a serial port, which can directly control the external line interface unit and other components using the industry standard 'host' mode for device control.

TRANSWITCH<sup>®</sup>

The framer provides a microprocessor interface that is compatible with either Motorola or Intel processors. It is designed to act as an 8-bit peripheral using asynchronous bus transfers. Polling or interrupt support and latching of critical events are provided to accelerate interrupt processing and reduce the burden on the attached microprocessor. Individual alarm masks are available to ignore certain alarms or to operate different channels in different modes. Direct access to the slip buffers is provided for time slots and the signaling RAMs, which makes sending special signaling or time slot codes possible with low overhead. Scanning for signaling is facilitated with signaling debounce and interrupt on signaling change of state.

The framer supports a wide variety of individual and multiplexed system interface options to permit seamless interfacing to many types of time slot-based devices. Both MVIP and HMVIP/H.100 interfaces are provided for operation with many different system buses and devices. For maintenance support the E1Fx8 incorporates a per E1 PRBS code word generator/analyzer that provides 2<sup>11</sup>-1, 2<sup>15</sup>-1, QRSS (2<sup>20</sup>-1) and 2<sup>23</sup>-1 codes in addition to a programmable 32-bit code word. In addition, a per E1 time slot loopback activate and deactivate function compatible with the T1Fx8 and ANSI T1.403-1998 Fractional T1 Loopback are provided. Error forcing and diagnostic access are also provided.

To support monitoring functions, the E1Fx8 provides a bypass mode in which a received E1 signal is monitored and looped back to the transmitter. In this mode the Sa4 through Sa8 bits may be individually replaced and the CRC-4 is updated to reflect only the changed bits, retaining end to end performance monitoring per ITU-T G.706 Annex C.