# HYS72T128001HF[N/A]-3.7-A HYS72T256021HF[N/A]-3.7-A

# 240-Pin Fully-Buffered DDR2 SDRAM Modules

DDR2 SDRAM FB-DIMM SDRAM RoHS Compliant Green Product High-Speed Differential Point to-Point Link Interface at 1.5 V

**Memory Products**

Never stop thinking.

Edition 2005-11

Published by Infineon Technologies AG, St.-Martin-Strasse 53, 81669 München, Germany © Infineon Technologies AG 2005. All Rights Reserved.

#### **Attention please!**

The information herein is given to describe certain components and shall not be considered as a guarantee of characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

### HYS72T128001HF[N/A]-3.7-A HYS72T256021HF[N/A]-3.7-A

### Revision History: 2005-11, Rev. 1.10

| Previous Version: 1.01 |                                                                                    |  |  |  |  |  |

|------------------------|------------------------------------------------------------------------------------|--|--|--|--|--|

| Page                   | Subjects (major changes since last revision)                                       |  |  |  |  |  |

| 7                      | Updated Table 1 "Performance for DDR2-533" on Page 7                               |  |  |  |  |  |

| 8                      | Updated Table 2 "Ordering Information (Pb-free components and assembly)" on Page 8 |  |  |  |  |  |

| 8                      | Added Table 3 "Address Format" on Page 8                                           |  |  |  |  |  |

| 8                      | Added Table 4 "Components on Modules" on Page 8                                    |  |  |  |  |  |

| 23                     | Updated Table 6 "Electrical Characteristics" on Page 23                            |  |  |  |  |  |

| 51                     | Updated "SPD Codes" on Page 51                                                     |  |  |  |  |  |

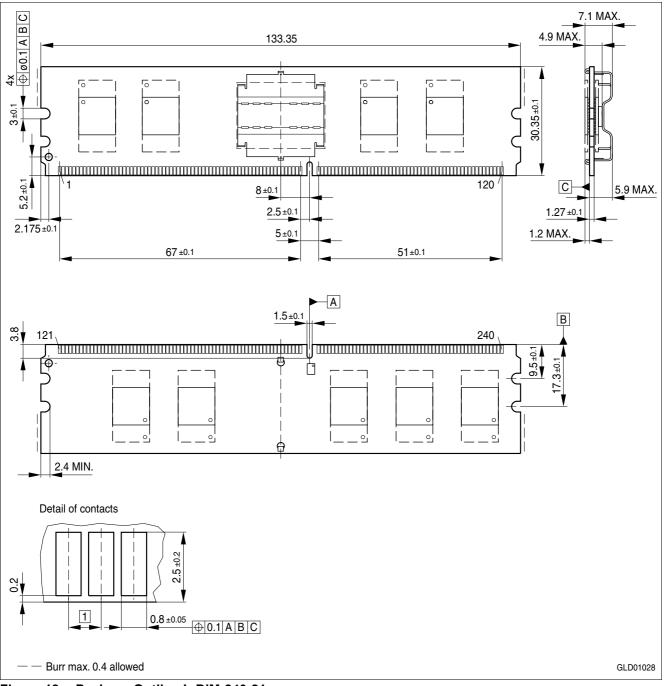

| 62                     | Updated Figure 18 "Package Outline L-DIM-240-21" on Page 62                        |  |  |  |  |  |

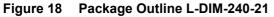

| 63                     | Updated Figure 19 "Package Outline L-DIM-240-22" on Page 63                        |  |  |  |  |  |

|                        |                                                                                    |  |  |  |  |  |

We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send us your proposal (including a reference to this document) to: techdoc.mp@infineon.com

#### **Table of Contents**

# **Table of Contents**

| <b>1</b><br>1.1<br>1.2                                                                                 | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 7                                                                                                                    |

|--------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| 2                                                                                                      | Pin Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 9                                                                                                                    |

| 3                                                                                                      | FB-DIMM Input/Output Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 15                                                                                                                     |

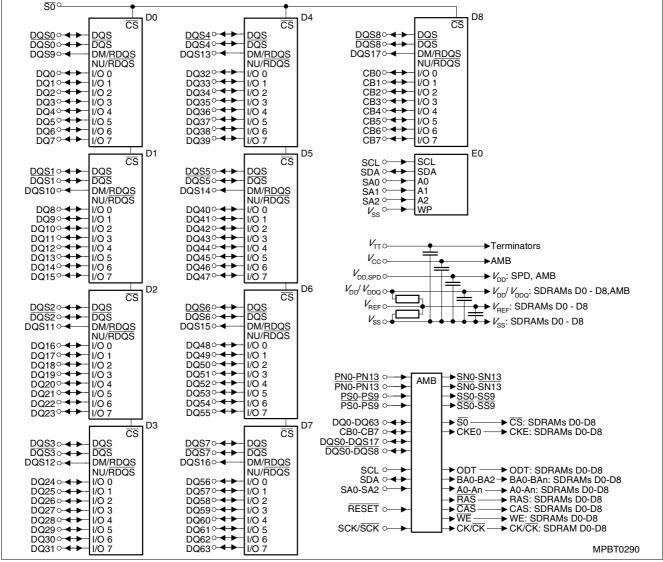

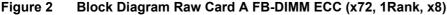

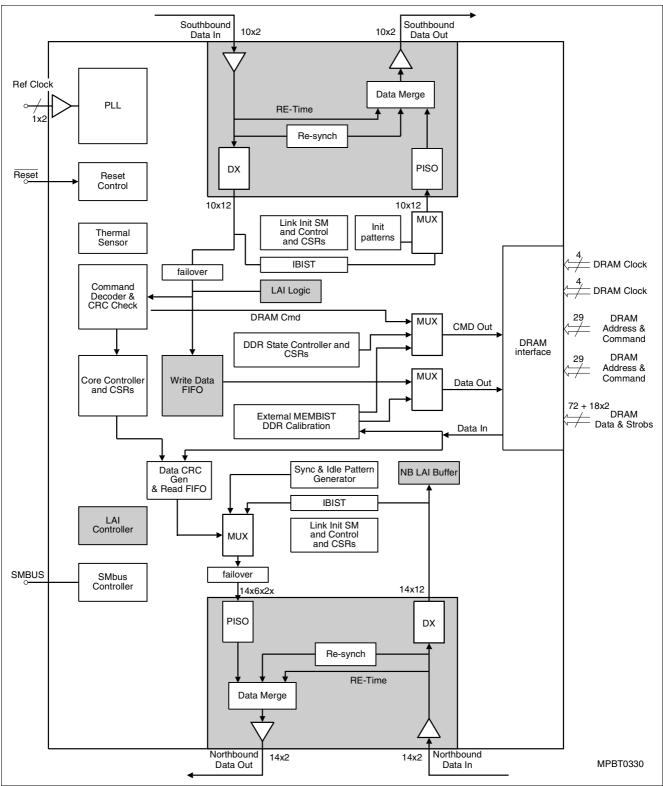

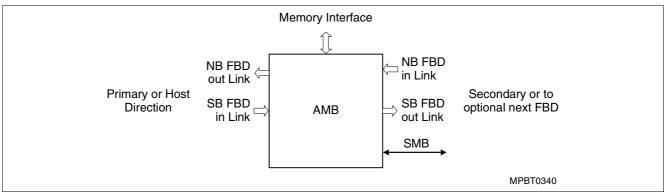

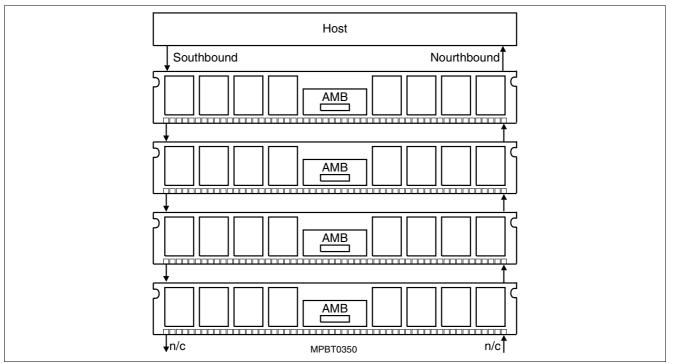

| 4                                                                                                      | Block Diagrams                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 16                                                                                                                     |

| <b>5</b><br>5.1<br>5.2<br>5.3<br>5.4<br>5.4.1<br>5.4.2<br>5.4.3<br>5.4.3<br>5.4.4<br>5.5<br>5.6<br>5.7 | Jedec<br>Advanced Memory Buffer Overview<br>Advanced Memory Buffer Functionality<br>Interfaces<br>High-Speed Differential Point-to-Point Link (at 1.5 V) Interfaces<br>DDR2 Channel<br>SMBus Slave Interface<br>Channel Latency<br>Peak Theoretical Channel Throughput<br>Hot-add<br>Hot-remove<br>Hot-replace                                                                                                                                                                                                       | <ol> <li>18</li> <li>20</li> <li>21</li> <li>21</li> <li>21</li> <li>21</li> <li>22</li> <li>22</li> <li>22</li> </ol> |

| <b>6</b><br>6.1                                                                                        | Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                        |

| 7<br>7.1<br>7.1.1<br>7.1.2<br>7.1.3<br>7.1.4<br>7.1.5<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6<br>7.6.1      | High-Speed Differential Point-to-Point Link Interface         Differential Signaling         Transition Density in Transmitted Signals         Jitter and Bit Error Rate         De-Emphasis         Electrical Idle (EI)         Reference Clock         High Speed Serial Link Reference Clocks (SCK, SCK)         Spread Spectrum Clocking (SSC)         Reference Clock Input Specifications         Differential Receiver Input Specifications         Differential Receiver Input Compliance Eye Specification | 25<br>26<br>26<br>27<br>27<br>27<br>27<br>27<br>28<br>32<br>32                                                         |

| <b>8</b><br>8.1<br>8.1.1<br>8.2<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4<br>8.2.5<br>8.2.6<br>8.2.7         | Channel Initialization<br>RESET Signal<br>Inband Control 'Signals'<br>Channel Initialization Sequence<br>Firmware Transition Control<br>AMB Internal State Variables<br>Disable State<br>Training State<br>Testing State<br>Polling State<br>Config State                                                                                                                                                                                                                                                            | 35<br>36<br>36<br>36<br>37<br>37<br>37<br>37                                                                           |

| <b>9</b><br>9.1                                                                                        | Channel Protocol Southbound Frames                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                        |

#### **Table of Contents**

| 9.1.1   | Normal Southbound Frames                                         |    |   |

|---------|------------------------------------------------------------------|----|---|

| 9.1.2   | Fail-over Southbound Frames                                      |    |   |

| 9.1.3   | Command Frame Format                                             |    |   |

| 9.1.3.1 | Command Frame with Data Format                                   |    |   |

| 9.1.3.2 | Command+Wdata Frame Format                                       |    |   |

| 9.1.4   | Southbound Commands                                              |    |   |

| 9.1.4.1 | DRAM Commands                                                    |    |   |

| 9.1.4.2 | Channel Commands                                                 |    |   |

| 9.1.4.3 | CKE Control Commands                                             |    |   |

| 9.1.4.4 | Soft Channel Reset Command                                       |    |   |

| 9.1.4.5 | Sync Command                                                     |    |   |

| 9.1.4.6 | NOP Frame                                                        |    |   |

| 9.1.4.7 | Command Delivery Timing                                          |    |   |

| 9.1.4.8 | Concurrent Command Delivery Rules                                |    |   |

| 9.1.4.9 | Command Encoding                                                 |    |   |

| 9.2     | Northbound CRC Modes                                             | 4′ | 1 |

| 9.2.1   | Northbound Idle Frame                                            |    |   |

| 9.2.2   | Northbound Alert Frame                                           |    |   |

| 9.2.3   | Northbound Data Frames                                           | 42 | 2 |

| 9.2.3.1 | 14-bit Lane Northbound Data Frame                                | 42 | 2 |

| 9.2.3.2 | 13-bit Lane Fail-over Northbound Data Frame                      |    |   |

| 9.2.3.3 | 13-bit Lane Northbound Data Frame                                | 42 | 2 |

| 9.2.3.4 | 13-bit Lane Fail-Over Northbound Data Frame                      | 42 | 2 |

| 9.2.3.5 | 12-bit Lane Northbound Data Frame (Non-ECC Mode)                 | 43 | 3 |

| 9.2.3.6 | Northbound Register Data Frame                                   | 43 | 3 |

| 9.2.3.7 | Northbound Status Frame                                          | 43 | 3 |

| 9.3     | DRAM Memory Timing                                               | 43 | 3 |

| 9.3.1   | Read Timing                                                      | 43 | 3 |

| 9.3.2   | Write Timing                                                     | 44 | 1 |

| 9.3.2.1 | Write Data FIFO                                                  | 48 | 5 |

| 9.3.3   | Simultaneous Read and Write Data Transfers                       | 48 | 5 |

| 9.3.4   | DRAM Bus Segment Restrictions                                    | 48 | 5 |

| 10      | Reliability, Availability and Serviceability                     | 46 | 6 |

| 10.1    | Overview                                                         |    |   |

| 10.2    | Example Error Flows                                              |    |   |

| 10.2.1  | Command Error Flow                                               |    |   |

| 10.2.2  | Write Data Error Flow                                            |    |   |

| 10.2.3  | Read Error Flow                                                  |    |   |

| 10.3    | Overview of Error Protection, Detection, Correction, and Logging |    |   |

| 10.4    | Error Protection and Detection Methods                           |    |   |

| 10.4.1  | CRC Logic Used on Normal Southbound Frames                       |    |   |

| 10.4.2  | Fail-over Southbound Frames                                      |    |   |

| 10.4.3  | Write and Read Data ECC Error Protection                         |    |   |

| 10.5    | Southbound Error Handling at the AMB                             |    |   |

| 10.5.1  | Exiting Command Error State                                      |    |   |

| 10.6    | Northbound Error Handling at the AMB                             |    |   |

| 10.7    | Error Logging                                                    |    |   |

| 10.8    | Fail-over Mode Operation                                         |    |   |

| 10.8.1  | Fail-over Mode Operation on Southbound Lanes                     |    |   |

| 10.8.2  | Fail-over Mode Operation on Northbound Lanes                     |    |   |

| 10.9    | AMB Pass-through Functionality                                   |    |   |

|         |                                                                  |    |   |

#### **Table of Contents**

|    | Memory Initialization |    |

|----|-----------------------|----|

| 11 | SPD Codes             | 51 |

| 12 | Package Outline       | 61 |

| 13 | DDR2 Nomencature      | 64 |

Overview

### 1 Overview

This chapter describes the main characteristics of the 240-Pin Fully-Buffered DDR2 SDRAM Modules product family.

### 1.1 Features

- 240-pin Fully-Buffered ECC Dual-In-Line DDR2 SDRAM Module for PC, Workstation and Server main memory applications.

- One rank 128Mb x 72 and two ranks 256Mb x 72 memory array.

- JEDEC Standard Double Data Rate 2 Synchronous DRAMs (DDR2 SDRAMs) with 1.8 V (± 0.1 V) power supply.

- Built with 1Gb DDR2 SDRAMs in 68-ball Chipsize Packages.

- Re-drive and re-sync of all address, command, clock and data signals using AMB (Advanced Memory Buffer).

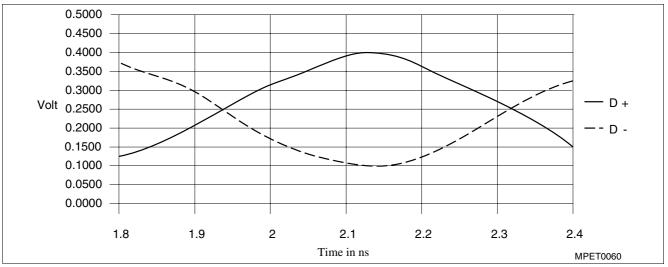

- High-Speed Differential Point-to-Point Link Interface at 1.5 V (Jedec standard pending).

- Host Interface and AMB component industry standard compliant.

- Supports SMBus protocol interface for access to the AMB configuration registers.

Performance for DDR2-533

- Detects errors on the channel and reports them to the host memory controller.

- Automatic DDR2 DRAM Bus Calibration.

- Automatic Channel Calibration.

- Full Host Control of the DDR2 DRAMs.

- Over-Temperature Detection and Alert.

- Hot Add-on and Hot Remove Capability.

- MBIST and IBIST Test Functions.

- Transparent Mode for DRAM Test Support.

- Low profile: 133.35mm x 30,35mm

- 240 Pin gold plated card connector with 1.00mm contact centers (JEDEC standard pending).

- Based on JEDEC standard reference card designs (Jedec standard pending).

- SPD (Serial Presence Detect) with 256 Byte serial E<sup>2</sup>PROM.Performance:

- RoHS Compliant Products<sup>1)</sup>

| Product Type Speed Code | -3.7           | Units            |     |     |

|-------------------------|----------------|------------------|-----|-----|

| Speed Grade             | PC2-4200 4-4-4 |                  |     |     |

| Max. Clock Frequency    | @CL5           | $f_{CK5}$        | 266 | MHz |

|                         | @CL4           | $f_{\rm CK4}$    | 266 | MHz |

|                         | @CL3           | $f_{CK3}$        | 200 | MHz |

| Min. RAS-CAS-Delay      |                | t <sub>RCD</sub> | 15  | ns  |

| Min. Row Precharge Time |                | t <sub>RP</sub>  | 15  | ns  |

| Min. Row Active Time    |                | t <sub>RAS</sub> | 45  | ns  |

| Min. Row Cycle Time     |                | t <sub>RC</sub>  | 60  | ns  |

### 1.2 Description

This document describes the electrical and mechanical features of Infineon's 240-pin, PC2-4200F ECC type, Fully Buffered Double-Data-Rate Two Synchronous DRAM Dual In-Line Memory Modules (DDR2 SDRAM FB-DIMMs). Fully Buffered DIMMs use commodity

DRAMs isolated from the memory channel behind a buffer on the DIMM. They are intended for use as main memory when installed in systems such as servers and workstations. PC2-4200 refers to the DIMM naming convention indicating the DDR2 SDRAMs running at

Table 1

RoHS Compliant Product: Restriction of the use of certain hazardous substances (RoHS) in electrical and electronic equipment as defined in the directive 2002/95/EC issued by the European Parliament and of the Council of 27 January 2003. These substances include mercury, lead, cadmium, hexavalent chromium, polybrominated biphenyls and polybrominated biphenyl ethers.

#### Overview

266 MHz clock speed and offering 4200 MB/s peak bandwidth. FB-DIMM features a novel architecture including the Advanced Memory Buffer. This single chip component, located in the center of each DIMM, acts as a repeater and buffer for all signals and commands which are exchanged between the host controller and the DDR2 SDRAMs including data inand output. The AMB communicates with the host controller and / or the adjacent DIMMs on a system board using an Industry Standard High-Speed Differential Point-to-Point Link Interface at 1.5 V. The Advanced Memory Buffer also allows buffering of memory traffic to support large memory capacities. All memory control for the DRAM resides in the host, including memory request initiation, timing, refresh, scrubbing, sparing, configuration access, and power management. The Advanced Memory Buffer interface is responsible for handling channel and memory requests to and from the local DIMM and for forwarding requests to other DIMMs on the memory channel. Fully Buffered DIMM provides a high memory bandwidth, large capacity channel solution that has a narrow host interface. The maximum memory capacity is 288 DDR2 SDRAM devices per channel or 8 DIMMs.

#### Table 2 Ordering Information (Pb-free components and assembly)

| Type & Partnumber <sup>1)</sup> | Compliance Code <sup>2)</sup> | Description            | SDRAM<br>Technology |

|---------------------------------|-------------------------------|------------------------|---------------------|

| PC2-4200F (DDR2-533):           |                               | -                      |                     |

| HYS72T128001HFN-3.7-A           | PC2-4200F-444-10-A            | one rank 1 GB FB–DIMM  | 1Gbit (x8)          |

| HYS72T128001HFA-3.7-A           | PC2-4200F-444-10-A            | one rank 1 GB FB–DIMM  | 1Gbit (x8)          |

| HYS72T256021HFN-3.7-A           | PC2-4200F-444-10-B            | two ranks 2 GB FB–DIMM | 1Gbit (x8)          |

| HYS72T256021HFA-3.7-A           | PC2-4200F-444-10-B            | two ranks 2 GB FB–DIMM | 1Gbit (x8)          |

All product types end with a place code, designating the silicon die revision. Example: HYS 72T64000HF-3.7-A, indicating Rev. A dice are used for DDR2 SDRAM components. To learn more on INFINEON DDR2 module and component nomenclature see section 8 of this datasheet.

2) The Compliance Code is printed on the module label and describes the speed grade, e.g. "PC2-4200F-444-10-C", where 4200F means Fully Buffered DIMM with 4.26 GB/sec Module Bandwidth and "444-10" means CAS latency = 4, t<sub>rcd</sub> latency = 4 and t<sub>rp</sub> latency = 4 using JEDEC SPD Revision 1.0 and assembled on Raw Card "C".

#### Table 3 Address Format

| DIMM<br>Density | Module<br>Organization | Memory<br>Ranks | ECC/<br>Non-ECC | # of<br>SDRAMs | # of row/bank/columns bits | Raw<br>Card |

|-----------------|------------------------|-----------------|-----------------|----------------|----------------------------|-------------|

| 1 GB            | 128M ×72               | 1               | ECC             | 9              | 14/3/10                    | А           |

| 2 GB            | 256M ×72               | 2               | ECC             | 18             | 14/3/10                    | В           |

#### Table 4 Components on Modules<sup>1)</sup>

| Product Type   | DRAM components <sup>2)</sup> | DRAM Density | DRAM Organisation |

|----------------|-------------------------------|--------------|-------------------|

| HYS72T128001HF | HYB18T1G800AF                 | 1 Gbit       | 128M ×8           |

| HYS72T256021HF | HYB18T1G800AF                 | 1 Gbit       | 128M ×8           |

1) For a detailed description of all functionalities of the DRAM components on these modules see the component datasheet.

2) Green Product

# 2 Pin Configuration

The pin configuration of the DDR2 SDRAM DIMM is listed by function in **Table 5** (240 pins). The abbreviations used in columns Pin and Buffer Type are explained in **Table 7** and **Table 6** respectively. The pin numbering is depicted in **Figure 1**.

### Table 5 Pin Configuration of FB-DIMM

| Pin#            | Name  | Pin  | Buffer  | Function                          |

|-----------------|-------|------|---------|-----------------------------------|

|                 |       | Туре | Туре    |                                   |

| Clock Signals   |       |      |         |                                   |

| 228             | SCK   | 1    | HSDL_15 | System Clock Input, positive line |

| 229             | SCK   | I    | HSDL_15 | System Clock Input, negative line |

| Control Signals |       |      |         |                                   |

| 17              | RESET | I    | LV-CMOS | AMB reset signal                  |

| Northbound      |       |      |         |                                   |

| 22              | PN0   | 0    | HSDL_15 | Primary Northbound Data, positive |

| 25              | PN1   | 0    | HSDL_15 | lines                             |

| 28              | PN2   | 0    | HSDL_15 |                                   |

| 31              | PN3   | 0    | HSDL_15 |                                   |

| 34              | PN4   | 0    | HSDL_15 |                                   |

| 37              | PN5   | 0    | HSDL_15 |                                   |

| 51              | PN6   | 0    | HSDL_15 |                                   |

| 54              | PN7   | 0    | HSDL_15 |                                   |

| 57              | PN8   | 0    | HSDL_15 |                                   |

| 60              | PN9   | 0    | HSDL_15 |                                   |

| 63              | PN10  | 0    | HSDL_15 |                                   |

| 66              | PN11  | 0    | HSDL_15 |                                   |

| 48              | PN12  | 0    | HSDL_15 | _                                 |

| 40              | PN13  | 0    | HSDL_15 |                                   |

| 23              | PN0   | 0    | HSDL_15 | Primary Northbound Data, negative |

| 26              | PN1   | 0    | HSDL_15 | lines                             |

| 29              | PN2   | 0    | HSDL_15 | -                                 |

| 32              | PN3   | 0    | HSDL_15 | -                                 |

| 35              | PN4   | 0    | HSDL_15 | -                                 |

| 38              | PN5   | 0    | HSDL_15 | -                                 |

| 52              | PN6   | 0    | HSDL_15 | -                                 |

| 55              | PN7   | 0    | HSDL_15 |                                   |

| 58              | PN8   | 0    | HSDL_15 |                                   |

| 61              | PN9   | 0    | HSDL_15 |                                   |

| 64              | PN10  | 0    | HSDL_15 |                                   |

| 67              | PN11  | 0    | HSDL_15 | 1                                 |

| 49              | PN12  | 0    | HSDL_15 | -                                 |

| 41              | PN13  | 0    | HSDL_15 | -                                 |

| <b>_</b>   | ration of FB-DIMM | ,           | Duffer         | From et le un                     |

|------------|-------------------|-------------|----------------|-----------------------------------|

| Pin#       | Name              | Pin<br>Type | Buffer<br>Type | Function                          |

| 142        | SN0               | 1           | HSDL_15        | Secondary Northbound Data,        |

| 145        | SN1               | 1           | HSDL_15        | positive lines                    |

| 148        | SN2               | 1           | HSDL_15        |                                   |

| 151        | SN3               | 1           | HSDL_15        |                                   |

| 154        | SN4               | 1           | HSDL_15        |                                   |

| 157        | SN5               | 1           | HSDL_15        |                                   |

| 171        | SN6               | 1           | HSDL_15        |                                   |

| 174        | SN7               | I           | HSDL_15        | Secondary Northbound Data,        |

| 177        | SN8               | I           | HSDL_15        | positive lines                    |

| 180        | SN9               | I           | HSDL_15        |                                   |

| 183        | SN10              | I           | HSDL_15        |                                   |

| 186        | SN11              | 1           | HSDL_15        |                                   |

| 168        | SN12              | I           | HSDL_15        |                                   |

| 160        | SN13              | 1           | HSDL_15        |                                   |

| 143        | SN0               | I           | HSDL_15        | Secondary Northbound Data,        |

| 146        | SN1               | 1           | HSDL_15        | negative lines                    |

| 149        | SN2               | 1           | HSDL_15        |                                   |

| 152        | SN3               | 1           | HSDL_15        |                                   |

| 155        | SN4               | 1           | HSDL_15        |                                   |

| 158        | SN5               | 1           | HSDL_15        |                                   |

| 172        | SN6               | 1           | HSDL_15        |                                   |

| 175        | SN7               | 1           | HSDL_15        |                                   |

| 178        | SN8               | I           | HSDL_15        |                                   |

| 181        | SN9               | 1           | HSDL_15        |                                   |

| 184        | SN10              | 1           | HSDL_15        |                                   |

| 187        | SN11              | 1           | HSDL_15        |                                   |

| 169        | SN12              | 1           | HSDL_15        |                                   |

| 161        | SN13              | 1           | HSDL_15        |                                   |

| Southbound |                   |             |                |                                   |

| 70         | PS0               | 1           | HSDL_15        | Primary Southbound Data, positive |

| 73         | PS1               | 1           | HSDL_15        | lines                             |

| 76         | PS2               | 1           | HSDL_15        |                                   |

| 79         | PS3               | 1           | HSDL_15        | -                                 |

| 82         | PS4               | 1           | HSDL_15        |                                   |

| 93         | PS5               | 1           | HSDL_15        | -                                 |

| 96         | PS6               | 1           | HSDL_15        |                                   |

| 99         | PS7               | 1           | HSDL_15        |                                   |

| 102        | PS8               | 1           | HSDL_15        |                                   |

| 90         | PS9               | 1           | HSDL_15        |                                   |

### Table 5 Pin Configuration of FB-DIMM (cont'd)

| Table 5         Pin Configuration | of FB-DIMM         | (cont'd)    |                |                                             |

|-----------------------------------|--------------------|-------------|----------------|---------------------------------------------|

| Pin#                              | Name               | Pin<br>Type | Buffer<br>Type | Function                                    |

| 71                                | PS0                | 1<br>1      | HSDL_15        | Primary Southbound Data, negative           |

| 74                                | PS1                | 1           | HSDL 15        | lines                                       |

| 77                                | PS2                | 1           | HSDL_15        |                                             |

| 80                                | PS3                | 1           | HSDL_15        | _                                           |

| 83                                | PS4                | 1           | HSDL_15        | _                                           |

| 94                                | PS5                | 1           | HSDL 15        | _                                           |

| 97                                | PS6                | 1           | HSDL_15        | _                                           |

| 100                               | PS7                | 1           | HSDL 15        | _                                           |

| 103                               | PS8                | 1           | HSDL_15        | _                                           |

| 91                                | PS9                | 1           | HSDL_15        | _                                           |

| 190                               | SS0                | 0           | HSDL 15        | Secondary Southbound data,                  |

| 193                               | SS1                | 0           | HSDL_15        | positive lines                              |

| 195                               | SS2                | 0           | HSDL_15        |                                             |

| 190                               | SS3                | 0           | HSDL_15        | _                                           |

| 202                               | SS3<br>SS4         | 0           | HSDL_15        | _                                           |

| 213                               | SS5                |             | _              | Secondary Southbound data                   |

|                                   |                    | 0           | HSDL_15        | Secondary Southbound data, positive lines   |

| 216<br>219                        | SS6<br>SS7         | 0           | HSDL_15        |                                             |

|                                   |                    |             | HSDL_15        | _                                           |

| 222                               | SS8                | 0           | HSDL_15        | _                                           |

| 210                               | SS9                | 0           | HSDL_15        | Occordence Occuthe cound date               |

| 191                               | SS0                | 0           | HSDL_15        | Secondary Southbound data, negative lines   |

| 194                               | SS1                | 0           | HSDL_15        |                                             |

| 197                               | SS2                | 0           | HSDL_15        | _                                           |

| 200                               | SS3                | 0           | HSDL_15        | _                                           |

| 203                               | SS4                | 0           | HSDL_15        | _                                           |

| 214                               | SS5                | 0           | HSDL_15        | _                                           |

| 217                               | SS6                | 0           | HSDL_15        | _                                           |

| 220                               | SS7                | 0           | HSDL_15        | _                                           |

| 223                               | SS8                | 0           | HSDL_15        | _                                           |

| 211                               | SS9                | 0           | HSDL_15        |                                             |

| EEPROM                            |                    |             |                |                                             |

| 120                               | SCL                | I           | CMOS           | Serial Bus Clock                            |

| 119                               | SDA                | I/O         | OD             | Serial Bus Data                             |

| 239                               | SA0                | I           | CMOS           | Serial Address Select Bus 2:0               |

| 240                               | SA1                | I           | CMOS           |                                             |

| 118                               | SA2                | I           | CMOS           |                                             |

| Power Supplies                    | 1                  |             |                |                                             |

| 238                               | V <sub>DDSPD</sub> | PWR         | -              | EEPROM Power Supply                         |

| 9,10,12,13,129,130,132,133        | V <sub>cc</sub>    | PWR         | _              | AMB Core Power / Channel Interface<br>Power |

### Table 5 Pin Configuration of FB-DIMM (cont'd)

| Pin#                             | Name            | Pin  | Buffer | Function                                    |

|----------------------------------|-----------------|------|--------|---------------------------------------------|

|                                  |                 | Туре | Туре   |                                             |

| 15,117,135,237                   | V <sub>TT</sub> | PWR  | -      | Address/Command/Clock                       |

|                                  |                 |      |        | Termination Power                           |

| 1,2,3,5,6,7,108,109,111,112,113, | V <sub>DD</sub> | PWR  | —      | Power Supply                                |

| 115,116,121,122,123,125,126,     |                 |      |        |                                             |

| 127,231,232,233,235,236          |                 |      |        |                                             |

| 4,8,11,14,18,21,24,27,30,33,36,  | V <sub>SS</sub> | GND  | _      | Ground Plane                                |

| 39,42,43,46,47,50,53,56,59,62,   |                 |      |        |                                             |

| 65,68,69,72,75,78,81,84,85,88,   |                 |      |        |                                             |

| 89,92,95,98,101,104,107,110,     |                 |      |        |                                             |

| 114,124,128,131,134,138,141,     |                 |      |        |                                             |

| 144,147,150,153,156,159,162,     |                 |      |        |                                             |

| 163,166,167,170,173,176,179,     |                 |      |        |                                             |

| 182,185,188,189,192,195,198,     |                 |      |        |                                             |

| 201,204,205,208,209,212,215,     |                 |      |        |                                             |

| 218,221,224,227,230,234          |                 |      |        |                                             |

| Other Pins                       |                 |      |        |                                             |

| 19,20,44,45,86,87,105,106,139,   | NC              | NC   | -      | Not connected                               |

| 140,164,165,206,207,225,226      |                 |      |        | Pins not connected on Infineon FB-          |

|                                  |                 |      |        | DIMM's                                      |

| 136                              | VID0            | -    | -      | Voltage ID                                  |

| 16                               | VID1            | -    | _      | Note: These Pins must be unconnected        |

|                                  |                 |      |        | for DDR2-based Fully Buffered               |

|                                  |                 |      |        | DIMMs VID[0] is V <sub>DD</sub> value:      |

|                                  |                 |      |        | OPEN = 1.8 V, GND = 1.5 V;                  |

|                                  |                 |      |        | VID[1] is V <sub>CC</sub> value: OPEN = 1.5 |

|                                  |                 |      |        | V, GND = 1.2 V                              |

| 137                              | Test            | AI   | -      | VREF                                        |

|                                  |                 |      |        | Note: Pin must be unconnected for           |

|                                  |                 |      |        | normal operation                            |

### Table 5 Pin Configuration of FB-DIMM (cont'd)

### Table 6Abbreviations for Buffer Type

| Abbreviation | Description                                                                                                                             |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| HSDL_15      | High-Speed Differential Point-to-Point Link Interface at 1.5 V                                                                          |

| LV-CMOS      | Low Voltage CMOS                                                                                                                        |

| CMOS         | CMOS Levels                                                                                                                             |

| OD           | Open Drain. The corresponding pin has 2 operational states, active low and tristate, and allows multiple devices to share as a wire-OR. |

|              | Table 7 Abbreviations for Fin Type          |  |  |  |  |  |

|--------------|---------------------------------------------|--|--|--|--|--|

| Abbreviation | Description                                 |  |  |  |  |  |

| Ι            | Standard input-only pin. Digital levels.    |  |  |  |  |  |

| 0            | Output. Digital levels.                     |  |  |  |  |  |

| Ι/Ο          | I/O is a bidirectional input/output signal. |  |  |  |  |  |

| AI           | Input. Analog levels.                       |  |  |  |  |  |

| PWR          | Power                                       |  |  |  |  |  |

| GND          | Ground                                      |  |  |  |  |  |

| NU           | Not Usable                                  |  |  |  |  |  |

| NC           | Not Connected                               |  |  |  |  |  |

### Table 7 Abbreviations for Pin Type

**Pin Configuration**

| V <sub>DD</sub> - Pin 001 — V — Pin 002 —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                | (            |           | F                                      | Pin 121 - V <sub>DD</sub>       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------|-----------|----------------------------------------|---------------------------------|

| $V_{DD} = PIII 001$ $V_{DD} = PII 002$ —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                |              |           | — Pin 122 - V <sub>DD</sub>            |                                 |

| $V_{DD} - Pin 003 - V_{DD} - Pin 002 - V_{DD} - Pin 002 - V_{DD} - V_{SS} - Pin 004 - V_$ |                |              |           | Din 104 V                              | Pin 123 - V <sub>DD</sub>       |

| V Dia 005 VSS - FII1 004                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | $\mathbf{H}$   |              |           | FIII 124 - V <sub>SS</sub> r           | Pin 125 - V <sub>DD</sub>       |

| $V_{DD} = Pin 005 - V_{DD} = Pin 006 - V_{DD} = Pi$ |                | )            |           | — Pin 126 - V <sub>DD</sub>            |                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                | (            |           |                                        | Pin 127 - V <sub>DD</sub>       |

| V Dip 000 VSS - FII1000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | $\mathbf{H}$ ( |              |           | FIII 120 - V <sub>SS</sub> F           | Pin 129 - V <sub>cc</sub>       |

| $V_{cc} = Pin 009 - V_{cc} = Pin 010 - V_{cc}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                |              |           | — Pin 130 - V <sub>cc</sub>            |                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $\mathbf{H}$   | (            |           |                                        | Pin 131 - V <sub>ss</sub>       |

| $V_{cc}^{ss}$ - Pin 013 $V_{cc}$ - Pin 012 —<br>V <sub>cc</sub> - Pin 013 $V_{cc}$ - Pin 014 —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                | )            |           |                                        | Pin 133 - V <sub>cc</sub>       |

| V Dia 015 V <sub>SS</sub> - Pin 014                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                | (            |           |                                        |                                 |

| $V_{\rm H}$ - Pin 015 $V_{\rm SS}$ - Pin 014 $-$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | $\mathbf{H}$ / |              |           | - Pin 136 - VID0                       | Pin 135 - V <sub>TT</sub>       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                | )            |           |                                        | Pin 137 - TEST                  |

| V Pin 018                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                | (            |           |                                        |                                 |

| NC - Pin 020                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                |              |           |                                        | Pin 139 - NC                    |

| V - Pin (121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                |              |           |                                        | Pin 141 - V <sub>ss</sub>       |

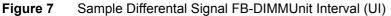

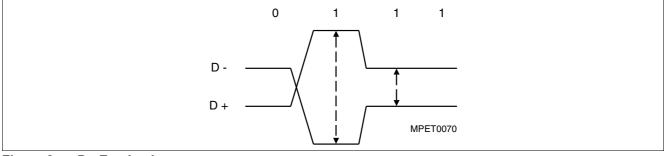

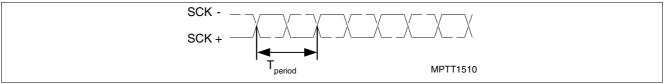

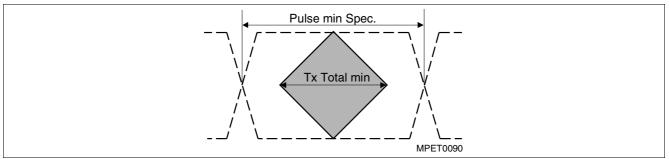

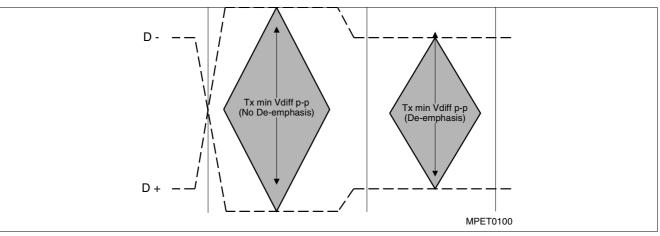

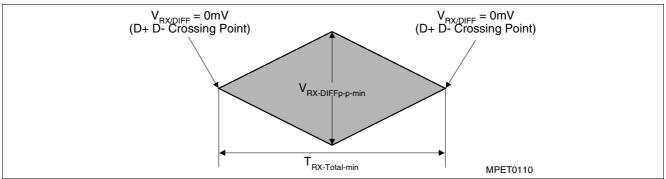

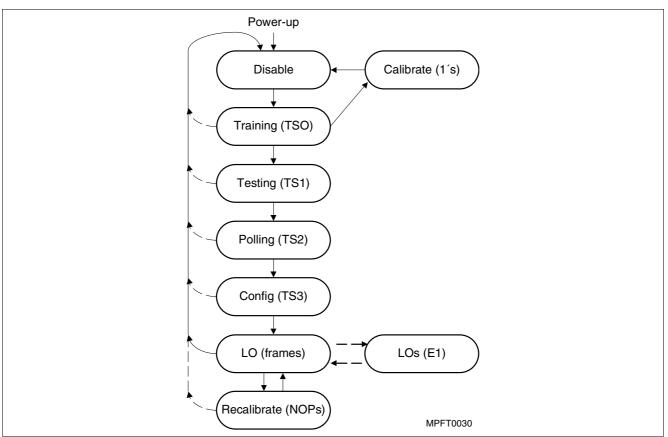

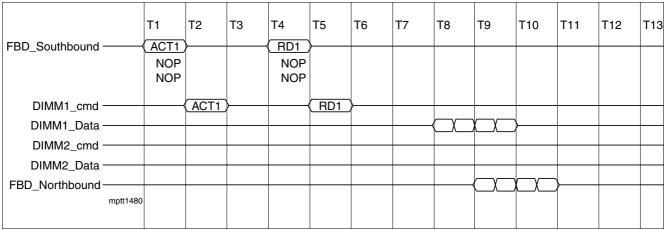

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                | (            |           |                                        |                                 |