## ST7FLCD1

# 8-bit MCU for LCD monitors with 60 KBytes Flash, 2 KBytes RAM, 2 DDC ports and infrared controller

### **Features**

- 60 KBytes Flash program memory

- In-circuit debugging and programming

- In-application programming

- Data RAM: up to 2 KBytes (256 bytes stack, 2 x 256 bytes for DDCs)

- 8 MHz, up to 9 MHz internal clock frequency

- True bit manipulation

- Run and wait CPU modes

- Programmable watchdog for system reliability

- Protection against illegal opcode execution

- 2 DDC bus interfaces with:

- DDC 2B protocol implemented in hardware

- Programmable DDC CI modes

- Enhanced DDC (EDDC) address decoding

- HDCP encryption keys

- Fast I<sup>2</sup>C single master interface

- 8-bit timer with programmable pre-sca.cr. autoreload and independent buzzer ວນເກນ\*

- 8-bit timer with external triuger

- 4-channel, 8-bit analog to digital converter

- 4 + 2 8-bit PWM digital to analog outputs with frequency adjustment

- Infrared controller (IFR)

- Up ιο 23 I/O lines in 28-pin package

- ▼ '≥ imes programmable as interrupt inputs

- Master reset and low voltage detector (LVD) reset

- Complete development support on PC Windows

- Full software package (assembler, linker, Ccompiler and source level debugger)

Order code: ST7FLCD1

## **Description**

The ST7FLCD1 is a microcontrolle: (IACU) from the ST7 family with dedicated peripherals for LCD monitor applications. The STATLCD1 is an industry standard 8-bit core that offers an enhanced instruction set. The 5V supplied processor rules with an external clock at 24 MHz (27 MHz naximum). Under software control, the MCU mode changes to Wait mode thus reducing power consumption. The enhanced instruction set and addressing modes offer real programming potential.

In addition to standard 8-bit data management, the MCU features also include true bit manipulation, 8x8 unsigned multiplication and indirect addressing modes.

The device gathers the on-chip oscillator, CPU, 60-Kbyte Flash, 2-KByte RAM, I/Os, two 8-bit timers, infrared preprocessor, 4-channel Analog-to-Digital Converter, 2 DDCs, I<sup>2</sup>C single master, watchdog, reset and six 8-bit PWM outputs for analog DC control of external functions.

Contents ST7FLCD1

# **Contents**

| 1   | Gene   | ral information                                 | 6          |

|-----|--------|-------------------------------------------------|------------|

|     | 1.1    | Reference documents                             | 7          |

|     | 1.2    | Pin description                                 | 8          |

|     | 1.3    | External connections                            | 9          |

|     | 1.4    | Memory map 1                                    | 1          |

| 2   | Centr  | al processing unit (CPU)                        | 5          |

|     | 2.1    | Main features 1                                 | 5          |

|     |        | 2.1.1 CPU registers                             | 5          |

| 3   | Reset  |                                                 | 2          |

|     | 3.1    | Low voltage detector and watchdog reset         | 2:2        |

|     | 3.2    | Watchdog or illegal operating code access reset | 23         |

|     | 3.3    | External reset                                  |            |

|     | 3.4    | Reset procedure                                 |            |

| 4   | Interr | upts 2                                          | 4          |

|     | 4.1    | Software                                        | :4         |

|     | 4.2    | External interrupts (ITA, ITB)                  | <u>'</u> 4 |

|     | 4.3    | Peripheral interrupts                           | <u>'</u> 4 |

|     | 4.4    | Processing 2                                    | 25         |

|     | 4.5    | Register description                            | :6         |

| 5   | Flash  | program memory                                  | 8          |

| \ ( | 5.1    | Main features 2                                 | 28         |

|     | 5.2    | Structure                                       | 28         |

| 102 | 5.3    | Program memory read-out protection              | 28         |

| , . | 5.4    | ICP (in-circuit programming)                    | :9         |

|     | 5.5    | IAP (in-application programming)                | 0          |

|     | 5.6    | Register description 3                          | ;1         |

|     | 5.7    | Flash option bytes 3                            | 1          |

ST7FLCD1 Contents

| 6    | Clocks and low power modes |                                     |    |  |  |  |  |

|------|----------------------------|-------------------------------------|----|--|--|--|--|

|      | 6.1                        | Clock system                        | 32 |  |  |  |  |

|      |                            | 6.1.1 General description           | 32 |  |  |  |  |

|      |                            | 6.1.2 Crystal oscillator mode       | 32 |  |  |  |  |

|      |                            | 6.1.3 External clock mode           | 32 |  |  |  |  |

|      |                            | 6.1.4 Clock signals                 | 33 |  |  |  |  |

|      | 6.2                        | Power saving modes                  | 33 |  |  |  |  |

|      |                            | 6.2.1 HALT mode                     | 33 |  |  |  |  |

|      |                            | 6.2.2 WAIT mode                     | 33 |  |  |  |  |

|      |                            | 6.2.3 Exit from HALT and WAIT modes | 33 |  |  |  |  |

|      |                            | 6.2.4 Selected peripherals mode     | 35 |  |  |  |  |

| 7    | I/O po                     | orts                                | 36 |  |  |  |  |

|      | 7.1                        | Common functional description       | 37 |  |  |  |  |

|      | 7.2                        | Port A                              | 38 |  |  |  |  |

|      | 7.3                        | Port B                              | 40 |  |  |  |  |

|      | 7.4                        | Port C                              | 42 |  |  |  |  |

|      | 7.5                        | Port D                              | 43 |  |  |  |  |

|      | 7.6                        | Register description                | 44 |  |  |  |  |

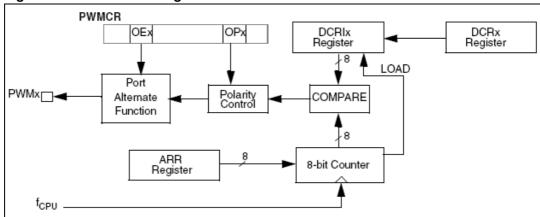

| 8    | PWM                        | generator                           | 46 |  |  |  |  |

|      | 8.1                        | Main features                       |    |  |  |  |  |

|      | 8.2                        | Functional description              |    |  |  |  |  |

|      | 8.3                        | Register description                |    |  |  |  |  |

|      | 0.3                        | Register description                | 49 |  |  |  |  |

| 9    | 8-bit a                    | analog-to-digital converter (ADC)   | 52 |  |  |  |  |

|      | 9.1                        | Main features                       | 52 |  |  |  |  |

| \(   | 9.2                        | Functional description              | 52 |  |  |  |  |

| c0// |                            | 9.2.1 Characteristics               | 52 |  |  |  |  |

| 102  |                            | 9.2.2 Procedure                     | 53 |  |  |  |  |

| ) •  | 9.3                        | Register description                | 54 |  |  |  |  |

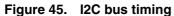

| 10   | I2C si                     | ingle-master bus interface          | 56 |  |  |  |  |

|      | 10.1                       | Main features                       |    |  |  |  |  |

|      | 10.2                       | General description                 | 56 |  |  |  |  |

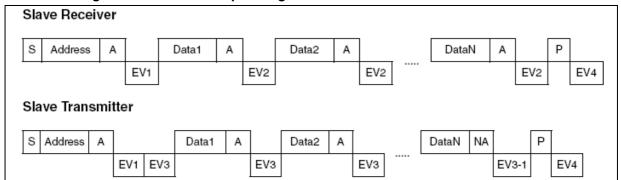

|     | 10.3    | Functional description (master mode)     | 58   |

|-----|---------|------------------------------------------|------|

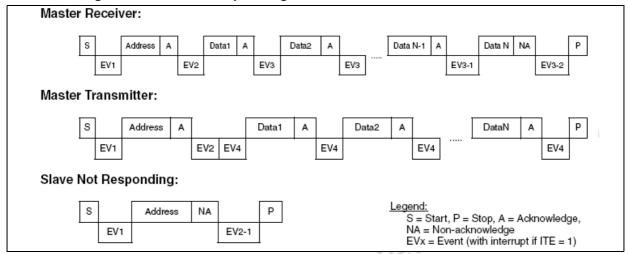

|     | 10.4    | Transfer sequencing                      | 58   |

|     |         | 10.4.1 Master receiver                   | 58   |

|     |         | 10.4.2 Master transmitter                | 58   |

|     | 10.5    | Register description                     | 60   |

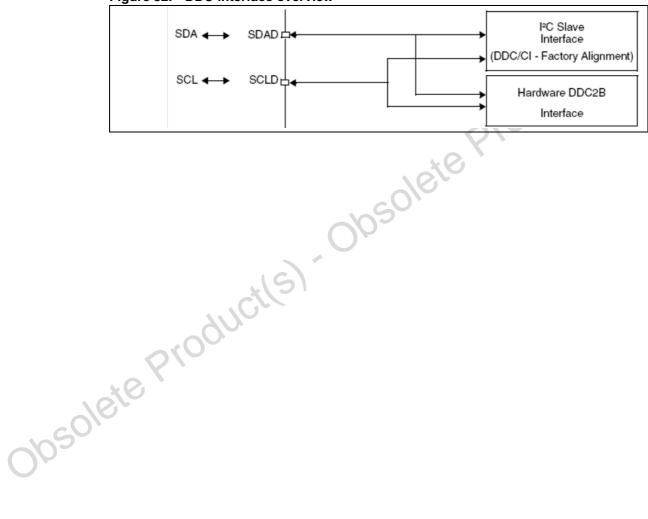

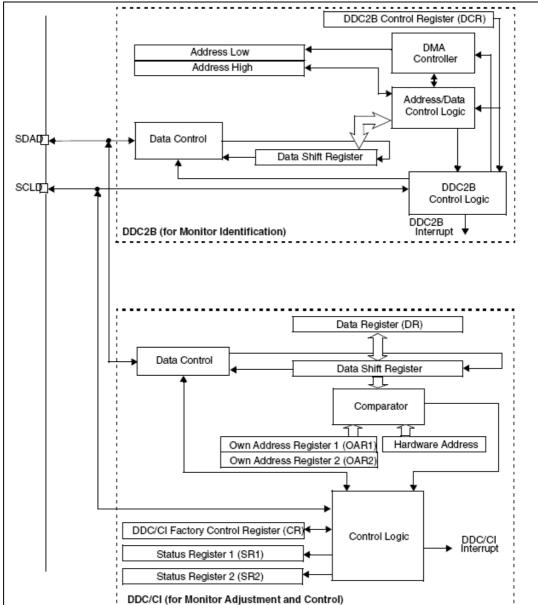

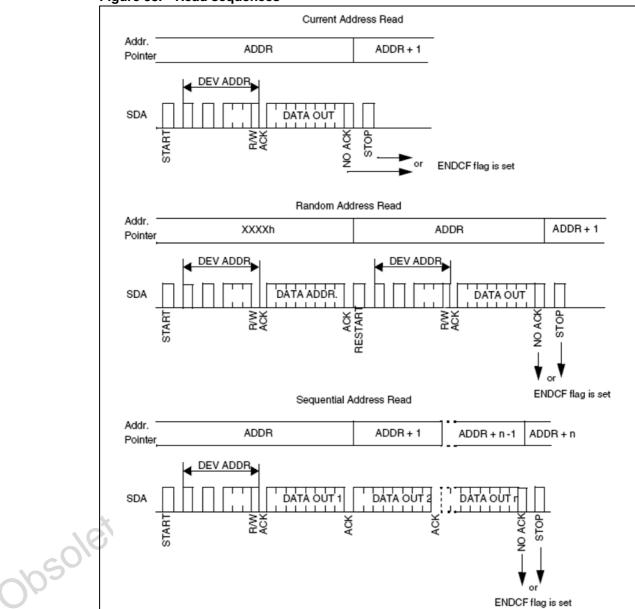

| 11  | Displa  | ay data channel interfaces (DDC)         | 65   |

|     | 11.1    | DDC interface features                   | 65   |

|     |         | 11.1.1 Hardware DDC2B interface features | 65   |

|     |         | 11.1.2 DDC/CI factory interface features | 65   |

|     | 11.2    | Signal description                       | 67   |

|     |         | 11.2.1 Serial data (SDA)                 | 67   |

|     |         | 11.2.2 Serial clock (SCL)                | 68   |

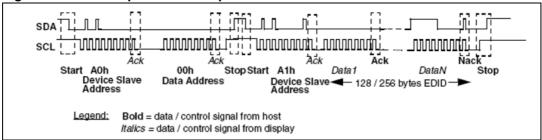

|     | 11.3    | DDC standard                             | 68   |

|     |         | 11.3.1 DDC2B interface                   | 68   |

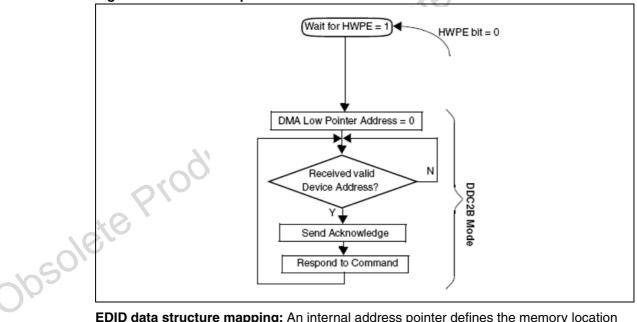

|     |         | 11.3.2 Mode description                  | 69   |

|     | 11.4    | DDC/CI factory alignment interface       | 72   |

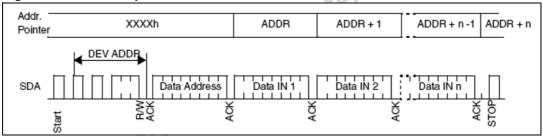

|     |         | 11.4.1 I <sup>2</sup> C modes            | . 72 |

|     | 11.5    | Transfer sequencing                      | 74   |

|     | 11.6    | Transfer sequencing                      |      |

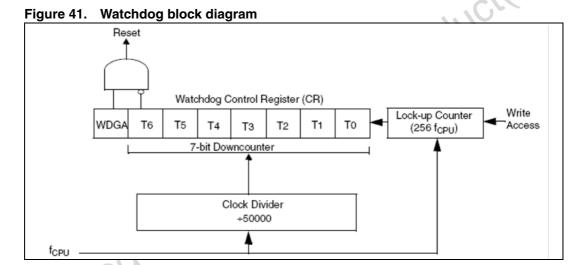

| 12  | Watcl   | hdog timer (WDG)                         | 81   |

|     | 12.1    | Main features                            | 81   |

|     | 12.2    | Main watchdog counter                    | 81   |

|     | 12.3    | Lock-up counter                          | 82   |

|     | 12.4    | Interrupts                               | 82   |

|     | 12.5    | Register description                     | 83   |

| \(  | 3/10    |                                          |      |

| 13  | 8-bit   | timer (TIMA)                             | 84   |

| 103 | 13.1    | Main features                            | 84   |

| , . | 13.2    | Functional description                   | 84   |

|     | 13.3    | Register description                     | 85   |

| 14  | 8-bit t | timer with external trigger (TIMB)       | 87   |

|     | 14.1    | Main features                            | 87   |

|     |         |                                          |      |

| ST7FLCD1 |  | ( | Contents |

|----------|--|---|----------|

|          |  |   |          |

|       | 14.2  | Functional description                 | 87         |

|-------|-------|----------------------------------------|------------|

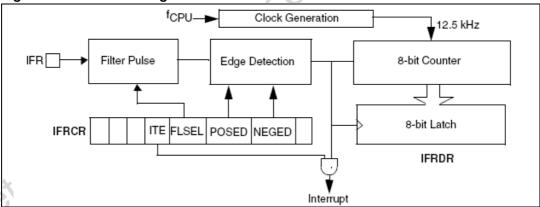

| 15    | Infra | red preprocessor (IFR)                 | <b>9</b> 0 |

|       | 15.1  | Main features                          | 90         |

|       | 15.2  | Functional description                 | 90         |

|       | 15.3  | Register description                   | 91         |

| 16    | Regi  | sters                                  | 93         |

|       | 16.1  | Register description                   | 93         |

| 17    | Elect | rical characteristics                  | <b>9</b> 6 |

|       | 17.1  | Absolute maximum ratings               | 96         |

|       | 17.2  | Power considerations                   | 97         |

|       | 17.3  | Thermal characteristics                | 97         |

|       | 17.4  | AC/DC electrical characteristics       | 98         |

|       | 17.5  | Power on/off electrical specifications | 99         |

|       | 17.6  | Power on/off electrical specifications | 00         |

|       | 17.7  | I2C/DDC bus electrical specifications  | 00         |

|       | 17.8  | I <sup>2</sup> C/DDC bus timings       | 01         |

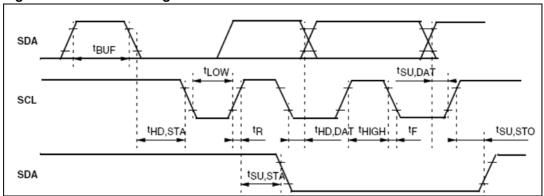

| 18    | Pack  | age mechanical data 10                 |            |

|       | 18.1  | Lead-free packaging                    | 04         |

|       |       | *(5)                                   |            |

| 19    | Revis | sion history 10                        | )5         |

| Obsol |       | 0.000                                  |            |

|       |       | Pic                                    |            |

|       | 3/8   |                                        |            |

| -0    | No.   |                                        |            |

| 0050  |       |                                        |            |

| O     |       |                                        |            |

|       |       |                                        |            |

General information ST7FLCD1

## 1 General information

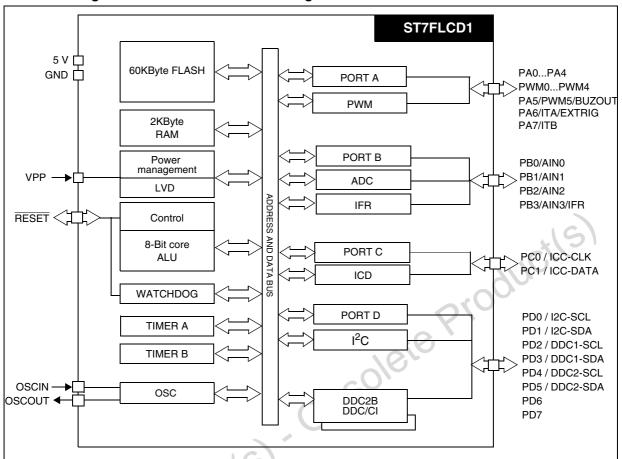

Figure 1. ST7LCD1 functional diagram

Table 1. Abbreviations

|     | Abbreviations | Description                   |

|-----|---------------|-------------------------------|

|     | ADC           | Analog-to-Digital Converter   |

|     | ALU           | Arithmetical and Logical Unit |

| 16  | CPU           | Central Processing Unit       |

| 601 | DDC           | Display Data Channel          |

| 000 | DMA           | Direct Memory Access          |

| 0.  | I2C or IIC    | Inter-Integrated Circuit bus  |

|     | IAP           | In-Application Programming    |

|     | ICC           | In-Circuit Communication      |

|     | ICP           | In-Circuit Programming        |

|     | ICT           | In-Circuit Testing            |

|     | IFR           | Infrared Controller           |

ST7FLCD1 **General information**

Table 1. **Abbreviations (continued)**

| Abbreviations | Description            |

|---------------|------------------------|

| IT            | Interrupt              |

| LCD           | Liquid Crystal Display |

| LVD           | Low Voltage Detector   |

| MCU           | Microcontroller Unit   |

| OSC           | Oscillator             |

| PWM           | Pulse Width Modulator  |

| TIM           | Timer                  |

| WDG           | Watchdog               |

#### 1.1 **Reference documents**

Book: ST7 MCU Family Manual

CD: MCU on CD

Many libraries, software and applications notes are available.

apport coducits. Obsolete Producits. Ask your STMicroelectronics sales office, your local support or search the company web site

General information ST7FLCD1

## 1.2 Pin description

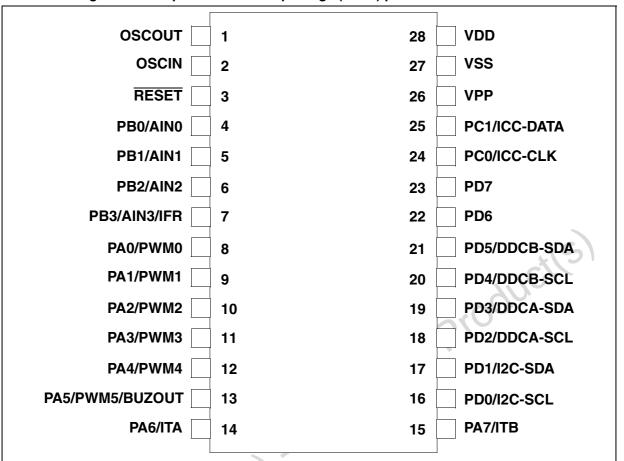

Figure 2. 28-pin small outline package (SO28) pinout

Table 2. 28-pin small outline package pin description

| Pin | Pin name     | Туре | Description                                | Remark              |

|-----|--------------|------|--------------------------------------------|---------------------|

| 1   | OSCOUT       | 0    | Oscillator Input                           | normal use at 24MHz |

| 2   | OSCIN        | I    | Oscillator Output                          | normai use at 24MHZ |

| 3   | RESET        | I/O  | Reset                                      |                     |

| 4   | PB0/AIN0     | I/O  | Port B0 or ADC analog input 0              |                     |

| 5   | PB1/AIN1     | I/O  | Port B1 or ADC analog input 1              |                     |

| 6   | PB2/AIN2     | I/O  | Port B2 or ADC analog input 2              |                     |

| 7   | PB3/AIN3/IFR | I/O  | Port B3 or ADC analog input 3 or IFR input |                     |

| 8   | PA0/PWM0     | I/O  | Port A0 or PWM output 0                    |                     |

| 9   | PA1/PWM1     | I/O  | Port A1 or PWM output 1                    |                     |

| 10  | PA2/PWM2     | I/O  | Port A2 or PWM output 2                    |                     |

ST7FLCD1 General information

Table 2. 28-pin small outline package pin description (continued)

| Pin | Pin name            | Туре | Description                              | Remark                             |

|-----|---------------------|------|------------------------------------------|------------------------------------|

| 11  | PA3/PWM3            | I/O  | Port A3 or PWM output 3                  |                                    |

| 12  | PA4/PWM4            | I/O  | Port A4 or PWM output 4                  |                                    |

| 13  | PA5/PWM5/BUZ<br>OUT | I/O  | Port A5 or PWM output 5 or Buzzer output |                                    |

| 14  | PA6/ITA             | I/O  | Port A6 or interrupt input A             |                                    |

| 15  | PA7/ITB             | I/O  | Port A7 or interrupt input B             |                                    |

| 16  | PD0/I2C-SCL         | I/O  | Port D0 or I2C serial bus clock          |                                    |

| 17  | PD1/I2C-SDA         | I/O  | Port D1 or I2C serial bus data           |                                    |

| 18  | PD2/DDCA-SCL        | I/O  | Port D2 or DDCA serial bus clock         |                                    |

| 19  | PD3/DDCA-SDA        | I/O  | Port D3 or DDCA serial bus data          |                                    |

| 20  | PD4/DDCB-SCL        | I/O  | Port D4 or DDCB serial bus clock         |                                    |

| 21  | PD5/DDCB-SDA        | I/O  | Port D5 or DDCB serial bus data          | .15)                               |

| 22  | PD6                 | I/O  | Port D6                                  |                                    |

| 23  | PD7                 | I/O  | Port D7                                  | 40,0                               |

| 24  | PC0/ICC-CLK         | I/O  | Port C0 or ICC clock                     | 1100                               |

| 25  | PC1/ICC-DATA        | I/O  | Port C1 or ICC data                      |                                    |

| 26  | VPP                 | PS   | FLASH Programming supply voltage         | normal op. mode: 0V <sup>(1)</sup> |

| 27  | VSS                 | PS   | Ground                                   | 0V                                 |

| 28  | VDD                 | PS   | Power supply                             | 5V                                 |

<sup>1.</sup> This pin must be connected to a 10k pulldown resistor, see Section 1.3

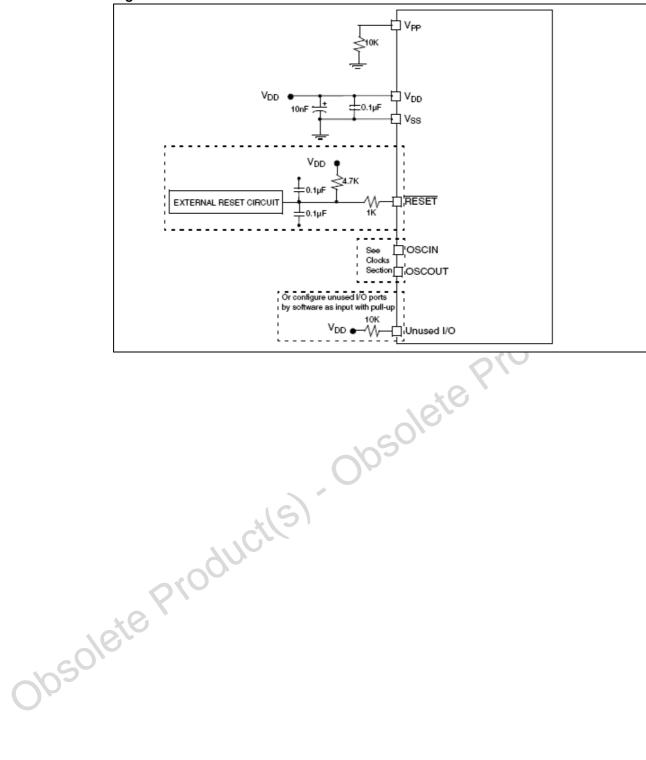

## 1.3 External connections

Figure 3 shows the recommended external connections for the device.

The VPP pin is only used for programming or erasing the Flash memory array, and must be tied to a 10 K pulldown resistor for normal operation.

The 10 nF and 0.1  $\mu$ F decoupling capacitors on the power supply lines are a suggested EMC performance/cost tradeoff. The external RC reset network (including the mandatory 1K serial resistor) is intended to protect the device against parasitic resets, especially in noisy environments. Unused I/Os should be tied high to avoid any unnecessary power consumption on floating lines. An alternative solution is to program the unused ports as inputs with pull-up.

9/106

General information ST7FLCD1

Figure 3. Recommended external connections

ST7FLCD1 General information

## 1.4 Memory map

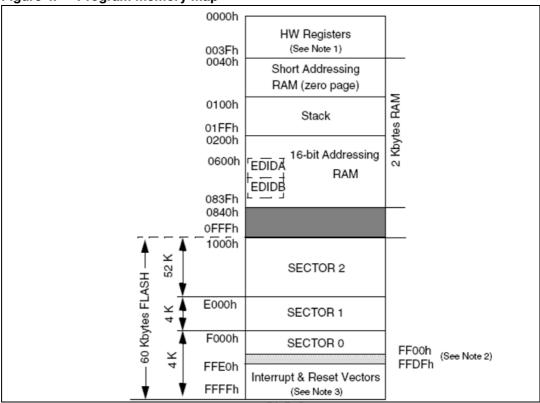

Figure 4. Program memory map

Note: 1 Refer to Table 3

- 2 Area FF00h to FFDFh is reserved in the event of ICD use.

- 3 Refer to Table 4

Table 3. Hardware register memory map

| Address | Block  | Register Label | Register Name                  | Reset Status | Remarks |

|---------|--------|----------------|--------------------------------|--------------|---------|

| 0000h   | NAME   | NAMER          | Circuit name register          | 00h          | Read    |

| 0001h   | MISC   | MISCR          | Miscellaneous register         | 00h          | R/W     |

| 0002h   | Port A | PADR           | Port A data register           | 00h          | R/W     |

| 0003h   | POILA  | PADDR          | Port A data direction register | 00h          | R/W     |

| 0004h   | Port B | PBDR           | Port B data register           | 00h          | R/W     |

| 0005h   |        | PBDDR          | Port B data direction register | 00h          | R/W     |

| 0006h   | Port C | PCDR           | Port C data register           | 00h          | R/W     |

| 0007h   | Port C | PCDDR          | Port C data direction register | 00h          | R/W     |

| 0008h   | Port D | PDDR           | Port D data register           | 00h          | R/W     |

| 0009h   | TOILD  | PDDDR          | Port D data direction register | 00h          | R/W     |

General information ST7FLCD1

Table 3. Hardware register memory map (continued)

| Address | Block            | Block Register Label Register Name F |                                          | Reset Status | Remarks |

|---------|------------------|--------------------------------------|------------------------------------------|--------------|---------|

| 000Ah   | 400              | ADCDR                                | ADC data register                        | 00h          | R       |

| 000Bh   | ADC              | ADCCSR                               | ADC control status register              | 00h          | R/W     |

| 000Ch   | INTERRUPT        | ITRFRE                               | External interrupt register              | 00h          | R/W     |

| 000Dh   | T13.4.4          | TIMCSRA                              | Timer control status register            | 00h          | R/W     |

| 000Eh   | TIMA             | TIMCPRA                              | Timer counter preload register           | 00h          | R/W     |

| 000Fh   |                  | PWMDCR0                              | 8 bits PWM0 duty cycle register          | 00h          | R/W     |

| 0010h   |                  | PWMDCR1                              | 8 bits PWM1 duty cycle register          | 00h          | R/W     |

| 0011h   |                  | PWMDCR2                              | 8 bits PWM2 duty cycle register          | 00h          | R/W     |

| 0012h   |                  | PWMDCR3                              | 8 bits PWM3 duty cycle register          | 00h          | R/W     |

| 0013h   | DIAM             | PWMCRA                               | PWM[03] control register                 | 00h          | R/W     |

| 0014h   | PWM              | PWMARRA                              | PWM[03] auto reload register             | FFh          | R/W     |

| 0015h   |                  | PWMDCR4                              | 8 bits PWM4 duty cycle register          | 00h          | R/W     |

| 0016h   |                  | PWMDCR5                              | 8 bits PWM5 duty cycle register          | 00h          | R/W     |

| 0017h   | <u>.</u>         | PWMCRB                               | PWM[45] control register                 | 00h          | R/W     |

| 0018h   |                  | PWMARRB                              | PWM[45] auto reload register             | FFh          | R/W     |

| 0019h   | FLASH            | FCSR                                 | Flash control/status register            | 00h          | R/W     |

| 001Ah   | Reserved         |                                      | 18:10                                    |              |         |

| 001Bh   | WDG              | WDGCR                                | Watchdog control I register              | 7Fh          | R/W     |

| 001Ch   |                  | I2CCR                                | I2C control register                     | 00h          | R/W     |

| 001Dh   | I <sup>2</sup> C | I2CSR                                | I2C status register                      | 00h          | R       |

| 001Eh   | 150              | I2CCCR                               | I2C clock control register               | 00h          | R/W     |

| 001Fh   |                  | I2CDR 5                              | I2C data register                        | 00h          | R/W     |

| 0020h   |                  | DDCCRA                               | DDC control register                     | 00h          | R/W     |

| 0021h   |                  | DDCSR1A                              | DDC status 1 register                    | 00h          | R       |

| 0022h   | 70               | DDCSR2A                              | DDC status 2 register                    | 00h          | R       |

| 0023h   | DDC A            | DDCOAR1A                             | DDC (7 Bits)<br>slave address 1 register | 00h          | R/W     |

| 0024h   | DDC A            | DDCOAR2A                             | DDC (7 Bits)<br>slave address 2 register | 00h          | R/W     |

| 0025h   |                  | DDCDRA                               | DDC data register                        | 00h          | R/W     |

| 0026h   |                  | RESERVED                             |                                          |              | •       |

| 0027h   |                  | DDCDCRA                              | DDC2B control register                   | 00h          | R/W     |

| 0028h   |                  | DDCCRB                               | DDC control register                     | 00h          | R/W     |

| 0029h   | DDC B            | DDCSR1B                              | DDC status 1 register                    | 00h          | R       |

| 002Ah   |                  | DDCSR2B                              | DDC status 2 register                    | 00h          | R       |

ST7FLCD1 General information

Table 3. Hardware register memory map (continued)

| Address | Block    | Register Label | Register Name                         | Reset Status | Remarks |

|---------|----------|----------------|---------------------------------------|--------------|---------|

| 002Bh   |          | DDCOAR1B       | DDC (7 Bits) slave address 1 register | 00h          | R/W     |

| 002Ch   | DDC B    | DDCOAR2B       | DDC (7 Bits) slave address 2 register | 00h          | R/W     |

| 002Dh   |          | DDCDRB         | DDC data register                     | 00h          | R/W     |

| 002Eh   |          | RESERVED       |                                       |              |         |

| 002Fh   |          | DDCDCRB        | DDC2B control register                | 00h          | R/W     |

| 0030h   |          | DMCR           | Debug control register                | 00h          | R/W     |

| 0031h   |          | DMSR           | Debug status register                 | 10h          | R       |

| 0032h   |          | DMBK1H         | Debug breakpoint 1 MSB register       | FFh          | R/W     |

| 0033h   | DM       | DMBK1L         | Debug breakpoint 1 LSB register       | FFh          | R/W     |

| 0034h   |          | DMBK2H         | Debug breakpoint 2 MSB<br>Register    | FFh          | R/W     |

| 0035h   |          | DMBK2L         | Debug Breakpoint 2 LSB register       | FFh          | R/W     |

| 0036h   | - IFR    | IFRDR          | Counter data register                 | 00h          | R       |

| 0037h   | TIFK     | IFRCR          | Control register                      | 00h          | R/W     |

| 0038h   | TIMD     | TIMCSRB        | Timer control status register         | 00h          | R/W     |

| 0039h   | - TIMB   | TIMCPRB        | Timer counter preload register        | 01h          | R/W     |

| 003Ah   | RESERVED | •              | · O/e                                 | •            | •       |

Table 4. Interrupt vector map

| Vector address | Description                       | Remarks            |

|----------------|-----------------------------------|--------------------|

| FFE0-FFE1h     | Not Used                          | -                  |

| FFE2-FFE3h     | Timer A Overflow interrupt vector | Internal interrupt |

| FFE4-FFE5h     | Timer B Overflow Interrupt Vector | Internal interrupt |

| FFE6-FFE7h     | Not Used                          | -                  |

| FFE8-FFE9h     | I <sup>2</sup> C interrupt vector | Internal interrupt |

| FFEA-FFEBh     | ITB interrupt vector              | External interrupt |

| FFEC-FFEDh     | ITA interrupt vector              | External interrupt |

| FFEE-FFEFh     | IFR interrupt vector              | Internal interrupt |

| FFF0-FFF1h     | Not Used                          |                    |

| FFF2-FFF3h     | DDC2B B interrupt vector          | Internal interrupt |

| FFF4-FFF5h     | DDC/CI B interrupt vector         | Internal interrupt |

| FFF6-FFF7h     | DDC2B A interrupt vector          | Internal interrupt |

| FFF8-FFF9h     | DDC/CI A interrupt vector         | Internal interrupt |

| FFFA-FFFBh     | Not Used                          | -                  |

13/106

General information ST7FLCD1

Table 4. Interrupt vector map (continued)

| Vector address | Description                      | Remarks       |

|----------------|----------------------------------|---------------|

| FFFC-FFFDh     | TRAP (software) interrupt vector | CPU interrupt |

| FFFE-FFFFh     | RESET vector                     | -             |

14/106

## 2 Central processing unit (CPU)

This CPU has a full 8-bit architecture and contains six internal registers allowing efficient 8-bit data manipulation.

## 2.1 Main features

- Enable executing 63 basic instructions

- Fast 8-bit by 8-bit multiply

- 17 main addressing modes (with indirect addressing mode)

- Two 8-bit index registers

- 16-bit stack pointer

- 8 MHz CPU internal frequency (9 MHz max)

- Low power modes: WAIT and HALT

- Maskable hardware interrupts

- Non-maskable software interrupt

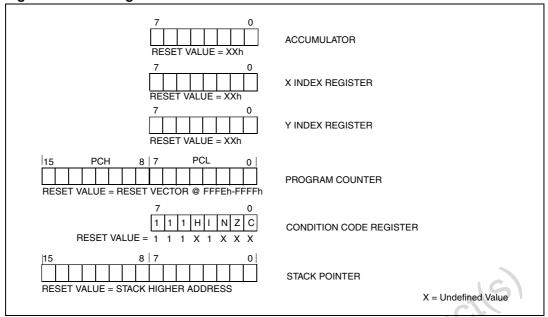

## 2.1.1 CPU registers

The 6 CPU registers shown in *Figure 5* are not present in the memory mapping and are accessed by specific instructions.

#### Accumulator (A)

The Accumulator is an 8-bit general purpose register that holds operands and results of arithmetic and logic calculations. It also manipulates data.

#### Index registers (X and Y)

In indexed addressing modes, these 8-bit registers are used to create either effective addresses or temporary storage areas for data manipulation. (The Cross-Assembler generates a previous instruction (PRE) to indicate that next instruction refers to Y register.)

The Y register is not affected by interrupt automatic procedures (not pushed to and popped from the stack).

#### Program counter (PC)

The program counter is a 16-bit register containing the address of next instruction the CPU executes. The program counter consists of two 8-bit registers:

- PCL (Program Counter Low which is the LSB)

- PCH (Program Counter High which is the MSB).

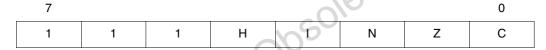

### Condition code register (CC)

Read/Write

Reset Value: 111x1XXX

The 8-bit condition code register contains the interrupt mask and four flags resulting from the instruction just executed. This register can also be handled by the PUSH and POP instructions.

These bits can be individually tested and/or controlled by specific instructions.

### Bit 4 = H half carry

This bit is set by hardware when a carry occurs between bits 3 and 4 of the ALU during an ADD or ADC instruction. It is reset by hardware during the same instructions.

0: No half carry has occurred.

1: A half carry has occurred.

This bit is tested using the JRH or JRNH instruction. The H bit is useful in BCD arithmetic subroutines.

Note: Instruction groups are defined in Table 6.

#### Bit 3 = I interrupt mask

This bit is set by hardware when entering in interrupt or by software to disable all interrupts except the TRAP software interrupt. This bit is cleared by software.

0: Interrupts are enabled.

1: Interrupts are disabled.

This bit is controlled by the RIM, SIM and IRET instructions and is tested by the JRM and JRNM instructions.

Interrupts requested while I is set are latched and processed when I is cleared. By default an interrupt routine is not interruptible as I bit is set by hardware when you enter it and reset by the IRET instruction at the end of interrupt routine. In case I bit is cleared by software during the interrupt routine, pending interrupts are serviced regardless of the priority level of the current interrupt routine.

#### Bit 2 = N negative

This bit is set and cleared by hardware. It is representative of the result sign of the last arithmetic, logical or data manipulation. It is a copy of the 7<sup>th</sup> bit of the result.

- 0: The last operation result is positive or null.

- 1: The last operation result is negative (i.e. the most significant bit is a logic 1).

This bit is accessed by the JRMI and JRPL instructions.

#### Bit 1 = Z zero

This bit is set and cleared by hardware. This bit indicates that the result of the last arithmetic, logical or data manipulation is zero.

- 0: The result of the last operation is different from zero.

- 1: The result of the last operation is zero.

This bit is accessed by the JREQ and JRNE test instructions.

#### Bit 0 = C carry/borrow

This bit is set and cleared by hardware and software. Informs if an overflow or underflow occurred during the last arithmetic operation.

- 0: No overflow or underflow has occurred.

- 1: An overflow or underflow has occurred.

This bit is driven by the SCF and RCF instructions and tested by the JRC and JRNC instructions. It is also affected by the "bit test and branch", shift and rotate instructions.

#### Stack pointer (SP)

#### Read/Write

Reset Value: 01 FFh

| 15  |     |     |     |     |     |     | 8   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   |

| 7   |     |     |     |     |     |     | 0   |

| SP7 | SP6 | SP5 | SP4 | SP3 | SP2 | SP1 | SP0 |

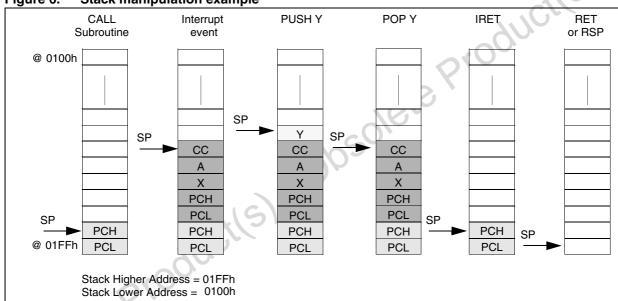

The stack pointer is a 16-bit register always pointing to the next free location in the stack. The pointer value increments when data is taken from the stack, it decrements once data is transferred into the stack (see *Figure 6*).

Since the stack is 256 bytes deep, the most significant byte is forced by hardware. Following an MCU Reset, or after a Reset Stack Pointer instruction (RSP), the Stack Pointer contains its reset value (the SP7 to SP0 bits are set) which is the stack highest address.

The least significant byte of the Stack Pointer (called S) can be directly accessed by a LD instruction.

Note:

When the lower limit is exceeded, the Stack Pointer wraps around stack upper limit, without indicating stack overflow. The previously stored information is then overwritten and therefore lost. Stack also wraps in case of underflow.

Stack is used to save return address during a subroutine call and CPU context during interrupt. You can directly manipulate the stack using PUSH and POP instructions. In case of interrupt, PCL is stored at the first location pointed to by the SP. Other registers are then stored in the next locations as shown in *Figure 6*.

When interrupt is received, the SP value decrements and the context is pushed to the stack.

On return from interrupt, the SP value increments and the context is popped from the stack.

A subroutine call and interrupt occupy two and five locations in the stack area respectively.

Figure 6. Stack manipulation example

Table 5. Instruction set

|                     |       |       |       | l     |       |       |       |       |

|---------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| -c0.                | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

| Load and transfer   | LD    | CLR   |       |       |       |       |       |       |

| Stack operation     | PUSH  | POP   | RSP   |       |       |       |       |       |

| Increment/decrement | INC   | DEC   |       |       |       |       |       |       |

| Compare and tests   | СР    | TNZ   | ВСР   |       |       |       |       |       |

| Logical operations  | AND   | OR    | XOR   | CPL   | NEG   |       |       |       |

| Bit operations      | BSET  | BRES  |       |       |       |       |       |       |

Table 5. Instruction set (continued)

|                                  | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Conditional bit test and branch  | BTJT  | BTJF  |       |       |       |       |       |       |

| Arithmetic operations            | ADC   | ADD   | SUB   | SBC   | MUL   |       |       |       |

| Shift and rotates                | SLL   | SRL   | SRA   | RLC   | RRC   | SWAP  | SLA   |       |

| Unconditional jump or call       | JRA   | JRT   | JRF   | JP    | CALL  | CALLR | NOP   | RET   |

| Conditional branch               | JRXX  |       |       |       |       |       |       |       |

| Interruption management          | TRAP  | WFI   | HALT  | IRET  |       |       |       |       |

| Code condition flag modification | SIM   | RIM   | SCF   | RCF   |       |       |       |       |

Table 6. Instruction groups

| Mnemo | Description              | Function/Example      | Dst       | Src | Н | U | N | z | С |

|-------|--------------------------|-----------------------|-----------|-----|---|---|---|---|---|

| ADC   | Add with Carry           | A = A + M + C         | Α         | M   | H |   | N | Z | С |

| ADD   | Addition                 | A = A + M             | Α         | М   | Н |   | N | Z | С |

| AND   | Logical And              | A = A . M             | Α         | М   |   |   | N | Z |   |

| ВСР   | Bit compare A, Memory    | tst (A . M)           | Α         | М   |   |   | N | Z |   |

| BRES  | Bit Reset                | bres Byte, #3         | М         |     |   |   |   |   |   |

| BSET  | Bit Set                  | bset Byte, #3         | М         |     |   |   |   |   |   |

| BTJF  | Jump if bit is false (0) | btjf Byte, #3, Jmp1   | М         |     |   |   |   |   | С |

| BTJT  | Jump if bit is true (1)  | btjt Byte, #3, Jmp1   | М         |     |   |   |   |   | С |

| CALL  | Call subroutine          |                       |           |     |   |   |   |   |   |

| CALLR | Call subroutine relative |                       |           |     |   |   |   |   |   |

| CLR   | Clear                    |                       | reg,<br>M |     |   |   | 0 | 1 |   |

| СР    | Arithmetic Compare       | tst(Reg - M)          | reg       | М   |   |   | N | Z | С |

| CPL   | One Complement           | A = FFH-A             | reg,<br>M |     |   |   | N | Z | 1 |

| DEC   | Decrement                | dec Y                 | reg,<br>M |     |   |   | N | Z |   |

| HALT  | Halt                     | reset when WDG active |           |     |   | 0 |   |   |   |

| IRET  | Interrupt routine return | Pop CC, A, X, PC      |           |     | Н | I | N | Z | С |

Table 6. Instruction groups (continued)

| Mnemo | Description                | Function/Example   | Dst        | Src       |   | Н | I | N | Z | С |

|-------|----------------------------|--------------------|------------|-----------|---|---|---|---|---|---|

| INC   | Increment                  | inc X              | reg,<br>M  |           |   |   |   | N | Z |   |

| JP    | Absolute Jump              | jp [TBL.w]         |            |           |   |   |   |   |   |   |

| JRA   | Jump relative always       |                    |            |           |   |   |   |   |   |   |

| JRT   | Jump relative              |                    |            |           |   |   |   |   |   |   |

| JRF   | Never jump                 | jrf *              |            |           |   |   |   |   |   |   |

| JRIH  | Jump if ext. interrupt = 1 |                    |            |           |   |   |   |   |   |   |

| JRIL  | Jump if ext. interrupt = 0 |                    |            |           |   |   |   |   |   |   |

| JRH   | Jump if H = 1              | H = 1 ?            |            |           |   |   |   |   |   |   |

| JRNH  | Jump if H = 0              | H = 0 ?            |            |           |   |   |   |   |   |   |

| JRM   | Jump if I = 1              | I = 1 ?            |            |           |   |   |   | X | 9 | 1 |

| JRNM  | Jump if I = 0              | I = 0 ?            |            |           |   | 7 |   | כ |   |   |

| JRMI  | Jump if N = 1 (minus)      | N = 1 ?            |            |           | ( | 5 |   |   |   |   |

| JRPL  | Jump if N = 0 (plus)       | N = 0 ?            |            | 8         |   |   |   |   |   |   |

| JREQ  | Jump if Z = 1 (equal)      | Z = 1 ?            |            | 3         |   |   |   |   |   |   |

| JRNE  | Jump if Z = 0 (not equal)  | Z = 0 ?            | 10         |           |   |   |   |   |   |   |

| JRC   | Jump if C = 1              | C = 1?             |            |           |   |   |   |   |   |   |

| JRNC  | Jump if C = 0              | C = 0 ?            |            |           |   |   |   |   |   |   |

| JRULT | Jump if C = 1              | Unsigned <         |            |           |   |   |   |   |   |   |

| JRUGE | Jump if C = 0              | Jmp if unsigned >= |            |           |   |   |   |   |   |   |

| JRUGT | Jump if $(C + Z = 0)$      | Unsigned >         |            |           |   |   |   |   |   |   |

| JRULE | Jump if $(C + Z = 1)$      | Unsigned <=        |            |           |   |   |   |   |   |   |

| LD    | Load                       | dst <= src         | reg,<br>M  | M,<br>reg |   |   |   | N | Z |   |

| MUL   | Multiply                   | X,A = X * A        | A, X,<br>Y | X, Y,     |   | 0 |   |   |   | 0 |

| NEG   | Negate (2's compl)         | neg \$10           | reg,<br>M  |           |   |   |   | N | Z | С |

| NOP   | No Operation               |                    |            |           |   |   |   |   |   |   |

| OR    | OR operation               | A = A + M          | Α          | М         |   |   |   | N | Z |   |

| POP   | Pop from the Stack         | pop reg            | reg        | М         |   |   |   |   |   |   |

|       |                            | pop CC             | CC         | М         |   | Н | I | N | Z | С |

Table 6. Instruction groups (continued)

| Mnemo | Description            | Function/Example    | Dst       | Src        |   | Н | I   | N   | z | С |

|-------|------------------------|---------------------|-----------|------------|---|---|-----|-----|---|---|

| PUSH  | Push onto the Stack    | push Y              | М         | reg,<br>CC | • |   |     |     |   |   |

| RCF   | Reset carry flag       | C = 0               |           |            | • |   |     |     |   | 0 |

| RET   | Subroutine Return      |                     |           |            |   |   |     |     |   |   |

| RIM   | Enable Interrupts      | I = 0               |           |            |   |   | 0   |     |   |   |

| RLC   | Rotate left true C     | C <= Dst <= C       | reg,<br>M |            |   |   |     | N   | Z | С |

| RRC   | Rotate right true C    | C => Dst => C       | reg,<br>M |            |   |   |     | N   | Z | С |

| RSP   | Reset Stack Pointer    | S = Max allowed     |           |            |   |   |     |     |   |   |

| SBC   | Subtract with Carry    | A = A - M - C       | Α         | М          | • |   |     | N   | Z | С |

| SCF   | Set carry flag         | C = 1               |           |            |   |   | . ( | -11 | ) | 1 |

| SIM   | Disable Interrupts     | I = 1               |           |            |   | 2 | 1   |     |   |   |

| SLA   | Shift left Arithmetic  | C <= Dst <= 0       | reg,<br>M | Q          |   | ) |     | N   | Z | С |

| SLL   | Shift left Logic       | C <= Dst <= 0       | reg,<br>M | 3          |   |   |     | N   | Z | С |

| SRL   | Shift right Logic      | 0 => Dst => C       | reg,<br>M |            |   |   |     | 0   | Z | С |

| SRA   | Shift right Arithmetic | Dst7 => Dst => C    | reg,<br>M |            |   |   |     | Ζ   | Z | С |

| SUB   | Subtraction            | A = A - M           | Α         | М          |   |   |     | N   | Z | С |

| SWAP  | SWAP nibbles           | Dst[74] <=> Dst[30] | reg,<br>M |            |   |   |     | N   | Z |   |

| TNZ   | Test for Neg & Zero    | tnz lbl1            |           |            |   |   |     | Ν   | Z |   |

| TRAP  | S/W trap               | S/W interrupt       |           |            |   |   | 1   |     |   |   |

| WFI   | Wait for Interrupt     |                     |           |            |   |   | 0   |     |   |   |

| XOR   | Exclusive OR           | A = A XOR M         | Α         | М          |   |   |     | N   | Z |   |

**\_**y/

ST7FLCD1 Reset

#### 3 Reset

The reset procedure provides an orderly software start-up or quits low power modes.

Three reset modes are provided:

- Low voltage detector reset,

- 2. Watchdog or illegal operating code access reset,

- External reset at the RESET pin.

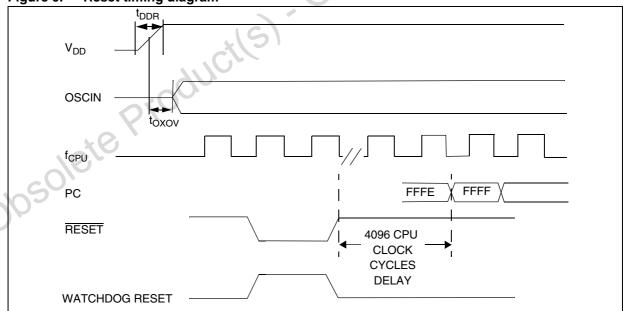

At reset, the reset vector is fetched from FFFEh and FFFFh addresses and loaded into the PC (the program execution starting from this point).

An internal circuitry provides a 4096 CPU clock cycle delay as soon as that the oscillator becomes active.

# 3.1 Low voltage detector and watchdog reset Productie

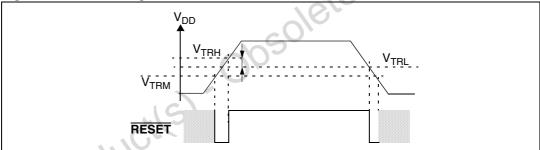

The low voltage detector circuitry generates a reset when:

V<sub>DD</sub> is above V<sub>TRM</sub>,

$V_{DD}$  is below  $V_{TRH}$  when  $V_{DD}$  is rising,

V<sub>DD</sub> is below V<sub>TRL</sub> when V<sub>DD</sub> is falling (*Figure 7*)

Figure 7. Low voltage detector

Typical hysteresis (V<sub>TRH</sub>-V<sub>TRL</sub>) of 250 mV

This circuitry is active only when V<sub>DD</sub> is higher than V<sub>TRM</sub>.

During low voltage detector Reset, the RESET pin is held low, thus permitting the MCU to reset other devices.

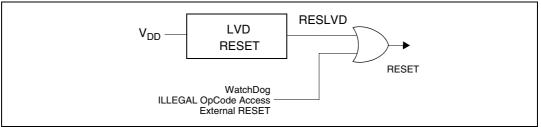

During a watchdog reset, the RESET pin is pulled low permitting the MCU to reset other devices as when low voltage (Figure 8). The reset cycle is pulled low during 500ns typically. ST7FLCD1 Reset

Figure 8. Reset generation diagram

## 3.2 Watchdog or illegal operating code access reset

For more information regarding the watchdog, refer to Section 12.

An illegal opcode reset occurs if the MCU attempts to read and execute a code that does not match a valid ST7 instruction.

## 3.3 External reset

The external reset is an active low input signal applied to RESET pin of MCU.

As shown in *Figure 9*, RESET signal must remain low for a minimum of 1µs.

Internal Schmitt trigger and filter provided at the RESET pin improve noise immunity.

## 3.4 Reset procedure

At power-up, the MCU follows the sequence described in Figure 9.

Figure 9. Reset timing diagram

Note: Refer to Electrical Characteristics for values of  $t_{DDR}$ ,  $t_{OXOV}$ ,  $V_{TRH}$ ,  $V_{TRL}$  and  $V_{TRM}$

Interrupts ST7FLCD1

## 4 Interrupts

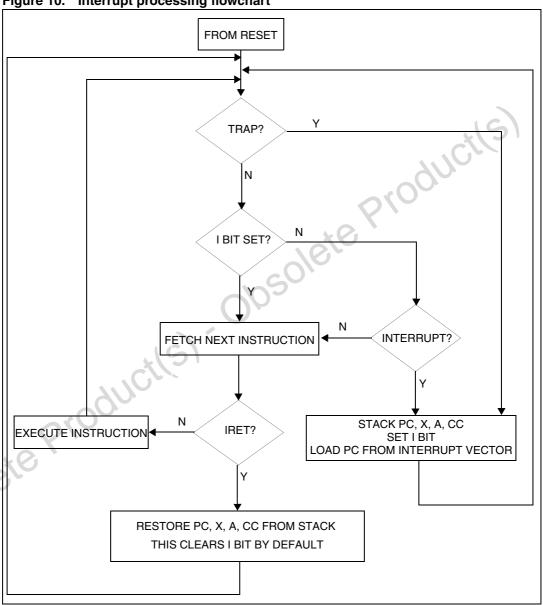

There are two different methods to interrupt the ST7:

- 1. Maskable hardware interrupts as listed in *Table 8*

- 2. Non-maskable software interrupt (TRAP).

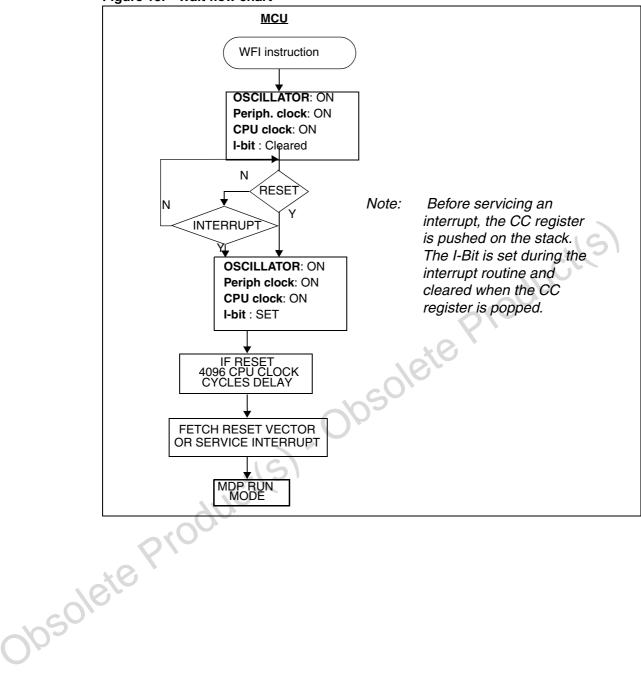

The Interrupt processing flowchart is shown in Figure 10.

Only enabled maskable interrupts are serviced. However, disabled interrupts are latched and processed. For an interrupt to be serviced, PC, X, A and CC registers are saved onto the stack, interrupt mask (I bit of the Condition Code Register) is set to prevent additional interrupts. Y register is not automatically saved.

The PC is then loaded with interrupt vector, the interrupt service routine runs (refer to *Table 8* for vector addresses) and ends with the IRET instruction. With this letter, registers contents are recovered from the stack and normal processing resumes.

Note: I bit is then cleared providing that the corresponding bit stored in the stack is zero.

Though many interrupts can be run simultaneously, a priority order is defined (see *Table 8*). The RESET pin has the highest priority.

If I bit is set, only TRAP interrupt is enabled.

All interrupts allow the processor to exit WAIT low power mode.

## 4.1 Software

The software interrupt is the executable instruction TRAP. The interrupt is recognized when the TRAP instruction is executed, regardless of I bit state. When interrupt is recognized, it is serviced according to flowchart described in *Figure 10*.

Note: During ICC communication the TRAP interrupt is reserved.

## 4.2 External interrupts (ITA, ITB)

The ITA (PA6), ITB (PA7) pins generate an interrupt when a falling or rising edge occurs on these pins. These interrupts are enabled with ITAITE, ITBITE bits respectively, in ITRFRE register, also providing that I bit from CC register is reset. Each external interrupt has an interrupt vector that uses ITRFRE register.

## 4.3 Peripheral interrupts

The various peripheral devices with interrupts include both Display Data Channels (DDC A and DDC B), the Infrared Controller (IFR), two 8-bit timers (Timer A and Timer B) and the I<sup>2</sup>C interface.

Different peripheral interrupt flags fetch an interrupt if the I bit from the CC register is reset and the corresponding Enable bit is set. If any of these conditions is not fulfilled, the interrupt is latched but not serviced, thus remaining pending.

ST7FLCD1 Interrupts

#### 4.4 **Processing**

Interrupt flags are located in the status register. The Enable bits are in the control register. When an enabled interrupt occurs, normal processing is suspended at the end of the current instruction execution. It is then serviced according to the flowchart from Figure 10.

The general sequence for clearing an interrupt is an access to the status register while the flag is set followed by a read or write of an associated register. Note that the clearing sequence resets the internal latch. A pending interrupt (i.e. waiting for being enabled) will therefore be lost if the clear sequence is executed.

Figure 10. Interrupt processing flowchart

25/106

Interrupts ST7FLCD1

## 4.5 Register description

#### Table 7. External interrupt register map

| Address | Reset |     | Register | bit 7 | bit 6 | bit 5       | bit 4  | bit 3  | bit 2       | bit 1  | bit 0  |

|---------|-------|-----|----------|-------|-------|-------------|--------|--------|-------------|--------|--------|

| 000Ch   | 00h   | R/W | ITRFRE   | 0     | 0     | ITB<br>EDGE | ITBLAT | ITBITE | ITA<br>EDGE | ITALAT | ITAITE |

#### **External interrupt register (ITRFRE)**

Read/Write

Reset value:00h

| 7 | 6 | 5       | 4      | 3      | 2       | 1      | 0      |

|---|---|---------|--------|--------|---------|--------|--------|

| 0 | 0 | ITBEDGE | ITBLAT | ITBITE | ITAEDGE | ITALAT | ITAITE |

Bit 7 = Reserved. Force by hardware to 0.

Bit 6 = Reserved. Force by hardware to 0.

Bit 5 = ITBEDGE Interrupt B Edge Selection. This bit is set and cleared by software.

0: Falling edge detected on ITB (default)

1: Rising edge detected on ITB

**Bit 4 = ITBLAT** Falling or Rising Edge Detector Latch. This bit is set by hardware, when a falling or rising edge, depending on the sensitivity, occurs on ITB/PA7 pin. An interrupt is generated if ITBITE=1. It is cleared by software.

0: No edge detected on ITB (default)

1: Edge detected on ITB

Bit 3 = ITBITE ITB Interrupt Enable. This bit is set and cleared by software.

0: ITB interrupt disabled (default)

1: ITB interrupt enabled

Bit 2 = ITAEDGE Interrupt A Edge Selection. This bit is set and cleared by software.

0: Falling edge detected on ITA (default)

1: Rising edge detected on ITA

**Bit 1 = ITALAT** Falling or Rising Edge Detector Latch. This bit is set by hardware when a falling or a rising edge, depending on the sensitivity, occurs on ITA/PA6 pin. An interrupt is generated if ITAITE=1. It is cleared by software.

0: No edge detected on ITA (default)

1: Edge detected on ITA

Bit 0 = ITAITE ITA Interrupt Enable. This bit is set and cleared by software.

0: ITA interrupt disabled (default)

1: ITA interrupt enabled

ST7FLCD1 Interrupts

Table 8. Interrupt mapping

| Source block | Description                       | Register<br>label  | Flag   | Maskable | Vector address | Priority order     |

|--------------|-----------------------------------|--------------------|--------|----------|----------------|--------------------|

| RESET        | Reset                             | N/A                | N/A    | no       | FFFEh-FFFFh    |                    |

| TRAP         | Software                          | N/A                | N/A    | no       | FFFCh-FFFDh    |                    |

| Not used     |                                   |                    | •      | •        | FFFAh-FFFBh    |                    |

| DDC/CI A     | DDC Interrupt                     | DDCSR1A<br>DDCSR2A | **     | yes      | FFF8h-FFF9h    |                    |

| DDC2B A      | End of communication<br>Interrupt | DDCDCRA            | ENDCF  | yes      | FFF6h-FFF7h    | Highes<br>Priority |

| DDC2B A      | End of download<br>Interrupt      | DDCDCRA            | EDF    | yes      | FFF6h-FFF7h    |                    |

| DDC/CI B     | DDC Interrupt                     | DDCSR1B<br>DDCSR2B | **     | yes      | FFF4h-FFF5h    |                    |

| DDC2B B      | End of communication<br>Interrupt | DDCDCRB            | ENDCF  | yes      | FFF2h-FFF3h    | 1/9                |

| DDC2B B      | End of download<br>Interrupt      | DDCDCRB            | EDF    | yes      | FFF2h-FFF3h    |                    |

| Not used     |                                   |                    |        |          | FFF0h-FFF1h    |                    |

| IFR          | IFR Interrupt                     | IFRCR              |        | yes 🗼 🔾  | FFEEh-FFEFh    |                    |

| Port A bit 6 | External Interrupt ITA            | ITRFRE             | ITALAT | 76,      | FFECh-FFEDh    |                    |

| Port A bit 7 | External Interrupt ITB            | ITRFRE             | ITBLAT | yes      | FFEAh-FFEBh    | ▼                  |

| I2C          | I2C Peripheral<br>Interrupts      | I2CSR1<br>I2CSR2   | 40,0   | yes      | FFE8h-FFE9h    | Lowes<br>Priority  |

| Not used     |                                   | 10                 | '      | <u> </u> | FFE6h-FFE7h    |                    |

| TIMB         | Timer B overflow                  | TIMCSRB            | TOF    | yes      | FFE4h-FFE5h    |                    |

| TIMA         | Timer A overflow                  | TIMCSRA            | TOF    | yes      | FFE2h-FFE3h    |                    |

|              | 72                                | •                  | •      | •        | FFE0h-FFE1h    | 1                  |

## 5 Flash program memory

The ST7 dual voltage High Density Flash (HDFlash) is a non-volatile memory that can be electrically erased as a single block or by individual sectors and programmed on a Byte-by-Byte basis using an external Vpp supply.

The HDFlash devices can be programmed and erased off-board (plugged in a programming tool) or on-board using ICP (In-Circuit Programming) IAP (In-Application Programming).

The array matrix organisation allows each sector to be erased and reprogrammed without affecting other sectors.

### 5.1 Main features

- Three Flash programming modes:

- Insertion in a programming tool. In this mode, all sectors including option bytes can be programmed or erased

- ICP (In-Circuit Programming). In this mode, all sectors including option bytes can be programmed or erased without removing the device from the application board.

- IAP (In-Application programming). In this mode, all sectors except Sector 0 can be programmed or erased without removing the device from the application board and while the application is running.

- ICT (In-Circuit Testing) for downloading and executing user application test patterns in RAM

- Read-out protection against piracy

- Register Access Security System (RASS) to prevent accidental programming or erasing

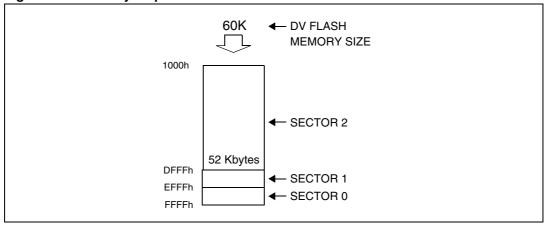

#### 5.2 Structure

The Flash memory is organized in sectors and can be used for both code and data storage.

Depending on the overall Flash memory size in the microcontroller device, three user sectors are available. Each sector is independently erasable. Thus, complete erasing of the whole Flash memory is avoided when only partial erasing is required.

The first two sectors have a fixed size of 4 Kbyte (see *Figure 11*). They are mapped in the upper part of the ST7 addressing space to the reset and interrupt vectors are located in Sector 0 (F000h-FFFFh).

## 5.3 Program memory read-out protection

The read-out protection is enabled through an option bit.

When this option is selected, the programs and data stored in the program memory (Flash or ROM) are protected against read-out piracy (including a re-write protection). In Flash devices, when this protection is removed by reprogramming the Option Byte, the entire program memory is first automatically erased. Refer to the *Section 5.7* for more details.

Figure 11. Memory map and sector address.

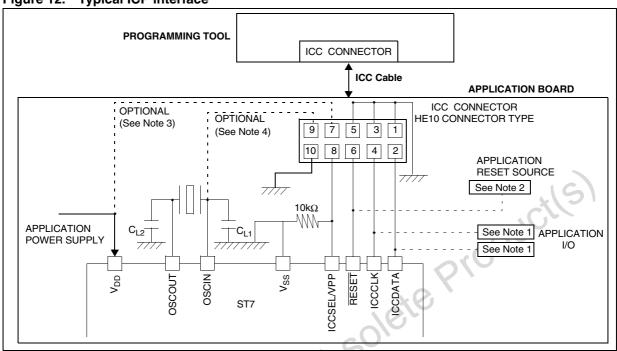

## 5.4 ICP (in-circuit programming)

To perform ICP, the microcontroller must be switched to ICC (In-circuit Communication) mode by an external controller or programming tool.

Depending on the ICP code downloaded in RAM, Flash memory programming can be fully customized (number of bytes to program, program locations or selection serial communication interface for downloading).

When using a STMicroelectronics or third-party programming tool that supports ICP and the specific microcontroller device, the user only needs to implement the ICP hardware interface on the application board (see *Figure 12*). For more details on the pin locations, refer to the device pin description.

ICP needs a minimum of 4 and up to 6 pins to be connected to the programming tool. these pins are:

RESET: device reset

VSS: device power supply ground

ICC-CLK: ICC output serial clock pin

ICC-DATA: ICC input serial data pin

VPP: programming voltage

VDD: application board power supply

Note:

- If the ICC-CLK or ICC-DATA pins are only used as outputs in the application, no signal isolation is necessary. As soon as the Programming Tool is plugged to the board, even if an ICC session is not in progress, the ICC-CLK and ICC-DATA pins are not available for the application. If they are used as inputs by the application, isolation such as a serial resistor has to be implemented in case another device forces the signal. Refer to the Programming Tool documentation for recommended resistor values.

- 2 During the ICC session, the programming tool must control the RESET pin. This can lead to conflicts between the programming tool and the application reset circuit if it drives more than 5mA at high level (push pull output or pull-up resistor<1K). A Schottky diode can be used to isolate the application RESET circuit in this case. When using a classical RC network with R>1K or a reset management IC with open drain output and pull-up resistor>1K, no

- additional components are needed. In all cases the user must ensure that no external reset is generated by the application during the ICC session.

- 3 The use of Pin 7 of the ICC connector depends on the Programming Tool architecture. This pin must be connected when using most ST Programming Tools (it is used to monitor the application power supply)..

Figure 12. Typical ICP interface

## 5.5 IAP (in-application programming)

This mode uses a boot loader program previously stored in Sector 0 by the user (in ICP mode or by plugging the device in a programming tool).

This mode is fully controlled by user software. This allows it to be adapted to the user application, (user-defined strategy for entering programming mode, choice of communications protocol used to fetch the data to be stored, etc.). For example, it is possible to download code from the SPI, SCI, USB or CAN interface and program it in the Flash. IAP mode can be used to program any of the Flash sectors except Sector 0, which is write/erase protected to allow recovery in case errors occur during the programming operation.

## 5.6 Register description

### Flash control/status register (FCSR)

Read/Write

Reset Value: 0000 0000 (00h)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---|---|---|---|---|---|---|---|--|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |

This register is reserved for use by Programming Tool software. It controls the Flash programming and erasing operations.

## 5.7 Flash option bytes

Each device is available for production in user programmable versions (FLASH) as well as in factory coded versions (ROM). FLASH devices are shipped to customers with a default content (FFh), while ROM factory coded parts contain the code supplied by the customer. This implies that FLASh devices have to be configured by the customer using the Option Bytes while the ROM devices are factory-configured.

The option bytes are used to select the hardware configuration of the microcontroller. They have no address in the memory map and can be accessed only in programming mode (for example using a standard ST7 programming tool). The default content of the FLASH is fixed to FFh. To program directly the FLASH devices using ICP, FLASH devices are shipped to customers with the internal RC clock source enabled. In masked ROM devices, the option bytes are fixed in hardware by the ROM code.

## Static option byte 1

|         | 7 | 6   | 5 | 4 | 3 | 2 | 1 | 0     |

|---------|---|-----|---|---|---|---|---|-------|

|         |   | 115 |   |   |   |   |   | FMP_R |

| Default | 1 | 1   | 1 | 1 | 1 | 1 | 1 | 1     |

OPT0= FMP\_R Flash memory read-out protection

This option indicates if the user flash memory is protected against read-out piracy. This protection is based on a read and write protection of the memory in test modes and ICP mode. Erasing the option bytes when the FMP\_R option is selected causes the whole user memory to be erased first.

0: Read-out protection enabled

1: Read-out protection disabled

#### Static option byte 2

|         | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|---|---|---|---|---|---|---|---|

|         |   |   |   |   |   |   |   |   |

| Default | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

## 6 Clocks and low power modes

## 6.1 Clock system

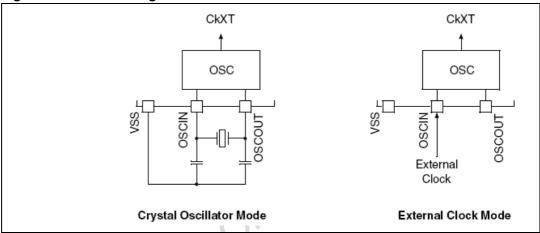

### 6.1.1 General description

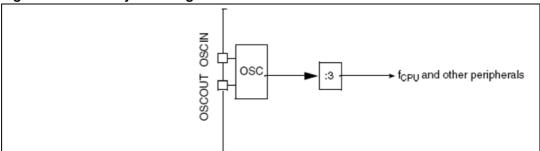

To operate, the device needs a number of clock signals. All clock signals derive from the root 24MHz clock signal CkXT provided at the output of the "OSC" circuit (refer to *Figure 13*). If a 24MHz quartz crystal is applied on pins OSCIN, OSCOUT, the OSC operates in a crystal-controlled oscillator mode. An external clock signal can also be applied on OSCIN pin, putting the OSC in external clock mode operation.

The block diagram in *Figure 13* shows the basic configuration of the clock system.

Figure 13. Main clock generation

## 6.1.2 Crystal oscillator mode

In this mode, the root clock is generated by on-chip oscillator controlled by an external parallel fundamental-mode quartz crystal. General design precautions must be followed to ensure a maximum stability. Foot capacitors  $C_{L1}$  and  $C_{L2}$  must be adapted to match the crystal used. A 100Kohms resistor is internally connected to OSCIN and OSCOUT.

Note:

If a Murata ceramic resonator is to be used, Murata recommends their CERALOCK® CSTCGseries (fundamental type) with built-in CL1 and CL2 capacitors, such as:-CSTCG24M0V51-R0 for 24-MHz external, 8-MHz internal clock operation

CSTCG27M0V51-R0 for 27-MHz external, 9-MHz internal clock operation

No additional external capacitor is therefore needed with either model of this series.

## 6.1.3 External clock mode

In this mode, an external clock is provided on pin OSCIN, while the OSCOUT is left open (*Figure 13*). The signal is internally buffered before feeding the following stages. There is the same emphasis on stability of the external clock as in crystal oscillator mode.

## 6.1.4 Clock signals

The root clock is divided by factors of 3, to obtain CPU clock (f<sub>CPU</sub>).

Figure 14. Clock system diagram

## 6.2 Power saving modes

MCU offers the possibility to decrease power consumption at any time by software operation.

#### 6.2.1 HALT mode

The HALT mode is the MCU lowest power consumption mode. Meanwhile, the HALT mode also stops the oscillator stage completely which is the most critical condition (MCU cannot recover by itself). For this reason, the HALT mode is not compatible with the watchdog protection:

Table 9. Watchdog compatibility

| Watchdog | Executing HALT instruction   |

|----------|------------------------------|

| Enabled  | Generates an immediate reset |

| Disabled | Puts the MCU in HALT mode    |

### 6.2.2 WAIT mode

This mode is a low power consumption mode. The WFI instruction sets the MCU in WAIT mode: The internal clock remains active but all CPU processing is stopped; however, all other peripherals still run.

Note: In WAIT mode DMA (DDCs) accesses are possible.

#### 6.2.3 Exit from HALT and WAIT modes

The MCU can exit HALT mode at reception of an external interrupt: ITA or ITB. The oscillator is then turned on and a stabilizing time is necessary before releasing CPU operation (4096 CPU clock cycles). After this delay, the CPU continues operation according to what caused its release, either by servicing an interrupt or by fetching the reset vector in case of reset.

During WAIT mode, the I bit from the condition code register is cleared, enabling all interrupts. This leads the MCU to exit WAIT mode, the corresponding interrupt vector to be fetched, the interrupt routine to be executed and normal processing to resume.

A reset causes the program counter to fetch the reset vector. Processing starts as with a normal reset.

Figure 15. Wait flow chart

## 6.2.4 Selected peripherals mode

Some peripherals have an "on/off "bit to disconnect the block (or part of) and decrease the MCU power consumption (configuration by default at reset):

Table 10. Peripheral modes

|       |                | 1                |                                          |     |

|-------|----------------|------------------|------------------------------------------|-----|

|       | Bits           | Register         | Comment                                  | Res |

| PORTs | PxDDi          | PxDDR            | cut the output function pad (input mode) | OFF |

| ADC   | ADON           | ADCSR            | cut analog consumption and clock         | OFF |

| PWMi  | OEi            | PWMCRx           | cut the pad consumption                  | OFF |

| DDC   | PE,<br>DDC2BPE | DDCCR,<br>DDCDCR |                                          | OFF |

| WDG   | WGDA           | WDGCR            | cut the output reset                     | OFF |

| I2C   | PE             | I2CCR            |                                          | OF  |

|       |                |                  | cut the output reset                     |     |

I/O ports ST7FLCD1

## 7 I/O ports

I/O ports are used to transfer data through digital inputs and outputs. For specific pins, I/O ports allow the input of analog signals or the Input/Output of alternate signals for on-chip peripherals (DDC, Timer...).

Each pin can be independently programmed as digital input or output. Each pin can be an analog input when an analog switch is connected to the Analog Digital Converter (ADC).

Alternate enable Alternate  $V_{\mathrm{DD}}$ output 0 P-BUFFER (if required) DR latch Alternate enable Data Bus **DDR** Common Analog Rail latch PAD Analog Enable (ADC) Analog Switch (if required) DDR SEL N-BUFFER DR SEL Alternate Enable **VSS** Digital Enable Alternate Input

Figure 16. I/O pin critical circuit

Note: This is the typical I/O pin configuration. Each port is customized with a specific configuration in order to handle certain functions.

36/106

ST7FLCD1 I/O ports

Table 11. I/O pin function

| DDR | Mode   |

|-----|--------|

| 0   | Input  |

| 1   | Output |

# 7.1 Common functional description

Each port pin of the I/O Ports can be individually configured as either input or output, under software control.

Each bit of Data Direction Register (DDR) corresponds to an I/O pin of the associated port. This corresponding bit must be set to configure its associated pin as output and must be cleared to configure its associated pin as input. The Data Direction Registers can be read and written.

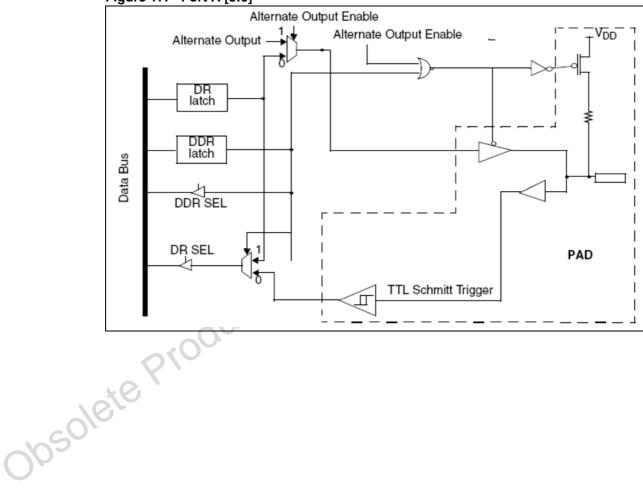

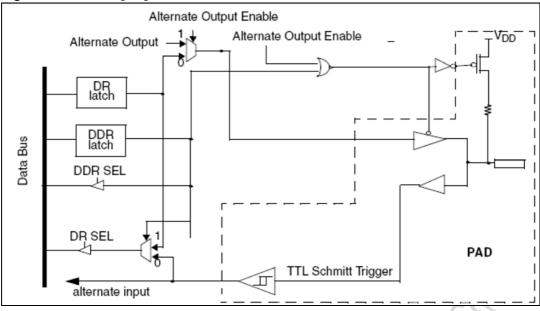

The typical I/O circuit is shown in *Figure 15*. Any write to an I/O port updates the port data register even when configured as input. Any read of an I/O port returns either the data latched in the port data register (pins configured as output) or the value of the I/O pins (pins configured as input).

**Remark**: when there is no I/O pin inside an I/O port, the returned value is logic (pin configured as input).

At reset, all DDR registers are cleared, configuring all I/O ports as inputs. Data Registers (DR) are also cleared at reset.

### Input mode

When DDR=0, the corresponding I/O is configured in Input mode.

In this case, the output buffer is switched off, the state of the I/O is readable through the Data Register address, coming directly from the TTL Schmitt Trigger output and not from the Data Register output.

### **Output mode**

When DDR=1, the corresponding I/O is configured in Output mode.

In this case, the output buffer is activated according to the Data Register content.

A read operation is directly performed from the Data Register output.

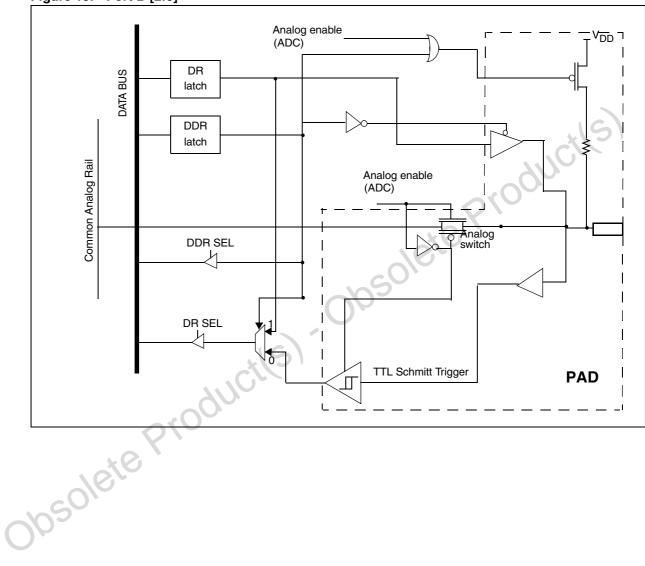

### **Analog input**

Each I/O can be used as analog input by adding an analog switch driven by the Analog Digital Converter. The I/O must be configured in Input before using it as analog input.

When the analog channel is selected by the ADC the analog value is directly driven to the ADC through an analog switch.

### Alternate mode

A signal coming from an on-chip peripheral is an output on the I/O, the latter then being automatically configured in output mode.

I/O ports ST7FLCD1

The signal coming from the peripheral enables the alternate signal to be output. A signal coming from an I/O can be input in an on-chip peripheral.

An alternate Input must first be configured in Input mode (DDR=0). Alternate and I/O Input configurations are identical without pull-up. The signal to be input in the peripheral is taken after the TTL Schmitt trigger when available.

The I/O state is readable as in Input mode by addressing the corresponding I/O Data Register.

## 7.2 Port A

Each Port A bit can be defined as an Input line or as a Push-Pull. It can be also be used to output the PWM outputs.

Table 12. Port A descriptions

| Down A | 1/0                  | )         | Alternate function     |                              |  |  |  |

|--------|----------------------|-----------|------------------------|------------------------------|--|--|--|

| Port A | Input <sup>(1)</sup> | Output    | Signal                 | Condition                    |  |  |  |

| PA0    | With weak pull-up    | Push-pull | PWM0                   | OE0=1 (PWM)                  |  |  |  |

| PA1    | With weak pull-up    | Push-pull | PWM1                   | OE1=1 (PWM)                  |  |  |  |

| PA2    | With weak pull-up    | Push-pull | PWM2                   | OE2=1 (PWM)                  |  |  |  |

| PA3    | With weak pull-up    | Push-pull | PWM3                   | OE3=1 (PWM)                  |  |  |  |

| PA4    | With weak pull-up    | Push-pull | PWM4                   | OE4=1 (PWM)                  |  |  |  |

| PA5    | With weak pull-up    | Push-pull | PWM5                   | OE5=1 (PWM)                  |  |  |  |

|        | With weak pull-up    | 00        | BUZOUT                 | BUZEN = 1 (timer A) $^{(2)}$ |  |  |  |

| PA6    | With weak pull-up    | Push-pull | External interrupt ITA | see external interrupt       |  |  |  |

| PA7    | With weak pull-up    | Push-pull | External interrupt ITB | register description         |  |  |  |

<sup>1.</sup> Reset state

Outputs PA4 and PA5 may also be configured as high current (8 mA) push-pull outputs by means of the MISCR register.

## Miscellaneous register (MISCR)

Read/Write

Reset value:00h

| 7 | 6 | 5 | 4 | 3 | 2      | 1      | 0 |

|---|---|---|---|---|--------|--------|---|

| 0 | 0 | 0 | 0 | 0 | PA5OVD | PA4OVD | 0 |

**Bits** [7:3] = **Reserved**. Forced by hardware to 0.

Bit 2 = PA5OVD Port A Bit 5 Overdrive

<sup>2.</sup> If both PWM5 and BUZOUT are enabled, BUZOUT has priority over PWM5.

ST7FLCD1 I/O ports

This bit is set and cleared by software. It is used only if Port A Bit 5 is set as an output (PADDR, PWM5 or BUZOUT). It has no effect if set as an input.

0: 2 mA Push-pull Output

1: 8 mA Push-pull Output

### Bit 1 = PA4OVD Port A Bit 4 Overdrive

This bit is set and cleared by software. It is used only if Port A Bit 4 is set as an output (PADDR or PWM4). It has no effect if set as an input.

0: 2 mA Push-pull Output

1: 8 mA Push-pull Output

**Bit 0 = Reserved.** Must be cleared by software.

Figure 17. Port A [5:0]

I/O ports ST7FLCD1

Figure 18. Port A [7:6]

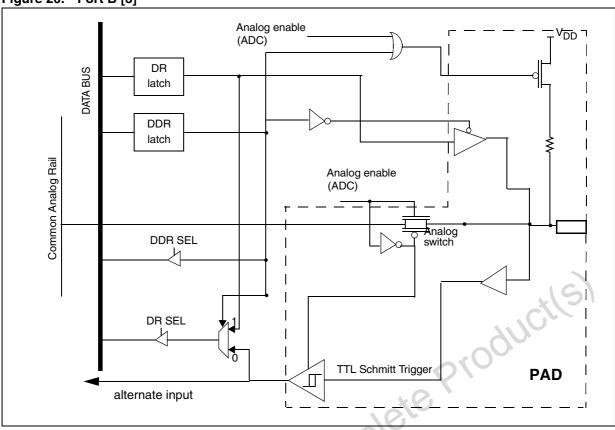

# **7.3** Port B

Each port B bit can be used as the Analog source to the Analog Digital Converter.

Only one I/O line at a time must be configured as an analog input. Pins levels are all limited to 5V.

All unused I/O lines should be tied to an appropriate logic level (either  $V_{DD}$  or  $V_{SS}$ ).

Since ADC and microprocessor are on the same chip and if high precision is required, the user should not switch heavily loaded signals during conversion. Such switching will affect the supply voltages used as analog references. The conversion accuracy depends on the quality of power supplies ( $V_{DD}$  and  $V_{SS}$ ). The user must take special care to ensure that a well regulated reference voltage is present on  $V_{DD}$  and  $V_{SS}$  pins (power supply variations must be less than 3.3V/ms). This implies, in particular, that a suitable decoupling capacitor is used at  $V_{DD}$  pin.

Table 13. Port B description

| PORT B | 1/0                                  |           | Alternate Function         |                                   |  |  |  |

|--------|--------------------------------------|-----------|----------------------------|-----------------------------------|--|--|--|

|        | Input*                               | Output    | Signal                     | Condition                         |  |  |  |

| PB0    | With weak pull-up when digital input | Push-pull | Analog input<br>(ADC):AIN0 | ADON = 1 & CH[1:0]=00<br>(ADCCSR) |  |  |  |

| PB1    | With weak pull-up when digital input | Push-pull | Analog input (ADC)<br>AIN1 | ADON = 1 & CH[1:0]=01<br>(ADCCSR) |  |  |  |

| PB2    | With weak pull-up when digital input | Push-pull | Analog input (ADC)<br>AIN2 | ADON = 1 & CH[1:0]=10<br>(ADCCSR) |  |  |  |

ST7FLCD1 I/O ports

Table 13. Port B description

| PORT B | 1/0                                  |           | Alternate Function              |                                                                                     |  |  |

|--------|--------------------------------------|-----------|---------------------------------|-------------------------------------------------------------------------------------|--|--|

|        | Input*                               | Output    | Signal                          | Condition                                                                           |  |  |

| PB3    | With weak pull-up when digital input | Push-pull | Analog input (ADC)<br>AIN3/ IFR | ADON = 1 & CH[1:0]=11<br>(ADCCSR) for analog input<br>in this case, IFR is disabled |  |  |

<sup>\*</sup>Reset State

Figure 19. Port B [2:0]

I/O ports ST7FLCD1

Figure 20. Port B [3]

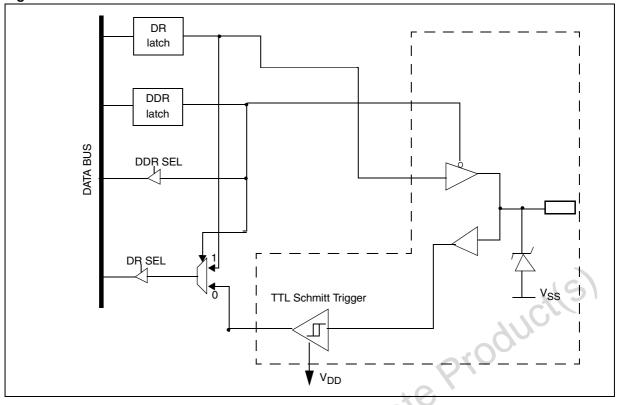

# **7.4** Port C

The available port pins of port C may be used as general purpose I/O.

Table 14. Port C description

| PORT C | 7/1/            | 0          | Alternate | Function  |

|--------|-----------------|------------|-----------|-----------|

| PUNIC  | Input*          | Output     | Signal    | Condition |

| PC0    | Without pull-up | Open-drain |           |           |

| PC1    | Without pull-up | Open-drain |           |           |

<sup>\*</sup>Reset state

Note:

These 2 pins are reserved for ICC use during ICC communication. If ICC is not used at all, they can be used as general purpose I/Os.

42/106

ST7FLCD1 I/O ports

Figure 21. Port C

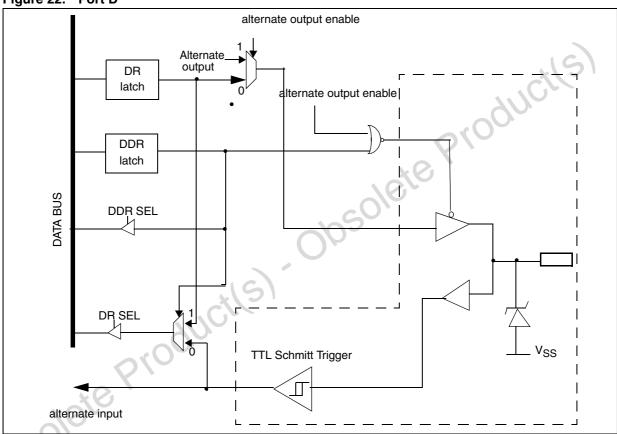

# **7.5** Port D

The alternate functions are:

the I/O pins of the on-chip I<sup>2</sup>C SCLI & SDAI for PD[1:0],

the I/O pins of the on-chip DDCA SCLD & SDAD for PD[3:2],

the I/O pins of the on-chip DDCB SCLD & SDAD for PD[5:4]

input and output on PD[7:6]

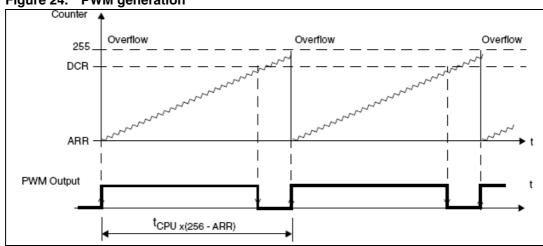

Table 15. Port D description