# 16M-BIT Low Voltage, Serial MASK ROM with 50MHz SPI Bus Interface

### **FEATURES**

- 16Mbit of Mask ROM

- 3.0 to 3.6V Single Supply Voltage

- SPI Bus Compatible Serial Interface

- 50MHz Clock Rate (maximum)

### **DESCRIPTION**

The MX23L1654 is a 16Mbit (2M x 8) Serial Mask ROM accessed by a high speed SPI-compatible bus.

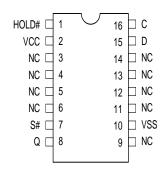

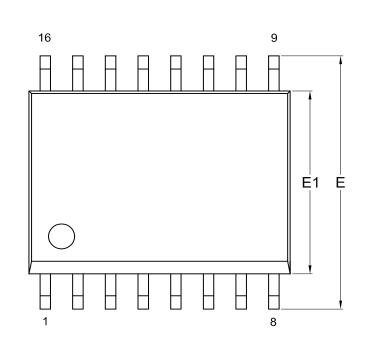

## **PIN CONFIGURATIONS**

## 16-PIN SOP (300 mil)

# PIN DESCRIPTION

| SYMBOL | DESCRIPTION        |

|--------|--------------------|

| С      | Serial Clock       |

| D      | Serial Data Input  |

| Q      | Serial Data Output |

| S#     | Chip Select        |

| HOLD#  | Hold               |

| VCC    | Supply Voltage     |

| VSS    | Ground             |

### Note:

- 1. NC=No Connection

- 2. See page 16 (onwards) for package dimensions, and how to identify pin-1.

## ORDER INFORMATION

| Part No.        | Speed | Package | Remark                     |

|-----------------|-------|---------|----------------------------|

| MX23L1654MC-20  | 20ns  | 16-SOP  |                            |

| MX23L1654MC-20G | 20ns  | 16-SOP  | Pb-free                    |

| MX23L1654MI-20G | 20ns  | 16-SOP  | Pb-free (Industrial Grade) |

#### Note:

<sup>\*</sup> Industrial grade operating temperature: -25 ~ 85 °C Commercial grade operating temperature: 0 ~ 70 °C

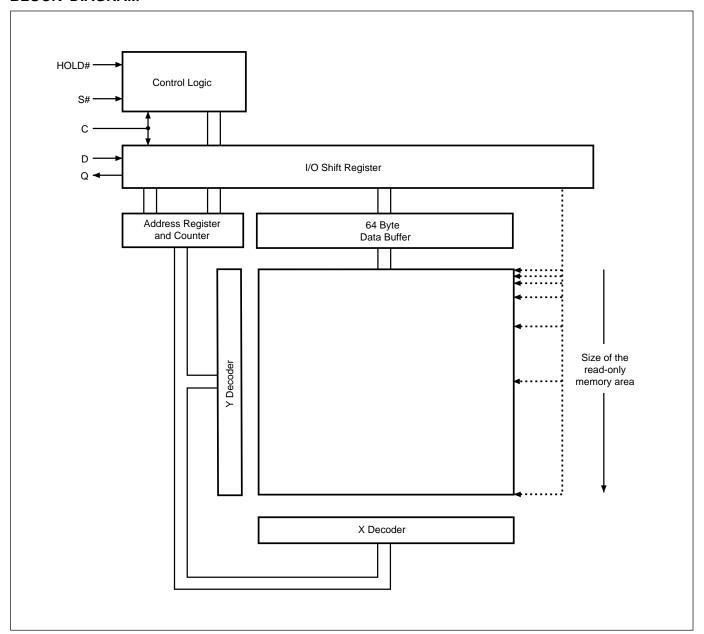

## **MEMORY ORGANIZATION**

The memory is organized as:

- 2M bytes (8 bits each)

## **BLOCK DIAGRAM**

### SIGNAL DESCRIPTION

**Serial Data Output (Q).** This output signal is used to transfer data serially out of the device. Data is shifted out on the falling edge of Serial Clock (C).

**Serial Data Input (D).** This input signal is used to transfer data serially into the device. It receives instructions, addresses, and the data to be programmed. Values are latched on the rising edge of Serial Clock (C).

**Serial Clock (C).** This input signal provides the timing of the serial interface. Instructions, addresses, or data present at Serial Data Input (D) are latched on the rising edge of Serial Clock (C). Data on Serial Data Output (Q) changes after the falling edge of Serial Clock (C).

Chip Select (S#). When this input signal is High, the

device is deselected. Driving Chip Select (S#) Low enables the device, placing it in the active power mode.

After Power-up, a falling edge on Chip Select (S#) is required prior to the start of any instruction.

**Hold (HOLD#).** The Hold (HOLD#) signal is used to pause any serial communications with the device without deselecting the device.

During the Hold condition, the Serial Data Output (Q) is high impedance, and Serial Data Input (D) and Serial Clock (C) are Don't Care.

To start the Hold condition, the device must be selected, with Chip Select (S#) driven Low.

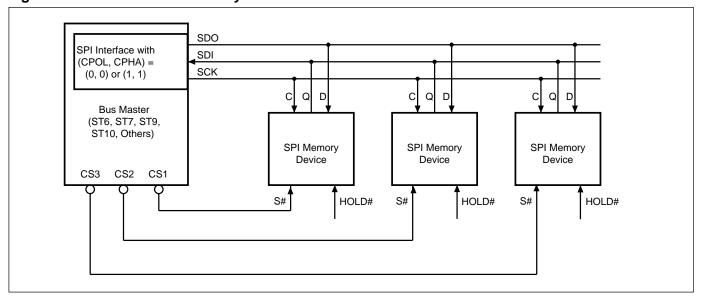

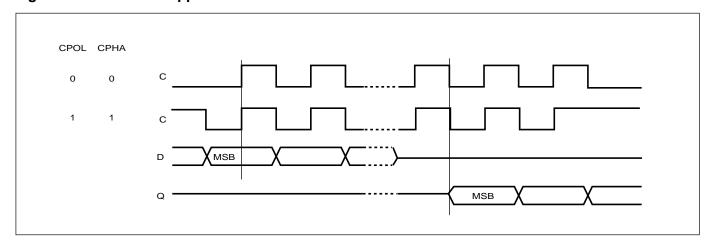

## **SPI MODES**

These devices can be driven by a microcontroller with its SPI peripheral running in either of the two following modes:

- CPOL=0, CPHA=0

- CPOL=1, CPHA=1

For these two modes, input data is latched in on the rising edge of Serial Clock (C), and output data is available from

the falling edge of Serial Clock (C).

The difference between the two modes, as shown in Figure 2, is the clock polarity when the bus master is in Stand-by mode and not transferring data:

- C remains at 0 for (CPOL=0, CPHA=0)

- C remains at 1 for (CPOL=1, CPHA=1)

Figure 1. Bus Master and Memory Devices on the SPI Bus

Note: 1. Hold (HOLD#) signals should be driven, High or Low as appropriate.

Figure 2. SPI Modes Supported

## **OPERATING FEATURES**

## **Active Power, Stand-by Power**

When Chip Select (S#) is Low, the device is enabled, and in the Active Power mode. When Chip Select (S#) is High, the device is disabled, but could remain in the Active Power mode until all internal cycles have completed. The device then goes in to the Stand-by Power mode. The device consumption drops to ICC1 .

## **Protection Modes**

The environments where non-volatile memory devices are used can be very noisy. No SPI device can operate correctly in the presence of excessive noise. To help combat this, the MX23L1654 boasts the following data protection mechanisms:

- Power-On Reset and an internal timer (tPUW) can provide protection against inadvertant changes while the power supply is outside the operating specification.

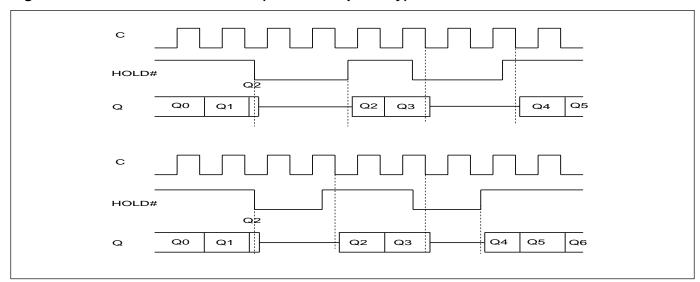

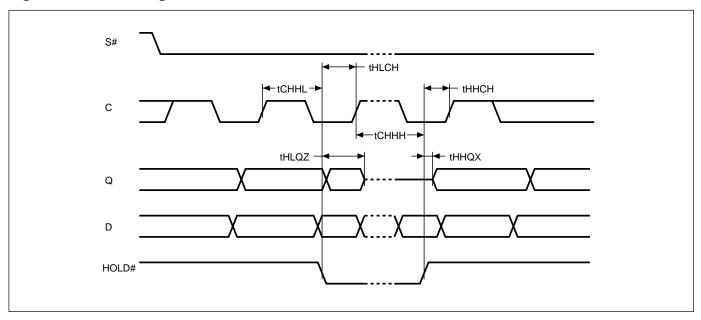

## **Hold Condition**

The Hold (HOLD#) signal is used to pause any serial communications with the device without resetting the clocking sequence.

To enter the Hold condition, the device must be selected, with Chip Select (S#) Low.

The Hold condition starts on the falling edge of the Hold (HOLD) signal, provided that this coincides with Serial Clock (C) being Low (as shown in Figure 3).

The Hold condition ends on the rising edge of the Hold (HOLD#) signal, provided that this coincides with Serial Clock (C) being Low.

If the falling edge does not coincide with Serial Clock (C) being Low, the Hold condition starts after Serial Clock (C) next goes Low. Similarly, if the rising edge does not coincide with Serial Clock (C) being Low, the Hold condition ends after Serial Clock (C) next goes Low. (This is shown in Figure 2).

During the Hold condition, the Serial Data Output (Q) is high impedance, and Serial Data Input (D) and Serial Clock (C) are Don't Care.

Normally, the device is kept selected, with Chip Select (S#) driven Low, for the whole duration of the Hold condition. This is to ensure that the state of the internal logic remains unchanged from the moment of entering the Hold condition.

If Chip Select (S#) goes High while the device is in the Hold condition, this has the effect of resetting the internal logic of the device. To restart communication with the device, it is necessary to drive Hold (HOLD#) High, and then to drive Chip Select (S#) Low. This prevents the device from going back to the Hold condition.

Figure 3. Hold Condition Activation (for data output only)

## **INSTRUCTIONS**

All instructions, addresses and data are shifted in and out of the device, most significant bit first.

Serial Data Input (D) is sampled on the first rising edge of Serial Clock (C) after Chip Select (S#) is driven Low. Then, the one-byte instruction code must be shifted in to the device, most significant bit first, on Serial Data Input (D), each bit being latched on the rising edges of Serial Clock (C).

The instruction set is listed in Table 1.

Every instruction sequence starts with a one-byte instruction code. Depending on the instruction, this might be followed by address bytes, or by data bytes, or by both or none.

In the case of a Read Data Bytes (READ), Read Data Bytes at Higher Speed (Fast\_Read), the shifted-in instruction sequence is followed by a data-out sequence. Chip Select (S#) can be driven High after any bit of the data-out sequence is being shifted out.

**Table 1. Instruction Set**

| Instruction | Description                     | One-byte Instruction | Address<br>Bytes | Dummy<br>Bytes | Data<br>Bytes |        |

|-------------|---------------------------------|----------------------|------------------|----------------|---------------|--------|

| READ        | Read Data Bytes                 | 0000 0011            | 03h              | 3              | 0             | 1 to ∞ |

| FAST_READ   | Read Data Bytes at Higher Speed | 0000 1011            | 0Bh              | 3              | 1             | 1 to ∞ |

| RDID        | Read Identification             | 1001 1111            | 9Fh              | 0              | 0             | 1 to 3 |

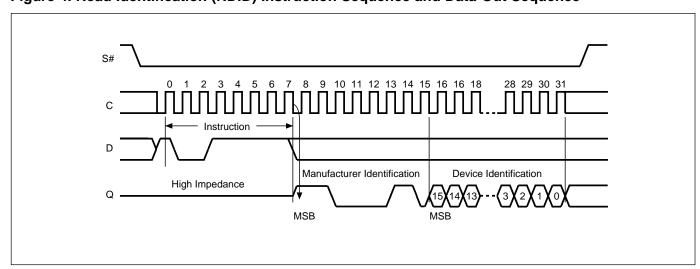

## Read Identification (RDID)

The Read Identification (RDID) instruction allows the 8-bit manufacturer identification to be read, followed by two bytes of device identification. The manufacturer identification is assigned by JEDEC, and has the value C2h for Macronix. The device identification is assigned by the device manufacturer, and indicates the memory type in the first byte (05h), and the memory capacity of the device in the second byte (15h).

The Read Identification (RDID) instruction should not be issued while the device is in Deep Power-down mode.

The device is first selected by driving Chip Select (S#)

Low. Then, the 8-bit instruction code for the instruction is shifted in. This is followed by the 24-bit device identification, stored in the memory, being shifted out on Serial Data Output (Q), each bit being shifted out during the falling edge of Serial Clock (C).

The instruction sequence is shown in Figure 4.

The Read Identification (RDID) instruction is terminated by driving Chip Select (S#) High at any time during data output. When Chip Select (S#) is driven High, the device is put in the Standby Power mode. Once in the Standby Power mode, the device waits to be selected, so that it can receive, decode and execute instructions.

Table 2. Read Identification (RDID) Data-Out Sequence

| Manufacturer Identification  | Device Ide  | ntification     |

|------------------------------|-------------|-----------------|

| Walluracturer Identification | Memory Type | Memory Capacity |

| C2h                          | 05h         | 15h             |

Figure 4. Read Identification (RDID) Instruction Sequence and Data-Out Sequence

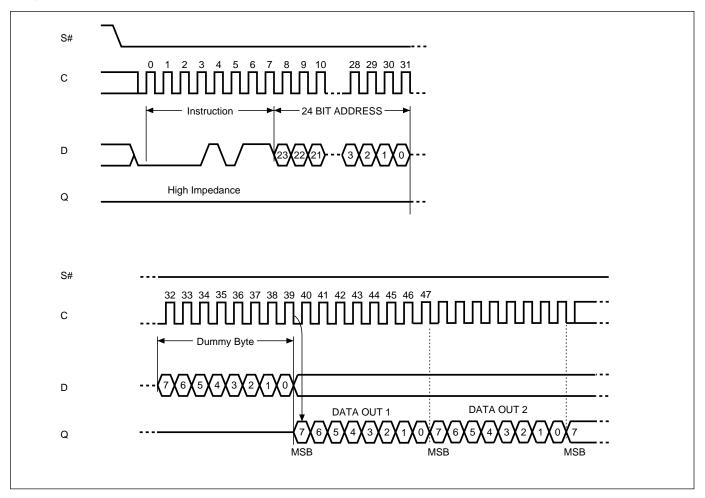

Figure 5. Read Data Bytes (READ) Instruction Sequence and Data-Out Sequence

Note: 1. Address bits A23, A22, A21 are Don't Care.

## Read Data Bytes (READ)

The device is first selected by driving Chip Select (S#) Low. The instruction code for the Read Data Bytes (READ) instruction is followed by a 3-byte address (A23-A0), each bit being latched-in during the rising edge of Serial Clock (C). Then the memory contents, at that address, is shifted out on Serial Data Output (Q), each bit being shifted out, at a maximum frequency fR, during the falling edge of Serial Clock (C).

The instruction sequence is shown in Figure 5. The first byte addressed can be at any location. The address is automatically incremented to the next higher address after each byte of data is shifted out. The whole memory can, therefore, be read with a single Read Data Bytes (READ) instruction. When the highest address is reached, the address counter rolls over to 000000h, allowing the read sequence to be continued indefinitely.

The Read Data Bytes (READ) instruction is terminated by driving Chip Select (S#) High. Chip Select (S#) can be driven High at any time during data output.

P/N: PM1247 8 REV. 1.4, NOV. 07, 2006

Figure 6. Read Data Bytes at Higher Speed (FAST\_READ) Instruction Sequence and Data-Out Sequence

### Read Data Bytes at Higher Speed (FAST\_READ)

The device is first selected by driving Chip Select (S#) Low. The instruction code for the Read Data Bytes at Higher Speed (FAST\_READ) instruction is followed by a 3-byte address (A23-A0) and a dummy byte, each bit being latched-in during the rising edge of Serial Clock (C). Then the memory contents, at that address, is shifted out on Serial Data Output (Q), each bit being shifted out, at a maximum frequency fC, during the falling edge of Serial Clock (C).

The instruction sequence is shown in Figure 6. The first

byte addressed can be at any location. The address is automatically incremented to the next higher address after each byte of data is shifted out. The whole memory can, therefore, be read with a single Read Data Bytes at Higher Speed (FAST\_READ) instruction. When the highest address is reached, the address counter rolls over to 000000h, allowing the read sequence to be continued indefinitely.

The Read Data Bytes at Higher Speed (FAST\_READ) instruction is terminated by driving Chip Select (S#) High. Chip Select (S#) can be driven High at any time during data output.

P/N: PM1247 9 REV. 1.4, NOV. 07, 2006

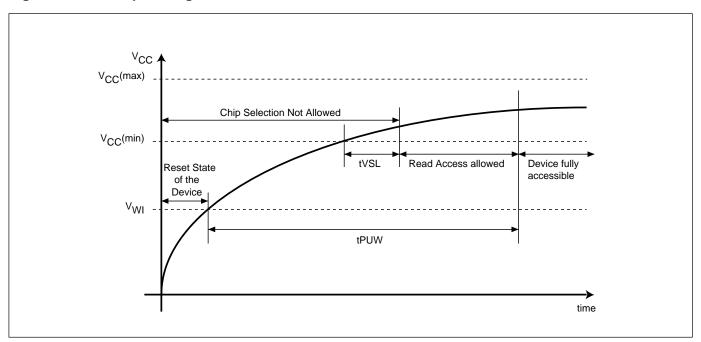

## POWER-UP AND POWER-DOWN

At Power-up and Power-down, the device must not be selected (that is Chip Select (S#) must follow the voltage applied on VCC) until VCC reaches the correct value:

- VCC(min) at Power-up, and then for a further delay of tVSL

- VSS at Power-down

Usually a simple pull-up resistor on Chip Select (S#) can be used to insure safe and proper Power-up and Powerdown.

To avoid data corruption and inadvertent write operations during power up, a Power On Reset (POR) circuit is included. The logic inside the device is held reset while VCC is less than the POR threshold value, VWI -- all operations are disabled, and the device does not respond to any instruction.

These values are specified in Table 3.

If the delay, tVSL, has elapsed, after VCC has risen above VCC (min), the device can be selected for READ instructions even if the tPUW delay is not yet fully elapsed.

At Power-up, the device is in the following state:

- The device is in the Standby mode.

Normal precautions must be taken for supply rail decoupling, to stablise the VCC feed. Each device in a system should have the VCC rail decoupled by a suitable capacitor close to the package pins.

(Generally, this capacitor is of the order of 0.1uF).

At Power-down, when VCC drops from the operating voltage, to below the POR threshold value, VWI, all operations are disabled and the device does not respond to any instruction.

Figure 7. Power-up Timing

## **Table 3. Power-Up Timing**

| Symbol             | Parameter                       | Min. | Max. | Unit |

|--------------------|---------------------------------|------|------|------|

| t <sub>VSL</sub> 1 | V <sub>CC</sub> (min) to S# low | 30   |      | us   |

Note: 1. These parameters are characterized only.

## **MAXIMUM RATING**

Stressing the device above the rating listed in the "Absolute Maximum Ratings" table may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the Operating sections of this specification is not implied. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability.

**Table 4. Absolute Maximum Ratings**

| Symbol            | Parameter                                                       | Min.   | Max.             | Unit |

|-------------------|-----------------------------------------------------------------|--------|------------------|------|

| T <sub>STG</sub>  | Storage Temperature                                             | - 65   | 150              | °C   |

| T <sub>LEAD</sub> | Lead Temperature during Soldering <sup>1</sup>                  |        | 260 <sup>2</sup> | °C   |

| V <sub>IO</sub>   | Input and Output Voltage (with respect to Ground)               | - 0.6  | 4.0              | V    |

| Vcc               | Supply Voltage                                                  | - 0.6  | 4.0              | V    |

| V <sub>ESD</sub>  | Electrostatic Discharge Voltage (Human Body model) <sup>3</sup> | - 2000 | 2000             | V    |

Note: 1. Compliant with the ECOPACK® 7191395 specification for lead-free soldering processes

- 2. Not exceeding 250°C for more than 30 seconds, and peaking at 260°C

- 3. JEDEC Std JESD22-A114A (C1=100 pF, R1=1500  $\Omega$ , R2=500  $\Omega$ )

P/N: PM1247 REV. 1.4, NOV. 07, 2006

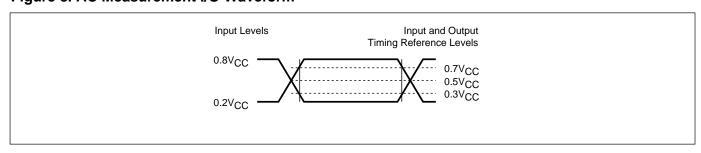

## DC AND AC PARAMETERS

This section summarizes the operating and mea-surement conditions, and the DC and AC characteristics of the device. The parameters in the DC and AC Characteristic

tables that follow are derived from tests performed under the Measurement Conditions summarized in the relevant tables. Designers should check that the operating conditions in their circuit match the measurement conditions when relying on the quoted parameters.

**Table 5. Operating Conditions**

| Symbol         | Parameter                     | Min. | Max. | Unit |

|----------------|-------------------------------|------|------|------|

| Vcc            | Supply Voltage                | 3.0  | 3.6  | V    |

| T <sub>A</sub> | Ambient Operating Temperature | -25  | 85   | °C   |

**Table 6. AC Measurement Conditions**

| Symbol         | Parameter                        | Min.                 | Max.                 | Unit |

|----------------|----------------------------------|----------------------|----------------------|------|

| C <sub>L</sub> | Load Capacitance                 | 3                    | pF                   |      |

|                | Input Rise and Fall Times        |                      | 5                    | ns   |

|                | Input Pulse Voltages             | 0.2V <sub>CC</sub> t | o 0.8V <sub>CC</sub> | V    |

|                | Input Timing Reference Voltages  | 0.3V <sub>CC</sub> t | V                    |      |

|                | Output Timing Reference Voltages | V <sub>C</sub>       | V                    |      |

Note: 1. Output Hi-Z is defined as the point where data out is no longer driven.

Figure 8. AC Measurement I/O Waveform

**Table 7. Capacitance**

| Symbol           | Parameter                      | Min.           | Max. | Unit |    |

|------------------|--------------------------------|----------------|------|------|----|

| C <sub>OUT</sub> | Output Capacitance (Q)         | $V_{OUT} = 0V$ |      | 8    | pF |

| C <sub>IN</sub>  | Input Capacitance (other pins) | $V_{IN} = 0V$  |      | 6    | pF |

Note: Sampled only, not 100% tested, at T<sub>A</sub>=25°C and a frequency of 20 MHz.

## **Table 8. DC Characteristics**

| Symbol           | Parameter                                                               | Parameter Test Condition (in addition to those in Table 8) Min. |                       |                      | Unit |

|------------------|-------------------------------------------------------------------------|-----------------------------------------------------------------|-----------------------|----------------------|------|

| ILI              | Input Leakage Current                                                   |                                                                 |                       | ± 2                  | uA   |

| I <sub>LO</sub>  | Output Leakage Current                                                  |                                                                 |                       | ± 2                  | uA   |

| I <sub>CC1</sub> | Standby Current                                                         | $S# = V_{CC}$ , $V_{IN} = V_{SS}$ or $V_{CC}$                   |                       | 50                   | uA   |

|                  | $C = 0.1V_{CC} / 0.9.V_{CC} \text{ at 50MHz},$ Operating Current (READ) |                                                                 |                       | 8                    | mA   |

| I <sub>CC2</sub> | Operating Current (NEAD)                                                | $C = 0.1V_{CC} / 0.9.V_{CC}$ at 20MHz,<br>Q = open              |                       | 4                    | mA   |

| V <sub>IL</sub>  | Input Low Voltage                                                       |                                                                 | - 0.5                 | 0.3V <sub>CC</sub>   | V    |

| V <sub>IH</sub>  | Input High Voltage                                                      |                                                                 | 0.7V <sub>CC</sub>    | V <sub>CC</sub> +0.4 | V    |

| $V_{OL}$         | Output Low Voltage                                                      | I <sub>OL</sub> = 1.6mA                                         |                       | 0.4                  | V    |

| V <sub>OH</sub>  | Output High Voltage                                                     | I <sub>OH</sub> = -100 uA                                       | V <sub>CC</sub> - 0.2 |                      | V    |

## **Table 9. AC Characteristics**

| Test conditions specified in Table 4 and Table 5 |                  |                                                                 |      |      |      |      |  |  |  |  |

|--------------------------------------------------|------------------|-----------------------------------------------------------------|------|------|------|------|--|--|--|--|

| Symbol                                           | Alt.             | Parameter                                                       | Min. | Тур. | Max. | Unit |  |  |  |  |

| f <sub>C</sub>                                   | f <sub>C</sub>   | Clock Frequency for the following instructions: FAST_READ, RDID | D.C. |      | 50   | MHz  |  |  |  |  |

| f <sub>R</sub>                                   |                  | Clock Frequency for READ instructions                           | D.C. |      | 20   | MHz  |  |  |  |  |

| t <sub>CH</sub> 1                                | tCLH             | Clock High Time                                                 | 9    |      |      | ns   |  |  |  |  |

| t <sub>CL</sub> 1                                | t <sub>CLL</sub> | Clock Low Time                                                  | 9    |      |      | ns   |  |  |  |  |

| t <sub>CLCH</sub> <sup>2</sup>                   |                  | Clock Rise Time <sup>3</sup> (peak to peak)                     | 0.1  |      |      | V/ns |  |  |  |  |

| t <sub>CHCL</sub> <sup>2</sup>                   |                  | Clock Fall Time <sup>3</sup> (peak to peak)                     | 0.1  |      |      | V/ns |  |  |  |  |

| t <sub>SLCH</sub>                                | t <sub>CSS</sub> | S# Active Setup Time (relative to C)                            | 5    |      |      | ns   |  |  |  |  |

| tCHSL                                            |                  | S# Not Active Hold Time (relative to C)                         | 5    |      |      | ns   |  |  |  |  |

| tDVCH                                            | t <sub>DSU</sub> | Data In Setup Time                                              | 2    |      |      | ns   |  |  |  |  |

| tCHDX                                            | t <sub>DH</sub>  | Data In Hold Time                                               | 5    |      |      | ns   |  |  |  |  |

| tchsh                                            |                  | S# Active Hold Time (relative to C)                             | 5    |      |      | ns   |  |  |  |  |

| tsнсн                                            |                  | S# Not Active Setup Time (relative to C)                        | 5    |      |      | ns   |  |  |  |  |

| t <sub>SHSL</sub>                                | tcsh             | S# Deselect Time                                                | 100  |      |      | ns   |  |  |  |  |

| t <sub>SHQZ</sub> <sup>2</sup>                   | t <sub>DIS</sub> | Output Disable Time                                             |      |      | 8    | ns   |  |  |  |  |

| t <sub>CLQV</sub>                                | t <sub>V</sub>   | Clock Low to Output Valid                                       | 1    |      | 8    | ns   |  |  |  |  |

| t <sub>CLQX</sub>                                | t <sub>HO</sub>  | Output Hold Time                                                | 0    |      |      | ns   |  |  |  |  |

| tHLCH                                            |                  | HOLD# Setup Time (relative to C)                                | 5    |      |      | ns   |  |  |  |  |

| tсннн                                            |                  | HOLD# Hold Time (relative to C)                                 | 5    |      |      | ns   |  |  |  |  |

| tHHCH                                            |                  | HOLD Setup Time (relative to C)                                 | 5    |      |      | ns   |  |  |  |  |

| tCHHL                                            |                  | HOLD Hold Time (relative to C)                                  | 5    |      |      | ns   |  |  |  |  |

| t <sub>HHQX</sub> <sup>2</sup>                   | t <sub>LZ</sub>  | HOLD to Output Low-Z                                            |      |      | 8    | ns   |  |  |  |  |

| t <sub>HLQZ</sub> <sup>2</sup>                   | t <sub>HZ</sub>  | HOLD# to Output High-Z                                          |      |      | 8    | ns   |  |  |  |  |

Note: 1.  $t_{CH}$  +  $t_{CL}$  must be greater than or equal to 1/  $f_{C}$  2. Value guaranteed by characterization, not 100% tested in production. 3. Expressed as a slew-rate.

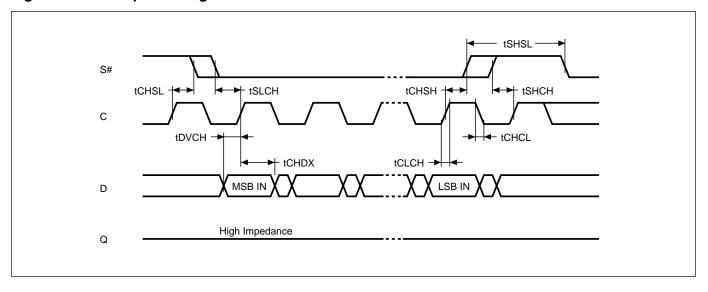

## Figure 9. Serial Input Timing

# Figure 10. Hold Timing

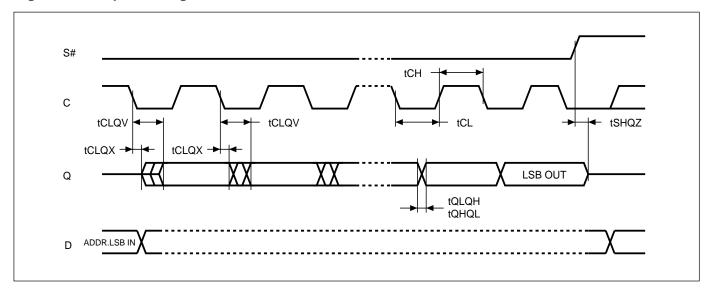

# Figure 11. Output Timing

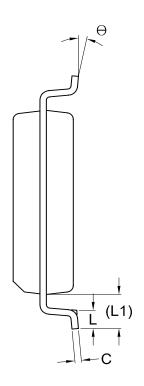

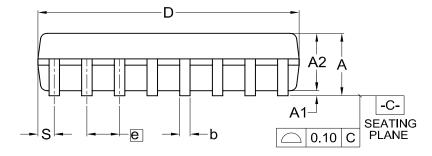

## **PACKAGE INFORMATION**

Title: Package Outline for SOP 16L (300MIL)

Dimensions (inch dimensions are derived from the original mm dimensions)

| SY<br>UNIT | MBOL | Α     | A1    | A2    | b     | С     | D     | E     | E1    | е     | L     | L1    | s     | θ |

|------------|------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---|

|            | Min. |       | 0.10  | 2.25  | 0.36  | 0.20  | 10.10 | 10.10 | 7.42  |       | 0.40  | 1.31  | 0.51  | 0 |

| mm         | Nom. | _     | 0.20  | 2.31  | 0.41  | 0.25  | 10.30 | 10.30 | 7.52  | 1.27  | 0.84  | 1.44  | 0.64  | 5 |

|            | Max. | 2.65  | 0.30  | 2.40  | 0.51  | 0.30  | 10.50 | 10.50 | 7.60  |       | 1.27  | 1.57  | 0.77  | 8 |

|            | Min. |       | 0.004 | 0.089 | 0.014 | 0.008 | 0.397 | 0.397 | 0.292 |       | 0.016 | 0.052 | 0.020 | 0 |

| Inch       | Nom. |       | 0.008 | 0.091 | 0.016 | 0.010 | 0.405 | 0.405 | 0.296 | 0.050 | 0.033 | 0.057 | 0.025 | 5 |

|            | Max. | 0.104 | 0.012 | 0.094 | 0.020 | 0.012 | 0.413 | 0.413 | 0.299 |       | 0.050 | 0.062 | 0.030 | 8 |

| DWG.NO.   | REVISION | REFERENCE |      |  | ISSUE DATE |

|-----------|----------|-----------|------|--|------------|

|           |          | JEDEC     | EIAJ |  | ISSUE DATE |

| 6110-1402 | 8        | MS-013    |      |  | 03-07-'06  |

## **REVISION HISTORY**

| Revision | Description                                                           | Page  | Date        |

|----------|-----------------------------------------------------------------------|-------|-------------|

| 1.1      | 1. Changed part name from MX23L1654A to MX23L1654                     | All   | SEP/23/2005 |

|          | 2. Modified Figure 4. Read Identification (RDID) Instruction Sequence | P7    |             |

|          | and Data-out Sequence                                                 |       |             |

| 1.2      | 1. Modified Table 9. AC Characteristics                               | P14   | NOV/03/2005 |

| 1.3      | 1. Modified supply voltage from 2.7~3.6V to 3.0~3.6V                  | P1,12 | DEC/05/2005 |

| 1.4      | 1. Added statement                                                    | P19   | NOV/07/2006 |

P/N: PM1247 REV. 1.4, NOV. 07, 2006

Macronix's products are not designed, manufactured, or intended for use for any high risk applications in which the failure of a single component could cause death, personal injury, severe physical damage, or other substantial harm to persons or property, such as life-support systems, high temperature automotive, medical, aircraft and military application. Macronix and its suppliers will not be liable to you and/or any third party for any claims, injuries or damages that may be incurred due to use of Macronix's products in the prohibited applications.

# MACRONIX INTERNATIONAL Co., LTD.

#### **Headquarters:**

TEL:+886-3-578-6688 FAX:+886-3-563-2888

### **Europe Office:**

TEL:+32-2-456-8020 FAX:+32-2-456-8021

### Hong Kong Office:

TEL:+86-512-6258-0888 FAX:+86-512-6258-6799

#### Japan Office:

Kawasaki Office: TEL:+81-44-246-9100 FAX:+81-44-246-9105

Technical Support Center:

TEL:+81-44-246-9875 FAX:+81-44-246-9951

## Singapore Office:

TEL:+65-6346-5505 FAX:+65-6348-8096

## Taipei Office:

TEL:+886-2-2509-3300 FAX:+886-2-2509-2200

#### MACRONIX AMERICA. INC.

TEL:+1-408-262-8887 FAX:+1-408-262-8810

## http://www.macronix.com