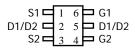

Dual N-Channel Enhancement Mode Field Effect Transistor

## **General Description**

The AO6808/L uses advanced trench technology to provide excellent  $R_{DS(ON)}$ , low gate charge and operation with gate voltages as low as 2.5V. This device is suitable for use as a load switch. It is ESD protected.

- -RoHS Compliant

- -AO6808L is Halogen Free

### **Features**

$$V_{DS} = 20V$$

$I_D = 6A$   $(V_{GS} = 4.5V)$

AO6808 and AO6808L are electrically identical.

$R_{DS(ON)} = 19m\Omega$  (typical) ( $V_{GS} = 4.5V$ )

$R_{DS(ON)} = 20m\Omega$  (typical) ( $V_{GS} = 4.0V$ )

$R_{DS(ON)} = 21m\Omega \text{ (typical)} \text{ (V}_{GS} = 3.1V)$

$R_{DS(ON)} = 23m\Omega$  (typical) ( $V_{GS} = 2.5V$ )

| Absolute Maximum Ratings T <sub>A</sub> =25°C unless otherwise noted |                      |                                   |            |              |       |  |  |

|----------------------------------------------------------------------|----------------------|-----------------------------------|------------|--------------|-------|--|--|

| Parameter                                                            |                      | Symbol                            | 10 Sec     | Steady State | Units |  |  |

| Drain-Source Voltage                                                 |                      | $V_{DS}$                          | 20         |              | V     |  |  |

| Gate-Source Voltage                                                  |                      | $V_{GS}$                          | ±12        |              | V     |  |  |

| Continuous Drain<br>Current <sup>A</sup>                             | T <sub>A</sub> =25°C |                                   | 6          | 4.6          |       |  |  |

|                                                                      | T <sub>A</sub> =70°C | I <sub>D</sub>                    | 4.6        | 3.7          | Α     |  |  |

| Pulsed Drain Current <sup>B</sup>                                    |                      | I <sub>DM</sub>                   | 60         |              |       |  |  |

| Power Dissipation <sup>A</sup>                                       | T <sub>A</sub> =25°C | $-P_{D}$                          | 1.3        | 0.8          | W     |  |  |

|                                                                      | T <sub>A</sub> =70°C | T D                               | 8.0        | 0.5          | VV    |  |  |

| Junction and Storage Temperature Range                               |                      | T <sub>J</sub> , T <sub>STG</sub> | -55 to 150 |              | °C    |  |  |

| Thermal Characteristics               |              |                                   |       |     |      |  |  |  |

|---------------------------------------|--------------|-----------------------------------|-------|-----|------|--|--|--|

| Parameter                             | Symbol       | Тур                               | Units |     |      |  |  |  |

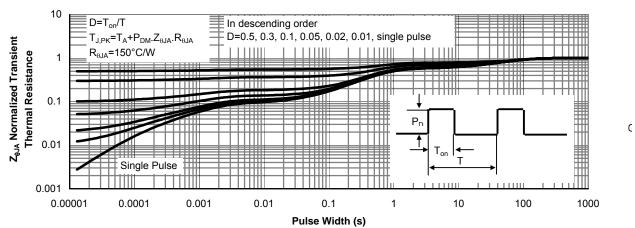

| Maximum Junction-to-Ambient A         | t ≤ 10s      | D                                 | 76    | 95  | °C/W |  |  |  |

| Maximum Junction-to-Ambient A         | Steady State | $R_{	hetaJA}$                     | 118   | 150 | °C/W |  |  |  |

| Maximum Junction-to-Lead <sup>C</sup> | Steady State | $R_{\scriptscriptstyle{	hetaJL}}$ | 54    | 68  | °C/W |  |  |  |

# Dual N-Channel Enhancement Mode Field Effect Transistor

#### Electrical Characteristics (T<sub>J</sub>=25°C unless otherwise noted)

| Symbol                | Parameter                             | Conditions                                                         | Min | Тур  | Max | Units |

|-----------------------|---------------------------------------|--------------------------------------------------------------------|-----|------|-----|-------|

| STATIC P              | ARAMETERS                             |                                                                    |     |      |     |       |

| $BV_{DSS}$            | Drain-Source Breakdown Voltage        | $I_D = 250 \mu A, V_{GS} = 0 V$                                    | 20  |      |     | V     |

| I <sub>DSS</sub>      | Zero Gate Voltage Drain Current       | V <sub>DS</sub> = 20V, V <sub>GS</sub> = 0V                        |     |      | 1   | μА    |

|                       |                                       | $T_J = 55^{\circ}C$                                                |     |      | 5   | μΑ    |

| $I_{GSS}$             | Gate-Body leakage current             | $V_{DS} = 0V, V_{GS} = \pm 10V$                                    |     |      | ±10 | μΑ    |

| $V_{GS(th)}$          | Gate Threshold Voltage                | $V_{DS} = V_{GS} I_{D} = 250 \mu A$                                | 0.5 | 0.75 | 1   | V     |

| $I_{D(ON)}$           | On state drain current                | $V_{GS} = 4.5V, V_{DS} = 5V$                                       | 60  |      |     | Α     |

| R <sub>DS(ON)</sub>   | Static Drain-Source On-Resistance     | $V_{GS} = 4.5V, I_D = 6.0A$                                        | 15  | 19   | 23  | mΩ    |

|                       |                                       | T <sub>J</sub> =125°C                                              | 21  | 27   | 33  |       |

|                       |                                       | $V_{GS} = 4.0V, I_D = 5.5A$                                        | 15  | 20   | 25  | mΩ    |

|                       |                                       | $V_{GS} = 3.1V, I_D = 5A$                                          | 16  | 21   | 27  | mΩ    |

|                       |                                       | $V_{GS} = 2.5V, I_D = 2A$                                          | 17  | 23   | 30  | mΩ    |

| g <sub>FS</sub>       | Forward Transconductance              | $V_{DS} = 5V, I_{D} = 6.0A$                                        |     | 34   |     | S     |

| $V_{SD}$              | Diode Forward Voltage                 | $I_S = 1A, V_{GS} = 0V$                                            |     | 0.65 | 1   | V     |

| I <sub>S</sub>        | Maximum Body-Diode Continuous Current |                                                                    |     |      | 1.3 | Α     |

| DYNAMIC               | PARAMETERS                            |                                                                    |     |      |     |       |

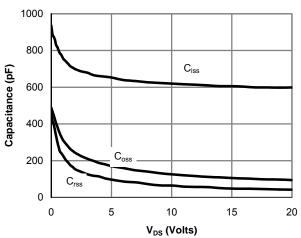

| C <sub>iss</sub>      | Input Capacitance                     |                                                                    |     | 620  | 780 | pF    |

| C <sub>oss</sub>      | Output Capacitance                    | $V_{GS}$ =0V, $V_{DS}$ =10V, f=1MHz                                |     | 125  |     | pF    |

| $C_{rss}$             | Reverse Transfer Capacitance          |                                                                    |     | 64   |     | pF    |

| SWITCHII              | NG PARAMETERS                         |                                                                    |     |      |     |       |

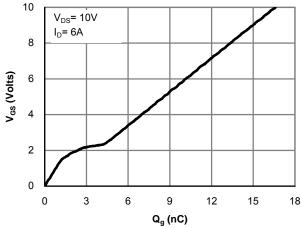

| Q <sub>g</sub> (10V)  | Total Gate Charge                     |                                                                    |     | 16.2 | 21  | nC    |

| Q <sub>g</sub> (4.5V) | Total Gate Charge                     | V <sub>GS</sub> = 10V, V <sub>DS</sub> = 10V, I <sub>D</sub> = 6A  |     | 7.7  | 10  | nC    |

| $Q_{gs}$              | Gate Source Charge                    | V <sub>GS</sub> - 10V, V <sub>DS</sub> - 10V, I <sub>D</sub> - 0A  |     | 1.5  |     | nC    |

| $Q_{gd}$              | Gate Drain Charge                     |                                                                    |     | 2.7  |     | nC    |

| t <sub>D(on)</sub>    | Turn-On DelayTime                     |                                                                    |     | 236  |     | ns    |

| t <sub>r</sub>        | Turn-On Rise Time                     | $V_{GS}$ =10V, $V_{DS}$ =10V, $R_{L}$ =1.7 $\Omega$ ,              |     | 448  |     | ns    |

| $t_{D(off)}$          | Turn-Off DelayTime                    | $R_{GEN}$ =3 $\Omega$                                              |     | 9.5  |     | μS    |

| t <sub>f</sub>        | Turn-Off Fall Time                    |                                                                    |     | 4.1  |     | μS    |

| t <sub>rr</sub>       | Body Diode Reverse Recovery Time      | I <sub>F</sub> =6A, dI/dt=100A/μs                                  |     | 25   | 33  | ns    |

| Q <sub>rr</sub>       | Body Diode Reverse Recovery Charge    | dy Diode Reverse Recovery Charge I <sub>F</sub> =6A, dI/dt=100A/μs |     | 9    |     | nC    |

A: The value of R  $_{\theta JA}$  is measured with the device mounted on 1in  $^2$  FR-4 board with 2oz. Copper, in a still air environment with T  $_A$  = 25°C. in any given application depends on the user's specific board design. The current rating is based on the t  $\leq$ 10s thermal resistance rating.

Rev0 April 2008

B: Repetitive rating, pulse width limited by junction temperature.

C. The R  $_{\theta JA}$  is the sum of the thermal impedence from junction to lead R  $_{\theta JL}$  and lead to ambient. D. The static characteristics in Figures 1 to 6 are obtained using < 300  $\mu s$  pulses, duty cycle 0.5% max.

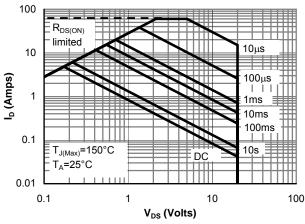

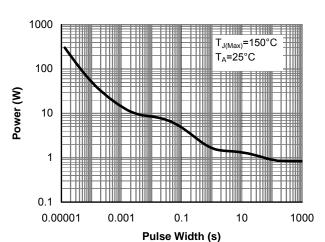

E. These tests are performed with the device mounted on 1 in  $^2$  FR-4 board with 2oz. Copper, in a still air environment with T  $_A$ =25°C. The SOA curve provides a single pulse rating.

Dual N-Channel Enhancement Mode Field Effect Transistor

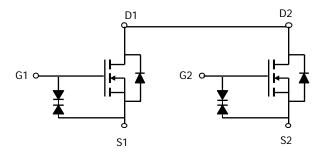

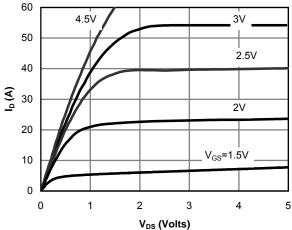

#### TYPICAL ELECTRICAL AND THERMAL CHARACTERISTICS

Figure 1: On-Region Characteristics

Figure 2: Transfer Characteristics

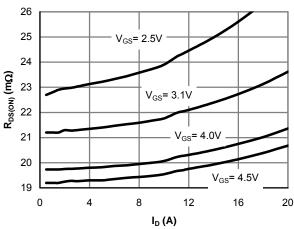

Figure 3: On-Resistance vs. Drain Current and Gate Voltage

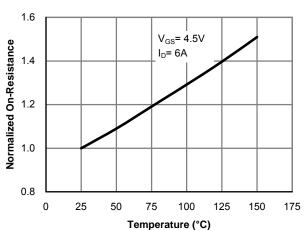

Figure 4: On-Resistance vs. Junction Temperature

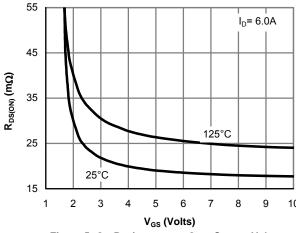

Figure 5: On-Resistance vs. Gate-Source Voltage

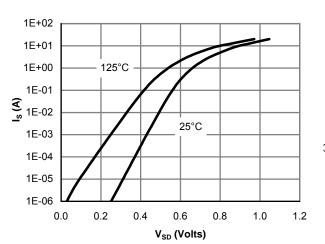

Figure 6: Body-Diode Characteristics

Dual N-Channel Enhancement Mode Field Effect Transistor

#### TYPICAL ELECTRICAL AND THERMAL CHARACTERISTICS

Figure 7: Gate-Charge Characteristics

Figure 8: Capacitance Characteristics

Figure 9: Maximum Forward Biased Safe

Operating Area (Note E)

Figure 10: Single Pulse Power Rating Junctionto-Ambient (Note E)

Figure 11: Normalized Maximum Transient Thermal Impedance(Note E)