Wireless Control

Edition February 19, 2010

Published by Infineon Technologies AG,

Am Campeon 1 - 12

85579 Neubiberg, Germany

© Infineon Technologies AG February 19, 2010.

All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as a guarantee of characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or the Infineon Technologies Companies and our Infineon Technologies Representatives worldwide (www.infineon.com).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

# SmartLEWIS<sup>TM</sup> RX+ TDA5235

Enhanced Sensitivity

Double-Configuration Receiver with

Digital Baseband Processing

Wireless Control

#### **TDA5235**

**Revision Number:** 010

**Revision History:** 2010-02-19 V1.0

| Revision history: | 2010-02-19                                                                         |

|-------------------|------------------------------------------------------------------------------------|

| Previous Version: | TDA5235_V0.1                                                                       |

| Page              | Subjects (major changes since last revision)                                       |

| Page 25           | Update of Figure 9                                                                 |

| Page 27           | Update of Figure 10                                                                |

| Page 29           | AFC limitation added                                                               |

| Page 31           | AGC setting proposal added                                                         |

| Page 32           | New Section 2.4.6.5 ADC added                                                      |

| Page 34           | Additional information on RSSIPRX register inserted                                |

| Page 39           | Signal and Noise Detector Procedure adapted                                        |

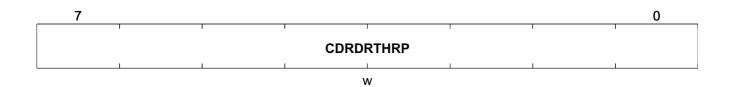

| Page 43           | x_CDRRI register recommendation changed                                            |

| Page 47, 50, 54   | Data Slicer Modes adapted; limitation added                                        |

| Page 67           | Update of Figure 41                                                                |

| Page 68           | Update of Figure 42                                                                |

| Page 76           | Additional hint on clock and data recovery algorithm of the user software inserted |

| Page 82           | PLDLEN limitation added                                                            |

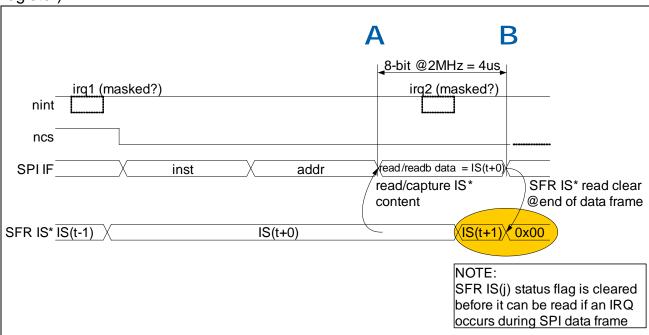

| Page 84           | Limitation for ISx readout and Burst-read function added                           |

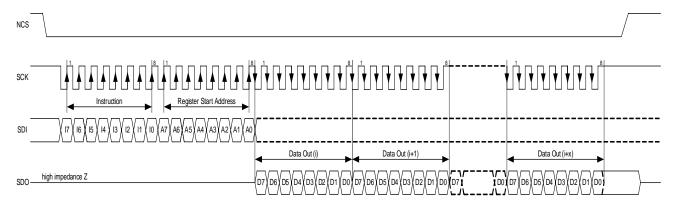

| Page 86           | Limitation for Burst-read function added                                           |

| Page 105          | Description of "Parallel Wake-up Search" adapted                                   |

| Page 123          | Additional hints added                                                             |

| Page 125          | Adaption of Section 4.1                                                            |

| Page 128          | New item C7 added                                                                  |

| Page 136 f        | Comments added for items I6, I7, I8, I9, J11, J12                                  |

| Page 136          | Item J1 updated                                                                    |

| Page 139 ff       | General test conditions noted for parameters K, L and M                            |

| Page 145          | BOM components C7, C8, L1, R2 and R3 updated                                       |

|                   | •                                                                                  |

#### **We Listen to Your Comments**

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to:

Wirelesscontrol@infineon.com

| Table of | able of Contents Pa                                     |    |  |

|----------|---------------------------------------------------------|----|--|

| 1        | Product Description                                     | 7  |  |

| 1.1      | Overview                                                | 7  |  |

| 1.2      | Features                                                | 8  |  |

| 1.3      | Applications                                            | 8  |  |

| 2        | Functional Description                                  | 9  |  |

| 2.1      | Pin Configuration                                       | 9  |  |

| 2.2      | Pin Definition and Pin Functionality                    | 10 |  |

| 2.3      | Functional Block Diagram                                | 16 |  |

| 2.4      | Functional Block Description                            | 17 |  |

| 2.4.1    | Architecture Overview                                   | 17 |  |

| 2.4.2    | Block Overview                                          | 18 |  |

| 2.4.3    | RF/IF Receiver                                          | 18 |  |

| 2.4.4    | Crystal Oscillator and Clock Divider                    | 22 |  |

| 2.4.5    | Sigma-Delta Fractional-N PLL Block                      | 25 |  |

| 2.4.5.1  | PLL Dividers                                            | 26 |  |

| 2.4.5.2  | Digital Modulator                                       | 26 |  |

| 2.4.6    | ASK and FSK Demodulator                                 | 27 |  |

| 2.4.6.1  | ASK Demodulator                                         | 27 |  |

| 2.4.6.2  | FSK Demodulator                                         | 28 |  |

| 2.4.6.3  | Automatic Frequency Control Unit (AFC)                  | 28 |  |

| 2.4.6.4  | Digital Automatic Gain Control Unit (AGC)               |    |  |

| 2.4.6.5  | Analog to Digital Converter (ADC)                       |    |  |

| 2.4.7    | RSSI Peak Detector                                      |    |  |

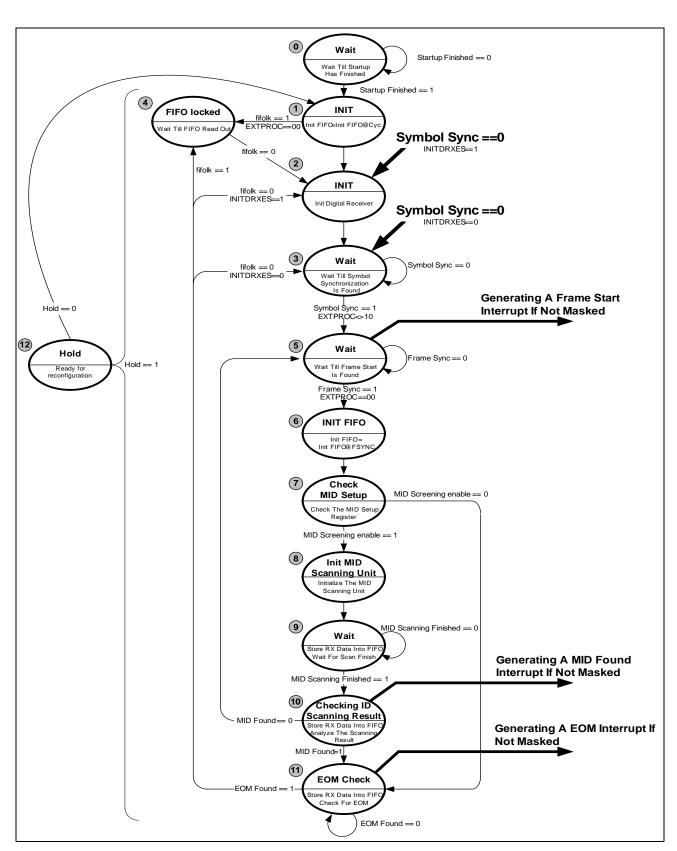

| 2.4.8    | Digital Baseband (DBB) Receiver                         |    |  |

| 2.4.8.1  | Data Filter and Signal Detection                        |    |  |

| 2.4.8.2  | Encoding Modes                                          |    |  |

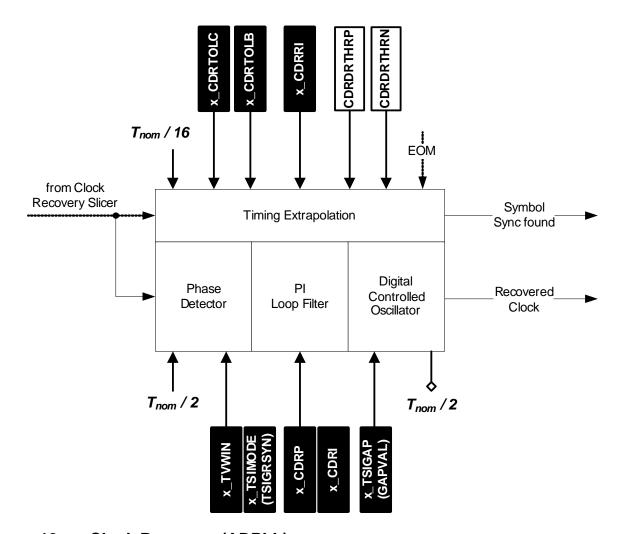

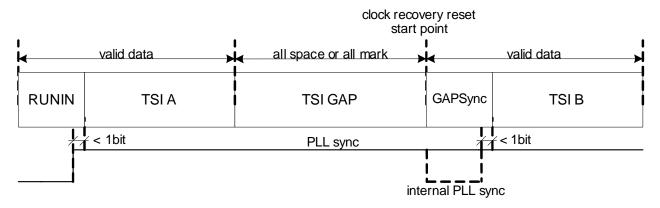

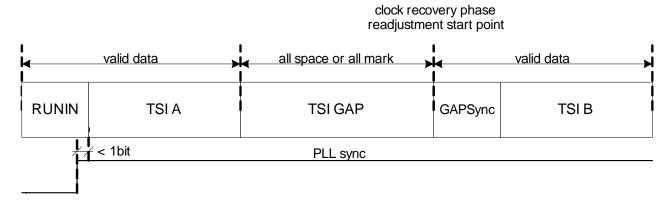

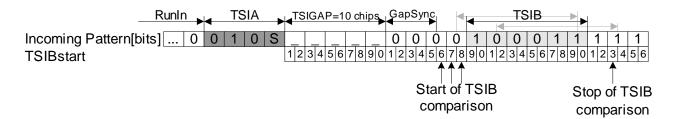

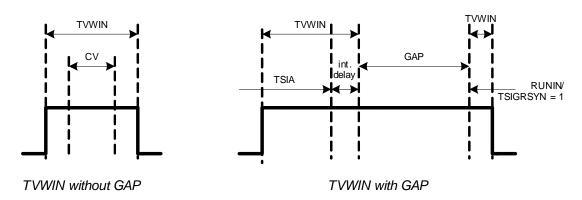

| 2.4.8.3  | Clock and Data Recovery                                 |    |  |

| 2.4.8.4  | Data Slicer and Line Decoding                           |    |  |

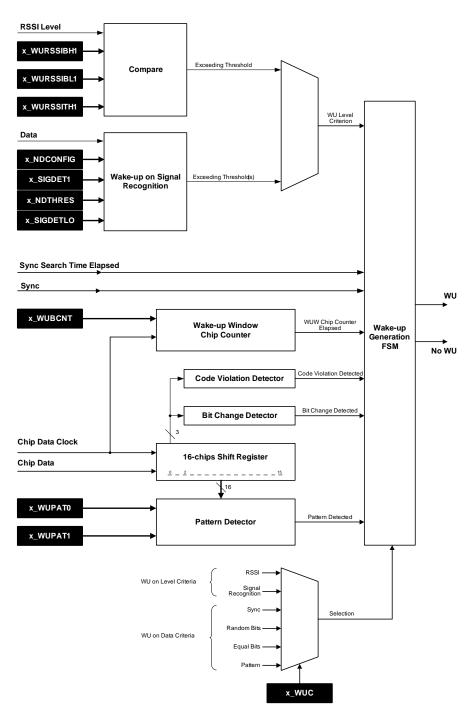

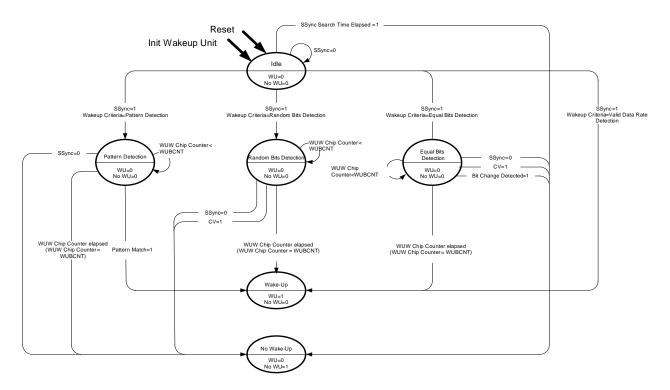

| 2.4.8.5  | Wake-Up Generator                                       |    |  |

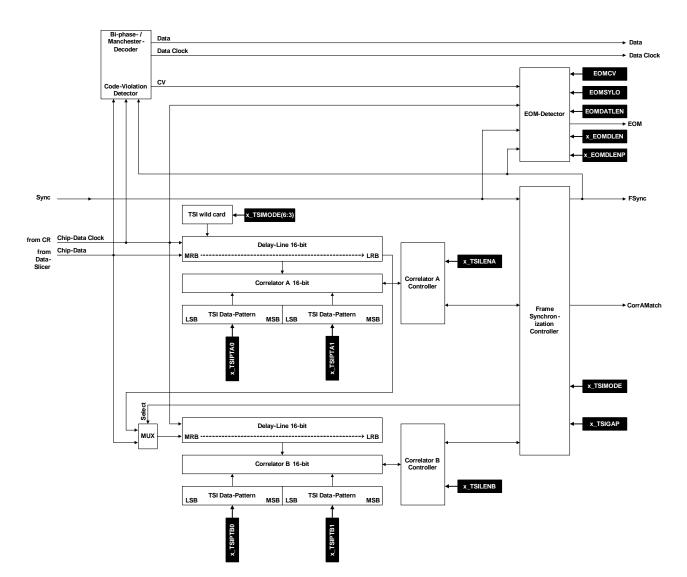

| 2.4.8.6  | Frame Synchronization                                   |    |  |

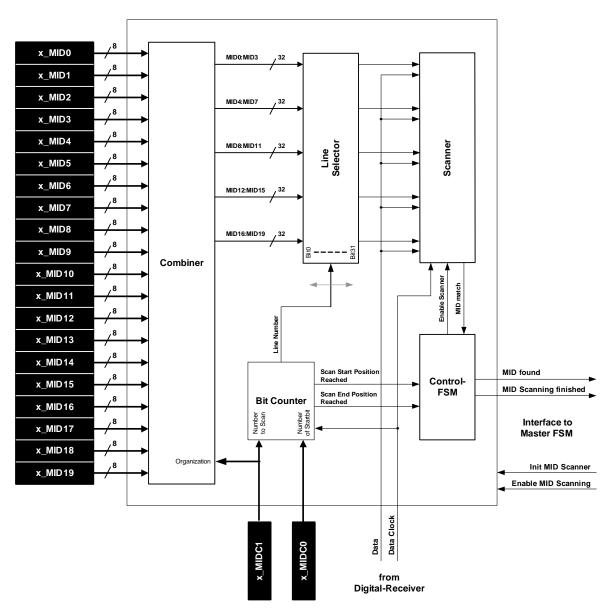

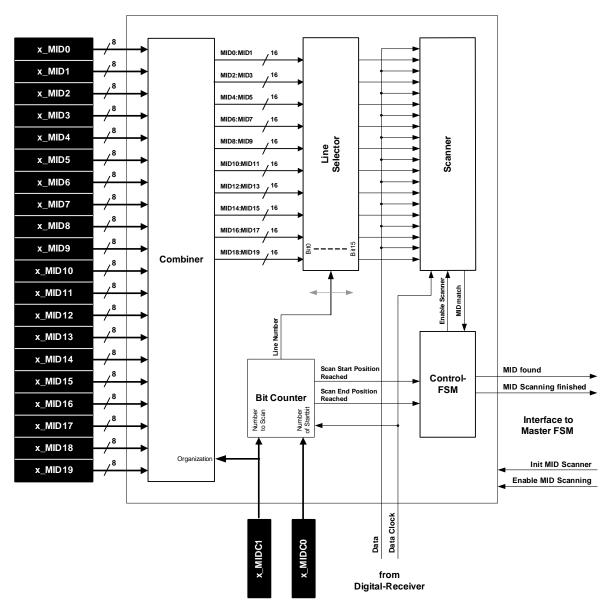

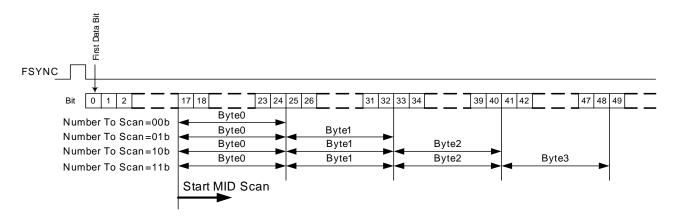

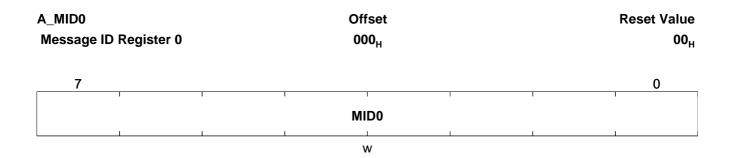

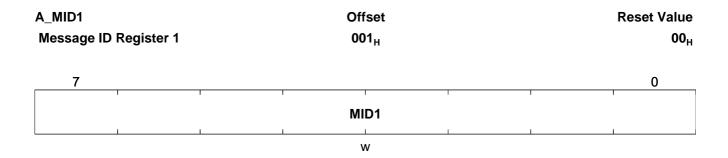

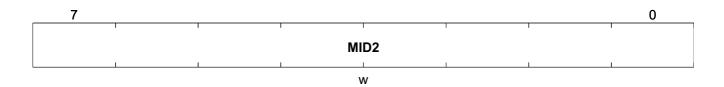

| 2.4.8.7  | Message ID Scanning                                     |    |  |

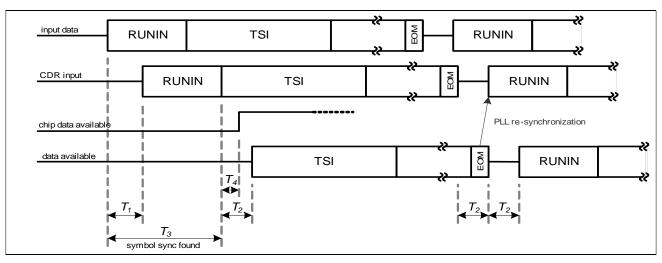

| 2.4.8.8  | RUNIN, Synchronization Search Time and Inter-Frame Time |    |  |

| 2.4.9    | Power Supply Circuitry                                  |    |  |

| 2.4.9.1  | Supply Current                                          |    |  |

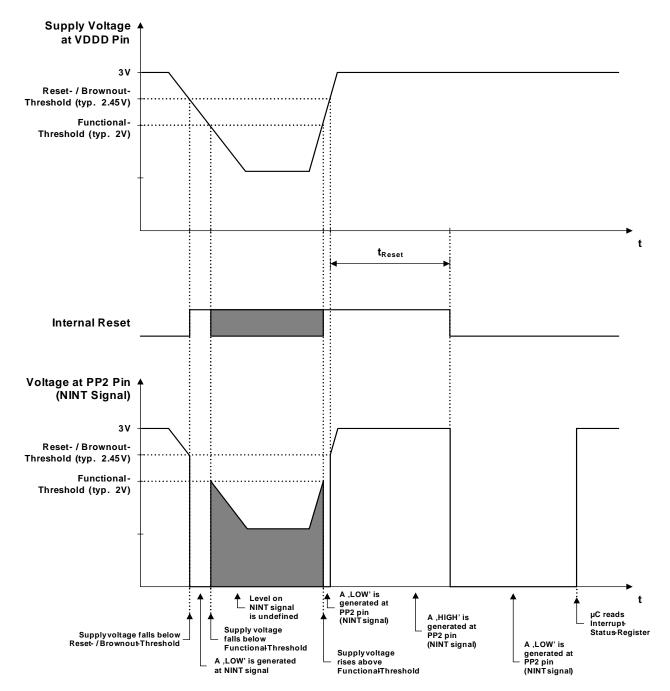

| 2.4.9.2  | Chip Reset                                              |    |  |

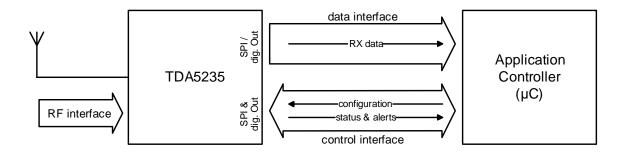

| 2.5      | System Interface                                        |    |  |

| 2.5.1    | Interfacing to the TDA5235                              |    |  |

| 2.5.1.1  | Control Interface                                       |    |  |

| 2.5.1.2  | Data Interface                                          |    |  |

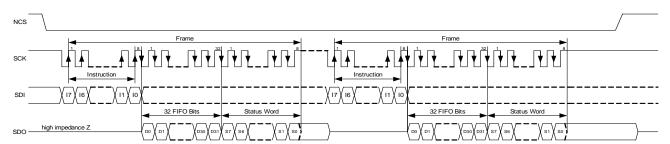

| 2.5.1.2  | Receive FIFO                                            |    |  |

| 2.5.3    | Digital Output Pins                                     |    |  |

| 2.5.4    | Interrupt Generation Unit                               |    |  |

| T        |                                                         |    |  |

| Table of | Contents                                                | Page  |

|----------|---------------------------------------------------------|-------|

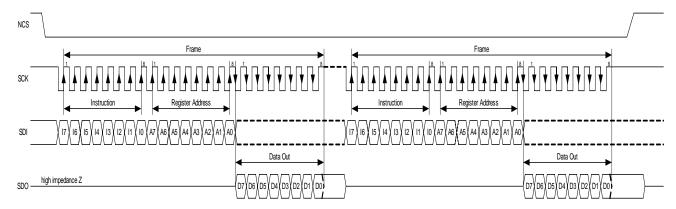

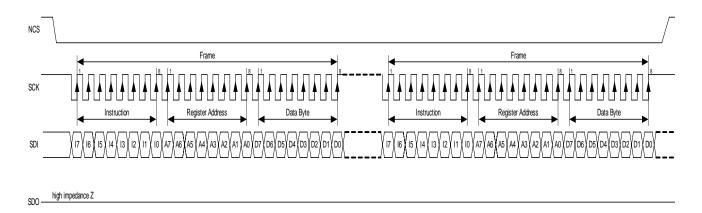

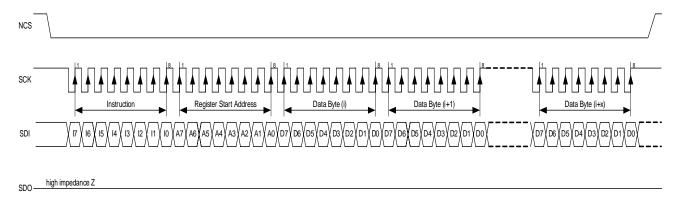

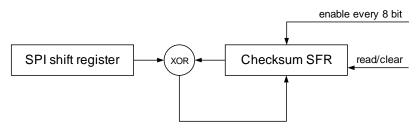

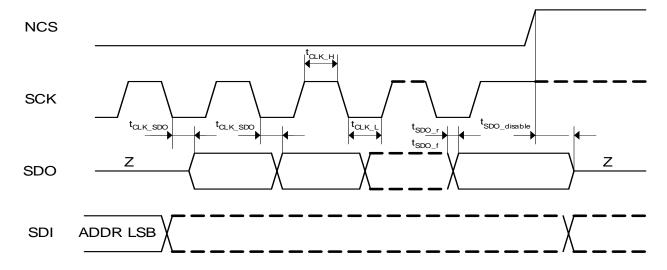

| 2.5.5    | Digital Control (4-wire SPI Bus)                        | 89    |

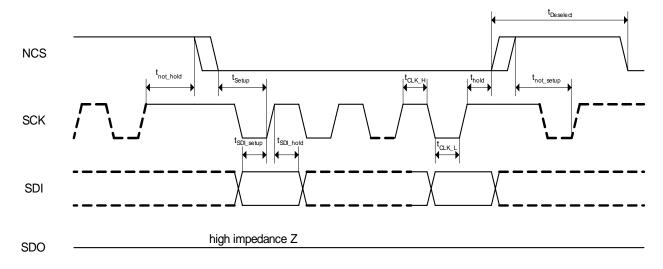

| 2.5.5.1  | Timing Diagrams                                         | 93    |

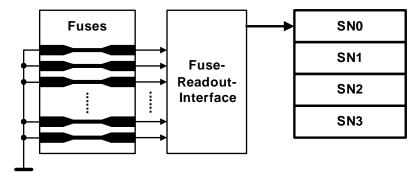

| 2.5.6    | Chip Serial Number                                      | 94    |

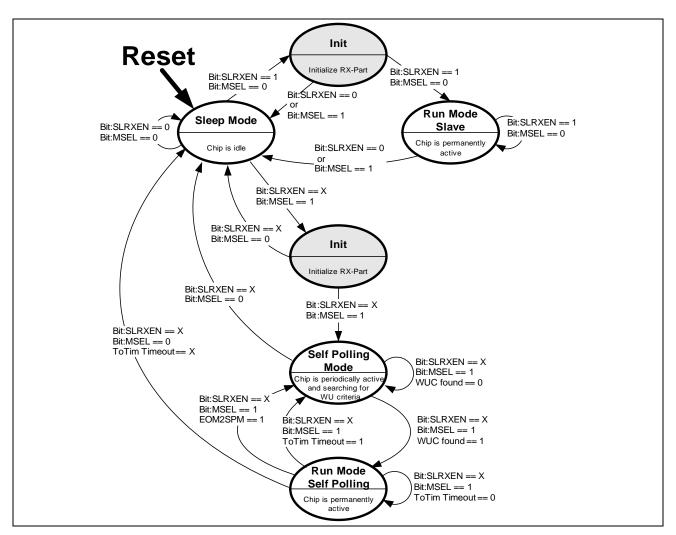

| 2.6      | System Management Unit (SMU)                            | 95    |

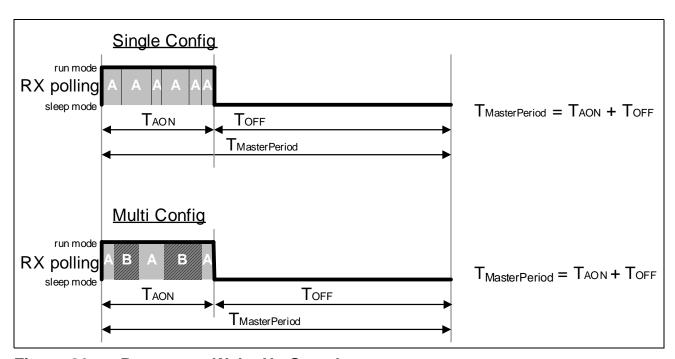

| 2.6.1    | Master Control Unit (MCU)                               | 95    |

| 2.6.1.1  | Overview                                                | 95    |

| 2.6.1.2  | Run Mode Slave (RMS)                                    |       |

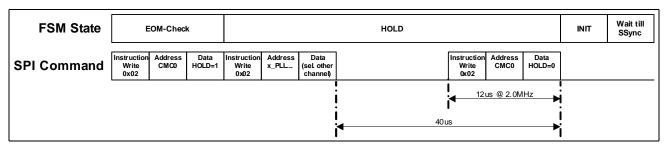

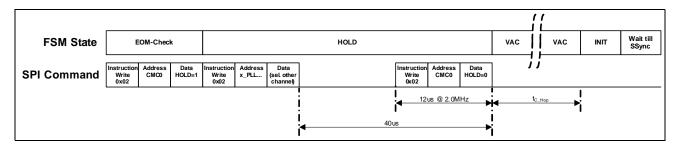

| 2.6.1.3  | HOLD Mode                                               |       |

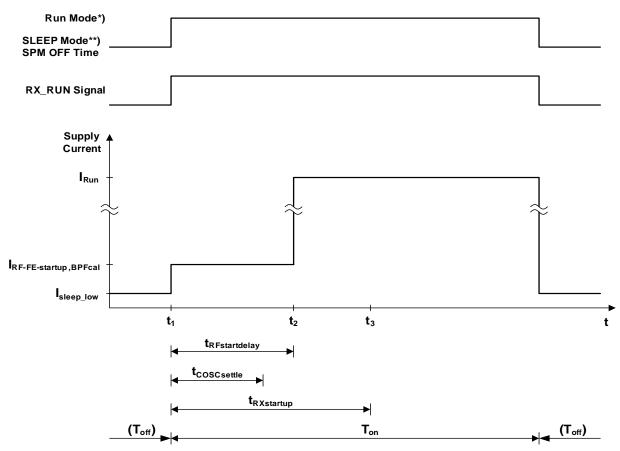

| 2.6.1.4  | SLEEP Mode                                              |       |

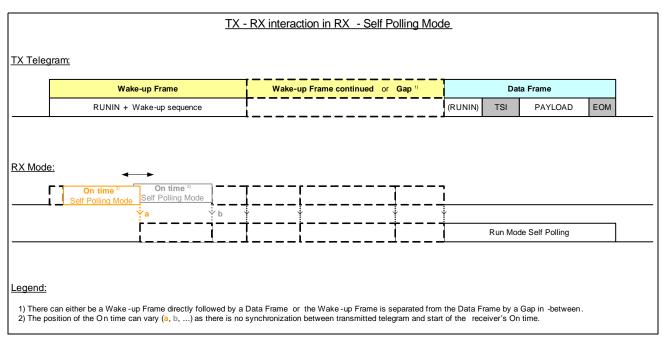

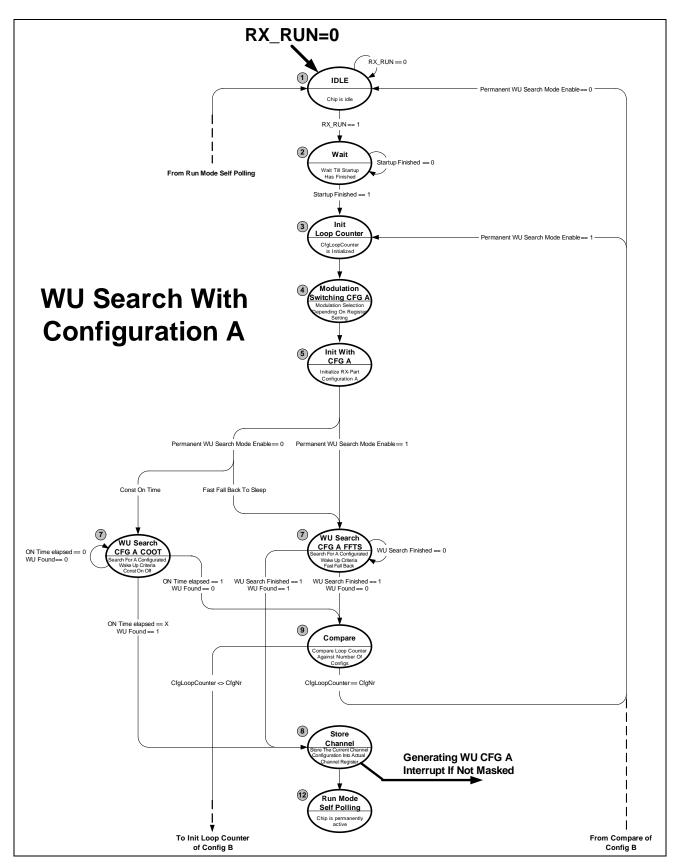

| 2.6.1.5  | Self Polling Mode (SPM)                                 |       |

| 2.6.1.6  | Automatic Modulation Switching                          |       |

| 2.6.1.7  | Multi-Channel in Self Polling Mode                      |       |

| 2.6.1.8  | Run Mode Self Polling (RMSP)                            |       |

| 2.6.2    | Polling Timer Unit                                      |       |

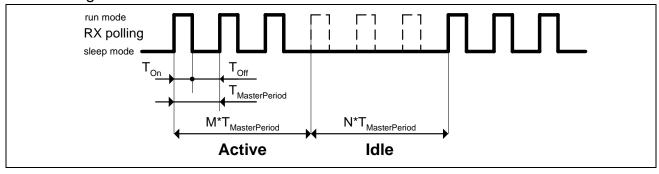

| 2.6.2.1  | Self Polling Modes                                      |       |

| 2.6.2.2  | Constant On-Off Time (COO)                              |       |

| 2.6.2.3  | Fast Fall Back to SLEEP (FFB)                           |       |

| 2.6.2.4  | Mixed Mode (MM, Const On-Off & Fast Fall Back to SLEEP) |       |

| 2.6.2.5  | Permanent Wake-Up Search (PWUS)                         |       |

| 2.6.2.6  | Active Idle Period Selection                            |       |

| 2.7      | Definitions                                             |       |

| 2.7.1    | Definition of Bit Rate                                  |       |

| 2.7.2    | Definition of Manchester Duty Cycle                     |       |

| 2.7.3    | Definition of Power Level                               |       |

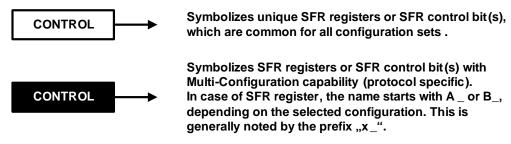

| 2.7.4    | Symbols of SFR Registers and Control Bits               |       |

| 2.8      | Digital Control (SFR Registers)                         |       |

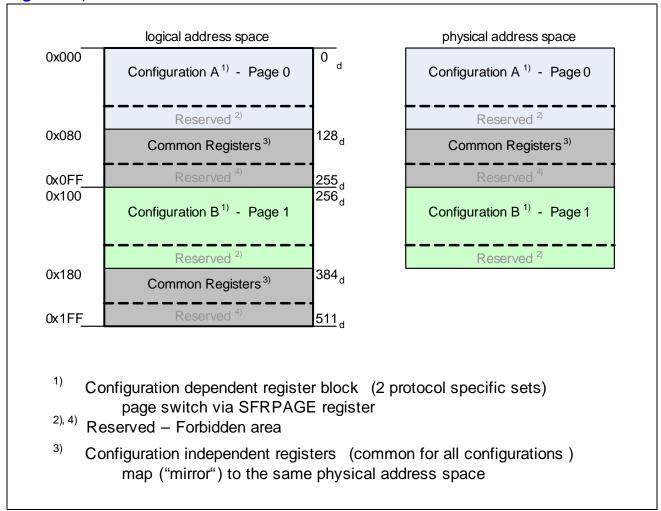

| 2.8.1    | SFR Address Paging                                      |       |

| 2.8.2    | SFR Register List and Detailed SFR Description          | . 127 |

| 3        | Applications                                            | . 129 |

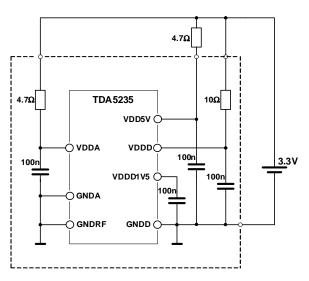

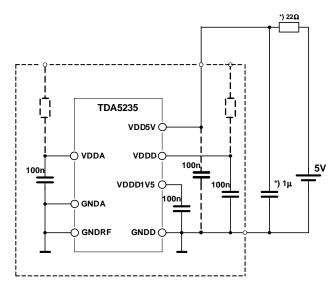

| 3.1      | Configuration Example                                   | . 130 |

| 4        | Reference                                               | . 131 |

| 4.1      | Electrical Data                                         |       |

| 4.1.1    | Absolute Maximum Ratings                                |       |

| 4.1.2    | Operating Range                                         |       |

| 4.1.3    | AC/DC Characteristics                                   |       |

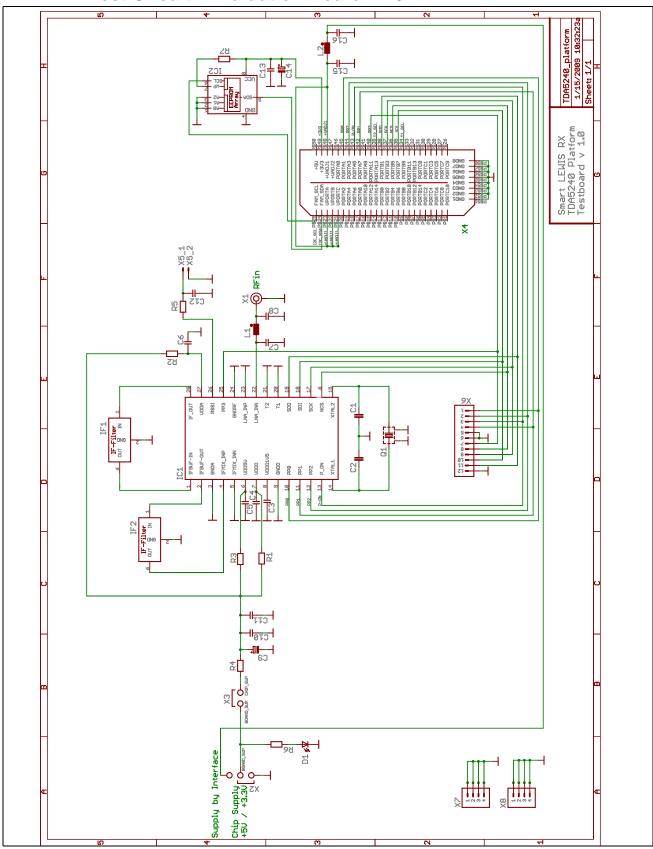

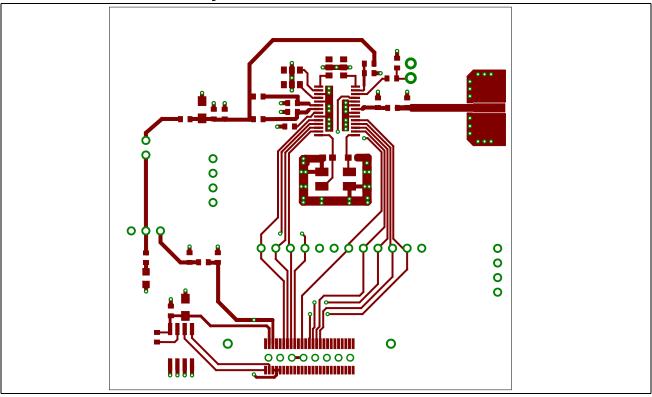

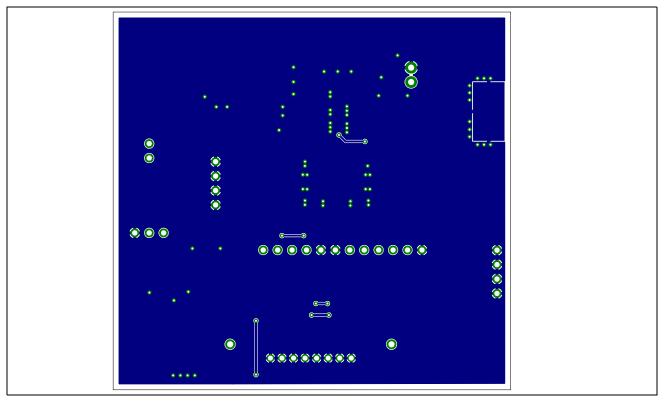

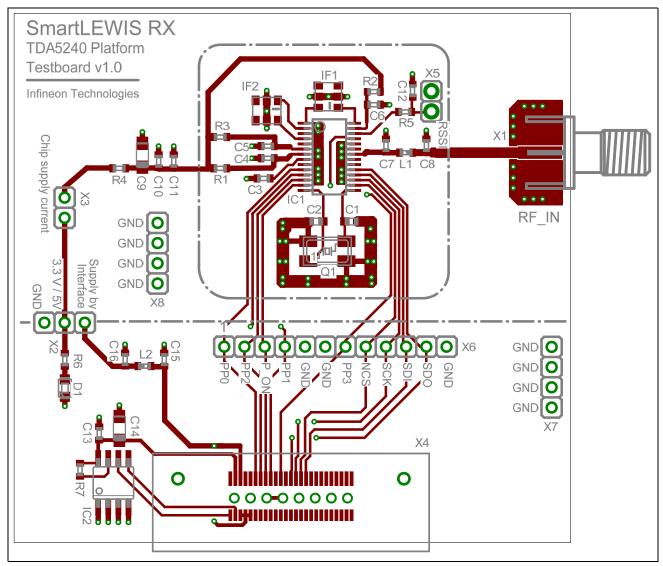

| 4.2      | Test Circuit - Evaluation Board v1.0                    | . 154 |

| 4.3      | Test Board Layout, Evaluation Board v1.0                | . 155 |

| 4.4      | Bill of Materials                                       |       |

| 5        | Package Outlines                                        | . 159 |

|          | Appendix - Registers Chapter                            | . 165 |

**Product Description**

# 1 Product Description

#### 1.1 Overview

The IC is a low power ASK/FSK Receiver for the frequency bands 300-320, 425-450, 863-870 and 902-928 MHz. Bi-phase modulation schemes, like Manchester, bi-phase mark, bi-phase space and differential Manchester are supported.

The chip offers best-in-class sensitivity performance at a very high level of integration and needs only a few external components.

The device is qualified to automotive quality standards and operates between -40 and +105°C at supply voltage ranges of 3.0-3.6 Volts or 4.5-5.5 Volts.

The receiver is realized as a double down conversion super-heterodyne/low-IF architecture each with image rejection supplemented by digital signal processing in the baseband. A fully integrated Sigma-Delta Fractional-N PLL Synthesizer allows for high-resolution frequency generation and uses a crystal oscillator as the reference. The on-chip temperature sensor may be utilized for temperature drift compensation via the crystal oscillator.

The digital baseband processing unit together with the high performance down converter is the key element for the exceptional sensitivity performance of the device which take it close to the theoretical top-performance limits. It comprises signal and noise detectors, matched data filter, clock and data recovery, data slicer and a format decoder. It demodulates the received ASK or FSK data stream independently and recovers the data clock out of the received data stream with very fast synchronization times which can then be either accessed via separate pins or used for further processing like frame synchronization and intermediate storage in the on-chip FIFO. The RSSI output signal is converted to the digital domain with an ADC. All these signals are accessible via the 4-wire SPI interface bus. Up to 2 pre-configured telegram formats can be stored into the device offering independent pre-processing of the received data to an extent not available till now. The down converter can be also configured in single-conversion mode at moderately reduced selectivity performance but at the advantage of omitting the IF ceramic filter.

#### **Product Description**

#### 1.2 Features

- Enhanced sensitivity receiver

- Multi-band (300-320, 425-450, 863-870 and 902-928 MHz)

- One crystal frequency for all supported frequency bands

- 21-bit Sigma-Delta Fractional-N PLL synthesizer with high resolution of 10.5 Hz

- Up to 2 parallel parameter sets for autonomous scanning and receiving from different sources reduces significantly host processor power consumption and system standby power consumption

- One frequency channels per parameter set is supported with 10.5 Hz resolution

- Autonomous receive mode leads to reduced noise of host processor and improved system performance

- Ultrafast Wake-up on RSSI

- Fast synchronization on incoming data stream typically within first 4 bits of a telegram

- Selectable IF filter bandwidth and optional external filters possible

- Double down conversion image reject mixer

- ASK and FSK capability

- Automatic Frequency Control (AFC) for carrier frequency offset compensation

- Supports bi-phase line codes like Manchester, bi-phase mark/space and differential Manchester

- NRZ data pre-processing capability

- · Digital base band receiver with clock synch, frame synch, format decoding and FIFO

- Separate outputs for recovered data and clock

- RSSI peak detectors

- · Wake-up generator and polling timer unit

- Message ID scanning

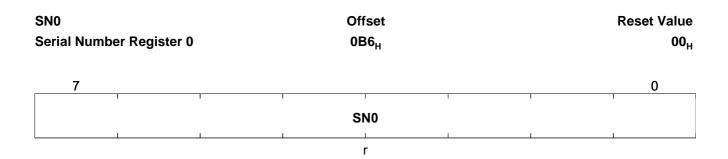

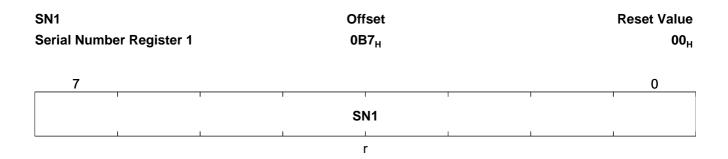

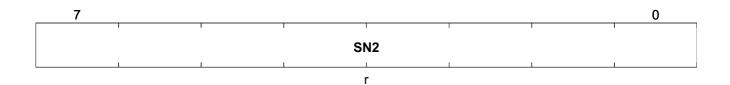

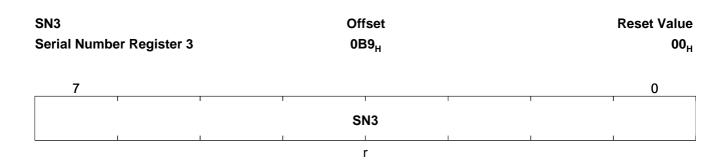

- Unique 32-bit serial number

- On-chip temperature sensor

- Integrated timer usable for external watch unit

- Integrated 4-wire SPI interface bus

- Supply voltage range 3.0 Volts to 3.6 Volts or 4.5 Volts to 5.5 Volts

- Operating temperature range -40 to +105°C

- ESD protection +/- 2 kV on all pins

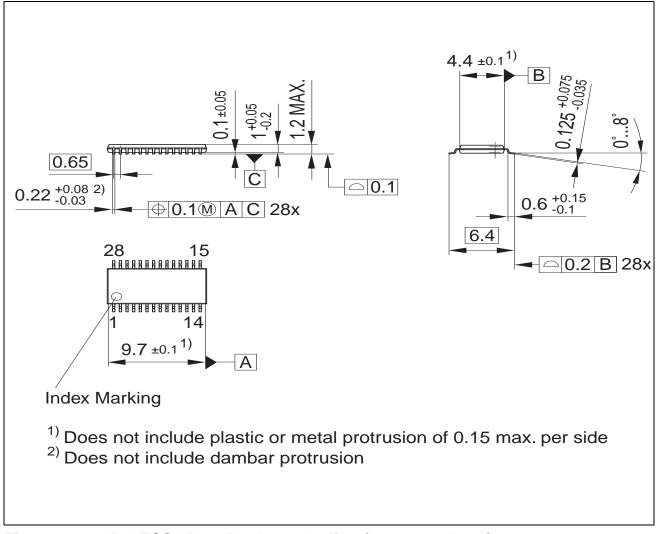

- Package PG-TSSOP-28

# 1.3 Applications

- Remote keyless entry systems

- · Remote start applications

- Tire pressure monitoring

- Short range radio data transmission

- Remote control units

- Cordless alarm systems

- Remote metering

# **2** Functional Description

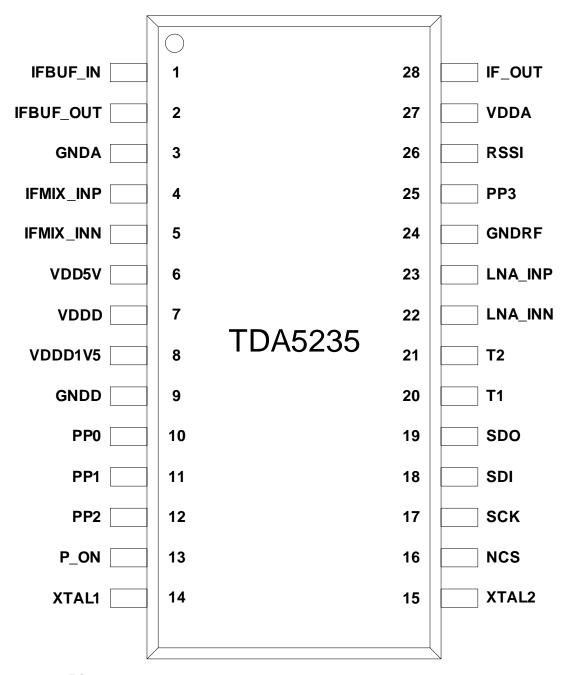

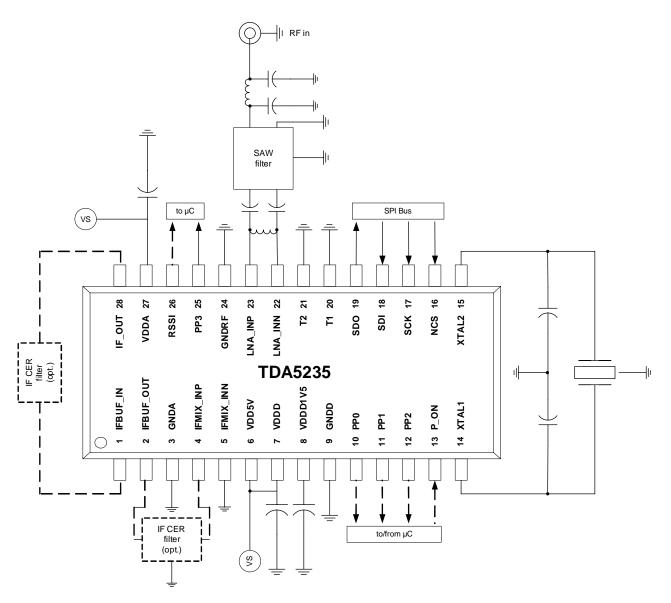

# 2.1 Pin Configuration

Figure 1 Pin-out

# 2.2 Pin Definition and Pin Functionality

Table 1 Pin Definition and Function

| Pin<br>No. | Pad name  | Equivalent I/O Schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Function                                                       |

|------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| 1          | IFBUF_IN  | IFBUF_IN 330\(\Omega\) IFBUF AVDDA  WIFMIX_INN MIX 2BUF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Analog input IF Buffer input Note: Input is biased at VDDA/2   |

| 2          | IFBUF_OUT | VDDA VDDA  STATE OF THE STATE | Analog output<br>IF Buffer output                              |

| 3          | GNDA      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Analog ground                                                  |

| 4          | IFMIX_INP | IFMIX_INP 330Ω IFMIX_INN MIX2BUF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Analog input + IF mixer input  Note: Input is biased at VDDA/2 |

| 5          | IFMIX_INN | see schematic of Pin 1 and 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Analog input IF mixer input                                    |

| 6          | VDD5V     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Analog input 5 Volt supply input                               |

| Pin<br>No. | Pad name | Equivalent I/O Schematic         | Function                                                                                                                                                                       |

|------------|----------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7          | VDDD     | VDD5V VReg VDDD VDDD             | Analog input digital supply input                                                                                                                                              |

| 8          | VDDD1V5  | VDDD  VReg  VDD1V5               | Analog output 1.5 Volt voltage regulator                                                                                                                                       |

| 9          | GNDD     |                                  | Digital ground                                                                                                                                                                 |

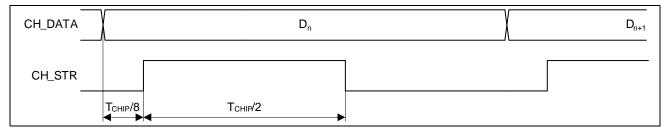

| 10         | PP0      | VDD5V VDD5V  PPx SDO  GNDD  GNDD | Digital output CLK_OUT, RX_RUN, NINT, LOW, HIGH, DATA, DATA_MATCHFIL, CH_DATA, CH_STR, RXD and RXSTR are programmable via a SFR (Special Function Register), default = CLK_OUT |

| Pin<br>No. | Pad name | Equivalent I/O Schematic   | Function                                                                                                                                        |

|------------|----------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 11         | PP1      | see schematic of Pin 10    | Digital output CLK_OUT, RX_RUN, NINT, LOW, HIGH, DATA, DATA_MATCHFIL, CH_DATA, CH_STR, RXD and RXSTR are programmable via a SFR, default = DATA |

| 12         | PP2      | see schematic of Pin 10    | Digital output CLK_OUT, RX_RUN, NINT, LOW, HIGH, DATA, DATA_MATCHFIL, CH_DATA, CH_STR, RXD and RXSTR are programmable via a SFR, default = NINT |

| 13         | P_ON     | P_ON NCS SCK SDI GNDD GNDD | Digital input power-on reset                                                                                                                    |

| Pin<br>No. | Pad name | Equivalent I/O Schematic                       | Function                                       |

|------------|----------|------------------------------------------------|------------------------------------------------|

| 14         | XTAL1    | VDDD VDDD  A A A A A A A A A A A A A A A A A A | Analog input crystal oscillator input          |

| 15         | XTAL2    | VDDD VDDD  A A A A A A A A A A A A A A A       | Analog output crystal oscillator output        |

| 16         | NCS      | see schematic of Pin 13                        | Digital input<br>SPI enable                    |

| 17         | SCK      | see schematic of Pin 13                        | Digital input<br>SPI clock                     |

| 18         | SDI      | see schematic of Pin 13                        | Digital input<br>SPI data in                   |

| 19         | SDO      | see schematic of Pin 10                        | Digital output<br>SPI data out                 |

| 20         | T1       |                                                | Digital input,<br>connect to Digital<br>Ground |

| 21         | T2       |                                                | Digital input,<br>connect to Digital<br>Ground |

| Pin<br>No. | Pad name | Equivalent I/O Schematic       | Function                                                                                                                                 |

|------------|----------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| 22         | LNA_INN  | LNA_INN LNA GNDRF              | Analog input - RF input                                                                                                                  |

| 23         | LNA_INP  | LNA_INP LNA GNDRF              | Analog input<br>+ RF input                                                                                                               |

| 24         | GNDRF    |                                | RF analog ground                                                                                                                         |

| 25         | PP3      | see schematic of Pin 10        | Digital output RX_RUN, NINT, LOW, HIGH, DATA, DATA_MATCHFIL, CH_DATA, CH_STR, RXD and RXSTR are programmable via a SFR, default = RX_RUN |

| 26         | RSSI     | VDDA VDDA  A  500Ω  GNDA  GNDA | Analog output<br>analog RSSI output/<br>analog test pin<br>ANA_TST                                                                       |

| Pin<br>No. | Pad name | Equivalent I/O Schematic                  | Function                      |

|------------|----------|-------------------------------------------|-------------------------------|

| 27         | VDDA     | VDD5V                                     | Analog input<br>Analog supply |

|            |          | GNDA                                      |                               |

| 28         | IF_OUT   | VDDA VDDA  IF_OUT  GNDA  SNDA  SNDA  SNDA | Analog output<br>IF output    |

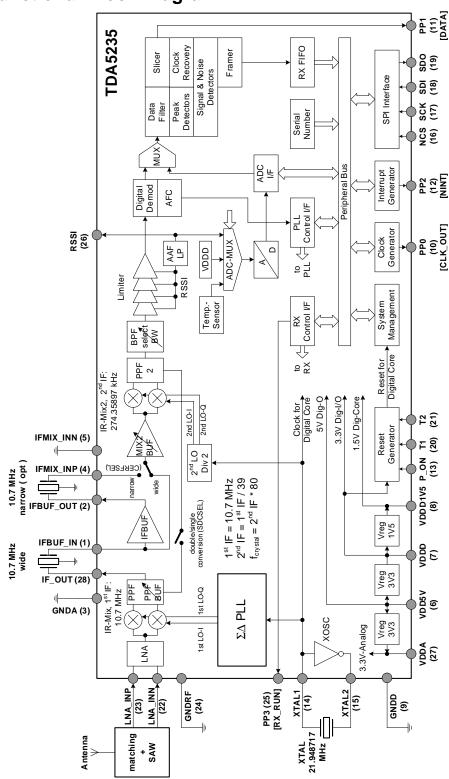

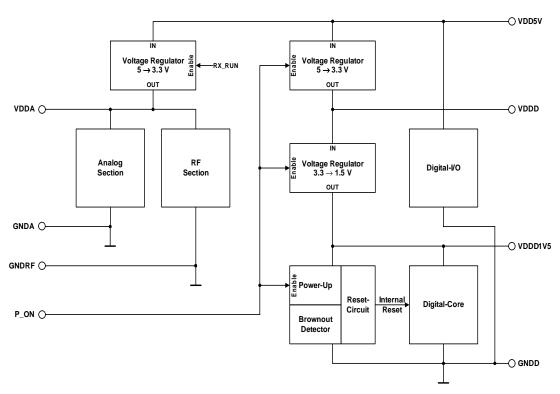

## 2.3 Functional Block Diagram

Figure 2 TDA5235 Block Diagram<sup>1)</sup>

<sup>1)</sup> The function on each PPx port pin can be programmed via SFR (see also **Table 1**). Default values are given in squared brackets in **Figure 2**.

## 2.4 Functional Block Description

#### 2.4.1 Architecture Overview

A fully integrated Sigma-Delta Fractional-N PLL Synthesizer covers the frequency bands 300-320 MHz, 425-450 MHz, 863-870 MHz, 902-928 MHz with a high frequency resolution, using only one VCO running at around 3.6 GHz.

For Multi-Configuration applications requiring different RF channels a very good channel separation is essential. To achieve the necessary high sensitivity and selectivity a double down conversion super-heterodyne architecture is used. The first IF frequency is located around 10.7 MHz and the second IF frequency around 274 kHz. For both IF frequencies an adjustment-free image frequency rejection feature is realized. In the second IF domain the filtering is done with an on-chip third order bandpass polyphase filter. A multistage bandpass limiter completes the RF/IF path of the receiver. For Single-Channel applications with relaxed requirements to selectivity, a single down conversion low-IF scheme can be selected.

For Multi-Configuration systems requiring different RF channels where even higher channel separation is required, up to two (switchable) external ceramic (CER) filters can be used to improve the selectivity.

An RSSI generator delivers a DC signal proportional to the applied input power and is also used as an ASK demodulator. Via an anti-aliasing filter this signal feeds an ADC with 10 bits resolution.

The harmonic suppressed limiter output signal feeds a digital FSK demodulator. This block demodulates the FSK data and delivers an AFC signal which controls the divider factor of the PLL synthesizer.

A digital receiver, which comprises RSSI peak detectors, a matched data filter, a clock and data recovery, a data slicer, a frame synchronization and a data FIFO, decodes the received ASK or FSK data stream. The recovered data and clock signals are accessible via 2 separate pins. The FIFO data buffer is accessible via the SPI bus interface.

The crystal oscillator serves as the reference frequency for the PLL phase detector, the clock signal of the Sigma-Delta modulator and divided by two as the 2<sup>nd</sup> local oscillator signal. To accelerate the start up time of the crystal oscillator two modes are selectable: a Low Power Mode (with lower precision) and a High Precision Mode.

#### 2.4.2 Block Overview

The TDA5235 is separated into the following main blocks:

- RF / IF Receiver

- Crystal Oscillator and Clock Divider

- Sigma-Delta Fractional-N PLL Synthesizer

- ASK / FSK Demodulator incl. AFC, AGC and ADC

- RSSI Peak Detector

- Digital Baseband Receiver

- Power Supply Circuitry

- System Interface

- System Management Unit

#### 2.4.3 RF/IF Receiver

The receiver path uses a double down conversion super-heterodyne/low-IF architecture, where the first IF frequency is located around 10.7 MHz and the second IF frequency around 274 kHz. For the first IF frequency an adjustment-free image frequency rejection is realized by means of two low-side injected I/Q-mixers followed by a second order passive polyphase filter centered at 10.7 MHz (PPF). The I/Q-oscillator signals for the first down conversion are delivered from the PLL synthesizer. The frequency selection in the first IF domain is done by an external CER filter (optionally by two, decoupled by a buffer amplifier). For moderate or low cost applications, this ceramic filter can be substituted by a simple LC Pi-filter or completely by-passed using the receiver as a single down conversion low-IF scheme with 274 kHz IF frequency. The down conversion to the second IF frequency is done by means of two high-side injected I/Q-mixers together with an on-chip third order bandpass polyphase filter (PPF2 + BPF). The I/Qoscillator signals for the second down conversion are directly derived by division of two from the crystal oscillator frequency. The bandwidth of the bandpass filter (BPF) can be selected from 50 kHz to 300 kHz in 5 steps. For a frequency offset of -150 kHz to -120 kHz, the AFC (Automatic Frequency Control) function is mandatory. Activated AFC option might require a longer preamble sequence in the receive data stream.

The receiver enable signal (RX\_RUN) can be offered at each of the port pins to control external components. Whenever the receiver is active, the RX\_RUN output signal is active. Active high or active low is configurable via PPCFG2 register.

The frequency relations are calculated with the following formulas:

$$f_{IF1} = 10.7MHz$$

$$f_{IF2} = \frac{f_{IF1}}{39}$$

$$f_{crystal} = f_{IF2} \times 80$$

$$f_{LO2} = \frac{f_{crystal}}{2}$$

$$f_{LO1} = f_{crystal} \times NF_{divider}$$

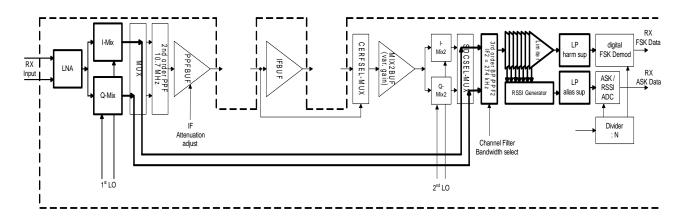

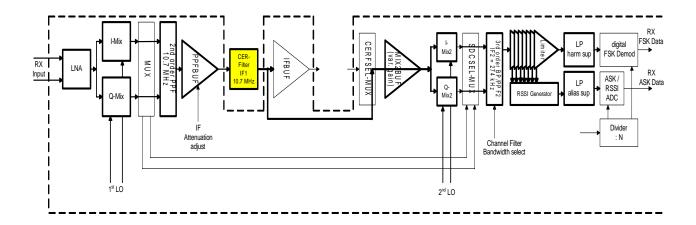

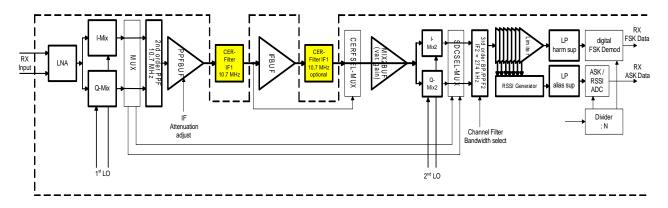

Figure 3 Block Diagram RF Section

The front end of the receiver comprises an LNA, an image reject mixer and a digitally gain controlled buffer amplifier. This buffer amplifier allows the production spread of the on-chip signal strip, of external matching circuitry and RF SAW and ceramic IF filters to be trimmed. The second image reject mixer down converts the first IF to the second IF.

The bandpass filter follows the subsequent formula:

$$f_{center} = \sqrt{f_{corner, low} \times f_{corner, high}}$$

Therefore asymmetric corner frequencies can be observed. The use of AFC results in more symmetry.

A multi-stage bandpass limiter at a center frequency of 274 kHz completes the receiver chain. The -3dB corner frequencies of the bandpass limiter are typically at 75 kHz and at 520 kHz.

An RSSI generator delivers a DC signal proportional to the applied input power and is also used as an ASK demodulator. Via a programmable anti-aliasing filter this signal is converted to the digital domain by means of a 10-bit ADC.

The limiter output signal is connected to a digital FSK demodulator.

The immunity against strong interference frequencies (so called blockers) is determined by the available filter bandwidth, the filter order and the 3<sup>rd</sup> order intercept point of the front end stages. For Single-Channel applications with moderate requirements to the selectivity the performance of the on-chip 3<sup>rd</sup> order bandpass polyphase filter might be sufficient. In this case no external filters are necessary and a single down conversion architecture can be used, which converts the input signal frequency directly to the 2<sup>nd</sup> IF frequency of 274 kHz.

Figure 4 Single Down Conversion (SDC, no external filters required)

For Multi-Configuration applications requiring different RF channels or systems which demand higher selectivity the double down conversion scheme together with one or two external CER filters can be selected. The order of such ceramic filters is in a range of 3, so the selectivity is further improved and a better channel separation is guaranteed.

Figure 5 Double Down Conversion (DDC) with one external filter

For applications which demand very high selectivity and/or channel separation even two CER filters may be used. Also in applications where one configuration/channel requires a wider bandwidth than the other (e.g. TPMS and RKE) the second filter can be bypassed.

Figure 6 Double Down Conversion (DDC) with two external filters

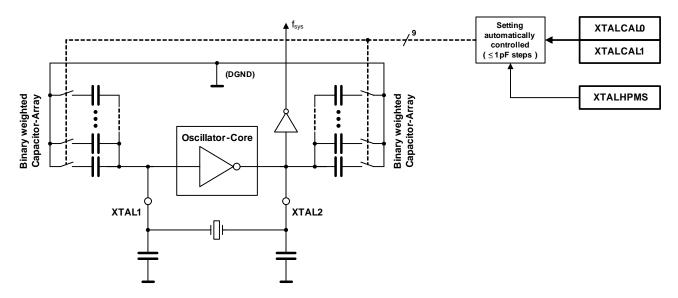

## 2.4.4 Crystal Oscillator and Clock Divider

The crystal oscillator is a Pierce type oscillator which operates together with the crystal in parallel resonance mode. An automatic amplitude regulation circuitry allows the oscillator to operate with minimum current consumption. In SLEEP Mode, where the current consumption should be as low as possible, the load capacitor must be small and the frequency is slightly detuned, therefore all internal trim capacitors are disconnected. The internal capacitors are controlled by the crystal oscillator calibration registers XTALCALx. With a binary weighted capacitor array the necessary load capacitor can be selected.

Whenever a XTALCALx register value is updated, the selected trim capacitors are automatically connected to the crystal so that the frequency is precise at the desired value. The SFR control bit XTALHPMS can be used to activate the High Precision Mode also during SLEEP Mode.

Figure 7 Crystal Oscillator

#### **Recommended Trimming Procedure**

- Set the registers XTALCAL0 and XTALCAL1 to the expected nominal values

- Set the TDA5235 to Run Mode Slave

- Wait for 0.5ms minimum

- Trim the oscillator by increasing and decreasing the values of XTALCAL0/1

- Register changes larger than 1 pF are automatically handled by the TDA5235 in 1pF steps

- After the Oscillator is trimmed, the TDA5235 can be set to SLEEP mode and keeps these values during SLEEP mode

- Add the settings of XTALCAL0/1 to the configuration. It must be set after every power up or brownout!

#### **Using the High Precision Mode**

As discussed earlier, the TDA5235 allows the crystal oscillator to be trimmed by the use of internal trim capacitors. It is also possible to use the trim functionality to compensate temperature drift of crystals.

During Run Mode (always when the receiver is active) the capacitors are automatically connected and the oscillator is working in the High Precision Mode.

On entering SLEEP Mode, the capacitors are automatically disconnected to save power.

If the High Precision Mode is also required for SLEEP Mode, the automatic disconnection of trim capacitors can be avoided by setting XTALHPMS to 1 (enable XTAL High Precision Mode during SLEEP Mode).

#### **External Clock Generation Unit**

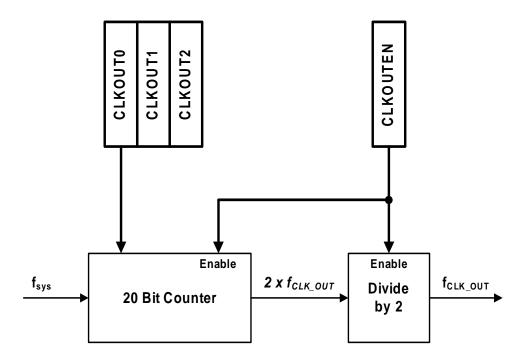

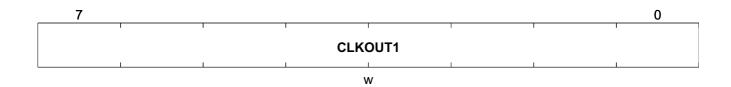

A built in programmable frequency divider can be used to generate an external clock source out of the crystal reference. The 20 bit wide division factor is stored in the registers CLKOUT0, CLKOUT1 and CLKOUT2. The minimum value of the programmable frequency divider is 2. This programmable divider is followed by an additional divider by 2, which generates a 50% duty cycle of the CLK\_OUT signal. So the maximum frequency at the CLK\_OUT signal is the crystal frequency divided by 4. The minimum CLK\_OUT frequency is the crystal frequency divided by 2<sup>21</sup>.

To save power, this programmable clock signal can be disabled by the SFR control bit CLKOUTEN. In this case the external clock signal is set to low.

The resulting CLK\_OUT frequency can be calculated by:

$$f_{CLKOUT} = \frac{f_{sys}}{2 \cdot division factor}$$

Figure 8 External Clock Generation Unit

The maximum CLK\_OUT frequency is limited by the driver capability of the PPx pin and depends on the external load connected to this pin. Please be aware that large loads and/or high clock frequencies at this pin may interfere with the receiver and reduce performance.

After Reset the PPx pin is activated and the division factor is initialized to 11 (equals  $f_{CLK\ OUT} = 998\ kHz$ ).

A clock output frequency higher than 1 MHz is not supported.

For high sensitivity applications, the use of the external clock generation unit is not recommended.

## 2.4.5 Sigma-Delta Fractional-N PLL Block

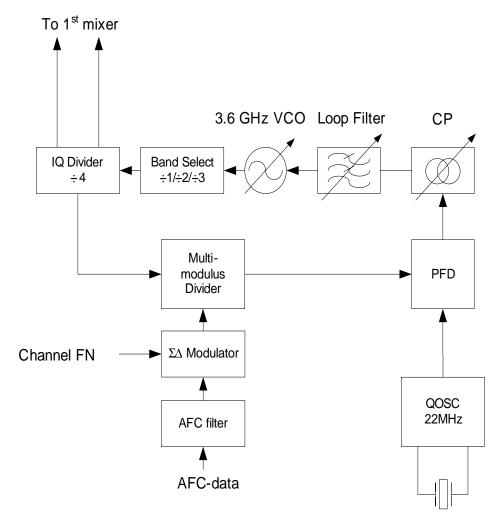

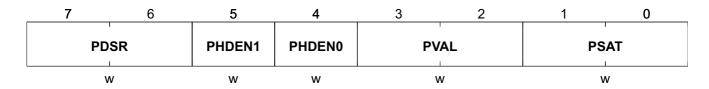

The Sigma-Delta Fractional-N PLL is fully integrated on chip. The *Voltage Controlled Oscillator* (VCO) with on-chip LC-tank runs at approximately 3.6 GHz and is first divided with a band select divider by 1, 2 or 3 and then with an I/Q-divider by 4 which provides an orthogonal local oscillator signal for the first image reject mixer with the necessary high accuracy.

The multi-modulus divider determines the channel selection and is controlled by a 3<sup>rd</sup> order Sigma-Delta Modulator (*SDM*). A type IV phase detector, a charge pump with programmable current and an on-chip loop filter closes the phase locked loop.

Figure 9 Synthesizer Block Diagram

When defining a Multi-Configuration system requiring different RF channels, the correct selection of channel spacing is extremely important. A general rule is not possible, but following must be considered:

- If an additional SAW filter is used, all channels including their tolerances have to be inside the SAW filter bandwidth.

- The distance between channels must be high enough, that no overlapping can occur. Strong input signals may still appear as recognizable input signal in the neighboring channel because of the limited suppression of IF Filters. Example: a typical 330kHz IF filter has at 10.3 MHz ( 10.7 MHz 0.4 MHz ) only 30 dB suppression. A -70 dBm input signal appears like a -100 dBm signal, which is inside the receiver sensitivity. In critical cases the use of two IF filters must be considered. See also **Chapter 2.4.3 RF/IF Receiver**.

#### 2.4.5.1 PLL Dividers

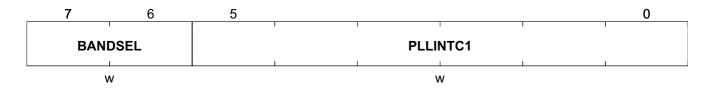

The divider chain consists of a band select divider 1/2/3, an I/Q-divider by 4 which provides an orthogonal 1st local oscillator signal for the first image reject mixer with the necessary high accuracy and a multi-modulus divider controlled by the Sigma-Delta Modulator. With the band select divider, the wanted frequency band is selected. Divide by 1 selects the 915 MHz and 868 MHz band, divide by 2 selects the 434 MHz band and divide by 3 selects the 315 MHz band. The ISM band selection is done via bit group BANDSEL in x\_PLLINTC1 register.

## 2.4.5.2 Digital Modulator

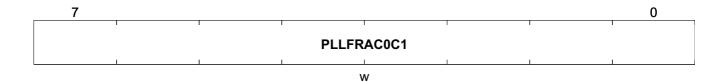

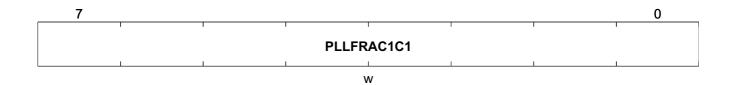

The 3<sup>rd</sup> order **Sigma-Delta Modulator (SDM)** has a 22 bit wide input word, however the LSB is always high, and is clocked by the XTAL oscillator. This determines the achievable frequency resolution.

The **Automatic Frequency Control Unit** filters the actual frequency offset from the FSK demodulator data and calculates the necessary correction of the divider factor to achieve the nominal IF center frequency.

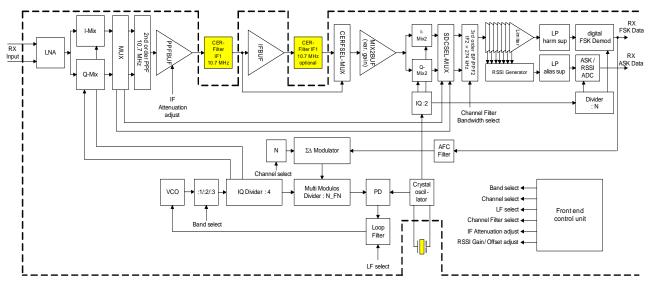

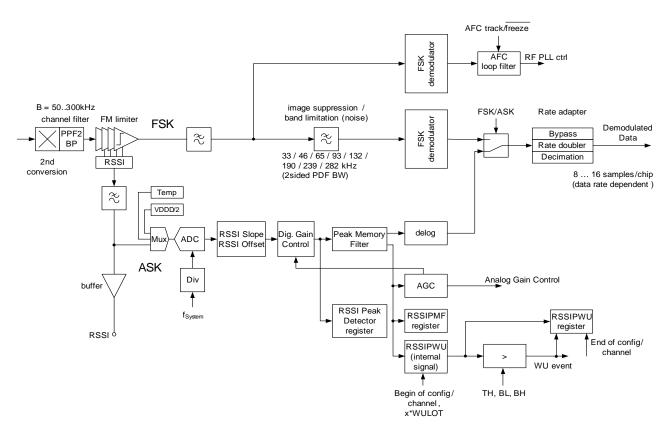

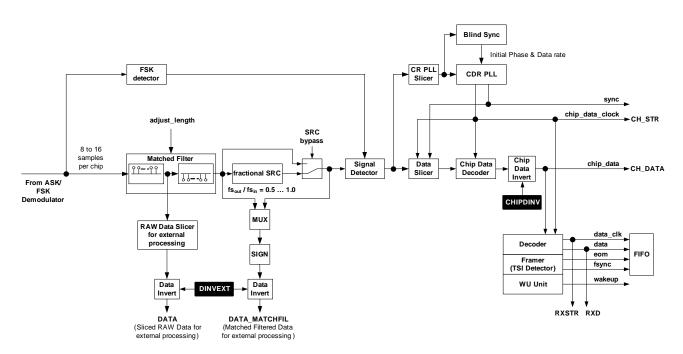

#### 2.4.6 ASK and FSK Demodulator

Figure 10 Functional Block Diagram ASK/FSK Demodulator

The IC comprises two separate demodulators for ASK and FSK.

After combining FSK and ASK data path, a sampling rate adaptation follows to meet an output oversampling between 8 and 16 samples per chip. Finally, an oversampling of 8 samples per chip can be achieved using a fractional sample rate converter (SRC) with linear interpolation (for further details see **Figure 15**).

#### 2.4.6.1 ASK Demodulator

The RSSI generator delivers a DC signal proportional to the applied input power at a logarithmic scale (dBm) and is also used as an ASK demodulator. Via a programmable anti-aliasing filter this signal is converted to the digital domain by means of a 10-bit ADC. For the AM demodulation a signal proportional to the linear power is required. Therefore a conversion from logarithmic scale to linear scale is necessary. This is done in the digital domain by a nonlinear filter together with an exponential function. The analog RSSI signal after the anti-aliasing filter is available at the RSSI pin via a buffer amplifier. To enable this buffer the SFR control bit RSSIMONEN must be set. The anti-aliasing filter can be by-passed for visualization on the RSSI pin (see AAFBYP control bit).

#### 2.4.6.2 FSK Demodulator

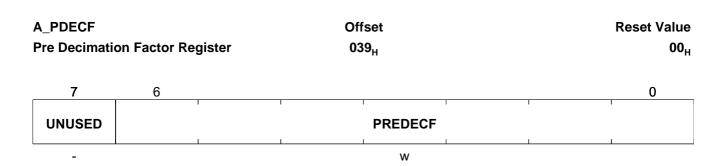

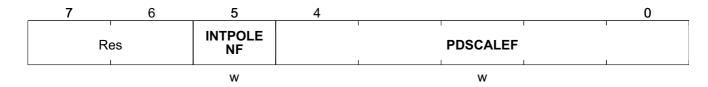

The limiter output signal, which has a constant amplitude over a wide range of the input signal, feeds the FSK demodulator. There is a configurable lowpass filter in front of the FSK demodulation to suppress the down conversion image and noise/limiter harmonics (FSK Pre-Demodulation Filter, PDF). This is realized as a 3<sup>rd</sup> order digital filter. The sampling rate after FSK demodulation is fixed and independent from the target data rate.

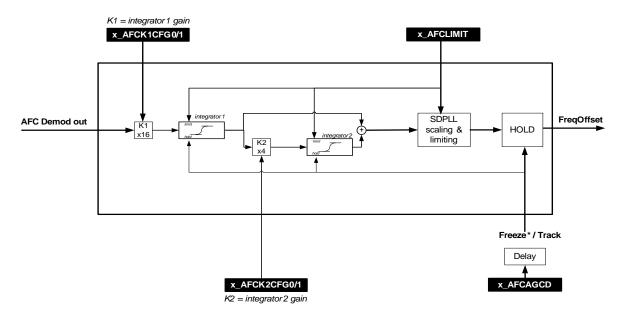

## 2.4.6.3 Automatic Frequency Control Unit (AFC)

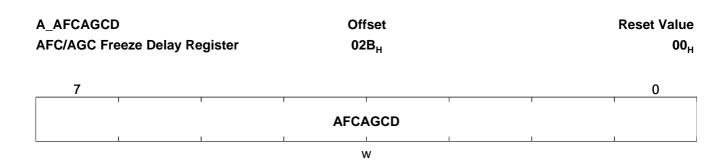

In front of the image suppression filter a second FSK demodulator is used to derive the control signal for the **Automatic Frequency Control Unit**, which is actually the DC value of the FSK demodulated signal. This makes the AFC loop independent from signal path filtering and allow so a wider frequency capture range of the AFC. The derivation of the AFC control signal is preferably done during the DC free preamble and is then frozen for the rest of the datagram.

Since the digital FSK demodulator determines the exact frequency offset between the received input frequency and the programmed input center frequency of the receiver, this offset can be corrected through the sigma delta control of the PLL. As shown in Figure 10, for AFC purposes a parallel demodulation path is implemented. This path does not contain the digital low pass filter (PDF, Pre-Demodulation Filter). The entire IF bandwidth, filtered by the analog bandpass filter only, is processed by the AFC demodulator.

There are two options for the active time of the AFC loop:

- 1. always on

- 2. active for a programmable time relative to a signal identification event (several options can be programmed in SFR).

In the latter case the AFC can either be started or frozen relative to the signal identification. After the active time the offset for the sigma-delta PLL (SD PLL) is frozen.

The programming of the active time is especially necessary in case the expected frame structure contains a gap (noise) between wake-up and payload in order to avoid the AFC from drifting.

AFC works both for FSK and ASK. In the latter case the AFC loop only regulates during ASK data = high.

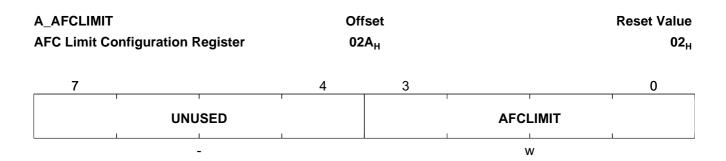

The maximum frequency offset generated by the AFC can be limited by means of the x\_AFCLIMIT register. This limit can be used to avoid the AFC from drifting in the presence of interferers or when no RF input signal is available (AFC wander). A maximum AFC limit of 42 kHz is recommended. AFC wandering needs to be kept in mind especially when using Run Mode Slave.

Figure 11 AFC Loop Filter (I-PI Filtering and Mapping)

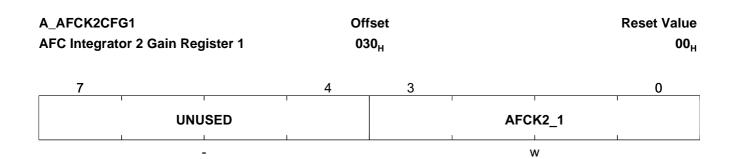

The bandwidth (and thus settling time) of the loop is programmed by means of the integrator gain coefficients K1 and K2 (x\_AFCK1CFG and x\_AFCK2CFG register).

K1 mainly determines the bandwidth. K2 influences the dynamics/damping (overshoot) - smaller K2 means smaller overshoot, but slower dynamics. The bandwidth of the AFC loop is approximately 1.3\*K1.

To avoid residual FM, limiting the AFC BW to  $1/20 \sim 1/40$  of the bit rate is suggested, therefore K1 must be set to approximately  $1/50 \sim 1/100$  of the bit rate. For most applications K2 can be set equal to K1 (overshoot is then <25%).

When very fast settling is necessary K1 and K2 can be increased up to bit rate/10, however, in this case approximately 1dB sensitivity loss is to be expected due to the AFC counteracting the input FSK signal.

**AFC limitation** at Local Oscillator (LO) frequencies at multiples of reference frequency (f\_xtal). When AFC is activated and AFC drives the wanted LO frequency over the integer limit of Sigma Delta (SD) modulator, the SD modulator stucks at frac=1.0 or frac=0.0 due to saturation. So when AFC can change the integer value for the LO (register x\_PLLINTC1) within the frequency range LO-frequency +/- AFC-limit, a change of the LO injection side or a smaller AFC-limit is recommended.

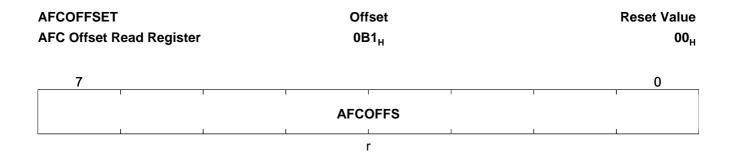

The frequency offset found by AFC (AFC loop filter output) can be readout via register AFCOFFSET, when AFC is activated. The value is in signed representation and has a frequency resolution of 2.68 kHz/digit. The output can be limited by the x\_AFCLIMIT register.

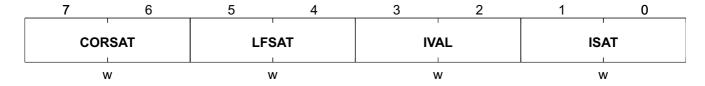

## 2.4.6.4 Digital Automatic Gain Control Unit (AGC)

Automatic Gain Control (AGC) is necessary mainly because of the limited dynamic range of the on-chip bandpass filter (BPF). The dynamic range reduces to less than 60dB in case of minimum BPF bandwidth.

AGC is used to cover the following cases:

- 1. ASK demodulation at large input signals

- 2. RSSI reading at large input signals

- 3. Improve IIP3 performance in either FSK or ASK mode

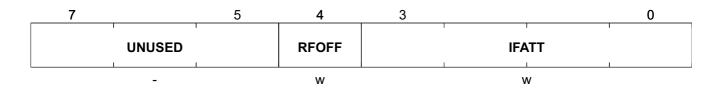

The 1<sup>st</sup> IF buffer (PPFBUF, see **Figure 3**) can be fine tuned "manually" by means of 4 bits thus optimizing the overall gain to the application (attenuation of 0dB to -12dB by means of IFATT0 to IFATT15 in DDC mode; SDC mode has lower IFATT range). This buffer allows the production spread of external components to be trimmed.

The gain of the 2<sup>nd</sup> IF path is set to three different values by means of an AGC algorithm. Depending on whether the receiver is used in single down conversion or in double down conversion mode the gain control in the 2<sup>nd</sup> IF path is either after the 2<sup>nd</sup> poly-phase network or in front of the 2<sup>nd</sup> mixer.

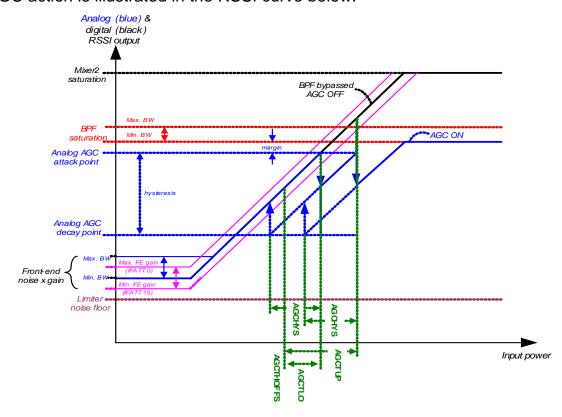

The AGC action is illustrated in the RSSI curve below:

Figure 12 Analog RSSI output curve with AGC action ON (blue) vs. OFF (black)

#### **Digital RSSI, AGC and Delog:**

In order to match the analog RSSI signal to the **digital RSSI** output a correction is necessary. It adds an offset (RSSIOFFS) and modifies the slope (RSSISLOPE) such that standardized AGC levels and an appropriate DELOG table can be applied.

Upon entering the **AGC unit** the digital RSSI signal is passed through a Peak Memory Filter (PMF). This filter has programmable up and down integration time constants (PMFUP, PMFDN) to set attack respectively decay time. The integration time for decay time must be significantly longer than the attack time in order to avoid the AGC interfering with the ASK modulation.

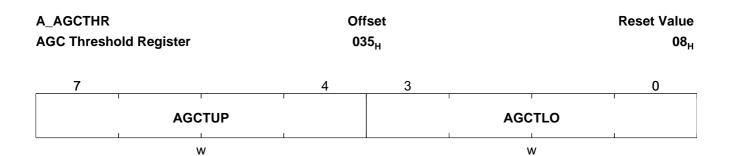

The integrator is followed by two digital Schmitt triggers with programmable thresholds (AGCTLO; AGCTUP) - one Schmitt trigger for each of the two attack thresholds (two digital AGC switching points). The hysteresis of the Schmitt triggers is programmable (AGCHYS) and sets the decay threshold. The Schmitt triggers control both the analog gain as well as the corresponding (programmable) digital gain correction (DGC).

The difference ("error") signal in the PMF is actually a normalized version of the modulation. This signal is then used as input for the **DELOG** table.

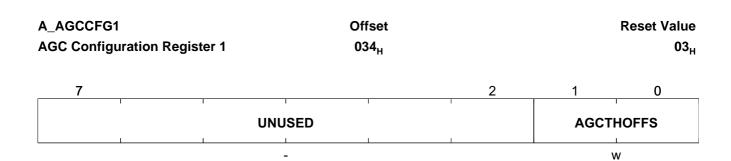

## **AGC threshold programming**

The SFR description for the AGC thresholds are in dBs. The first value to set is the AGC threshold offset in AGCTHOFFS.

This value is the offset relative to 0 input (no noise, no signal), which for the default setting of gain, and assuming typical insertion loss of matching network and ceramic filter, can be extrapolated to be approximately -143dBm.

In this case the default setting of the AGCTHOFFS of 63.9dB corresponds to an input power of approximately -79dBm (= -143dBm + 63.9dB).

The low (digital) AGC threshold is then -79 + 12.8dB (default AGCTLO) = -66dBm and the upper (digital) AGC threshold is -79 + 25.6 (default AGCTUP) = -53dBm.

Therefore a margin of about 6dB is indicated before a degradation of the linearity of the 2<sup>nd</sup> IF can be observed when using the 50kHz BPF or even about 16dB when using the 300kHz BPF.

The input power level at which the AGC switches back to maximum gain is -66dBm - 21.3dB (default AGCHYS) = -87dBm. This provides enough margin against the minimum sensitivity.

When AGC is activated, RSSI is untrimmed, IFATT <= 5.6dB and the same RSSI offset should be applied for all bandpass filter settings, then the settings in **Table 2** can be applied, where a small reduction of the RSSI input range can be observed.

Table 2 AGC Settings 1

AGC Threshold Hysteresis = 21.3 dB

AGC Digital RSSI Gain Correction = 15.5 dB

| BPF     | RSSI Offset<br>Compensation<br>(untrimmed) 1) | AGC<br>Threshold<br>Offset | AGC<br>Threshold<br>Low | AGC<br>Threshold<br>Up | RSSI Input<br>Range<br>Reduction |

|---------|-----------------------------------------------|----------------------------|-------------------------|------------------------|----------------------------------|

| 300 kHz | 32                                            | 63.9 dB                    | 8                       | 4                      | 5 dB                             |

| 200 kHz | 32                                            | 63.9 dB                    | 6                       | 2                      | 5 dB                             |

| 125 kHz | 32                                            | 63.9 dB                    | 5                       | 0                      | 5 dB                             |

| 80 kHz  | 32                                            | 51.1 dB                    | 11                      | 6                      | 2.8 dB                           |

| 50 kHz  | 32                                            | 51.1 dB                    | 9                       | 5                      | 0 dB                             |

<sup>1)</sup> Note: This value needs to be used for calculating the register value

For the full RSSI input range, the values in Table 3 can be applied.

Table 3 AGC Settings 2

AGC Threshold Hysteresis = 21.3 dB

AGC Digital RSSI Gain Correction = 15.5 dB

| BPF     | RSSI Offset<br>Compensation<br>(untrimmed) 1) | AGC<br>Threshold<br>Offset | AGC<br>Threshold<br>Low | AGC<br>Threshold<br>Up |

|---------|-----------------------------------------------|----------------------------|-------------------------|------------------------|

| 300 kHz | -18                                           | 63.9 dB                    | 5                       | 1                      |

| 200 kHz | -18                                           | 51.1 dB                    | 11                      | 7                      |

| 125 kHz | -18                                           | 51.1 dB                    | 10                      | 5                      |

| 80 kHz  | 4                                             | 51.1 dB                    | 9                       | 5                      |

| 50 kHz  | 32                                            | 51.1 dB                    | 9                       | 5                      |

<sup>1)</sup> Note: This value needs to be used for calculating the register value

#### Attack and Decay coefficients PMF-UP & PMF-DOWN:

The settling time of the loop is determined by means of the integrator gain coefficients PMFUP and PMFDN, which need to be calculated from the wanted attack and decay times.

The ADC is running at a fixed sampling frequency of 274kHz. Therefore the integrator is integrating with PMFUP\*274k per second, i.e. time constant is 1/(PMFUP\*274k). The attack times are typically 16 times faster than the decay times.

Typical calculation of the coefficients by means of an example:

- PMFUP = 2^-round( ln(AttTime / BitRate \* 274kHz) / ln(2) )

- PMFDN = 2^-round( In(DecTime / BitRate \* 274kHz) / In(2) ) / PMFUP

where AttTime, DecTime = attack, decay time in number of bits

Note: PMFDN = overall\_PMFDN / PMFUP

#### Example:

BitRate = 2kbps

AttTime = 0.1 bits

$=> PMFUP = 2^-round(ln(0.1bit/2kbps*274kHz)/ln(2)) = 2^-round(3.8) = 2^-4$

DecTime = 2 bits

$=> PMFDN = 2^-round(ln(2bit/2kbps*274kHz)/ln(2))/PMFUP = 2^-round(8.1)/2^-4 = 2^-4$

Note: In case of ASK with large modulation index the attack time (PMFUP) can be up to a factor 2 slower due to the fact that the ASK signal has a duty cycle of 50% - during the ASK low duration the integrator is actually slightly discharged due to the decay set by PMFDN.

The AGC start and freeze times are programmable. The same conditions can be used as in the corresponding AFC section above. They will however, be programmed in separate SFR registers.

#### 2.4.6.5 Analog to Digital Converter (ADC)

In front of the AD converter there is a multiplexer so that also temperature and VDDD can be measured (see **Figure 10**).

The default value of the ADC-MUX is RSSI (register ADCINSEL: 000 for RSSI; 001 for Temperature; 010 for VDDD/2).

After switching ADC-MUX to a value other than RSSI in SLEEP Mode, the internal references are activated and this ADC start-up lasts 100µs. So after this ADC start-up time the readout measurements may begin. The chip stays in this mode until reconfiguration of register ADCINSEL to setting RSSI. However, it is recommended to measure temperature during SLEEP mode (This is also valid for VDDD).

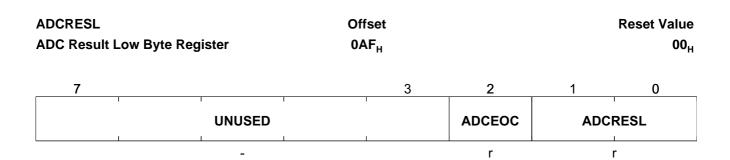

Readout of the 10-bit ADC has to be done via ADCRESH register (the lower 2 bits in ADCRESL register can be inconsistent and should not be used).

Typical the ADC refresh rate is  $3.7 \,\mu s$ . Time duration between two ADC readouts has to be at least  $3.7 \,\mu s$ , so this is already achieved due to the maximum SPI rate (16 bit for SPI command and address last  $8\mu s$  at an SPI rate of 2MBit/s). The EOC bit (end of conversion) indicates a successful conversion additionally. Repetition of the readout measurement for several times is for averaging purpose.

The input voltage of the ADC is in the range of 1 .. 2 V. Therefore VDDD/2 (= 1.65 V typical) is used to monitor VDDD.

Further details on the measurement and calibration procedure for temperature and VDDD can be taken from the corresponding application note.

Data Sheet 34 V1.0, 2010-02-19

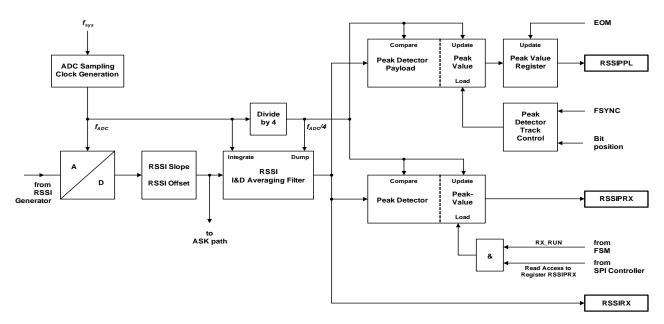

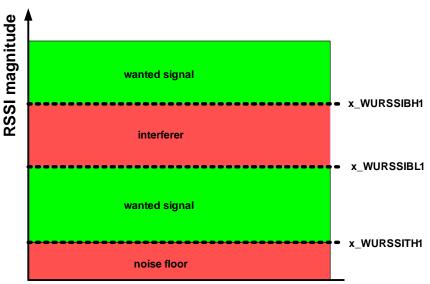

#### 2.4.7 RSSI Peak Detector

The IC possesses several digital RSSI peak level detectors. The RSSI level is averaged over 4 samples before it is fed to any of the peak detectors. This prevents the evaluated peak values to be dominated by single noise peaks.

Figure 13 Peak Detector Unit

**Peak Detector Payload** is used to measure the input signal power of a received and accepted data telegram. It is read via SFR RSSIPPL.

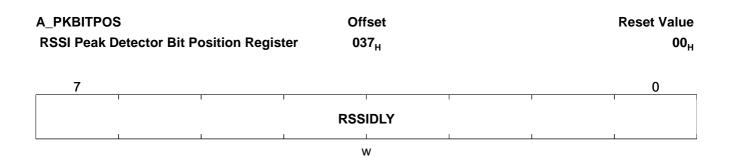

Observation of the RSSI signal starts at the detection of a TSI (FSYNC) and ends with the detection of EOM. The internal RSSIPPL value is cleared after FSYNC. The evaluated RSSI peak level RSSIPPL is transferred to the RSSIPPL register at EOM. Starting the observation of the RSSI level can be delayed by a selectable number of data bits and is controlled by the register x\_PKBITPOS. A latency in the generation of FSYNC and EOM of approx. 2..3 bits in relation to the contents of the Peak Detector must be considered. Within the boundaries described, the register RSSIPPL always contains the peak value of the last completely received data telegram. The register RSSIPPL is reset to 0 at power up reset only.

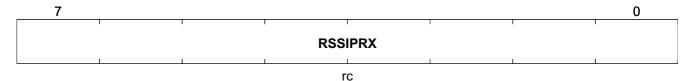

**Peak Detector** is used to measure RSSI independent of a data transfer and to digitally trim RSSI. It is read via SFR RSSIPRX.

Observation of the RSSI signal is active whenever the RX\_RUN signal is high. The RSSIPRX register is refreshed and the Peak Detector is reset after every read access to RSSIPRX.

It may be required to read RSSIPRX twice to obtain the required result. This is because, for example, during a trim procedure in which the input signal power is reduced, after

reading RSSIPRX, the peak detector will still hold the higher RSSI level. After reading RSSIPRX the lower RSSI level is loaded into the Peak Detector and can be read by reading RSSIPRX again.

Register RSSIPRX should not be read-out faster than 41µs in case AGC is ON (as register value would not represent the actual, but a lower value).

When the RX\_RUN signal is inactive, a read access has no influence to the peak detector value. The register RSSIPRX is reset to 0 at power up reset.

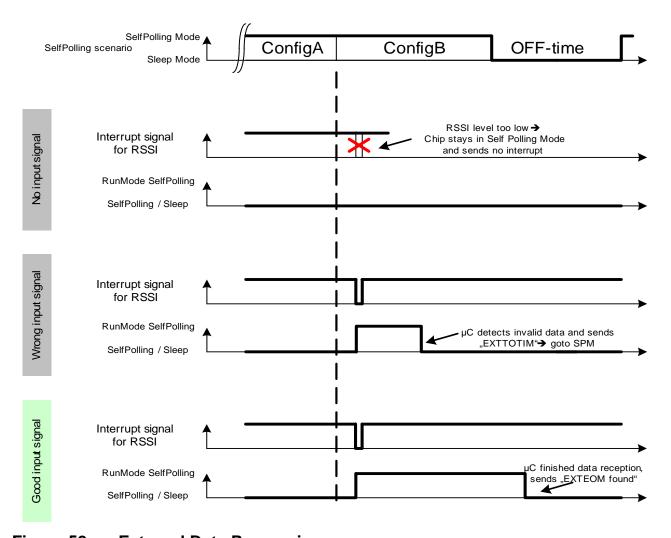

**Peak Detector Wake-Up** RSSIPWU (see **Figure 10**) is used to measure the input signal power during Wake-Up search. The internal signal RSSIPWU gets initialized to 0 at start of the first observation time window at the beginning of each configuration. The peak value of this signal is tracked during Wake-Up search.

In case of a Wake-Up, the actual peak value is written in the RSSIPWU register. Even in case no Wake-Up occurred, actual peak value is written in the RSSIPWU register at the end of the actual configuration of the Self Polling period. So if no Wake-Up occurred, then the RSSIPWU register contains the peak value of the last configuration of the Self Polling period, even in a Multi-Configuration setup. This functionality can be used to track RSSI during unsuccessful Wake-Up search due to no input signal or due to blocking RSSI detection.

For further details please refer to Chapter 2.4.8.5 Wake-Up Generator and Chapter 2.6.2 Polling Timer Unit.

<sup>\*1</sup> Computation Delay due to filtering and signal calculation.

Figure 14 Peak Detector Behavior

## **Recommended Digital Trimming Procedure**

- Download configuration file (Run Mode Slave; RSSISLOPE, RSSIOFFS set to default, i.e. RSSISLOPE=1, RSSIOFFS=0)

- Turn off AGC (AGCSTART=0) and set gain to AGCGAIN=0

- Apply P<sub>IN1</sub> = -85 dBm RF input signal

- Read RSSIRX eleven times (minimum 10 ms in-between readings), use average of last ten readings (always), store as RSSIM1

- Apply  $P_{IN2} = -65$  dBm RF input signal

- Read RSSIRX eleven times (minimum 10 ms in-between readings), use average of last ten readings (always), store as RSSIM2

- Calculate measured RSSI slope SLOPEM=(RSSIM2-RSSIM1)/(P<sub>IN2</sub>-P<sub>IN1</sub>)

- Adjust RSSISLOPE for required RSSI slope SLOPER as follows: RSSISLOPE=SLOPER/SLOPEM

- Adjust RSSIOFFS for required value RSSIR2 at P<sub>IN2</sub> as follows: RSSIOFFS=(RSSIR2-RSSIM2)+(SLOPEM-SLOPER)\*P<sub>IN2</sub>

- The new values for RSSISLOPE and RSSIOFFS have to be added to the configuration!

#### Notes:

- 1. The upper RF input level must stay well below the saturation level of the receiver (see Chapter 2.4.6.4 Digital Automatic Gain Control Unit (AGC))

- 2. The lower RF input level must stay well above the noise level of the receiver

- 3. If IF Attenuation is trimmed, this has to be done before trimming of RSSI

- 4. If RSSI needs to be trimmed in a higher input power range the AGCGAIN must be set accordingly

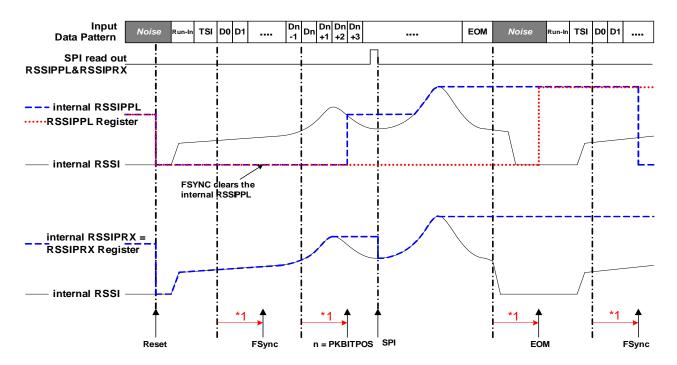

# 2.4.8 Digital Baseband (DBB) Receiver

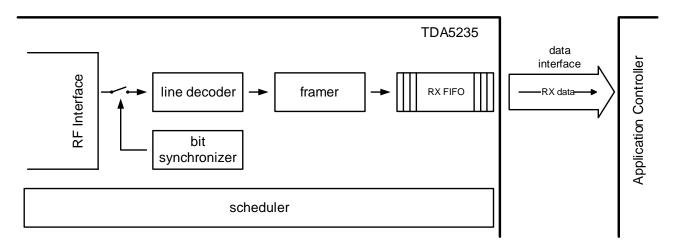

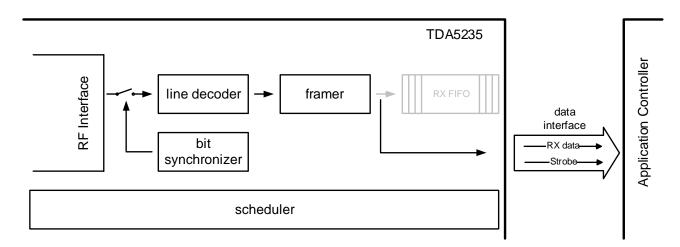

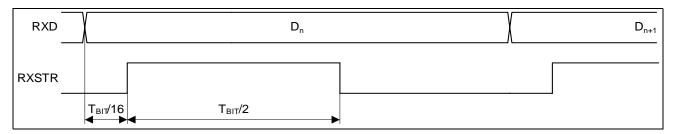

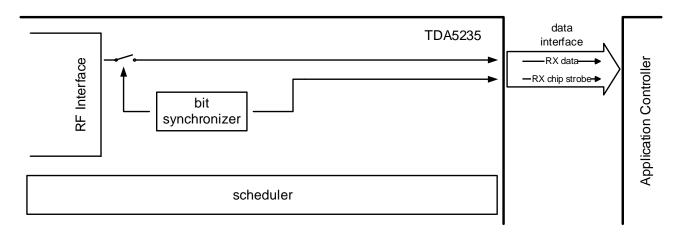

Figure 15 Functional Block Diagram Digital Baseband Receiver

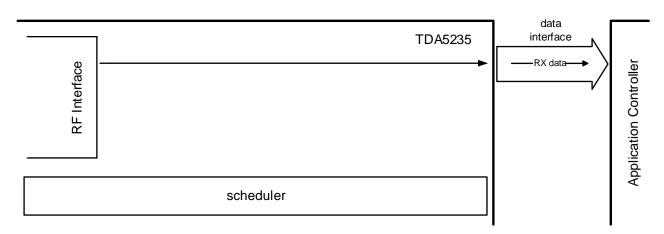

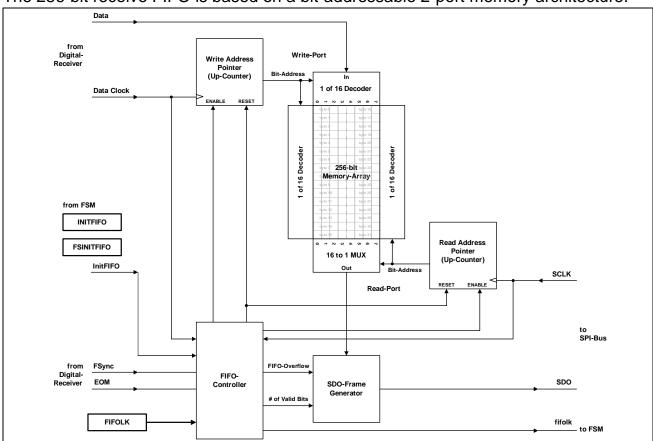

The digital baseband receiver comprises a matched data filter, a clock and data recovery, a data slicer, a line decoder, a wake-up generator, a frame synchronization and a data FIFO. The recovered data and clock signals are accessible via 2 separate pins. The FIFO data buffer is accessible via the SPI bus interface.

# 2.4.8.1 Data Filter and Signal Detection

The data filter is a matched filter (*MF*). The frequency response of a matched filter has ideally the same shape as the power spectral density (*PSD*) of the originally transmitted signal, therefore the signal-to-noise ratio (*SNR*) at the output of the matched filter becomes maximum. The input sampling rate of the baseband receiver has to be between 8 and 16 samples per chip. The oversampling factor within this range is depending on the data rate (see **Figure 10**). The MF has to be adjusted accordingly to this oversampling. After the MF a fractional sample rate converter (SRC) is applied using linear interpolation. Depending on the data rate decimation is adjusted within the range 1...2. Finally, at the output of the fractional SRC the sampling rate is adjusted to 8 samples per chip for further processing.

To distinguish whether the incoming signal is really a signal or only noise adequate detectors for ASK and FSK are built in.

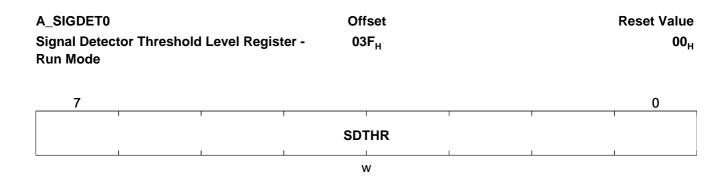

## Signal and Noise Detector

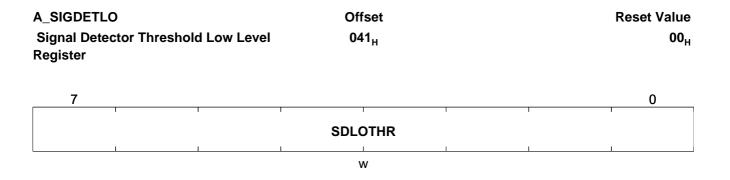

The Signal Detector decides between acceptable and unacceptable data (e.g. noise). This decision is taken by comparing the signal power of the actually received data (register SPWR) with a configurable threshold level (registers x\_SIGDET0/1), which must be evaluated. In case the actual signal power is above the threshold, acceptable data has been detected.

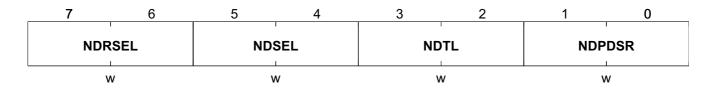

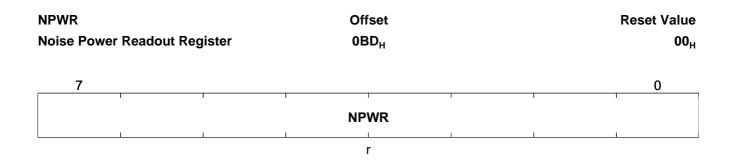

To decide in case of FSK whether there is a data signal or simply noise at the output of the rate adapter, there is a Noise Detector implemented. The principle is based on a power measurement of the demodulated signal. The current noise power is stored in the NPWR register and is updated at every SPI controller access. The Noise Detector is useful if data signal is transmitted with small FSK deviations. In case the current noise power (register NPWR) is below the configurable threshold (register x\_NDTHRES), a data signal has been detected.

The Signal Recognition mode must be configured based on whether ASK or FSK modulation is used. Signal Recognition can be a combination of Signal Detector and Noise Detector:

- Signal Detector (=Squelch) only (related registers: x\_SIGDET0, x\_SIGDET1 and SPWR). This mode is generally used for ASK and recommended for FSK.

- Noise Detector only (related registers: x\_NDTHRES and NPWR).

- Signal and Noise Detector simultaneously.

- Signal and Noise Detector simultaneously, but the FSK noise detect signal is valid only if the x\_SIGDETLO threshold is exceeded. This is the recommended FSK mode, if minimum FSK deviation is not sufficient to use Signal Detector only.

Signal Recognition can also be used as Wake-up on Level criterion (see Chapter 2.4.8.5).

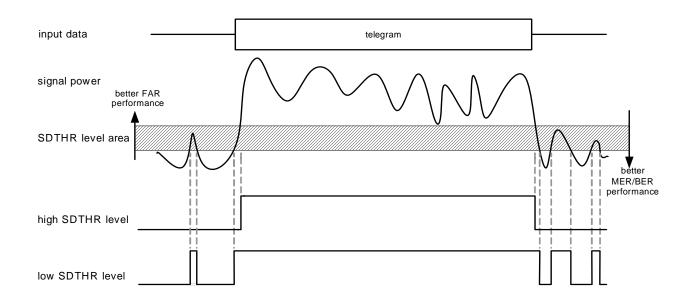

Figure 16 shows the system characteristics to consider in choosing the best Signal Detector level. On the one hand, a higher SIGDET threshold level must be set for achieving good FAR (False Alarm Rate) performance, but then the MER/BER (Message Error Rate/Bit Error Rate) performance will decrease. On the other hand, the MER/BER performance can be increased by setting smaller SIGDET threshold levels but then the FAR performance will worsen.

Data Sheet 39 V1.0, 2010-02-19

Figure 16 Signal Detector Threshold Level

# **Quick Procedure to Determine Signal and Noise Detector Thresholds Preparation**

A setup is required with original RF hardware as in the final application. The values of SPWR and NPWR can be read via the final application.

A complete configuration file using right modulation, data rate and Run Mode Slave, must be prepared and downloaded to the TDA5235.

# Signal Detector Threshold for ASK

Take 500 readings of SPWR (50 are also possible, but this leads to less accurate results) with no RF input signal applied (=noise only). Calculate average and Standard Deviation. Signal Detector Threshold is average plus 2 times the Standard Deviation. To load the x\_SIGDET0/1 register the calculated value must be rounded and converted to hexadecimals. For a final application, the Signal Detector Threshold should be varied to optimize the false alarm rate and the sensitivity.

# Signal and Noise Detector Thresholds for FSK

Signal Detector Threshold

Do 500 (50) readings of SPWR with no RF input signal applied (=noise only). Calculate average and Standard Deviation. Signal Detector Threshold is average plus 2 times the Standard Deviation. Of course this value has to be rounded and converted to

hexadecimals. For a final application the Signal Detector Threshold should be varied to optimize the false alarm rate and the sensitivity.

## Verification if Squelch only is possible

Apply a bit pattern (e.g. PRBS9) with correct data rate at about -80 dBm input signal power and minimum FSK deviation to the RF input. Do 500 (50) readings of SPWR, calculate average minus three times the Standard Deviation. This value should be higher than the calculated Signal Detector Threshold calculated above. If this is not the case, Signal Detector AND Noise Detector must be used.

#### Noise Detector Threshold

Do 500 (50) readings of NPWR with no RF input signal applied (=noise only). Calculate average and Standard Deviation. Noise Detector Threshold is average minus the Standard Deviation. Round this value and convert it to hexadecimals. For a final application, the Noise Detector Threshold should be varied to optimize false alarm rate and sensitivity.

## Signal Detector Low Threshold

The Signal Detector Low Threshold is always required in combination with the Noise Detector.

Set register bit SDLORE to 1 and set bit group SDLORSEL to 00. Apply a bit pattern (e.g. PRBS9) at correct data rate at about -80 dBm input signal power and minimum FSK deviation to the RF input. Do 500 (50) readings of SPWR, calculate average. If average is larger than 200 dec (=0xC8), SDLORSEL has to be increased to the next larger value until average is smaller than 200 dec.  $x_SIGDETLO = 0.8 *$  (average - 3 \* Standard Deviation). Set register SDLORE back to 0. The last setting of bit group SDLORSEL must also be used for configuration!

#### Verification

Threshold settings should be verified by testing receiver sensitivity over the input frequency range, with a step size of 100Hz, at minimum FSK deviation with all combinations of minimum and maximum data rate and duty cycle.

Further detailed information can be taken from the corresponding Application Note.

Data Sheet 41 V1.0, 2010-02-19

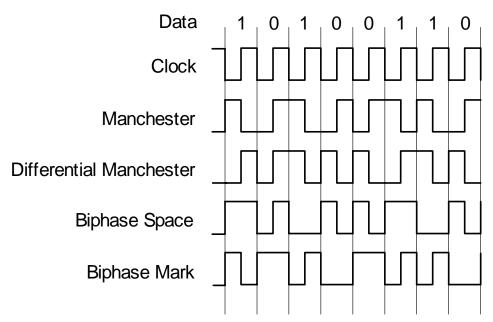

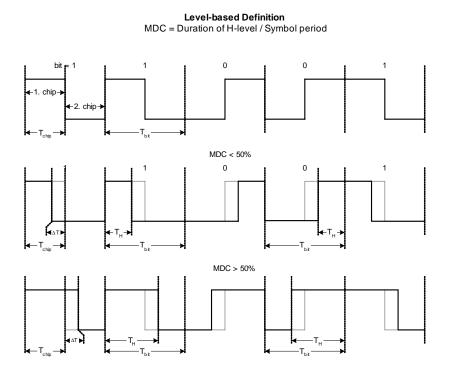

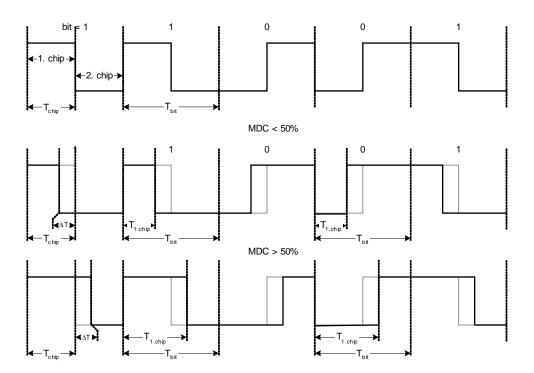

# 2.4.8.2 Encoding Modes

The IC supports the following Bi-phase encodings:

- Manchester code

- Differential Manchester code

- Bi-phase space code

- Bi-phase mark code

The encoding mode is set and enabled by bit group CODE in x\_DIGRXC configuration register.

Figure 17 Coding Schemes

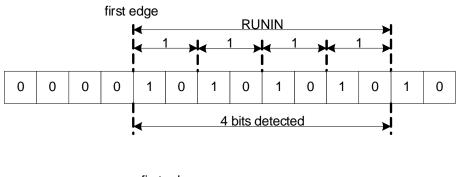

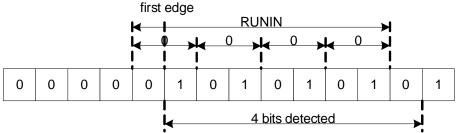

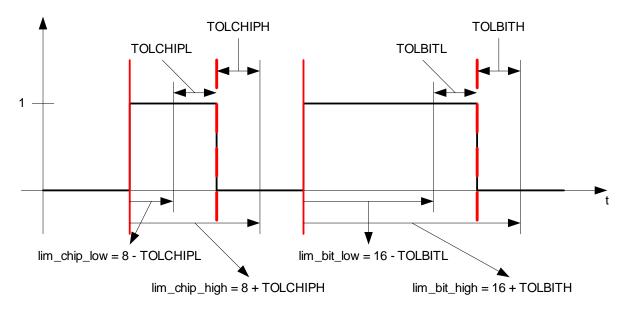

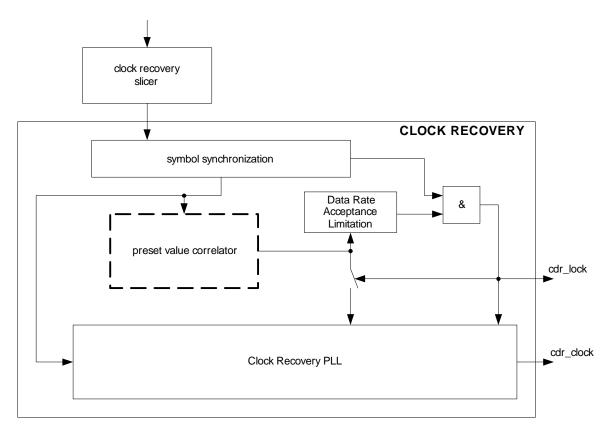

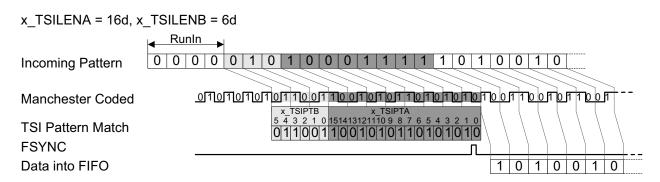

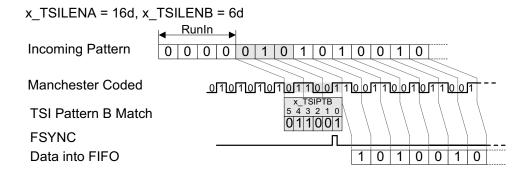

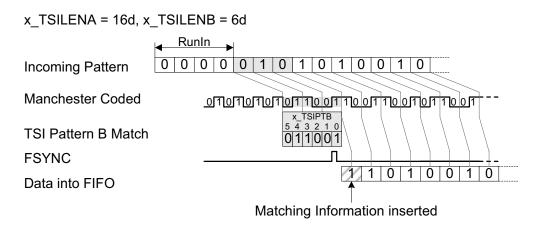

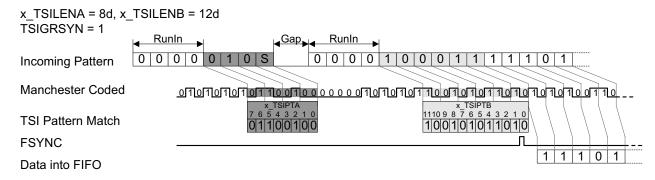

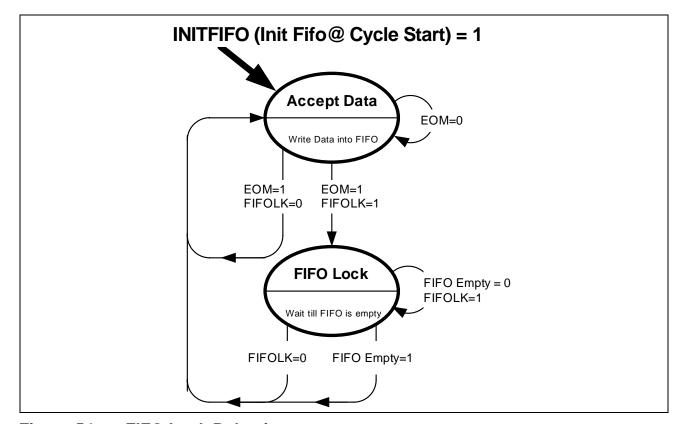

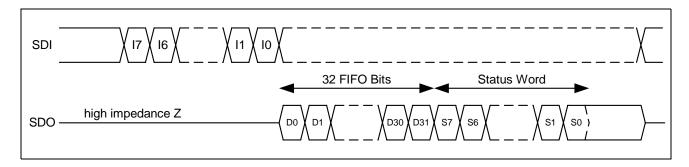

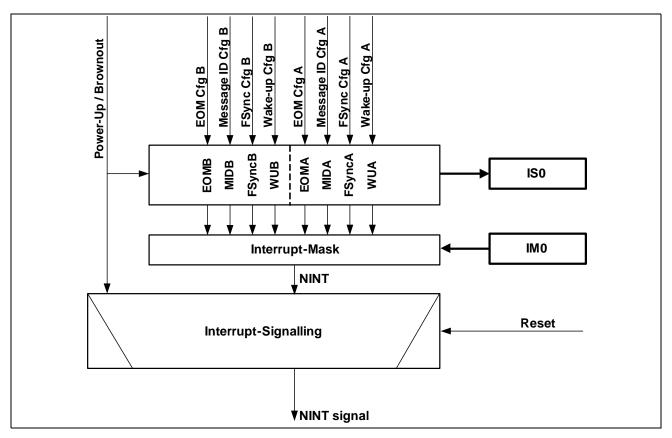

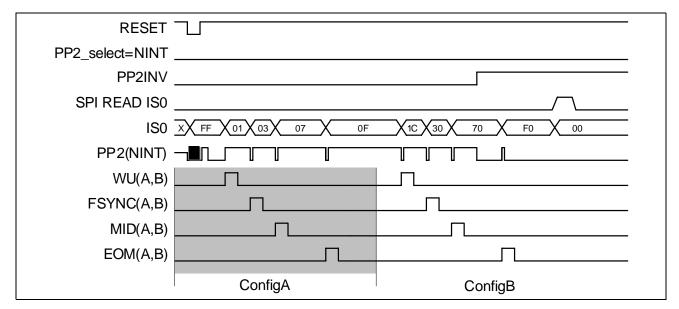

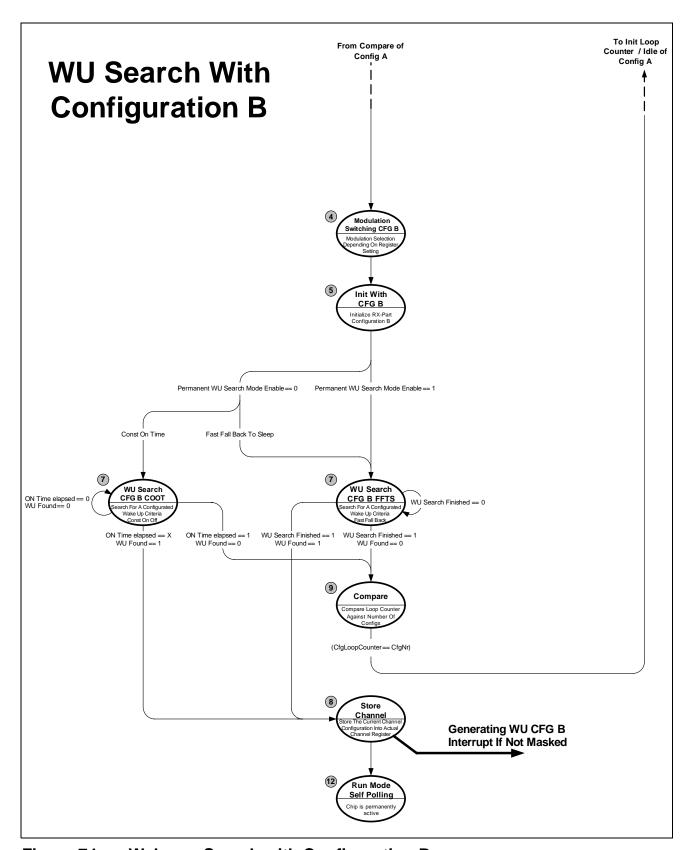

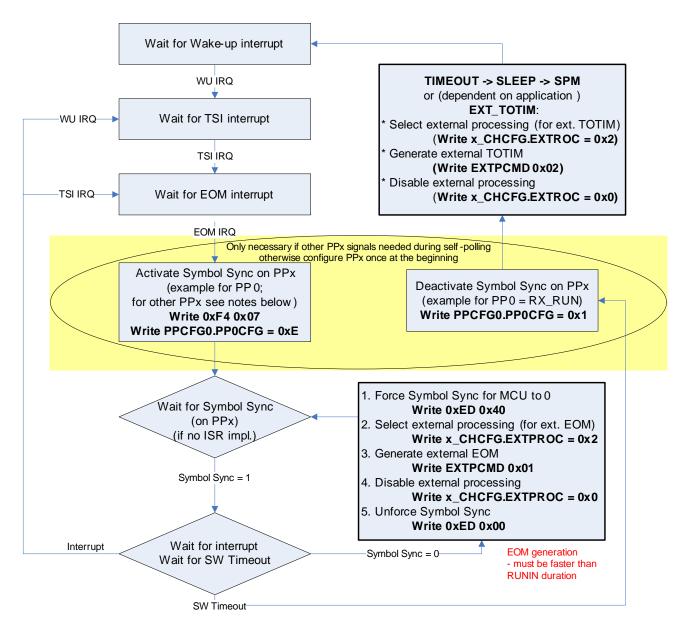

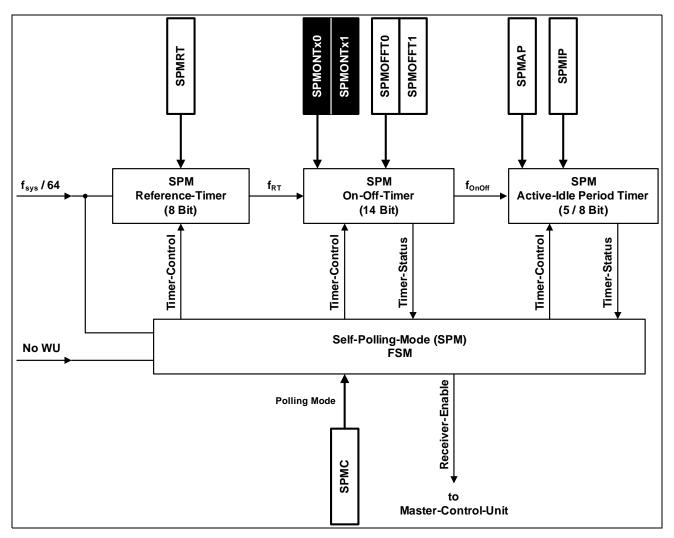

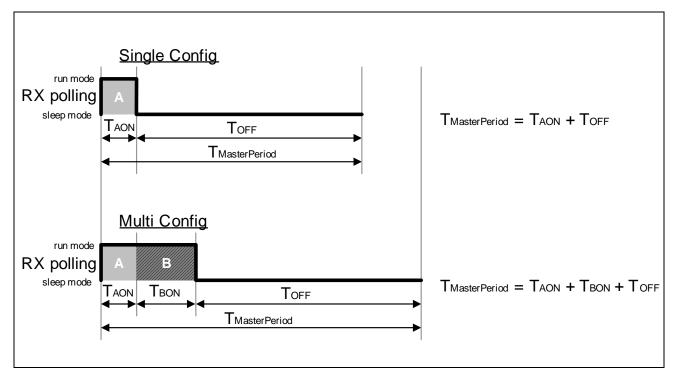

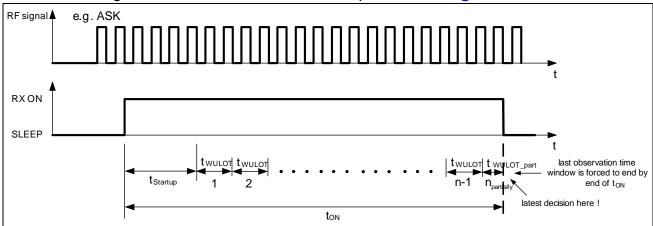

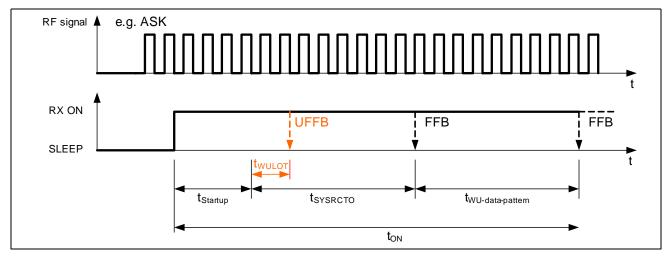

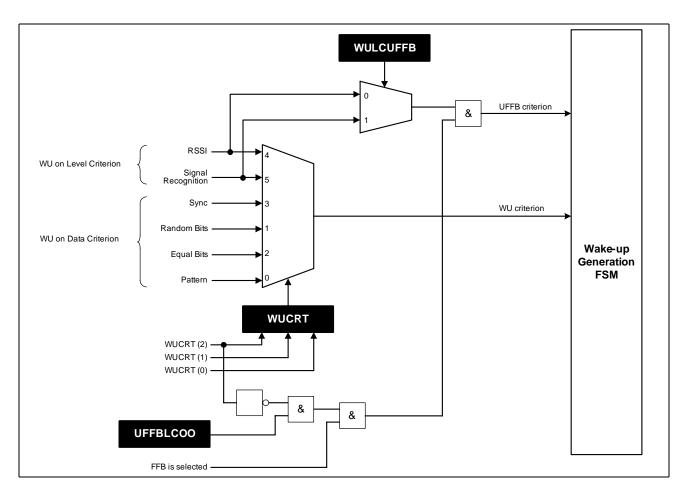

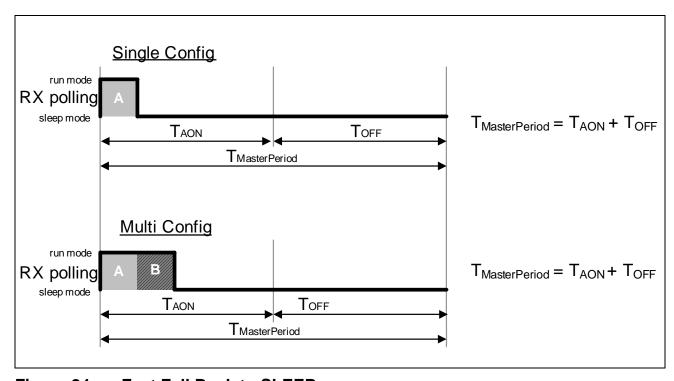

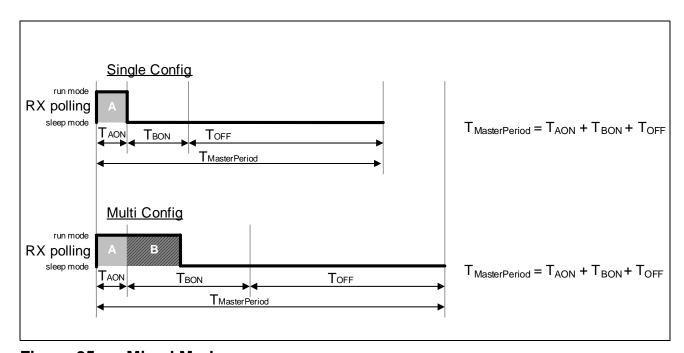

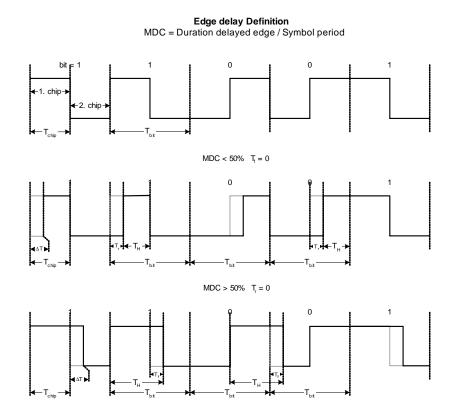

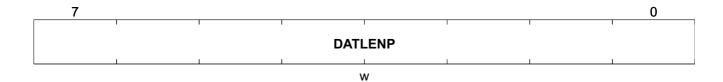

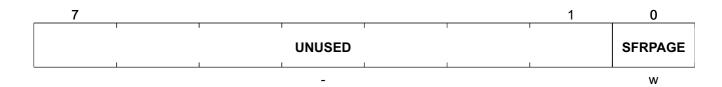

The encoding modes Inverted Manchester and Inverted Differential Manchester can also be decoded internally by usage of CHIPDINV bit in x\_DIGRXC register (see Figure 15).