### DUAL BIDIRECTIONAL THYRISTOR OVERVOLTAGE PROTECTORS

Copyright © 2000, Power Innovations Limited, UK

NOVEMBER 1997 - REVISED SEPTEMBER 2000

#### INSULATION OVERVOLTAGE PROTECTION

**Ion-Implanted Breakdown Region** Precise and Stable Voltage Low Voltage Overshoot under Surge

| TERMINALS | 6 | T &G     | , R&G                  | Т                     | & R                    |

|-----------|---|----------|------------------------|-----------------------|------------------------|

| DEVICE    | V | DRM<br>V | V <sub>(BO)</sub><br>V | V <sub>DRM</sub><br>V | V <sub>(BO)</sub><br>V |

| '3600     |   | 420      | 600                    | 840                   | 1200                   |

| '3700     |   | 500      | 700                    | 1000                  | 1400                   |

| WAVE SHAPE | STANDARD      | I <sub>TSP</sub><br>A |

|------------|---------------|-----------------------|

| 2/10       | GR-1089-CORE  | 190                   |

| 8/20       | IEC 61000-4-5 | 175                   |

| 10/160     | FCC Part 68   | 110                   |

| 10/700     | FCC Part 68   | 70                    |

| 10/700     | ITU-T K.20/21 | 70                    |

| 10/560     | FCC Part 68   | 50                    |

| 10/1000    | GR-1089-CORE  | 45                    |

MDXXAGA

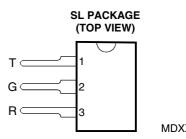

device symbol

Terminals T, R and G correspond to the alternative line designators of A, B and C

#### description

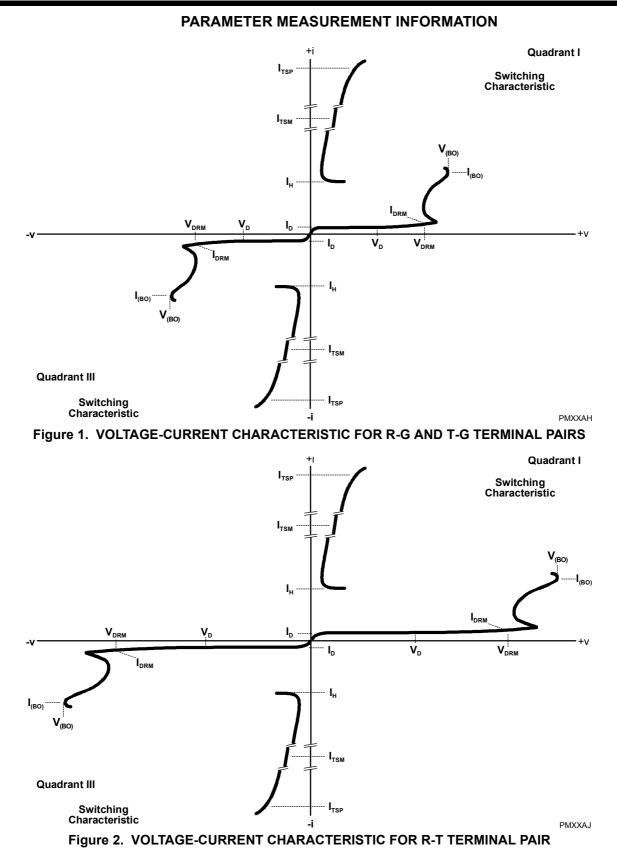

These devices are designed to limit overvoltages between systems and so protect their insulation. A single device can be used in two ways; as a 3-point protector or as a 2-point protector. In the 3-point mode, the G terminal is connected to the system protective ground and the R and T terminals are connected to the two conductors being protected. For the TISP3600F3, each conductor will have its voltage limited to ±600 V from the protective ground. The maximum inter-conductor voltage will be limited to ±1200 V.

In the 2-point mode, only the outer R and T terminals are connected and the G terminal is unconnected. The TISP3700F3 limits the voltage between the two connection nodes to ±1400 V with voltage limiting beginning above ±1000 V. Two TISP3700F3 devices connected in series would allow insulation testing to ±2000 V (1400 Vrms).

| HOW | то | ORDER |  |

|-----|----|-------|--|

|     |    |       |  |

| Ī | DEVICE     | PACKAGE            | CARRIER | ORDER #      |

|---|------------|--------------------|---------|--------------|

| Ī | TISP3600F3 | SL, Single-in-line | TUBE    | TISP3600F3SL |

|   | TISP3700F3 | SL, Single-in-line | TUBE    | TISP3700F3SL |

The protector consists of two symmetrical voltage-triggered bidirectional thyristors with a common connection. Overvoltages are normally caused by a.c. power system or lightning flash disturbances which are coupled on to the system. These overvoltages are initially clipped by breakdown clamping until the voltage rises to the breakover level, which causes the device to crowbar into a low-voltage on state. This low-voltage on state causes the current resulting from the overvoltage to be safely diverted through the device. The high crowbar holding current prevents d.c. latchup as the diverted current subsides.

The TISP3x00F3 is guaranteed to voltage limit and withstand the listed international lightning surges in both polarities.

#### PRODUCT INFORMATION

Information is current as of publication date. Products conform to specifications in accordance with the terms of Power Innovations standard warranty. Production processing does not necessarily include testing of all parameters.

NOVEMBER 1997 - REVISED SEPTEMBER 2000

### absolute maximum ratings, T<sub>A</sub> = 25 °C (unless otherwise noted)

| RATING                                                                                   |                                                     | SYMBOL           | VALUE          | UNIT |

|------------------------------------------------------------------------------------------|-----------------------------------------------------|------------------|----------------|------|

| Repetitive peak off-state voltage, (R-G or T-G value)                                    | TISP3600F3<br>TISP3700F3                            | V <sub>DRM</sub> | ± 420<br>± 500 | v    |

| Non-repetitive peak on-state pulse current (see Notes 1 and 2)                           |                                                     |                  |                |      |

| 2/10 (Telcordia GR-1089-CORE, 2/10 voltage wave shape)                                   |                                                     |                  | 190            |      |

| 1/20 (ITU-T K.22, 1.2/50 voltage wave shape, 25 $\Omega$ resistor)                       |                                                     |                  | 100            |      |

| 8/20 (IEC 61000-4-5, combination wave generator, 1.2/50 voltage wave s                   | shape)                                              |                  | 175            |      |

| 10/160 (FCC Part 68, 10/160 voltage wave shape)                                          |                                                     | IPPSM            | 110            | А    |

| 4/250 (ITU-T K.20/21, 10/700 voltage wave shape, simultaneous)                           |                                                     |                  | 95             | A    |

| 5/310 (ITU-T K.20/21, 10/700 voltage wave shape, single)                                 |                                                     |                  | 70             |      |

| 5/320 (FCC Part 68, 9/720 voltage wave shape, single)                                    | 320 (FCC Part 68, 9/720 voltage wave shape, single) |                  | 70             |      |

| 10/560 (FCC Part 68, 10/560 voltage wave shape)                                          |                                                     |                  | 50             |      |

| 10/1000 (Telcordia GR-1089-CORE, 10/1000 voltage wave shape)                             |                                                     |                  | 45             |      |

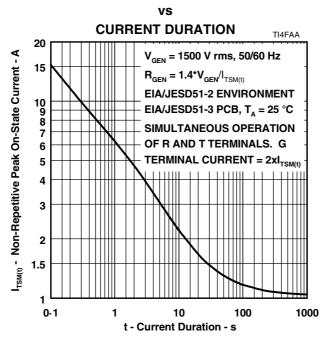

| Non-repetitive peak on-state current (see Notes 1 and 2)                                 |                                                     | ITSM             | C C            | •    |

| 50/60 Hz, 1 s                                                                            |                                                     |                  | 6              | A    |

| Initial rate of rise of on-state current, Linear current ramp, Maximum ramp value < 38 A |                                                     |                  | 250            | A/µs |

| Junction temperature                                                                     |                                                     |                  | -40 to +150    | °C   |

| Storage temperature range                                                                |                                                     | T <sub>stg</sub> | -65 to +150    | °C   |

NOTES: 1. Initially the TISP must be in thermal equilibrium with  $T_J = 25$  °C.

2. These non-repetitive rated currents are peak values of either polarirty. The rated current values may be applied to the R or T terminals. Additionally, both R and T terminals may have their rated current values applied simultaneously (in this case the G terminal return current will be the sum of the currents applied to the R and T terminals). The surge may be repeated after the TISP returns to its initial conditions.

### recommended operating conditions

|        |                                                             | MIN | ТҮР | MAX | UNIT |

|--------|-------------------------------------------------------------|-----|-----|-----|------|

|        | Series resistor for GR-1089-CORE first-level surge survival | 15  |     |     |      |

|        | Series resistor for ITU-T recommendation K.20 and K.21      | 0   |     |     | 0    |

| R1, R2 | Series resistor for FCC Part 68 9/720 survival              | 0   |     |     | Ω    |

|        | Series resistor for FCC Part 68 10/160, 10/560 survival     | 10  |     |     |      |

### electrical characteristics for the T and R terminals, $T_A = 25^{\circ}C$

|                   | PARAMETER                                  | TEST CONDITIONS                                                     |                          | MIN | TYP   | MAX            | UNIT  |

|-------------------|--------------------------------------------|---------------------------------------------------------------------|--------------------------|-----|-------|----------------|-------|

| I <sub>DRM</sub>  | Repetitive peak off-state current          | $V_{D} = \pm 2V_{DRM}$                                              |                          |     |       | ±10            | μA    |

| V <sub>(BO)</sub> | Breakover voltage                          | dv/dt = $\pm$ 700 V/ms, R <sub>SOURCE</sub> = 300 $\Omega$          | TISP3600F3<br>TISP3700F3 |     |       | ±1200<br>±1400 | V     |

| I <sub>(BO)</sub> | Breakover current                          | dv/dt = $\pm$ 700 V/ms, R <sub>SOURCE</sub> = 300 $\Omega$          |                          |     | ±0.1  |                | А     |

| Ι <sub>Η</sub>    | Holding current                            | I <sub>T</sub> = ±5 A, di/dt = +/-30 mA/ms                          |                          |     | ±0.15 |                | А     |

| dv/dt             | Critical rate of rise of off-state voltage | Linear voltage ramp, Maximum ramp value < 1.7V <sub>DRM</sub>       |                          | ±5  |       |                | kV/μs |

| ID                | Off-state current                          | $V_D = \pm 50 V$                                                    |                          |     |       | ±10            | μA    |

| Coff              | Off-state capacitance                      | $f = 100 \text{ kHz}, V_d = 1 \text{ V rms}, V_D = 0, (See Note 3)$ |                          |     |       | 0.1            | pF    |

NOTE 3: These capacitance measurements employ a three terminal capacitance bridge incorporating a guard circuit. The third terminal is connected to the guard terminal of the bridge.

NOVEMBER 1997 - REVISED SEPTEMBER 2000

#### electrical characteristics for the T and G or the R and G terminals, $T_A = 25 \degree C$

|                   | PARAMETER                                  | TEST CONDITIONS                                                                                         |                          | MIN   | TYP      | MAX          | UNIT  |

|-------------------|--------------------------------------------|---------------------------------------------------------------------------------------------------------|--------------------------|-------|----------|--------------|-------|

| I <sub>DRM</sub>  | Repetitive peak off-state current          | $V_D = \pm V_{DRM}$                                                                                     |                          |       |          | ±5           | μA    |

| V <sub>(BO)</sub> | Breakover voltage                          | dv/dt = +700 V/ms, Becure = 300 Ω                                                                       | TISP3600F3<br>TISP3700F3 |       |          | ±600<br>±700 | V     |

| I <sub>(BO)</sub> | Breakover current                          | dv/dt = $\pm$ 700 V/ms, R <sub>SOURCE</sub> = 300 $\Omega$                                              |                          |       | ±0.1     |              | А     |

| Ι <sub>Η</sub>    | Holding current                            | I <sub>T</sub> = ±5 A, di/dt = +/-30 mA/ms                                                              |                          | ±0.15 |          |              | А     |

| dv/dt             | Critical rate of rise of off-state voltage | Linear voltage ramp, Maximum ramp value < 0.85V <sub>DRM</sub>                                          |                          | ±5    |          |              | kV/µs |

| I <sub>D</sub>    | Off-state current                          | $V_{D} = \pm 50 V$                                                                                      |                          |       |          | ±10          | μA    |

| C <sub>off</sub>  | Off-state capacitance                      | f = 100 kHz, $V_d = 1 V rms$ , $V_D = 0$ , (See Note 4)<br>f = 100 kHz, $V_d = 1 V rms$ , $V_D = -50 V$ |                          |       | 44<br>11 | 74<br>20     | pF    |

NOTE 4: These capacitance measurements employ a three terminal capacitance bridge incorporating a guard circuit. The third terminal is connected to the guard terminal of the bridge.

#### thermal characteristics

|                       | PARAMETER | TEST CONDITIONS                                                                   | MIN | ТҮР | МАХ | UNIT |

|-----------------------|-----------|-----------------------------------------------------------------------------------|-----|-----|-----|------|

| $R_{	extsf{	heta}JA}$ |           | EIA/JESD51-3 PCB, $I_T = I_{TSM(1000)}$ ,<br>$T_A = 25 \text{ °C}$ , (see Note 5) |     |     | 50  | °C/W |

NOTE 5: EIA/JESD51-2 environment and PCB has standard footprint dimensions connected with 5 A rated printed wiring track widths.

NOVEMBER 1997 - REVISED SEPTEMBER 2000

### **DUAL BIDIRECTIONAL THYRISTOR OVERVOLTAGE PROTECTORS**

NOVEMBER 1997 - REVISED SEPTEMBER 2000

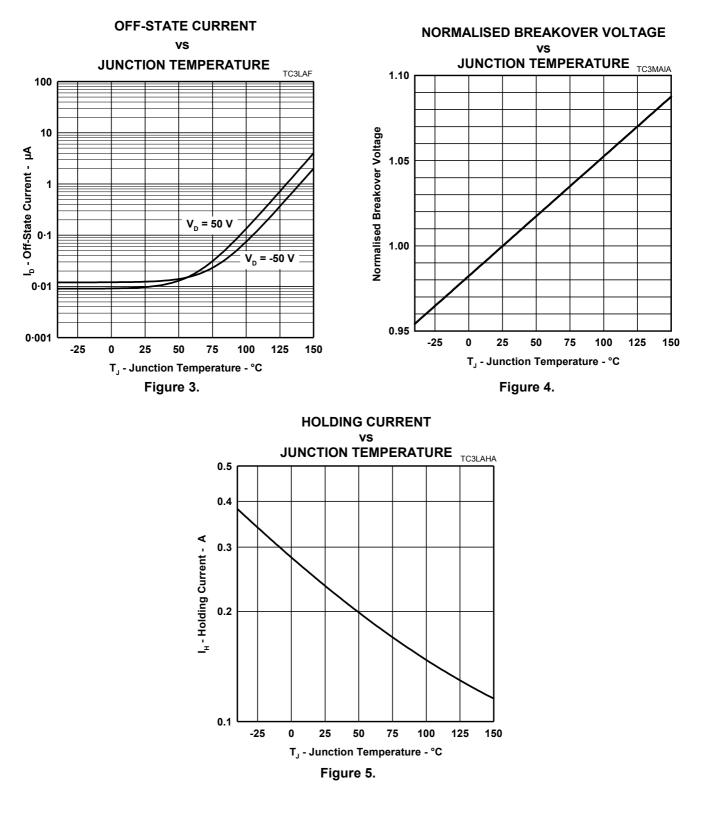

#### **TYPICAL CHARACTERISTICS**

INFORMATION PRODUCT

# DUAL BIDIRECTIONAL THYRISTOR OVERVOLTAGE PROTECTORS

NOVEMBER 1997 - REVISED SEPTEMBER 2000

#### THERMAL INFORMATION

Figure 6.

### DUAL BIDIRECTIONAL THYRISTOR OVERVOLTAGE PROTECTORS

NOVEMBER 1997 - REVISED SEPTEMBER 2000

#### **APPLICATIONS INFORMATION**

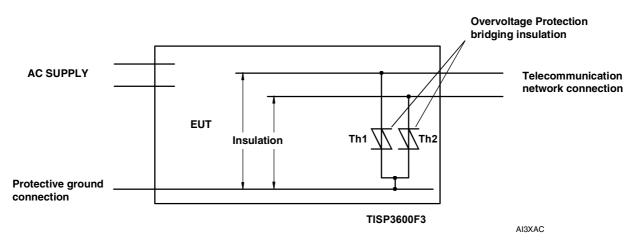

#### IEC 60950, EN 60950, UL 1950 and CSA 22.2 No.950

The '950 family of standards have certain requirements for equipment (EUT) with incoming lines of telecommunication network voltage (TNV). Any protector from a TNV conductor to protective ground must have a voltage rating of at least 1.6 times the equipment rated supply voltage (Figure 7). The intent is to prevent the possibility of the a.c. mains supply voltage from feeding into the telecommunication network and creating a safety hazard. International and European equipment usually have maximum rated voltage of 230 V rms, 240 V rms or 250 V rms. Multiplying the 250 V value by 1.6 gives a protector V<sub>DRM</sub> value of 400 V. Allowing for operation down 0 °C gives a V<sub>DRM</sub> requirement of 420 V at 25 °C. This need is met by the TISP3600F3.

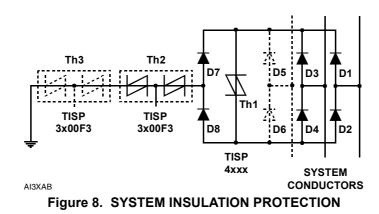

#### system insulation protection

Some wired systems are not directly connected to ground and are either floating or have a high resistance to ground. Induced transients may cause high voltages relative to ground resulting in arcing across insulation at wiring junctions. Arcing often leaves carbonised tracks which can degrade the system performance. Where the system is carrying a power feed, current conduction through the carbonised track may cause a safety hazard.

In Figure 8, a low-protector, Th1, from a TISP4xxx series limits the differential conductor voltage of the system. The use of a diode bridge, D1 through D4, reduces the capacitive loading of the protectors on the

### **DUAL BIDIRECTIONAL THYRISTOR OVERVOLTAGE PROTECTORS**

NOVEMBER 1997 - REVISED SEPTEMBER 2000

system and can be extended to protect more conductors as shown by the dotted diodes D5 and D6. Low voltage diodes can be used as the maximum reverse voltage stress is limited to the  $V_{(BO)}$  value of the TISP4xxx protector plus the diode forward recovery voltage. Steering diodes D7 and D8 and high-voltage protector Th2 limit the conductor voltage to ground. The limiting voltage is set by the choice of protector, TISP3600F3, 1200 V or TISP3700F3, 1400 V, and the number connected in series (one extra protector Th3 shown dotted).

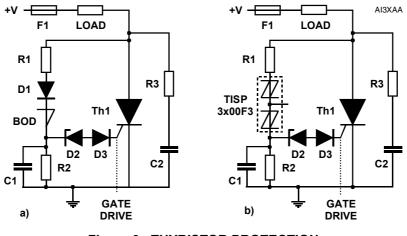

#### **BOD** replacement

Figure 9a shows a traditional overvoltage protection scheme for a high power switching thyristor, Th1. The protection voltage level is set by a BOD (BreakOver Diode) thyristor. Potentially damaging voltage transients cause the BOD to crowbar which turns on thyristor Th1. The on state of thyristor Th1 causes the current drawn by the load from the d.c. voltage supply +V to continuously increase until the fast acting fuse F1 operates.

Resistor R1 limits the peak BOD current and diode D1 protects the unidirectional BOD against reverse polarity voltage. Resistor R2 provides a d.c. return and with capacitor C1 forms a low pass network to prevent false triggering from noise. Further trigger voltage discrimination and isolation is given by the series combination of zener diode D2 and reverse blocking diode D3. Capacitor C2 and Resistor R3 form the normal snubber network for the thyristor Th1.

Figure 9. THYRISTOR PROTECTION

Figure 9b shows the TISP3x00F3 replacing the unidirectional BOD and reverse polarity protection diode, D1. Reverse polarity protection is not needed for the TISP3x00F3 as it is bidirectional.

### DUAL BIDIRECTIONAL THYRISTOR OVERVOLTAGE PROTECTORS

NOVEMBER 1997 - REVISED SEPTEMBER 2000

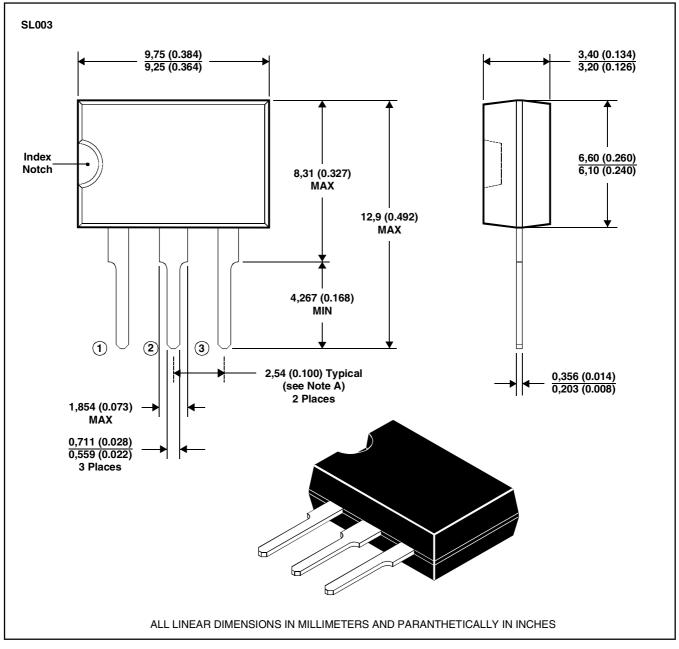

#### **MECHANICAL DATA**

### **SL003**

#### 3-pin plastic single-in-line package

This single-in-line package consists of a circuit mounted on a lead frame and encapsulated within a plastic compound. The compound will withstand soldering temperature with no deformation, and circuit performance characteristics will remain stable when operated in high humidity conditions. Leads require no additional cleaning or processing when used in soldered assembly.

NOTES: A. Each pin centreline is located within 0,25 (0.010) of its true longitudinal position. B. Body molding flash of up to 0,15 (0.006) may occur in the package lead plane.

MDXXCEA

## DUAL BIDIRECTIONAL THYRISTOR OVERVOLTAGE PROTECTORS

NOVEMBER 1997 - REVISED SEPTEMBER 2000

### **MECHANICAL DATA**

#### device symbolization code

Devices will be coded as below.

| DEVICE     | SYMBOLIZATION |

|------------|---------------|

| DEVICE     | CODE          |

| TISP3600F3 | SP3600F3      |

| TISP3700F3 | SP3700F3      |

NOVEMBER 1997 - REVISED SEPTEMBER 2000

#### **IMPORTANT NOTICE**

Power Innovations Limited (PI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to verify, before placing orders, that the information being relied on is current.

PI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with PI's standard warranty. Testing and other quality control techniques are utilized to the extent PI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

PI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor is any license, either express or implied, granted under any patent right, copyright, design right, or other intellectual property right of PI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

PI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORISED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS.

Copyright © 2000, Power Innovations Limited