# +5 Volt, Parallel Input Complete Dual 12-Bit DAC

AD8582

#### **FEATURES**

Complete Dual 12-Bit DAC

No External Components

Single +5 Volt Operation

1 mV/Bit with 4.095 V Full Scale

True Voltage Output, ±5 mA Drive

Very Low Power: 5 mW

APPLICATIONS

Digitally Controlled Calibration

Portable Equipment

Servo Controls

Process Control Equipment

PC Peripherals

#### GENERAL DESCRIPTION

The AD8582 is a complete, parallel input, dual 12-bit, voltage output DAC designed to operate from a single +5 volt supply. Built using a CBCMOS process, this monolithic DAC offers the user low cost, and ease-of-use in +5 volt only systems.

Included on the chip, in addition to the DACs, are a rail-to-rail amplifier, latch and reference. The reference  $(V_{\rm REP})$  is trimmed to 2.5 volts output, and the on-chip amplifier gains up the DAC output to 4.095 volts full scale. The user needs only supply a  $\pm 5$  volt supply.

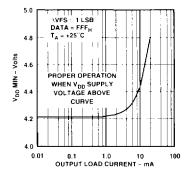

The AD8582 is coded natural binary. The op amp output swings from 0 volt to  $\pm 4.095$  volts for a one-millivolt-per-bit resolution, and is capable of driving  $\pm 5$  mA. Operation down to 4.3 V is possible with output load currents less than 1 mA.

Figure 1. Minimum Supply Voltage vs. Load

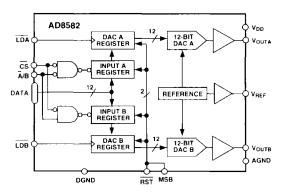

#### FUNCTIONAL BLOCK DIAGRAM

The high speed parallel data interface connects to the fastest processors without wait states. The double-buffered input structure allows the user to load the input registers one at a time, then a single load strobe tied to both LDA + LDB inputs will update both DAC outputs simultaneously. LDA and LDB can also be activated independently to immediately update their respective DAC registers. An address input decodes DAC A or DAC B when the chip select  $\overline{CS}$  input is strobed. An asynchronous reset input sets the output to zero scale. The MSB bit can be used to establish a preset to midscale when the reset input is strobed.

The AD8582 is available in the 24-pin plastic DIP and the surface mount SOIC-24. Each part is fully specified for operation over 40 C to  $\pm 85$  C, and the full  $\pm 5$  V  $\pm$  5% power supply range.

#### ORDERING INFORMATION<sup>1</sup>

| Model       | Temperature<br>Range | Package<br>Description | Package<br>Option <sup>2</sup> |  |  |

|-------------|----------------------|------------------------|--------------------------------|--|--|

| AD8582AN    | -40 C to +85 C       | 24-Pin Plastic DIP     | N-24                           |  |  |

| AD8582AR    | 40 'C to +85' C      | 24-Lead SOIC           | SOL-24                         |  |  |

| AD8582CHIPS | +25°C                | Die                    |                                |  |  |

#### NOTES

<sup>4</sup>For the specifications contact your local Analog Devices sales office. The AD8582 contains 1270 transistors

Tor outline information see Package Information section

## **AD8582—SPECIFICATIONS**

### **ELECTRICAL CHARACTERISTICS** (@ $V_{00} = +5.0 \text{ V} \pm 5\%$ , $R_L = \text{No Load}$ , $-40^{\circ}\text{C} \le T_A \le +85^{\circ}\text{C}$ , unless otherwise noted)

| Parameter                            | Symbol                  | Condition                                                                                         | Min   | Typ       | Max      | Units        |

|--------------------------------------|-------------------------|---------------------------------------------------------------------------------------------------|-------|-----------|----------|--------------|

| STATIC PERFORMANCE                   |                         |                                                                                                   |       |           |          |              |

| Resolution                           | N                       | Note 1                                                                                            | 12    |           |          | Bits         |

| Relative Accuracy                    | INL.                    |                                                                                                   | 2     | $\pm 3/4$ | +2       | LSB          |

| Differential Nonlinearity            | DNL                     | Monotonic                                                                                         | 1     | $\pm 3/4$ | + l      | LSB          |

| Zero-Scale Error                     | $V_{ZSL}$               | $Data = 000_n$                                                                                    |       | +0.2      | + 3      | mV           |

| Full-Scale Voltage                   | V <sub>18</sub>         | $Data = FFF_{H}^{2}$                                                                              | 4.079 | 4.095     | 4.111    | V            |

| Full-Scale Tempco                    | TCV <sub>FS</sub>       | Notes 2 and 3                                                                                     | i     | ±16       |          | ppm/         |

| MATCHING PERFORMANCE                 |                         |                                                                                                   |       |           |          |              |

| Linearity Matching Error             | ΔV <sub>FS</sub> A/B    |                                                                                                   |       | ±1        |          | LSB          |

| REFERENCE OUTPUT                     |                         |                                                                                                   |       |           |          |              |

| Output Voltage                       | $V_{RPP}$               |                                                                                                   | 2.484 | 2.500     | 2.516    | V            |

| Output Source Current                | $I_{RH}$                | Note 4                                                                                            |       |           | - 5      | mA           |

| Line Rejection                       | $LN_{RFI}$              |                                                                                                   | į     |           | 0.08     | %/V          |

| Load Regulation                      | $LD_{8EG}$              | $I_{RhF} = 0 \text{ mA to 5 mA}$                                                                  |       |           | 0.1      | %/mA         |

| ANALOG OUTPUT                        |                         |                                                                                                   |       |           |          |              |

| Output Current                       | $I_{\alpha_1 \gamma_1}$ | $Data = 800_{H}$                                                                                  |       |           | ± 5      | mA           |

| Load Regulation at Half Scale        | $LD_{RFG}$              | $R_{\rm I} = 402 \Omega$ to $\infty$ , Data = $800_{\rm H}$                                       |       | l         | 3        | LSB          |

| Capacitive Load                      | C <sub>1</sub>          | No Oscillation                                                                                    |       | 500       |          | pF           |

| DYNAMIC CHARACTERISTICS <sup>3</sup> |                         |                                                                                                   |       |           |          |              |

| Crosstalk                            | $\mathbf{C}^{1}$        |                                                                                                   |       | >64       |          | dB           |

| Voltage Output Settling Time         | t <sub>s</sub>          | To ±1 LSB of Final Value                                                                          |       | 16        |          | μs           |

| Digital Feedthrough                  | F <sub>1</sub>          | Signal Measured at DAC Output, While Changing Data (LDA = LDB = "1")                              |       | 35        |          | nV s         |

| LOGIC INPUTS                         |                         |                                                                                                   |       |           |          |              |

| Logic Input Low Voltage              | $V_{ii}$                |                                                                                                   |       |           | 0.8      | $\mathbf{v}$ |

| Logic Input High Voltage             | v <sub>iii</sub>        |                                                                                                   | 2.4   |           |          | v            |

| Input Leakage Current                | I <sub>0</sub>          |                                                                                                   |       |           | 10       | μA           |

| Input Capacitance                    | Cu                      | Note 3                                                                                            |       |           | 10       | pF           |

| TIMING SPECIFICATIONS                |                         |                                                                                                   |       |           |          |              |

| Chip Select Pulse Width              | t <sub>csw</sub>        |                                                                                                   | 30    |           |          | ns           |

| DAC Select Setup                     | tas                     |                                                                                                   | 30    |           |          | ns           |

| DAC Select Hold                      | t <sub>AH</sub>         |                                                                                                   | 0     |           |          | ns           |

| Data Setup                           | t <sub>DS</sub>         |                                                                                                   | 30    |           |          | ns           |

| Data Hold                            | t <sub>DH</sub>         |                                                                                                   | 10    |           |          | ns           |

| Load Setup                           | t <sub>18</sub>         |                                                                                                   | 20    |           |          | ns           |

| Load Hold                            | t <sub>i H</sub>        |                                                                                                   | 10    |           |          | ns           |

| Load Pulse Width                     | t <sub>1.15</sub> w     |                                                                                                   | 20    |           |          | ns           |

| Reset Pulse Width                    | t <sub>RSW</sub> .      |                                                                                                   | 30    |           |          | ns           |

| SUPPLY CHARACTERISTICS               |                         |                                                                                                   |       |           |          |              |

| Positive Supply Current              | I <sub>DI</sub> ,       | $V_{IH} = 2.4 \text{ V}, V_{II} = 0.8 \text{ V}$                                                  |       | 4         | 7        | mA           |

| <b>5 5 1 3</b>                       | 73                      | $V_{II} = 0 \text{ V}, V_{DD} = +5 \text{ V}$                                                     |       | 1         | 2        | mA           |

| Power Dissipation <sup>7</sup>       | P <sub>DISS</sub>       | $V_{IH} = 2.4 \text{ V}, V_{II} = 0.8 \text{ V}$<br>$V_{II} = 0 \text{ V}, V_{DD} = +5 \text{ V}$ |       | 20<br>5   | 35<br>10 | mW<br>mW     |

| Power Supply Sensitivity             | PSS                     |                                                                                                   | 1     | 0.002     | 0.004    | m w<br>%/%   |

| rower supply sensitivity             | 133                     | $\Delta V_{DD} = \pm 5\%$                                                                         |       | 0.002     | 0.004    | 707.70       |

#### NOTES

$<sup>^{\</sup>circ}1$  LSB = 1 mV for 0 V to  $\pm 4.095$  V output range.

Includes internal voltage reference error.

These parameters are guaranteed by design and not subject to production testing.

<sup>&#</sup>x27;Very little sink current is available at the V<sub>REE</sub> pin. Use external buffer if setting up a virtual ground.

<sup>&#</sup>x27;Settling time is not guaranteed for the first six codes 0 through 5.

<sup>&</sup>quot;All input control signals are specified with  $t_{\rm g}$  =  $t_{\rm f}$  = 5 ns (10% to 90% of +5 V) and timed from a voltage level of 1.6 V.

Power dissipation is a calculated value  $I_{\rm DD}$  + 5 V.

Specifications subject to change without notice.