## Datasheet

## AS8530

# LIN Transceiver with Integrated Voltage Regulator and MCU Interface for Automotive Applications

# 1 General Description

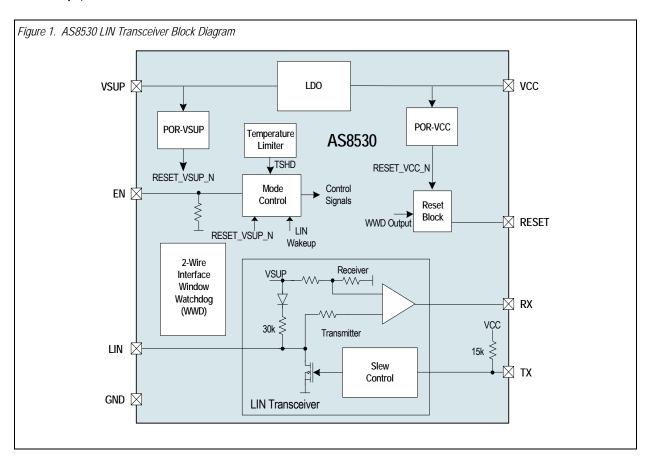

The AS8530 is a general purpose companion IC for sensor and actuator LIN slaves offering LIN transceiver and low drop voltage regulator.

It also provides a 2-wire microcontroller interface through shared EN and TX pins to access a window watchdog with RC oscillator, control registers, backup registers and monitoring information.

The IC is fabricated in a high voltage CMOS technology which is able to withstand voltages up to 42V.

The product is available in ep-SOIC8 package.

# 2 Key Features

- Operating voltage 6V to 18V

- Linear, low-drop voltage regulator: VCC = 5V ±5% or 3.3V ±5% as a factory programming option

- 50mA load current

- Operating modes: Normal and Standby or Normal and Sleep as a factory option

- Typically 45µA quiescent current in standby mode. Typically 35µA quiescent current in sleep mode

- Under voltage reset with factory options

- LIN bus transceiver I conforming to LIN 2.1, TX time out fail safe feature, over temperature warning and shut down

- Window watchdog if factory enabled

- Micro controller 2-wire interface through shared pins for watchdog trigger, monitoring, register read /write

- Chip ID for traceability and module ID

- 8 Backup registers to store data during VCC shut down

- ep-SOIC8 package

- -40°C to +125°C ambient operating temperature

# 3 Applications

The AS8530 is a System Basis Chip for automotive LIN networked sensor or actuator slaves.

## Contents

| 1 | General Description                                  | . 1 |

|---|------------------------------------------------------|-----|

| 2 | Key Features                                         | . 1 |

| 3 | Applications                                         | . 1 |

| 4 | Pin Assignments                                      | . 4 |

|   | 4.1 Pin Descriptions                                 | 4   |

| 5 | Absolute Maximum Ratings                             | . 5 |

| 6 | Electrical Characteristics                           | . 6 |

|   | 6.1 Operating Conditions                             |     |

|   | 6.2 Digital Inputs and Outputs                       |     |

|   | 6.3 Detailed System and Block Specifications         |     |

|   | 6.3.1 Electrical System Specifications               |     |

|   | 6.4 Low Dropout Regulator                            | 7   |

|   | 6.5 LIN Transceiver                                  | 8   |

|   | 6.5.1 DC Electrical Characteristics                  | 8   |

|   | 6.5.2 AC Electrical Characteristics                  |     |

|   | 6.5.3 Temperature Limiter                            |     |

|   | 6.5.4 TX Timeout Watchdog                            |     |

|   | 6.6 Vcc Undervoltage Reset and Window Watchdog       |     |

| - | 6.7 Two Port Serial Interface                        |     |

| 1 | Detailed Description                                 |     |

|   | 7.1 Voltage Regulator (LDO)                          |     |

|   | 7.2 Temperature Limiter                              |     |

|   | 7.3 Vsup Undervoltage Reset                          |     |

|   | 7.3.1 VSUP Undervoltage in Normal Mode               |     |

|   | 7.3.2 VSUP Undervoltage in Standby Mode / Sleep Mode |     |

|   | 7.4 RESET                                            |     |

|   | 7.5 VCC Undervoltage Reset                           |     |

|   | 7.6 Window Watchdog (WWD)                            |     |

|   | 7.7 LIN Transceiver                                  |     |

|   | 7.8 Operating Modes and States                       |     |

|   | 7.8.1 Normal Mode                                    |     |

|   | 7.8.2 Standby Mode                                   |     |

|   | 7.8.3 Sleep Mode                                     | 15  |

|   | 7.8.4 Temporary Shutdown Mode                        |     |

|   | 7.8.5 Thermal Shutdown State                         |     |

| _ | 7.9 State Diagram                                    |     |

| 8 | Application Information                              | 18  |

|   | 8.1 Initialization                                   | 18  |

|   | 8.2 Wake-Up                                          |     |

|   | 8.3 Over-Temperature Shutdown                        |     |

|   | 8.4 LIN BUS Transceiver                              |     |

|   | 8.4.1 Transmit Mode                                  |     |

|   | 8.4.2 Receive Mode                                   | 20  |

| 8.5 RX and TX Interface                             | 20 |

|-----------------------------------------------------|----|

| 8.6 MODE Input EN                                   | 21 |

| 8.7 Serial Port Interface                           | 23 |

| 8.7.1 Device Configuration using 2-Wire Serial Port | 23 |

| 8.8 Control and Diagnosis Registers                 | 26 |

| 8.8.1 Definition of Control and Status Registers    | 26 |

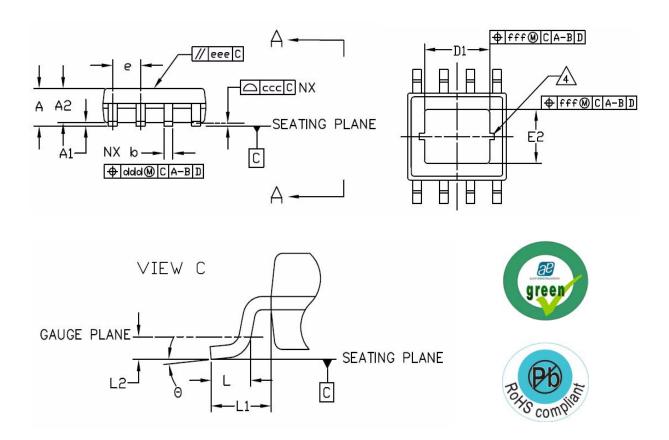

| 9 Package Drawings and Markings                     | 28 |

| 10 Ordering Information                             | 31 |

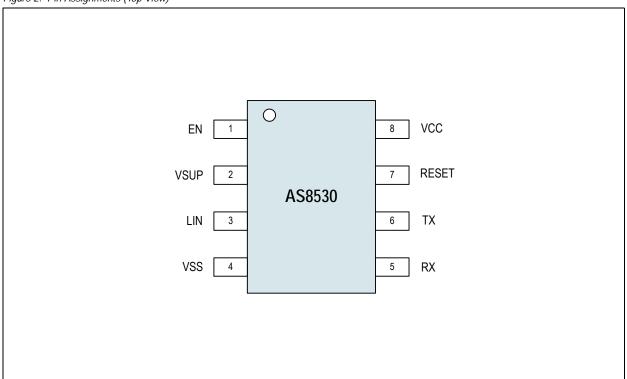

# 4 Pin Assignments

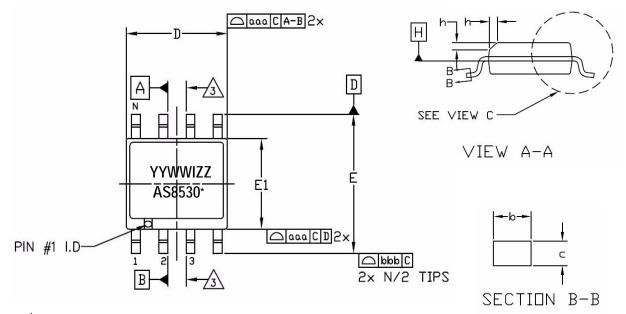

Figure 2. Pin Assignments (Top View)

## 4.1 Pin Descriptions

Table 1. Pin Descriptions

| Pin Number | Pin Name | Pin Type                     | Special Requirements                                         | Description                                                                                    |

|------------|----------|------------------------------|--------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| 1          | EN       | Digital input with pull-down | 2kV ESD                                                      | Enable high-voltage compatible pin with pull down to VSS and ½ VCC trigger level, active high. |

| 2          | Vsup     | Supply pad                   | Load dump (42V max),<br>4kV HBM ESD,<br>Jump start (27V max) | Battery supply                                                                                 |

| 3          | LIN      | Analog I/O                   | Conforms to LIN 2.1,<br>6kV HBM ESD                          | LIN Bus                                                                                        |

| 4          | VSS      | Supply pad                   |                                                              |                                                                                                |

| 5          | RX       | Digital output with pull-up  |                                                              | LIN transceiver receive signal, data out in test mode                                          |

| 6          | TX       | Digital input with pull-up   | 2kV ESD                                                      | LIN transceiver transmit signal, clock in test mode                                            |

| 7          | RESET    | Digital output               |                                                              | Digital output referenced to VCC, active low                                                   |

| 8          | VCC      | Supply pad                   |                                                              | Regulated 5V / 3.3V supply for loads up to 50mA. OTP selectable                                |

# 5 Absolute Maximum Ratings

Stresses beyond those listed in Table 2 may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in Electrical Characteristics on page 6 is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Table 2. Absolute Maximum Ratings

| Param                                             | Min                           | Max  | Units      | Comments                                     |                                                                                                                                                                                                                                                                                                   |

|---------------------------------------------------|-------------------------------|------|------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Electrical Parameters                             |                               |      |            |                                              |                                                                                                                                                                                                                                                                                                   |

|                                                   | Vsup                          | -0.3 | 42         | V                                            | Transient up to 500ms duration                                                                                                                                                                                                                                                                    |

|                                                   | EN                            | -0.3 | VSUP + 0.3 | V                                            |                                                                                                                                                                                                                                                                                                   |

| DC Supply Voltage                                 | Vcc                           | -0.3 | 7          | V                                            |                                                                                                                                                                                                                                                                                                   |

|                                                   | LIN                           | -27  | +40        | V                                            |                                                                                                                                                                                                                                                                                                   |

|                                                   | RESET, RX, TX                 | -0.3 | Vcc + 0.3  | V                                            |                                                                                                                                                                                                                                                                                                   |

| Input current (latch)                             | up immunity) I <sub>scr</sub> | -100 | 100        | mA                                           | Norm: JEDEC 78                                                                                                                                                                                                                                                                                    |

| Electrostatic Discharge                           |                               |      |            |                                              |                                                                                                                                                                                                                                                                                                   |

|                                                   |                               | ±2   |            |                                              | For on board signals Vcc, TX, RX, Reset                                                                                                                                                                                                                                                           |

| Electrostatic Discharge (ESD) Norm: AEC-Q-100-002 |                               | ±4   |            | kV                                           | For Vsup                                                                                                                                                                                                                                                                                          |

| Hom. ALO                                          | k 100 002                     | ±6   |            |                                              | LIN to Vss, HBM Model                                                                                                                                                                                                                                                                             |

| Continuous Power Dissip                           | oation                        |      |            |                                              |                                                                                                                                                                                                                                                                                                   |

| Total operating por<br>(all supplies and          |                               |      | 0.25       | W                                            | epSOIC8 in still air, soldered on JEDEC standard board @125° ambient, static operation = no time limit                                                                                                                                                                                            |

| Temperature Ranges and                            | Storage Conditions            |      |            |                                              |                                                                                                                                                                                                                                                                                                   |

| Storage temper                                    | rature (T <sub>strg</sub> )   | -55  | +150       | °C                                           |                                                                                                                                                                                                                                                                                                   |

| Package body temperature (T <sub>body</sub> )     |                               |      | +260       | °C                                           | The reflow peak soldering temperature (body temperature) specified is in accordance with IPC/<br>JEDEC J-STD-020 "Moisture/Reflow Sensitivity<br>Classification for Non-Hermetic Solid State Surface<br>Mount Devices".<br>The lead finish for Pb-free leaded packages is matte<br>tin (100% Sn). |

| Humidity non-c                                    | condensing                    | 5    | 85         | %                                            |                                                                                                                                                                                                                                                                                                   |

| Moisture Sens                                     |                               | 3    |            | Represents a maximum floor life time of 168h |                                                                                                                                                                                                                                                                                                   |

## 6 Electrical Characteristics

## 6.1 Operating Conditions

| Symbol            | Parameter               | Conditions                              | Min | Тур | Max  | Units |

|-------------------|-------------------------|-----------------------------------------|-----|-----|------|-------|

| Vsup              | Positive Supply Voltage | Normal operating condition              | 6   |     | 18   | V     |

| VSS               | Negative Supply Voltage |                                         | 0   |     |      | V     |

| Тамв              | Ambient temperature     | Maximum junction temperature (TJ) 150°C | -40 |     | +125 | °C    |

| I <sub>supp</sub> | Supply Current          |                                         |     |     | 65   | mA    |

## 6.2 Digital Inputs and Outputs

All pull-up, pull-downs have been implemented with active devices. RESET and RX have been measured with 100pF load.

| Parameter                 | Conditions                                                                                                                                                                                                                                                             | Min                                                                                                                                                                                                                                                                                                                                                               | Тур | Max          | Units                    |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------|--------------------------|

|                           | EN Input                                                                                                                                                                                                                                                               | -                                                                                                                                                                                                                                                                                                                                                                 |     | <del>'</del> |                          |

| High level input voltage  | High Voltage Pin which can also be connected to VSUP                                                                                                                                                                                                                   | 0.8Vcc                                                                                                                                                                                                                                                                                                                                                            |     |              | V                        |

| Low level input voltage   |                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                   |     | 0.2Vcc       | V                        |

| Input leakage current     | EN = L                                                                                                                                                                                                                                                                 | -1                                                                                                                                                                                                                                                                                                                                                                |     | +1           | μΑ                       |

| Pull down current         | EN = Vcc                                                                                                                                                                                                                                                               | 20                                                                                                                                                                                                                                                                                                                                                                |     | 40           | μΑ                       |

|                           | TX                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                   |     |              |                          |

| High level input voltage  |                                                                                                                                                                                                                                                                        | 0.8Vcc                                                                                                                                                                                                                                                                                                                                                            |     |              | V                        |

| Low level input voltage   |                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                   |     | 0.2Vcc       | V                        |

| Input leakage current     | TX = Vcc                                                                                                                                                                                                                                                               | -1                                                                                                                                                                                                                                                                                                                                                                |     | +1           | μΑ                       |

| Pull up current           | TX pulled to VSS                                                                                                                                                                                                                                                       | -30                                                                                                                                                                                                                                                                                                                                                               |     | -10          | μΑ                       |

|                           | RESET                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                   |     |              |                          |

| High level output voltage | IOUT = 1 mA, VSUP ≥ 6V                                                                                                                                                                                                                                                 | Vcc -<br>0.5                                                                                                                                                                                                                                                                                                                                                      |     |              | V                        |

| Low level output voltage  | Vsup≥6V                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                   |     | VSS<br>+ 0.4 | V                        |

|                           | RX                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                   |     |              |                          |

| High level output voltage |                                                                                                                                                                                                                                                                        | Vcc -<br>0.5                                                                                                                                                                                                                                                                                                                                                      |     |              | V                        |

| Low level output voltage  | IOUT = 1 mA, VSUP ≥ 6V                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                   |     | VSS + 0.4    | V                        |

|                           | High level input voltage  Low level input voltage  Input leakage current  Pull down current  High level input voltage  Low level input voltage  Input leakage current  Pull up current  High level output voltage  Low level output voltage  High level output voltage | High level input voltage  Low level input voltage  Input leakage current  Pull down current  EN = L  Pull down current  EN = VCC  TX  High level input voltage  Low level input voltage  Input leakage current  TX = VCC  Pull up current  TX pulled to VSS  RESET  High level output voltage  Low level output voltage  VSUP ≥ 6V  RX  High level output voltage |     |              | High level input voltage |

## 6.3 Detailed System and Block Specifications

### 6.3.1 Electrical System Specifications

| Symbol               | ı           | Parameter                                | Conditions                               | Min | Тур | Max | Units |

|----------------------|-------------|------------------------------------------|------------------------------------------|-----|-----|-----|-------|

|                      |             | Normal made                              | No load on VCC, LIN recessive, VSUP= 12V |     | 300 |     | μA    |

| JDD 1                | Normal mode | No load on VCC, LIN dominant, VSUP = 12V |                                          | 700 |     | μA  |       |

| IDD <sub>nom</sub> ' | consumption | Stand-by mode                            | Up to 125°C ambient (no load), VSUP= 12V |     | 45  |     | μA    |

|                      |             | Sleep mode                               | Up to 125°C ambient (no load), VSUP=12V  |     | 35  |     | μΑ    |

<sup>1.</sup> No external load on the LIN bus

### 6.4 Low Dropout Regulator

The LDO block is a linear voltage regulator, which provides a regulated (band-gap stabilized) output voltage (Vcc) from the battery supply voltage (Vsup).

$(6V < VSUP < 18V \text{ for option 1, } 6V < VSUP < 18V \text{ option 2; } -40^{\circ}C < T_{J} < 150^{\circ}C; \text{ all voltages are with respect to ground (VSS); positive current flows into the pin), normal operating mode if not otherwise mentioned.}$

| Symbol    | Parameter                       |          | Conditions                           | Min      | Тур      | Max          | Units                    |      |      |      |

|-----------|---------------------------------|----------|--------------------------------------|----------|----------|--------------|--------------------------|------|------|------|

| Vcc       | Regulated supply voltage        |          | Option 1                             |          |          | 5.25         | V                        |      |      |      |

| VCC       | ILOAD 0mA to 50mA               | Option 2 |                                      | 3.135    |          | 3.465        | V                        |      |      |      |

| TJ        | Junction Temperature            |          |                                      | -40      |          | 150          | °C                       |      |      |      |

| Vsup      | Supply Voltage Range            |          |                                      | 6        | 12       | 18           | V                        |      |      |      |

|           |                                 |          | Load < 50mA                          | 4.75     | 5.0      | 5.25         |                          |      |      |      |

|           |                                 |          | 50mA to 65mA                         | 4.5      |          | 5.5          |                          |      |      |      |

|           |                                 | Option 1 | Standby mode @ ICC < 5mA             | 4.5      |          | 5.5          |                          |      |      |      |

| Vcc       | Output Voltage Range            |          | Load-dump condition,<br>ILOAD < 50mA |          |          | 5.5          | V                        |      |      |      |

| VCC       | Output voitage Kange            |          | Load < 50mA                          | 3.135    | 3.3      | 3.465        | ]                        |      |      |      |

|           |                                 | Option 2 | Option 2                             | Option 2 | Option 2 | 50mA to 65mA | 2.97                     | 3.3  | 3.63 |      |

|           |                                 |          |                                      |          |          | Option 2     | Standby mode @ ICC < 5mA | 2.97 |      | 3.63 |

|           |                                 |          | Load-dump condition,<br>ILOAD < 50mA |          |          | 3.63         |                          |      |      |      |

| ICC_SH    | Output Short Circuit Current    |          | Normal mode                          | 50       |          | 250          | mA                       |      |      |      |

| ЮС_ЗП     | Output Short Circuit Current    |          | Standby mode                         | 5        |          | 250          | IIIA                     |      |      |      |

| dVcc1     | Line Regulation                 |          | ΔVcc / ΔVsup                         |          |          | 8            | mV/V                     |      |      |      |

| LOREG_SM  | Load Regulation (Standby mode)  | ΔVcc     | : / ΔICCn (for ILOAD > 500μA)        |          |          | 10           | mV/mA                    |      |      |      |

| LOREG_NM  | Load Regulation (Normal mode)   | ΔVcc     | : / ΔICCn (for ILOAD > 500μA)        |          |          | 1            | mV/mA                    |      |      |      |

| CL1       | Output Capacitor (Electrolytic) |          |                                      | 2.2      |          | 10           | μF                       |      |      |      |

| ESR1      | Output Capacitor (Liectrolytic) |          |                                      | 1        |          | 10           | Ω                        |      |      |      |

| CL2       | Output Capacitor (Ceramic)      |          |                                      | 100      |          | 220          | nF                       |      |      |      |

| ESR2      | - Output Capacitor (Ceramic)    |          |                                      | 0.02     |          | 1            | Ω                        |      |      |      |

| CSUP1E    | Input canacitor (Flectrolytic)  |          |                                      | 10       |          | 100          | μF                       |      |      |      |

| ESR1_CSUP | Input capacitor (Electrolytic)  |          | For EMC suppression                  | 1        |          | 10           | Ω                        |      |      |      |

| CSUP2C    | Input capacitor (Ceramic)       |          | I OF EINIO SUPPLESSION               | 100      |          | 220          | nF                       |      |      |      |

| ESR2_CSUP | - input capacitor (Ceramic)     |          |                                      |          |          | 1            | Ω                        |      |      |      |

### 6.5 LIN Transceiver

#### 6.5.1 DC Electrical Characteristics

$(4.5V < VCC < 5.5V; 6V < VSUP < 18V; -40°C < T_J < 150°C, VBUS is the voltage on the LIN node. All voltages are with respect to ground (VSS); positive current flows into the pin.$

| Symbol                    | Parameter                         | Conditions                                                                                                | Min   | Тур | Max   | Units |

|---------------------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------|-------|-----|-------|-------|

| Driver                    |                                   |                                                                                                           |       |     |       |       |

| I <sub>bus_lim</sub>      |                                   | Current limitation in Dominant State <sup>1</sup> LIN = VSUP_max                                          | 40    | 120 | 200   | mA    |

| LIN_V <sub>OL</sub>       |                                   | Output Voltage BUS (dominant state), $I_{LIN}$ = 40mA (short-circuit condition tested at $V_{OL}$ = 2.5V) |       |     | 2     | V     |

|                           | Pull-up resistor                  | Normal mode<br>(recessive BUS level on TX pin)                                                            | 20    | 40  | 60    | kΩ    |

| I <sub>bus_leak_rec</sub> |                                   | Driver OFF;<br>Vsup = 7.0V, 8V < VBUS < 18                                                                |       |     | 20    | μA    |

| Receiver                  |                                   |                                                                                                           |       |     |       |       |

| I <sub>bus_leak_dom</sub> | Input Leakage current at receiver | Input Leakage current at receiver<br>Driver OFF; Vbus = 0V; Vsup = 12V;<br>Vcc = 5V                       | -1    |     |       | mA    |

| l <sub>bus_no_GND</sub>   |                                   | VSS = Vsup; Vsup = 12V;<br>0V < VBUS < 18V, Vcc = 5V <sup>2</sup>                                         | -1    |     | 1     | mA    |

| I <sub>bus_no_bat</sub>   |                                   | VSUP = VSS;<br>0V < VBUS < 18V, VCC = VSS <sup>2</sup>                                                    |       |     | 100   | μA    |

| $V_{bus\_dom}$            |                                   |                                                                                                           |       |     | 0.4   | Vsup  |

| V <sub>bus_rec</sub>      |                                   |                                                                                                           | 0.6   |     |       | Vsup  |

| V <sub>bus_cnt</sub>      |                                   | $V_{bus\_cnt} = (V_{th\_dom} + V_{th\_rec})/2^{3}$                                                        | 0.475 |     | 0.525 | Vsup  |

| $V_{hys}$                 |                                   | $V_{hys} = (V_{th\_dom} - V_{th\_rec})^3$                                                                 | 0.05  |     | 0.175 | Vsup  |

<sup>1.</sup> This failure condition triggers thermal shut down when shut down temperature threshold is exceeded.

<sup>2.</sup> Not production tested.

<sup>3.</sup> Vth\_dom: Receiver threshold of the recessive to dominant LIN bus edge Vth\_rec : Receiver threshold of the dominant to recessive LIN bus edge

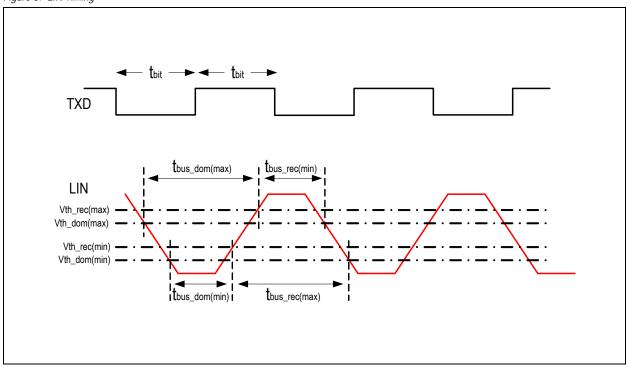

#### 6.5.2 AC Electrical Characteristics

LIN Driver, Bus load conditions ( $C_{BUS}$ ;  $R_{BUS}$ ): 1nF;  $1k\Omega/6$ ,8nF;  $660\Omega/10nF$ ;  $500\Omega$

| Symbol                                 | Conditions                                                                                                                                                                                                                                              | Min   | Тур | Max   | Units        |

|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|-------|--------------|

| D1 (worst case 20Kbps transmission)    | $\begin{split} &V_{th\_rec}(max) = 0.744 \text{ x VSUP;} \\ &V_{th\_dom}(max) = 0.581 \text{ x VSUP;} \\ &VSUP = 6.0V \text{ to 18V; tbit = 50}\mu\text{s;} \\ &D1 = \text{tbus\_rec}(min) \text{ / } (2 \text{ x tbit)} \end{split}$                   | 0.369 |     |       |              |

| D2<br>(worst case 20kbps transmission) | $\begin{split} &V_{th\_rec} \text{ (min)} = 0.422 \text{ x VSUP;} \\ &V_{th\_dom} \text{ (min)} = 0.284 \text{ x VSUP;} \\ &VSUP = 6V \text{ to } 18V; \text{ tbit} = 50\mu\text{s;} \\ &D2 = \text{tbus\_rec(max)}  /  (2 \text{ x tbit)} \end{split}$ |       |     | 0.581 |              |

| D3 (worst case 10.4kbps transmission)  | $\begin{split} &V_{th\_rec} \ (max) = 0.778 \ x \ VSUP; \\ &V_{th\_dom} \ (max) = 0.616 \ x \ VSUP; \\ &VSUP = 6.0V \ to \ 18V; \ tbit = 96\mu s; \\ &D3 = tbus\_rec(min) \ / \ (2 \ x \ tbit) \end{split}$                                             | 0.417 |     |       |              |

| D4 (worst case 10.4kbps transmission)  | $V_{th\_rec}$ (min) = 0.389 x VSUP;<br>$V_{th\_dom}$ (min) = 0.251 x VSUP;<br>VSUP = 6V to18V; tbit = 96 $\mu$ s;<br>D4 = tbus\_rec(max) / (2 x tbit)                                                                                                   |       |     | 0.59  |              |

| t <sub>dLR</sub>                       | VCC = 5V;<br>Propagation delay bus dominant to RX LOW                                                                                                                                                                                                   |       |     | 6     | μs           |

| t <sub>dHR</sub>                       | VCC = 5V;<br>Propagation delay bus dominant to RX HIGH                                                                                                                                                                                                  |       |     | 6     | μs           |

| t <sub>RS</sub>                        | Receiver Delay symmetry                                                                                                                                                                                                                                 | -2    |     | 2     | μs           |

| t <sub>wake</sub>                      | Wake-up delay time                                                                                                                                                                                                                                      | 30    |     | 150   | μs           |

| t <sub>sIn</sub>                       | Transition from standby mode to normal mode (clock frequency is 128kHz ± 25%)                                                                                                                                                                           |       | 4   |       | Clock cycles |

| t <sub>nsl</sub>                       | Transition from normal mode to standby mode (clock frequency is 128kHz ± 25%)                                                                                                                                                                           |       | 6   |       | Clock cycles |

| t <sub>rec_deb</sub>                   | Receiver De-bounce time                                                                                                                                                                                                                                 | 1     |     | 3     | μs           |

| C <sub>int</sub>                       | Guaranteed by design                                                                                                                                                                                                                                    |       | 220 | 250   | pF           |

**Note:** Sleep-mode to Normal mode transition is identical to the Power-ON sequence after the remote wakeup event on LIN bus. The transition time will include the t<sub>Res</sub> (RESET time) and start-up time for the LDO.

Figure 3. LIN Timing

## 6.5.3 Temperature Limiter

| Symbol               | Parameter                    | Conditions                                                                                                                                                           | Min | Тур | Max | Units |

|----------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| $T_{sd}$             | Shut down temperature        | Junction temperature                                                                                                                                                 | 139 |     | 171 | °C    |

| T <sub>ret</sub>     | Return temperature           | During shut down, the sensor must be powered by VSUP. Thermal shut down disables LDO and sets all drivers to high impedance, the IC returns from shut down with POR. | 121 |     | 149 | °C    |

| T <sub>otset</sub>   | Over-temp warning flag set   | The temperature beyond which the warning flag is set.                                                                                                                | 121 |     | 149 | °C    |

| T <sub>otclear</sub> | Over-temp warning flag clear | The return temperature when the warning flag is cleared                                                                                                              | 103 |     | 127 | °C    |

## 6.5.4 TX Timeout Watchdog

| Symbol                | Parameter                          | Conditions | Min | Тур | Max | Units |

|-----------------------|------------------------------------|------------|-----|-----|-----|-------|

| t <sub>lin_wdog</sub> | Time out duration (dominant state) |            | 0.5 | 1   | 2   | S     |

## 6.6 Vcc Undervoltage Reset and Window Watchdog

The values in this table are valid for normal and standby modes. All parameters are tested, unless mentioned otherwise.

| Symbol           | Parameter                                        | Conditions                                                                       | Min    | Тур     | Max     | Units |

|------------------|--------------------------------------------------|----------------------------------------------------------------------------------|--------|---------|---------|-------|

| Vuvr_off         | Vcc under-voltage threshold off (Default)        | Rising edge of VCC                                                               | 2.55   |         | 2.95    | V     |

| Vuvr_on          | Vcc under voltage threshold on (Default)         | Falling edge of VCC                                                              | 2.3    |         | 2.7     | ٧     |

| Vuvr1_off        | Vcc under voltage threshold off (Factory Option) | Rising edge of Vcc <sup>1</sup>                                                  | 3.0    |         | 3.4     | V     |

| Vuvr1_on         | Vcc under voltage threshold on (Factory Option)  | Falling edge of Vcc <sup>1</sup>                                                 | 2.75   |         | 3.15    | V     |

| Vuvr2_off        | Vcc under voltage threshold off (Factory Option) | Rising edge of VCC <sup>1</sup>                                                  | 3.5    |         | 3.9     | V     |

| Vuvr2_on         | Vcc under voltage threshold on (Factory Option)  | Falling edge of Vcc <sup>1</sup>                                                 | 3.25   |         | 3.65    | V     |

| Vuvr3_off        | Vcc under-voltage threshold off (Factory Option) | Rising edge of Vcc <sup>1</sup>                                                  | 4.0    |         | 4.4     | V     |

| Vuvr3_on         | Vcc under voltage threshold on (Factory Option)  | Falling edge of Vcc <sup>1</sup>                                                 | 3.75   |         | 4.15    | V     |

| Vhyst_vcc        | Hysteresis of under-voltage threshold on/off Vcc | Default and all other factory options                                            | 0.1    | 0.25    | 0.4     | ٧     |

| t <sub>rr</sub>  | Spike filter on VCC                              | To remove disturbance                                                            | 4      |         |         | μs    |

| Vsuvr_off        | VSUP under-voltage threshold off                 |                                                                                  |        | 3.85    |         | V     |

| Vsuvr_on         | VSUP under-voltage threshold on                  | BOR level (considered to be the Master<br>Reset for AS8530)                      |        | 3.25    |         | ٧     |

| WD_TCL           | WWD non-service time (if factory enabled)        | RESET will be generated <sup>1 2</sup>                                           | 0-75   | 0 -100  | 0-125   | ms    |

| WD_TSV           | WWD Service – time<br>(if factory enabled)       | RESET will not be generated <sup>1</sup>                                         | 75-150 | 100-200 | 125-250 | ms    |

| t <sub>Res</sub> | Reset delay time                                 | 4ms, 16ms, 32ms (typ) are factory options (min = -25% and max = +50% of typical) | 6      | 8       | 12      | ms    |

| $T_{shd}$        | Temporary shutdown reset active time             |                                                                                  | 0.1    |         | 1       | s     |

<sup>1.</sup> These are factory options which could be made available on specific request.

<sup>2. -40%, -20%, +20%, +60%,</sup> and +100% timings are available as factory options.

## 6.7 Two Port Serial Interface

| Symbol                     | Parameter                                            | Conditions                                         | Min | Тур | Max | Units  |

|----------------------------|------------------------------------------------------|----------------------------------------------------|-----|-----|-----|--------|

| General                    |                                                      |                                                    |     |     |     |        |

| BR <sub>2WIRE_SPI</sub>    | Bit rate                                             |                                                    |     |     | 250 | Kbps   |

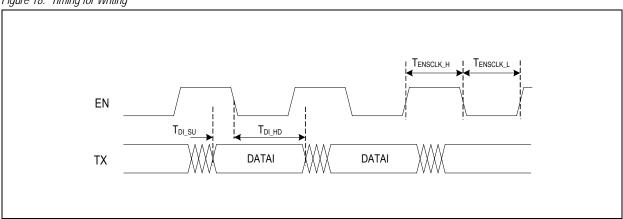

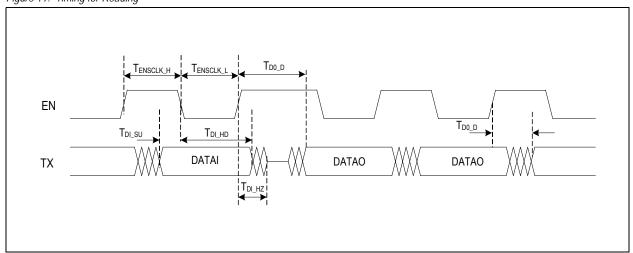

| T <sub>ENSCLK_H</sub>      | Clock high time                                      |                                                    | 2   |     |     | μs     |

| T <sub>ENSCLK_L</sub>      | Clock low time                                       |                                                    | 2   |     |     | μs     |

| Write timing               |                                                      |                                                    |     |     |     |        |

| t <sub>DI_SU</sub>         | Data in setup time                                   |                                                    | 20  |     |     | ns     |

| t <sub>DI_HD</sub>         | Data in hold time                                    |                                                    | 10  |     |     | ns     |

| Read timing                |                                                      |                                                    |     |     |     |        |

| t <sub>DO_S</sub>          | Data out setup time                                  |                                                    | 130 |     |     | ns     |

| tDO_HD                     | Data out hold time                                   |                                                    | 135 |     |     | ns     |

| t <sub>DO_D</sub>          | Data out delay                                       |                                                    |     |     | 80  | ns     |

| t <sub>DI_HZ</sub>         | Data in to high impedance delay                      | Time for the Microcontroller to release the TX bus |     |     | 80  | ns     |

| Timing parameter           | s when entering 2-Wire SP mode                       |                                                    |     |     |     |        |

| T <sub>tx_su</sub>         | TX setup time before EN goes Low                     |                                                    | 20  |     |     | ns     |

| T <sub>tx_hd</sub>         | TX hold time after EN goes High                      |                                                    | 20  |     |     | ns     |

| T <sub>tx_SP_trigger</sub> | EN falling edge to TX falling edge                   | To enter into 2-Wire SP mode                       | 2   |     | 10  | μs     |

| T <sub>STNDY_trigger</sub> | TX high time from EN falling edge                    | To enter into Sleep/Standby mode                   | 5   |     |     | cycles |

| T <sub>en_ENSCLK</sub>     | EN falling edge to start of 2-wire serial port clock |                                                    | 5   |     |     | cycles |

# 7 Detailed Description

The AS8530 chip consists of a low drop-out regulator and a LIN bus transceiver, which is a bi-directional bus interface for data transfer between LIN bus and the LIN protocol controller. Additionally integrated is a RESET unit with a power-on-reset delay and a programmable window watchdog. It also includes a watchdog time-out on LIN TX node to indicate if the microcontroller is stuck in a loop and to release unintentional LIN bus dominant state.

### 7.1 Voltage Regulator (LDO)

The voltage regulator has three operating modes. The features of the operating modes are given below:

- Normal mode: Stability to be better ±0.25V over input range and temperature for load current up to 50mA. The LDO Output provides a voltage of 5V or 3.3V as OTP option.

- Standby mode: The Standby mode is a low quiescent current mode used in car applications that are always switched on. The load current in standby mode is 5mA. Quiescent current (no load) is less than 45mA typically at room temperature.

- Sleep mode: Power down or temporary shutdown of the regulator can be set by a register bit. This bit can be written through 2-wire MCU interface

The LDO takes the input from bandgap and scales it up to the required voltage. The LDO starts charging only after the POR-VSUP event occurs (RESET\_VSUP\_N switched from low to high). The LDO can be powered-down by a control signal (temporary shutdown register) for the temporary shutdown mode.

#### 7.2 Temperature Limiter

Temperature limiter produces a power down when temperature exceeds 155°C ±10%. It powers up and generates a reset when it returns to 135°C ±10% junction temperature. During thermal shut down, temperature sensor is supplied by VSUP. During the temperature ramp-up phase, as soon as the temperature exceeds 135°C ±10%, a warning signal is issued and is written into the diagnostic register, which can be read through the SP interface.

#### 7.3 VSUP Undervoltage Reset

VSUP undervoltage reset generates a reset RESET\_VSUP\_N, switched from low to high when VSUP ramps up above VSUVR\_OFF. This is used to enable proper initialization of mode control and diagnostic registers. If VSUP < VSUVR\_ON, then RESET\_VSUP\_N switches from high level to low level (active). This is considered to be the master reset and will have the highest priority over all other signals. As soon as VSUP < VSUVR\_ON, the LDO, LIN Transceiver is completely shut off and system comes to a complete stop. AS8530 enters into the normal operating mode only after VSUP > VSUVR\_OFF.

#### 7.3.1 VSUP Undervoltage in Normal Mode

Supply Voltages below VSUVR\_OFF and above VSUVR\_ON do not influence the voltage regulator. The output voltage Vcc follows VSUP.

#### 7.3.2 VSUP Undervoltage in Standby Mode / Sleep Mode

No exit from the sleep mode or standby mode take place if the VSUP voltage drops down to VSUVR\_OFF. If VSUP goes below VSUVR\_ON, RESET\_VSUP\_N is active and resets the mode control and diagnostic register. The voltage regulator, LIN Transceiver modules are turned off. If VSUP rises again above VSUVR\_OFF, RESET\_VSUP\_N is switched from low to high. The system enters normal mode where LIN Transceiver and LDO are switched on.

#### 7.3.3 VSUP Undervoltage in Low Slew Mode

The behavior of AS8530 at low VSUP voltages is equal to the sleep mode. The low slew mode (set by control register through serial interface as an option) will be cancelled, if VSUP drops below VSUVR\_ON in this mode. The AS8530 enters the normal mode, if VSUP rises again above VSUVR OFF.

#### 7.4 RESET

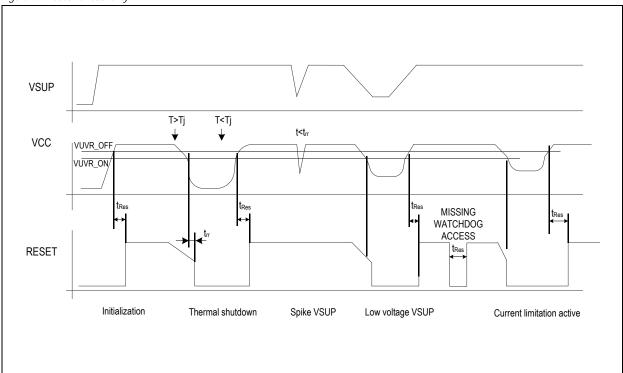

Reset generates an external RESET signal to reset the microcontroller and all other external circuits. The reset functionality is illustrated in Figure 4. Reset consists of a digital buffer at the output. RESET signal can be affected by RESET\_VCC\_N (which is the under-voltage reset on VCC) and Window watchdog output. All those conditions which cause a drop in the VCC voltage will be detected from the low voltage reset unit, which in-turn generates a reset signal. States like Temporary shut-down, Over-temperature monitor will influence the RESET output through RESET\_VCC\_N signal only.

#### 7.5 Vcc Undervoltage Reset

The POR-VCC generates RESET\_VCC\_N signal as output which determines under-voltage reset of the output of the LDO. The rising edge of the Vcc gives an under-voltage reset "off" and the falling edge of the Vcc gives an under-voltage reset "on". This under-voltage signal is used to control the RESET output. When Vcc rises up Vuvr\_off for a period greater than reset duration (tRes) then RESET\_VCC\_N switches from low level to high level and pin RESET is inactive (high). If Vcc falls below Vuvr\_on for a period greater than a predetermined delay (trr) then RESET\_VCC\_N switches from high level to low level and pin RESET is active (low). The RESET\_VCC\_N signal is used to initializes Window watchdog timer, TX time-out, Test control circuits, 2-wire SP, and logic associated with SP (everything other than the SP control registers). Vcc under-voltage reset threshold voltage level adjustment can be made by 2 bit OTP as explained in OTP interface.

#### 7.6 Window Watchdog (WWD)

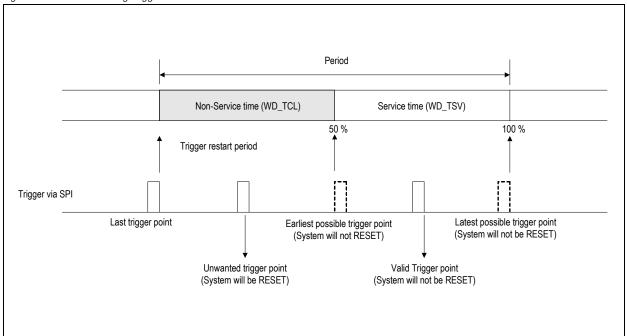

To keep the external microcontroller always in proper function state, a window watchdog circuit is implemented. The WWD trigger is generated by external MCU through SP interface. If the window is missed, a reset on the RESET pin with certain reset time (t<sub>Res</sub>) is generated. The WWD function can be enabled or disabled by factory setting. The watchdog is started after the ASSP exits reset. Under normal working conditions, microcontroller gives a WWD trigger every time in the window period of WD\_TSV (service time). If the trigger does not occur during WD\_TSV or occurs too early during WD\_TCL (non-service time), then RESET output is pulled low (active), which will reset the micro-controller. WWD circuit is turned on after the RESET pin goes back to high (inactive). If Vcc < Vuvr\_on, WWD circuit is switched off. When the WWD function is enabled, there is a 3-bit factory programming available to set the trigger window.

Figure 5. Window Watchdog Trigger

#### 7.7 LIN Transceiver

The transceiver provides short circuit limitation, hardware watchdog and over temperature shut down features. The TX watchdog timer is active when TX is pulled low (active). As soon as the TX watchdog timeout occurs, the LIN bus is released from dominant state to recessive state. The LIN transceiver has a pull-up resistor (for the slave node; extra resistor externally for the master node) to the VSUP. A diode protection is available to protect it from back supply from bus line.

The LIN transmitter has the basic functionality of relaying the data from the micro-controller on to the LIN. The data on the LIN needs to have controlled slew to have reduced EMI. The receiver relays the data from the LIN to the micro-controller. This transmitter has optimized EMC performance across different loading conditions conforming to the LIN 2.1 standards. The wake-up detects a wake up event on the LIN.

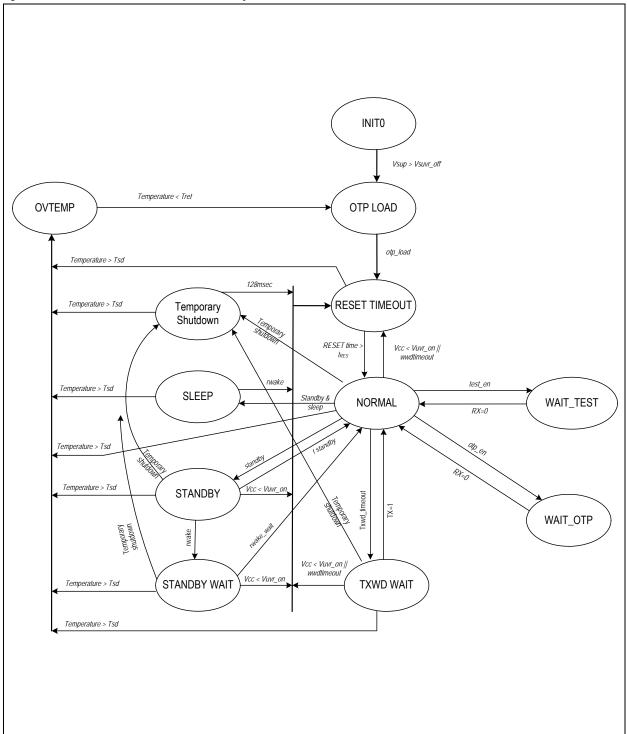

#### 7.8 Operating Modes and States

The AS8530 provides four main operating modes "normal", "sleep/stand-by" (programmed by OTP), "temporary shutdown" and "thermal shutdown". The LIN transceiver can be programmed to operate with lower slew in the normal mode. Refer to Table 3 for a detailed description on transition for each mode.

#### 7.8.1 Normal Mode

This is the mode after the power-up. In normal mode, LDO, LIN Transceiver, Window Watchdog, Resistive divider and the line drivers are all turned on. All the blocks are completely functional. LDO is now capable of delivering maximum load current possible as per the device specifications. The LIN Transceiver is capable of sending the TX data from microcontroller to the LIN bus at a maximum rate of 20Kbps. EN signal is set to high and LIN, TX, RX pins can be driven into dominant (low) or recessive (high) states. If the junction temperature increases more than Totset, a warning flag is set in the diagnostic register, which can be read through the 2-wire interface.

#### 7.8.2 Standby Mode

Standby mode is a functional low-power mode where LIN Transceiver is disabled. The LIN wake-up circuit and over-temperature monitor circuit is enabled. Window watchdog, TX timeout watchdog, Resistive divider, relay driver circuits are disabled. EN pin held low in this mode. TX pin is in recessive state (high). CS is pulled to VCC while SDI and SCLK outputs are pulled to VSS.

#### 7.8.3 Sleep Mode

As a factory programming option on request the AS8530 offers as a replacement to the standby mode with sleep mode. Sleep mode is the most current saving mode. If EN is held low, the LDO, LIN Transceiver and the reset and window watchdog unit will be switched off. Vcc is pulled down to zero. The LIN wake-up circuit, oscillator and over-temperature monitor circuit is active. LIN bus is in recessive state (high). Only wake-up possible is through remote wake-up, through LIN pin, pulling it to dominant state for 100µs typical (low), can change the state of the system.

#### 7.8.4 Temporary Shutdown Mode

In this mode, the VCC is pulled down and the LDO is powered down. This mode is introduced to interface with other components which do not have a pin for the reset functionality. This provides an alternative way to reset those components interfacing with AS8530. This mode is default disabled but can be enabled by an OTP option. In this mode, all internal modules supplied by the LDO are disabled. Only the oscillator, control registers are enabled. The VCC output can be temporarily switched off and pulled to VSS. EN signal, RX, TX is pulled low and LIN Transceiver along with the LIN wake-up circuit is powered down. No remote wake-up functionality is possible. LIN bus enters into recessive state. The system goes out of this mode to normal mode after the time-out of an internal counter delay (T<sub>shd</sub>). Normal mode to temporary shutdown transition will be controller by register bit in configuration register.

#### 7.8.5 Thermal Shutdown State

If the junction temperature  $T_J$  is higher than  $T_{sd}$ , the AS8530 will be switched into the thermal shutdown mode. The transceiver is completely disabled. No wake-up functionality is available. Window watchdog, TX timeout watchdog, and LDO are completely turned off. Only the over-temperature monitor would be working. As soon as the temperature returns back to  $T_{ret}$ , the system enters normal mode. For more information on transition, see Table 3.

Table 3. Transition Table

| Transition                    |                       | Interface |                  |                | Reg.             | Flags          |       |                  |          |          |                                                        |

|-------------------------------|-----------------------|-----------|------------------|----------------|------------------|----------------|-------|------------------|----------|----------|--------------------------------------------------------|

| From mode                     | To mode               | LIN       | RX               | TX             | EN               | 0x05<br>D0     | rwake | Uvbat            | ОТ       | Uvcc     | Comments                                               |

|                               | Stand-By              | X-RS      | X-H <sup>2</sup> | H <sup>3</sup> | H-L <sup>3</sup> | L              | Х     | Х                | inactive | inactive | TX is high for T <sub>STNDY_triggerr</sub>             |

| Normal                        | Sleep <sup>1</sup>    | X-RS      | X-H <sup>2</sup> | H <sup>3</sup> | H-L <sup>3</sup> | L              | Х     | Х                | inactive | set      | TX is high for T <sub>STNDY_triggerr</sub> 1           |

| Mode                          | Temporary<br>Shutdown | X-RS      | X-H <sup>2</sup> | Χ              | H <sup>3</sup>   | Н              | Х     | Х                | inactive | set      | The Control Bit is set through the 2-Wire SP interface |

|                               | Over-<br>Temperature  | X-RS      | X-H <sup>2</sup> | X              | Χ                | L              | Χ     | Х                | set      | set      |                                                        |

|                               | Normal (LW)           | Х         | H-X <sup>2</sup> | Χ              | L-H <sup>3</sup> | L              | Х     | Х                | inactive | inactive |                                                        |

|                               | Normal (RW)           | Х         | H-X <sup>2</sup> | Н              | Х                | L              | set   | Х                | inactive | inactive | Remote Wake up<br>Event occurred on LIN                |

| Stand-By<br>Mode              | Temporary<br>Shutdown | RS        | H <sup>2</sup>   | Н              | L                | H <sup>3</sup> | Х     | Х                | inactive | set      | The Control Bit is set through the 2-Wire SP interface |

|                               | Over-<br>Temperature  | RS        | H <sup>2</sup>   | Н              | L                | L              | Х     | Х                | set      | set      |                                                        |

| Temporary<br>Shutdown<br>Mode | Normal                | RS-X      | H-X <sup>2</sup> | Х              | Х                | L              | Х     | Х                | inactive | clear    | Internal 128ms timer expired                           |

|                               | Normal                | RS-X      | H-X <sup>2</sup> | Х              | Х                | L              | set   | Х                | inactive | clear    | Remote Wake up<br>Event occurred on LIN                |

| Sleep Mode <sup>3</sup>       | Over-<br>Temperature  | RS        | H <sup>2</sup>   | Х              | Х                | L              | Х     | Х                | set      | hold     | Temperature monitor output asserted (covered by scan)  |

| All States                    | Power Off             | Х         | Х                | Х              | Х                | Χ              | Х     | L-H <sup>3</sup> | Х        | Х        |                                                        |

- 1. Chosen by factory programming option

- 2. Effect of Transition

- 3. Cause for Transition

Note: L = low state, H = high state, OT = Over-temperature Reset, Uvcc = Undervoltage Vcc, Uvbat = Undervoltage VBAT, rwake =remote wake, X = do not care.

## 7.9 State Diagram

The complete functional state machine for AS8530 is illustrated in Figure 6. Some soft-states in the FSM like "TXWD Wait", "Standby Wait" and other "wait" states have been included for the sake of completeness.

Figure 6. Finite State Machine Model for the AS8530 System

# 8 Application Information

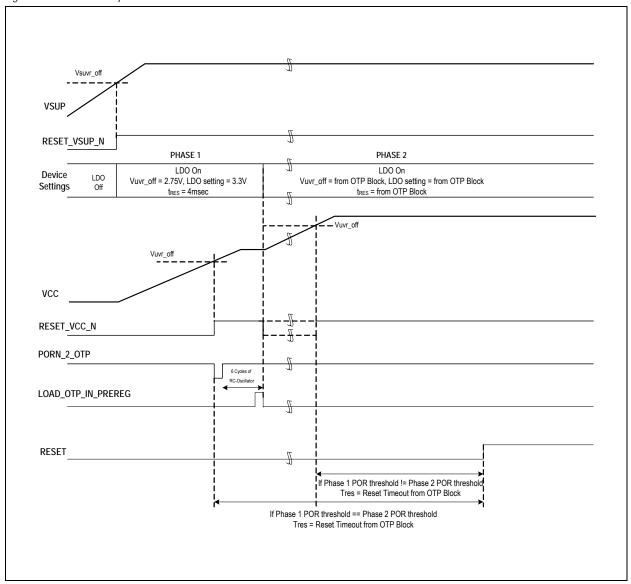

#### 8.1 Initialization

When the power supply is switched on, if VSUP > VSUVR\_OFF, RESET\_VSUP\_N becomes inactive (high). After this, the voltage regulator starts with a default LDO output setting of 3.3V and Vuvr\_off setting of 2.75V. If Vcc > Vuvr\_off (2.75V), active-low PORN\_2\_OTP is generated. The rising edge of PORN\_2\_OTP loads contents of fuse onto the OTP latch after load access time  $T_{Load}$ . LOAD\_OTP\_IN\_PREREG signal loads contents of OTP latch onto the pre-regulator domain register. This register gives actual settings of LDO, Vuvr\_off and Reset Timeout period  $T_{Res}$ . This is done because the OTP block is powered by the Vcc. If Vcc > Vuvr\_off (phase 2), Reset timeout is restarted. RESET signal is deasserted after Reset Timeout period  $T_{Res}$  (phase 2) and then device enters into normal mode. The circuit initializes correctly also for very slow ramp on VsuP (of the order of 0.5V/min).

Figure 7. Initialization Sequence for AS8530

Table 4. VSUP>Vsuvr\_on and Vcc<Vuvr\_on

| Block                                                             | Output Signal                  |

|-------------------------------------------------------------------|--------------------------------|

| TRANSCEIVER = Enabled (disabled only during initial VSUP ramp-up) | LIN = high-z, RX = follows V   |

| LDO = Enabled (disabled only during initial ramp-up)              | Vcc = low                      |

| RELAY DRIVER = Enabled                                            | LDRIVE1 = high, LDRIVE2 = high |

| RESET = Enabled                                                   | RESET = high-z                 |

| RESISTIVE DIVIDER = Enabled                                       | VBAT= high, VBAT_DIV = enabled |

Table 5. VSUP<Vsuvr\_on

| Block                        | Output Signal                  |

|------------------------------|--------------------------------|

| TRANSCEIVER = Disabled       | LIN = high-z, RX = high-z      |

| LDO = Disabled               | Vcc = low                      |

| RELAY DRIVER = Disabled      | LDRIVE1 = high, LDRIVE2 = high |

| RESET = Disabled             | RESET = high-z                 |

| RESISTIVE DIVIDER = Disabled | VBAT = high, VBAT_DIV = low    |

#### 8.2 Wake-Up

If the regulator is put into sleep/standby mode, it can be woken up with the BUS interface. A transition on the BUS (high to low) with a minimum predefined low time (twake) puts the regulator into normal mode.

### 8.3 Over-Temperature Shutdown

If the junction temperature increases beyond  $T_{sd}$  the over-temperature recognition will be activated and the regulator voltage will be switched off. The Vcc voltage drops down, the reset state is entered and the bus transceiver is switched off (recessive state). After TJ falls below  $T_{ret}$ , the AS8530 will be initialized again. This initialization starts independently from the voltage levels on EN and BUS. Within the thermal shutdown mode, the transceiver cannot switch to the normal mode either with local or with remote wake-up. The operation of the AS8530 is possible between TJ (125°C) and the switch off temperature  $T_{sd}$ , but small parameter differences can appear. After over-temperature switch-off, the IC initializes as explained in Initialization on page 18. The low slew mode for LIN Transceiver has to be selected again on re-initialization, if necessary.

### 8.4 LIN BUS Transceiver

The AS8530 has an integrated bi-directional bus interface device for data transfer between LIN bus and the LIN protocol controller. The transceiver consists of a driver with slew rate control, wave shaping and current limitation and a receiver with high voltage comparator followed by a de-bouncing unit.

#### 8.4.1 Transmit Mode

During transmission the data at the pin TX will be transferred to the BUS driver to generate a bus signal. To minimize the electromagnetic emission of the bus line, the BUS driver has an integrated slew rate control and wave shaping unit.

Transmitting will be interrupted in the following cases:

- Sleep mode

- Thermal Shutdown active

- Master Reset (VSUP < Vsuvr\_on)</p>

The recessive BUS level is generated from the integrated 30k pull up resistor in serial with an active diode This diode prevents the reverse current of VBUS during differential voltage between VSUP and BUS (VBUS>VSUP). No additional termination resistor is necessary to use the AS8530 in LIN slave nodes. If this IC is used for LIN master nodes it is necessary that the BUS pin is terminated via an external  $1k\Omega$  resistor in series with a diode to VBAT.

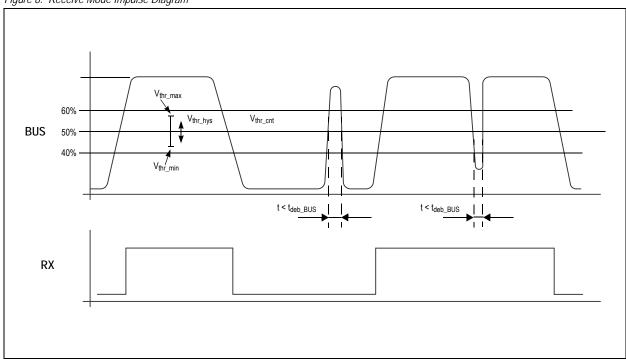

#### 8.4.2 Receive Mode

The data signals from the BUS pin will be transferred continuously to the pin RX. Short spikes on the bus signal are suppressed by the implemented de-bouncing circuit. Including all tolerances the LIN specific receive threshold values of 0.4\*Vsup and 0.6\*Vsup will be securely observed.

Figure 8. Receive Mode Impulse Diagram

#### 8.5 RX and TX Interface

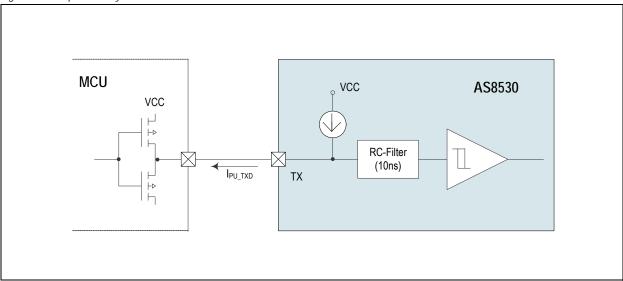

#### Input TX.

The 5V input TX controls directly the BUS level. LIN Transmitter acts like a slew-controlled level shifter. A dominant state (low) on TX leads to the LIN bus being pulled low (dominant state) too. The TX pin has an internal active pull up connected to Vcc. This guarantees that an open TX pin generates a recessive BUS level.

Figure 9. TX Input Circuitry

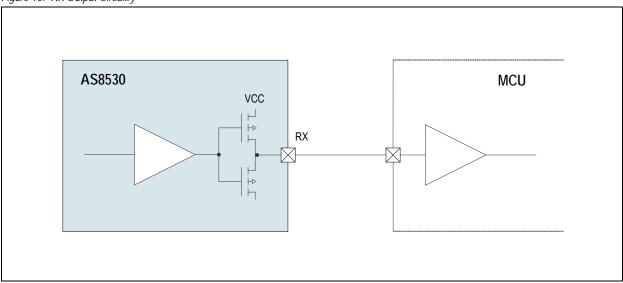

#### Output RX.

The received BUS signal will be output to the RX pin:

BUS < Vthr\_cnt -0.5 \* Vthr\_hys  $\rightarrow$  RX = low

BUS > Vthr\_cnt + 0.5 \* Vthr\_hys  $\rightarrow$  RX = high

This output is a push-pull driver between VCC and GND with an output current of 1mA.

Figure 10. RX Output Circuitry

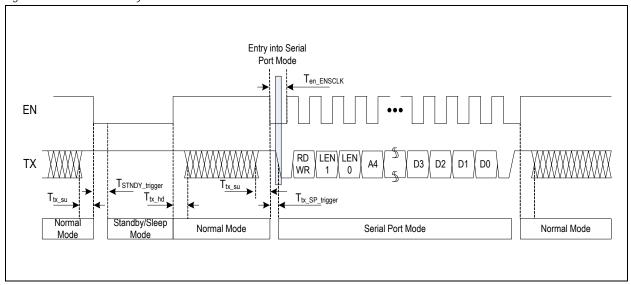

### 8.6 MODE Input EN

The AS8530 is switched from normal mode to the standby/sleep mode with a falling edge on EN and keeping TX high for  $T_{STNDY\_trigger}$  time. Device is switched from standby mode to normal mode with a rising edge at the EN pin. The mode change for AS8530 with a falling edge at EN can be done independently from the state of the bus transceiver. Device enters into Serial port mode by forcing EN low and driving TX high to low within  $T_{tx\_SP\_trigger}$  time after EN forced to low.

This ensures the direct control of device to enter into Standby/Sleep mode by microcontroller using EN pin.

Figure 11. EN Pin Functionality

The EN input has an internal active pull down to secure that if this pin is not connected, a low level will be generated.

Figure 12. Enable Controlled via. MCU

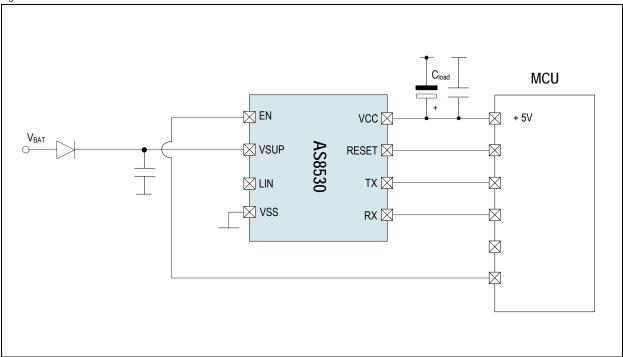

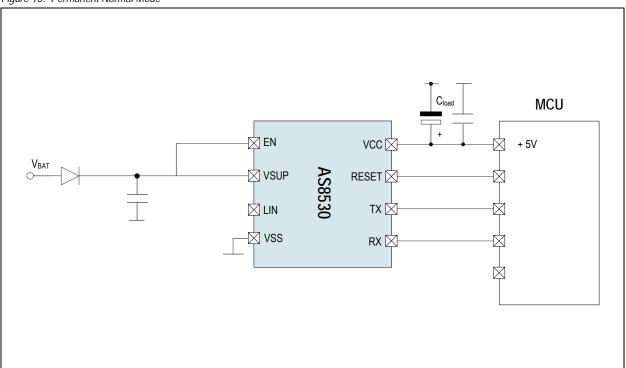

If the application doesn't need the wake up capability of the AS8530, a direct connection EN to VCC is possible. In this case the AS8530 operates in permanent normal mode. Also possible is the external (outside of the module) control of the EN line via. VSUP signal as shown below.

Figure 13. Permanent Normal Mode

#### 8.7 Serial Port Interface

The interface is essentially used to trigger the window watchdog, to access test mode and read out diagnostic information for the AS8530. The description of this interface and the protocol is explained below. Information on block status and errors can be displayed by diagnosis registers.

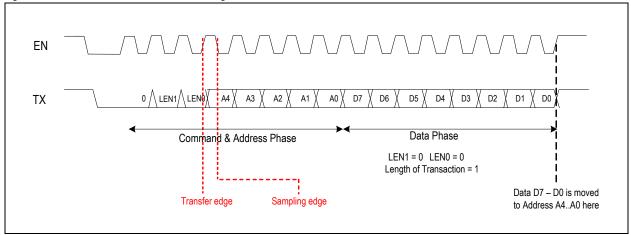

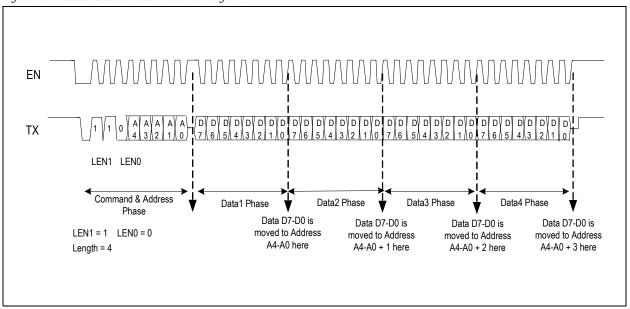

#### 8.7.1 Device Configuration using 2-Wire Serial Port

The AS8530 device configuration register is programmed via a 2-wire Serial Programming Interface. EN/SCL is used as Serial Clock and TX/SDA\_IO is used as Serial Data. EN is used as clock input to access serial port registers in serial port mode. Also EN is used to control transition from normal mode to standby/sleep mode. The TX input of the device will be multiplexed as following:

- LIN TX for transmitting data from microcontroller on LIN bus

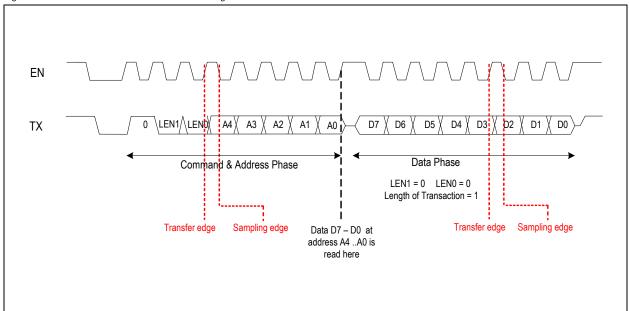

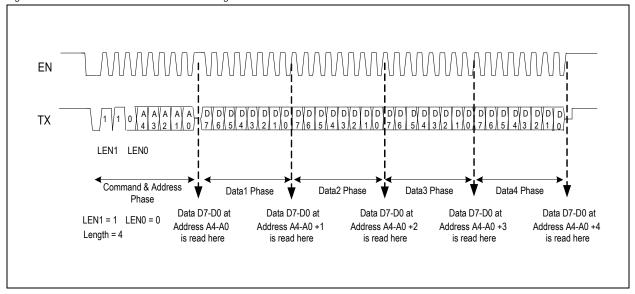

- SDA\_IO for Serial data input/output, this will be used for serially accessing data from configuration and status register