# 2.5V PHASE LOCKED LOOP CLOCK DRIVER

IDTCSPT855

#### **FEATURES**:

- PLL clock driver for DDR (Double Data Rate) synchronous DRAM applications

- · Spread spectrum clock compatible

- · Operating frequency: 60MHz to 180MHz

- · Low jitter (cycle-to-cycle): ±50ps

- Distributes one differential clock input to four differential clock outputs

- Enters low power mode and 3-state outputs when input CLK signal is less than 20MHz or PWRDWN is low

- · Operates from dual 2.5V supplies

- Consumes <200µA quiescent current</li>

- External feedback pins (FBIN, FBIN) are used to synchronize outputs to input clocks

- · Available in TSSOP package

### **DESCRIPTION:**

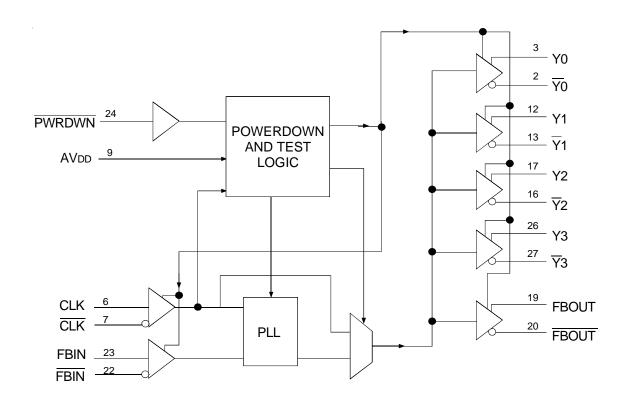

The CSPT855 is a high-performance, low-skew, low-jitter zero delay buffer that distributes one differential clock input pair (CLK,  $\overline{\text{CLK}}$ ) to four differential output pairs (Y [0:3],  $\overline{\text{Y}[0:3]}$ ) and one differential pair of feedback clock outputs (FBOUT,  $\overline{\text{FBOUT}}$ ). When  $\overline{\text{PWRDWN}}$  is high, the outputs switch in phase and frequency with CLK. When  $\overline{\text{PWRDWN}}$  is low, all outputs are disabled to a high-impedance state (3-state), and the PLL is shut down (low-power mode). The device also enters this low-power mode when the input frequency falls below a suggested detection frequency that is below 20MHz (typical 10MHz). An input frequency detection circuit detects the low-frequency condition, and after applying a >20MHz input signal, this detection circuit reactivates the PLL and enables the outputs.

When AVDD is tied to GND, the PLL is turned off and bypassed for test purposes. The CSPT855 is also able to track spread spectrum clocking for reducted EMI.

Since the CSPT855 is based on PLL circuitry, it requires a stabilization time to achieve phase-lock of the PLL. This stabilization time is required following power up.

## FUNCTIONAL BLOCK DIAGRAM

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

COMMERCIAL AND INDUSTRIAL TEMPERATURE RANGES

APRIL 2003

## **PIN CONFIGURATION**

TSSOP TOP VIEW

## ABSOLUTE MAXIMUM RATINGS(1)

| Symbol                          | Rating                    | Max                            | Unit |

|---------------------------------|---------------------------|--------------------------------|------|

| Vddq, AVdd                      | Supply Voltage Range      | -0.5 to +3.6                   | V    |

| VI <sup>(2)</sup>               | Input Voltage Range       | -0.5 to V <sub>DDQ</sub> + 0.5 | V    |

| Vo <sup>(2)</sup>               | Output Voltage Range      | -0.5 to V <sub>DDQ</sub> + 0.5 | V    |

| lik (Vi < 0 or                  | Input Clamp Current       | ±50                            | mA   |

| VI < VDDQ)                      |                           |                                |      |

| lok (Vo < 0 or                  | Output Clamp Current      | ±50                            | mA   |

| Vo > Vddq)                      |                           |                                |      |

| lo                              | Continuous Output Current | ±50                            | mA   |

| (VO = 0  to  VDDQ)              |                           |                                |      |

| VDDQ or GND                     | Continuous Current        | ±100                           | mA   |

| θ <sub>J</sub> Α <sup>(3)</sup> | Package Thermal Impedance | 105.8                          | °C/W |

| Tstg                            | Storage Temperature Range | - 65 to +150                   | °C   |

#### NOTES:

- Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause

permanent damage to the device. This is a stress rating only and functional operation

of the device at these or any other conditions above those indicated in the operational

sections of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect reliability.

- The input and output negative-voltage ratings may be exceeded if the input and output clamp-current ratings are observed. This value is limited to 3.6V maximum.

- 3. The package thermal impedance is calculated in accordance with JESD 51.

## **PIN DESCRIPTION**

| Pin Name     | Pin Number           | I/O | Description                                         |

|--------------|----------------------|-----|-----------------------------------------------------|

| AGND         | 10                   |     | Ground for 2.5V analog supply                       |

| AVDD         | 9                    |     | 2.5V analog supply                                  |

| CLK, CLK     | 6, 7                 | I   | Differential clock input                            |

| FBIN, FBIN   | 23,22                | - 1 | Feedback differential clock input                   |

| FBOUT, FBOUT | 19,20                | 0   | Feedback differential clock output                  |

| GND          | 1, 5, 14, 15, 28     |     | Ground                                              |

| PWRDWN       | 24                   | 1   | Control input to turn device in the power-down mode |

| VDDQ         | 4, 8, 11, 18, 21, 25 |     | 2.5V supply                                         |

| Y[0:3]       | 3, 12, 17, 26        | 0   | Buffered output copies of input clock, CLK          |

| Y[0:3]       | 2, 13, 16, 27        | 0   | Buffered output copies of input clock, CLK          |

## FUNCTION TABLE(1)

| INPUTS     |        |                       |                       |   | OUTPUTS |       |       |              |

|------------|--------|-----------------------|-----------------------|---|---------|-------|-------|--------------|

| AVDD       | PWRDWN | CLK                   | CLK                   | Υ | Ÿ       | FBOUT | FBOUT | PLL          |

| GND        | Н      | L                     | Н                     | L | Н       | L     | Н     | Bypassed/OFF |

| GND        | Н      | Н                     | L                     | Н | L       | Н     | L     | Bypassed/OFF |

| X          | L      | L                     | Н                     | Z | Z       | Z     | Z     | OFF          |

| Х          | L      | Н                     | L                     | Z | Z       | Z     | Z     | OFF          |

| 2.5V (nom) | Н      | L                     | Н                     | L | Н       | L     | Н     | ON           |

| 2.5V (nom) | Н      | Н                     | L                     | Н | L       | Н     | L     | ON           |

| 2.5V (nom) | Х      | <20MHz <sup>(2)</sup> | <20MHz <sup>(2)</sup> | Z | Z       | Z     | Z     | OFF          |

#### NOTES:

- 1. H = HIGH Voltage Level

- L = LOW Voltage Level

- Z = High-Impedance OFF-State

- X = Don't Care

- 2. Typically 10MHz.

## RECOMMENDED OPERATING CONDITIONS(1)

| Symbol     | Paramet                                                    | ter                                    | Min.          | Тур.   | Max.         | Unit |

|------------|------------------------------------------------------------|----------------------------------------|---------------|--------|--------------|------|

| AVDD, VDDQ | Supply Voltage                                             |                                        | 2.3           | _      | 2.7          | V    |

| VIL        | Input Voltage LOW                                          | CLK, CLK, FBIN, FBIN                   | _             | _      | VDDQ/2-0.18  | V    |

|            |                                                            | PRWDWN                                 | - 0.3         | _      | 0.7          |      |

| Vih        | Input Voltage HIGH                                         | CLK, CLK, FBIN, FBIN                   | VDDQ/2 + 0.18 | _      | _            | V    |

|            |                                                            | PRWDWN                                 | 1.7           | _      | VDDQ/2 + 0.3 |      |

|            | DC Input Signal Voltage <sup>(2)</sup>                     | DC Input Signal Voltage <sup>(2)</sup> |               | _      | VDDQ         | V    |

| Vid        | Differential Input Signal Voltage <sup>(3)</sup> CLK, FBIN |                                        | 0.36          | _      | VDDQ + 0.6   | V    |

| Vo(x)      | Output Differential Cross-Voltage <sup>(4)</sup>           |                                        | VDDQ/2 - 0.2  | VDDQ/2 | VDDQ/2 + 0.2 | V    |

| VI(X)      | Input Differential Pair Cross-Voltage(4)                   |                                        | VDDQ/2 - 0.2  | _      | VDDQ/2 + 0.2 | V    |

| Іон        | HIGH-Level Output Current                                  |                                        | _             | _      | - 12         | mA   |

| loL        | LOW-Level Output Current                                   |                                        | _             | _      | 12           | mA   |

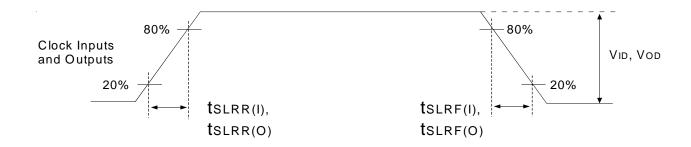

| SR         | Input Slew Rate, see figure 8                              |                                        | 1             | _      | 4            | V/ns |

| TA         | Operating Free-Air Temperature                             | Commercial                             | 0             |        | +70          | °C   |

|            |                                                            | Industrial                             | -40           | _      | +85          |      |

#### NOTES:

- 1. Unused inputs must be held HIGH or LOW to prevent them from floating.

- 2. DC input signal voltage specifies the allowable DC execution of differential input.

- 3. Differential input signal voltage specifies the differential voltage |  $V_{TR}$   $V_{CP}$  | required for switching, where  $V_{TR}$  is the true input level and  $V_{CP}$  is the complementary input level.

- 4. Differential cross-point voltage is expected to track variations of VDDQ and is the voltage at which the differential signals must be crossing.

## DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE

Following Conditions Apply Unless Otherwise Specified:

Commercial: TA =  $0^{\circ}$ C to  $+70^{\circ}$ C; Industrial: TA =  $-40^{\circ}$ C to  $+85^{\circ}$ C

| Symbol  | Parameter                                        |              | Conditions                                                       | Min.       | Тур.(1) | Max.         | Unit |

|---------|--------------------------------------------------|--------------|------------------------------------------------------------------|------------|---------|--------------|------|

| Vik     | Input Voltage (All Inputs)                       |              | VDDQ = 2.3V, II = -18mA                                          | _          | _       | -1.2         | V    |

| Vон     | HIGH-Level Output Voltage                        | )            | VDDQ = Min. to Max., IOH = -1mA                                  | VDDQ - 0.1 | _       | _            | V    |

|         |                                                  |              | VDDQ = 2.3V, IOH = -12mA                                         | 1.7        | _       | _            |      |

| Vol     | LOW-Level Output Voltage                         |              | VDDQ = Min. to Max., IOL = 1mA                                   | _          | _       | 0.1          | V    |

|         |                                                  |              | VDDQ = 2.3V, IOL = 12mA                                          | _          | _       | 0.6          |      |

| Іон     | HIGH-Level Output Curren                         | t            | VDDQ = 2.3V, Vo = 1V                                             | -18        | - 32    | _            | mA   |

| lol     | LOW-Level Output Current                         |              | VDDQ = 2.3V, Vo = 1.2V                                           | 26         | 35      | _            | mA   |

| Vod     | Output Voltage Swing                             |              | Differential outputs are terminated with $120\Omega$             | 1.1        | _       | VDDQ-0.4     | V    |

| Vox     | Output Differential Cross Voltage <sup>(2)</sup> |              | Differential outputs are terminated with $120\Omega$             | VDDQ/2-0.2 | VDDQ/2  | VDDQ/2 + 0.2 | V    |

| lı      | Input Current                                    |              | VDDQ = 2.7V, VI = 0V to 2.7V                                     | _          | _       | ±10          | μА   |

| loz     | High-Impedance State Output Current              |              | VDDQ = 2.7V, Vo = VDDQ or GND                                    | _          | _       | ±10          | μА   |

| IDD(PD) | Power-Down Current on Vo                         | DDQ and AVDD | CLK and CLK = 0MHz, PWRDWN = LOW,                                | _          | 100     | 200          | μА   |

|         |                                                  |              | $\Sigma$ of IDD and AIDD                                         |            |         |              |      |

| IDD     | Dynamic Current on VDDQ                          | CL = 14pF    | fo = 167MHz, Differential outputs terminated with $120\Omega$    | _          | 150     | 180          | mA   |

|         |                                                  | CL = 0pF     | $fo = 167MHz$ , Differential outputs terminated with $120\Omega$ | _          | 130     | 160          |      |

| Aldd    | Supply Current on AVDD                           |              | fo = 167MHz                                                      | _          | 8       | 10           | mA   |

| Сі      | Input Capacitance                                |              | VDDQ = 2.5V, VI = VDDQ or GND                                    | 2          | 2.5     | 3            | pF   |

| Со      | Output Capacitance                               |              | VDDQ = 2.5V, VI = VDDQ or GND                                    | 2.5        | 3       | 3.5          | pF   |

#### NOTES:

- 1. All typical values are at respective nominal VDDQ.

- 2. Differential cross-point voltage is expected to track variation of VDDO and is the voltage at which the differential signals must be crossing.

## TIMING REQUIREMENTS

| Symbol         | Parameter                                       | Min. | Max. | Unit |

|----------------|-------------------------------------------------|------|------|------|

| fclk           | Operating Clock Frequency                       | 60   | 180  | MHz  |

| toc            | Input Clock Duty Cycle                          | 40   | 60   | %    |

| t_             | Stabilization Time (PLL Mode) <sup>(1)</sup>    | _    | 10   | μS   |

| t <sub>L</sub> | Stabilization Time (Bypass Mode) <sup>(2)</sup> | _    | 30   | ns   |

#### NOTES:

- 1. Recovery time required when the device goes from power-down mode into bypass mode (test mode with AVDD at GND).

- 2. Time required for the integrated PLL circuit to obtain phase lock of its feedback signal to its reference signal. For phase lock to be obtained, a fixed-frequency, fixed-phase reference signal must be present at CLK. Until phase lock is obtained, the specifications for propagation delay, skew, and jitter parameters given in the switching characteristics table are not applicable. This parameter does not apply for input modulation under SSC application.

# SWITCHING CHARACTERISTICS

| Symbol                    | Description                                         |     | Test Conditions              | Min. | Typ. <sup>(1)</sup> | Max. | Unit |

|---------------------------|-----------------------------------------------------|-----|------------------------------|------|---------------------|------|------|

| tPLH <sup>(2)</sup>       | LOW to HIGH Level Propagation Delay Time            |     | Test mode, CLK to any output | _    | 4.5                 | _    | ns   |

| t <sub>PHL</sub> (2)      | HIGH to LOW Level Propagation Delay Time            |     | Test mode, CLK to any output | _    | 4.5                 | _    | ns   |

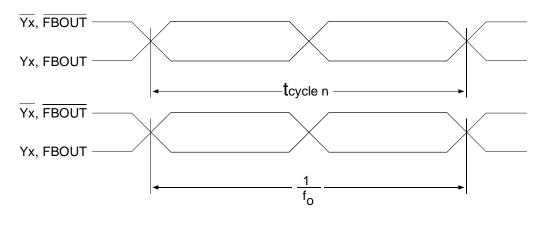

| tiit(per) <sup>(3)</sup>  | Jitter (period), see figure 6                       |     | 66MHz                        | - 55 | _                   | 55   | ps   |

|                           |                                                     |     | 100/ 133/ 167/ 180 MHz       | -35  | _                   | 35   | ]    |

| tлт(cc) <sup>(3)</sup>    | Jitter (cycle-to-cycle), see figure 2               |     | 66MHz                        | -60  | _                   | 60   | ps   |

|                           |                                                     |     | 100/ 133/ 167/ 180 MHz       | -50  | _                   | 50   | ]    |

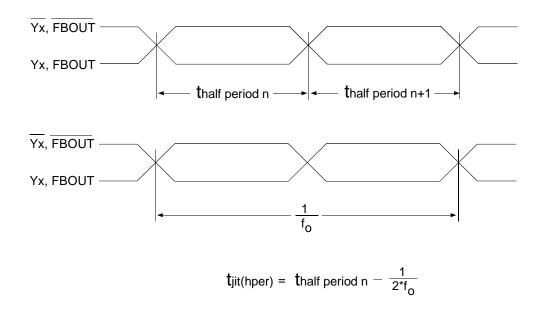

| tJIT(HPER) <sup>(3)</sup> | Half-Period Jitter, see figure 7                    |     | 66MHz                        | -130 | _                   | 130  |      |

|                           |                                                     |     | 100MHz                       | - 90 | _                   | 90   | ps   |

|                           |                                                     |     | 133/ 167/ 180 MHz            | -75  | _                   | 75   |      |

| tslr(0)                   | Output Clock Slew Rate (single-ended), see figure 8 |     | Load: 120Ω / 14pF            | 1    | _                   | 2    | V/ns |

|                           |                                                     |     | Load: 120Ω / 4pF             | 1    | _                   | 3    | ]    |

|                           |                                                     | I ⊢ | 66MHz                        | -180 | _                   | 180  |      |

|                           |                                                     |     | 100/ 133 MHz                 | -130 |                     | 130  |      |

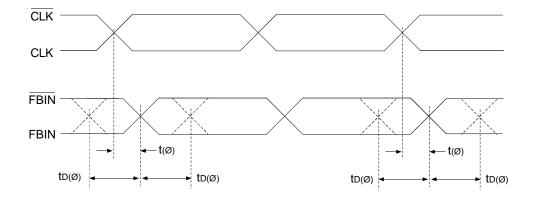

| tD(∅) <sup>(3)</sup>      | Dynamic Phase Offset (includes jitter)              |     | 167/ 180 MHz                 | -90  | -                   | 90   | ps   |

|                           | see figure 4                                        |     | 66MHz                        | -230 | _                   | 230  |      |

|                           |                                                     |     | 100/ 133 MHz                 | -170 |                     | 170  | ]    |

|                           |                                                     |     | 167/ 180 MHz                 | -100 | _                   | 100  |      |

| t(∅)                      | Static Phase Offset, see figure 3                   |     | 66MHz                        | -150 | _                   | 150  | ps   |

|                           |                                                     |     | 100/ 133/ 167/ 180 MHz       | -100 | _                   | 100  |      |

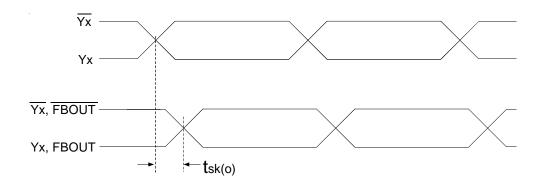

| tsk(0) <sup>(4)</sup>     | Output Skew, see figure 5                           |     |                              | _    | _                   | 50   | ps   |

| tr,tr                     | Output Rise and Fall Times (20% to 8                | 0%) | Load: 120Ω / 14pF            | 650  | _                   | 900  | ps   |

### NOTES:

- 1. All typical values are at respective nominal  $V_{\text{DDQ}}$ .

- 2. Refers to transition of non-inverting output.

- 3. This parameter guaranteed by design but not production tested.

- 4. All differential output pins are terminated with 120 $\Omega$  / 14pF.

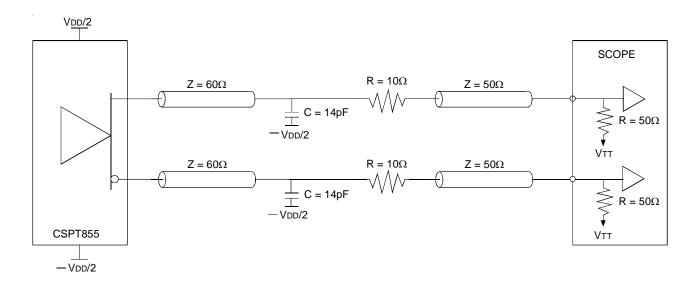

**NOTE:**1. V(TT) = GND

Figure 1. Output Load Test Circuit

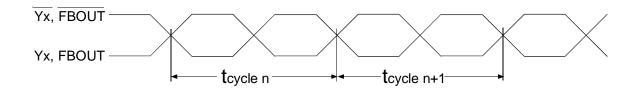

$t_{jit(cc)} = t_{cycle n} - t_{cycle n+1}$

Figure 2. Cycle-to-Cycle jitter

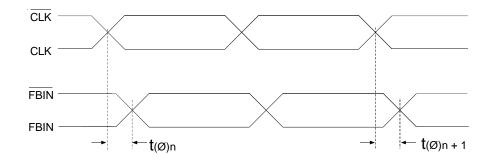

$$t_{(\emptyset)} = \frac{\sum_{1}^{n=N} t_{(\emptyset)n}}{N}$$

(N is a large number of samples)

Figure 3. Static Phase Offset

Figure 4. Dynamic Phase Offset

Figure 5. Output Skew

$$t_{jit(per)} = t_{cycle n} - \frac{1}{f_0}$$

Figure 6. Period jitter

Figure 7. Half-Period jitter

Figure 8. Input and Output Slew Rates

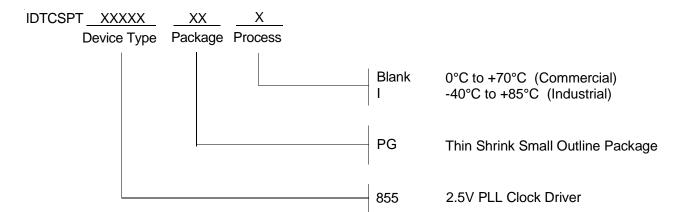

## ORDERING INFORMATION

2975 Stender Way Santa Clara, CA 95054 for SALES: 800-345-7015 or 408-727-6116 fax: 408-492-8674 www.idt.com for Tech Support: logichelp@idt.com (408) 654-6459