Two-wire serial interface 2k EEPROM (256-word × 8-bit) 4k EEPROM (512-word × 8-bit)

# **HITACHI**

ADE-203-1261A (Z) Rev. 1.0 Mar. 30, 2001

# **Description**

HN58X24xxSFPIAG series are two-wire serial interface EEPROM (Electrically Erasable and Programmable ROM). They realize high speed, low power consumption and a high level of reliability by employing advanced MNOS memory technology and CMOS process and low voltage circuitry technology. They also have a 8-byte page programming function to make their write operation faster.

#### **Features**

• Single supply: 1.8 V to 5.5 V

• Two-wire serial interface (I<sup>2</sup>C<sup>TM</sup> serial bus\*<sup>1</sup>)

• Clock frequency: 400 kHz

• Power dissipation:

— Standby: 3 μA (max)

Active (Read): 1 mA (max)Active (Write): 3 mA (max)

• Automatic page write: 8-byte/page

• Write cycle time: 10 ms (2.7 V to 5.5 V)/15ms (1.8 V to 2.7 V)

• Endurance: 10<sup>5</sup> Cycles (Page write mode)

Data retention: 10 Years

Small size packages: SOP 8-pinShipping tape and reel: 2,500 IC/reel

Note: 1. I<sup>2</sup>C is a trademark of Philips Corporation.

# **Ordering Information**

| Type No.        | Internal organizatio | n Operating voltage | Frequency | Package                            |

|-----------------|----------------------|---------------------|-----------|------------------------------------|

| HN58X2402SFPIAG | 2k bit (256 × 8-bit) | 1.8 V to 5.5 V      | 400 kHz   | 150 mil 8-pin plastic SOP (FP-8DB) |

| HN58X2404SFPIAG | 4k bit (512 × 8-bit) |                     |           |                                    |

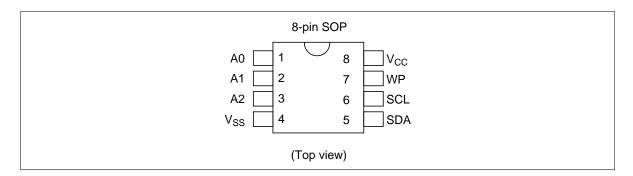

# **Pin Arrangement**

# **Pin Description**

| Pin name        | Function                 |

|-----------------|--------------------------|

| A0 to A2        | Device address           |

| SCL             | Serial clock input       |

| SDA             | Serial data input/output |

| WP              | Write protect            |

| V <sub>cc</sub> | Power supply             |

| V <sub>SS</sub> | Ground                   |

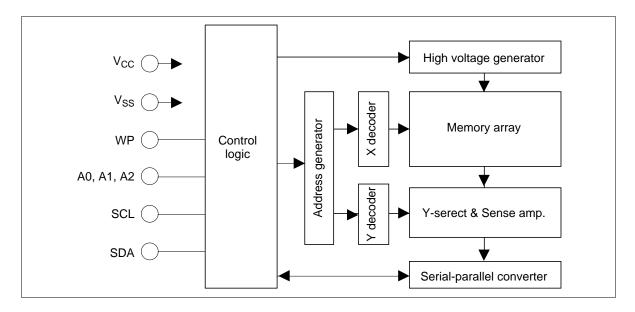

# **Block Diagram**

# **Absolute Maximum Ratings**

| Parameter                                  | Symbol          | Value            | Unit |

|--------------------------------------------|-----------------|------------------|------|

| Supply voltage relative to V <sub>SS</sub> | V <sub>cc</sub> | -0.6 to +7.0     | V    |

| Input voltage relative to V <sub>ss</sub>  | Vin             | -0.5*2 to +7.0*3 | V    |

| Operating temperature range*1              | Topr            | -40 to +85       | °C   |

| Storage temperature range                  | Tstg            | -65 to +125      | °C   |

Notes: 1. Including electrical characteristics and data retention.

- 2. Vin (min): -3.0 V for pulse width  $\leq 50$  ns.

- 3. Should not exceed  $V_{\rm cc}$  + 1.0 V.

# **DC Operating Conditions**

| Parameter             | Symbol          | Min                 | Тур | Max                        | Unit |

|-----------------------|-----------------|---------------------|-----|----------------------------|------|

| Supply voltage        | V <sub>cc</sub> | 1.8                 | _   | 5.5                        | V    |

|                       | V <sub>SS</sub> | 0                   | 0   | 0                          | V    |

| Input high voltage    | V <sub>IH</sub> | $V_{cc} \times 0.7$ | _   | V <sub>CC</sub> + 1.0      | V    |

| Input low voltage     | V <sub>IL</sub> | -0.3* <sup>1</sup>  | _   | $V_{\text{CC}} \times 0.3$ | V    |

| Operating temperature | Topr            | -40                 | _   | 85                         | °C   |

Note: 1.  $V_{IL}$  (min): -1.0 V for pulse width  $\leq$  50 ns.

DC Characteristics (Ta = -40 to +85°C,  $V_{CC}$  = 1.8 V to 5.5 V)

| Parameter                       | Symbol           | Min | Тур | Max | Unit | Test conditions                                                                                                                                                                                             |

|---------------------------------|------------------|-----|-----|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input leakage current           | I <sub>LI</sub>  | _   | _   | 2.0 | μΑ   | $V_{CC} = 5.5 \text{ V}$ , $Vin = 0 \text{ to } 5.5 \text{ V (SCL, SDA)}$                                                                                                                                   |

|                                 |                  | _   | _   | 20  | μΑ   | $V_{CC} = 5.5 \text{ V}, \text{ Vin} = 0 \text{ to } 5.5 \text{ V} \text{ (A0 to A2, WP)}$                                                                                                                  |

| Output leakage current          | I <sub>LO</sub>  | _   | _   | 2.0 | μΑ   | V <sub>CC</sub> = 5.5 V, Vout = 0 to 5.5 V                                                                                                                                                                  |

| Standby V <sub>cc</sub> current | I <sub>SB</sub>  | _   | 1.0 | 3.0 | μΑ   | $Vin = V_{SS} \text{ or } V_{CC}$                                                                                                                                                                           |

| Read V <sub>cc</sub> current    | I <sub>CC1</sub> | _   | _   | 1.0 | mΑ   | V <sub>CC</sub> = 5.5 V, Read at 400 kHz                                                                                                                                                                    |

| Write V <sub>cc</sub> current   | I <sub>CC2</sub> | _   | _   | 3.0 | mA   | V <sub>CC</sub> = 5.5 V, Write at 400 kHz                                                                                                                                                                   |

| Output low voltage              | $V_{OL2}$        | _   | _   | 0.4 | V    | $V_{CC} = 4.5 \text{ to } 5.5 \text{ V}, I_{OL} = 1.6 \text{ mA}$<br>$V_{CC} = 2.7 \text{ to } 4.5 \text{ V}, I_{OL} = 0.8 \text{ mA}$<br>$V_{CC} = 1.8 \text{ to } 2.7 \text{ V}, I_{OL} = 0.4 \text{ mA}$ |

|                                 | V <sub>OL1</sub> | _   | _   | 0.2 | V    | $V_{\rm CC}$ = 1.8 to 2.7 V, $I_{\rm OL}$ = 0.2 mA                                                                                                                                                          |

# **Capacitance** ( $Ta = 25^{\circ}C$ , f = 1 MHz)

| Parameter                             | Symbol              | Min | Тур | Max | Unit | Test conditions |

|---------------------------------------|---------------------|-----|-----|-----|------|-----------------|

| Input capacitance (A0 to A2, SCL, WP) | Cin*1               | _   | _   | 6.0 | pF   | Vin = 0 V       |

| Output capacitance (SDA)              | C <sub>I/O</sub> *1 | _   | _   | 6.0 | pF   | Vout = 0 V      |

Note: 1. This parameter is sampled and not 100% tested.

**AC Characteristics** (Ta = -40 to +85°C,  $V_{CC} = 1.8$  to 5.5 V)

#### **Test Conditions**

• Input pules levels:

$--- V_{IL} = 0.2 \times V_{CC}$

$--- V_{IH} = 0.8 \times V_{CC}$

• Input rise and fall time: 20 ns

• Input and output timing reference levels:  $0.5 \times V_{CC}$

• Output load: TTL Gate + 100 pF

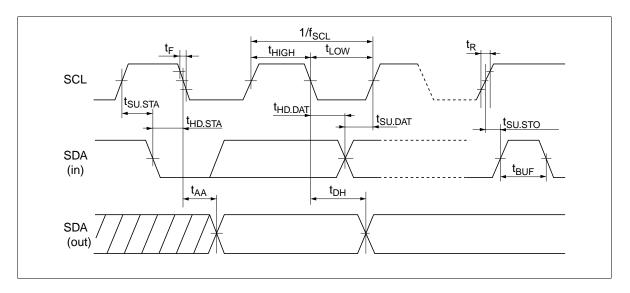

| Parameter              | Symbol                                     | Min                 | Тур  | Max | Unit | Notes |   |

|------------------------|--------------------------------------------|---------------------|------|-----|------|-------|---|

| Clock frequency        |                                            | f <sub>SCL</sub>    | _    | _   | 400  | kHz   |   |

| Clock pulse width low  |                                            | t <sub>LOW</sub>    | 1200 | _   | _    | ns    |   |

| Clock pulse width high | 1                                          | t <sub>HIGH</sub>   | 600  | _   | _    | ns    |   |

| Noise suppression tim  | е                                          | t,                  | _    | _   | 50   | ns    | 1 |

| Access time            |                                            | t <sub>AA</sub>     | 100  | _   | 900  | ns    |   |

| Bus free time for next | t <sub>BUF</sub>                           | 1200                | _    | _   | ns   |       |   |

| Start hold time        | t <sub>HD.STA</sub>                        | 600                 | _    | _   | ns   |       |   |

| Start setup time       |                                            | t <sub>SU.STA</sub> | 600  | _   | _    | ns    |   |

| Data in hold time      |                                            | t <sub>HD.DAT</sub> | 0    | _   | _    | ns    |   |

| Data in setup time     |                                            | t <sub>SU.DAT</sub> | 100  | _   | _    | ns    |   |

| Input rise time        |                                            | t <sub>R</sub>      | _    | _   | 300  | ns    | 1 |

| Input fall time        |                                            | t <sub>F</sub>      | _    | _   | 300  | ns    | 1 |

| Stop setup time        |                                            | t <sub>SU.STO</sub> | 600  | _   | _    | ns    |   |

| Data out hold time     |                                            | t <sub>DH</sub>     | 50   | _   | _    | ns    |   |

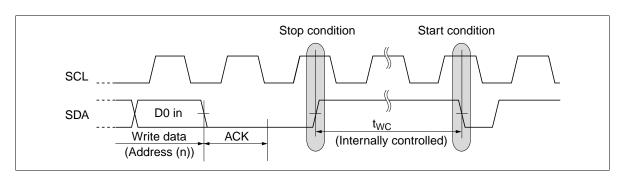

| Write cycle time       | $V_{CC} = 2.7 \text{ V to } 5.5 \text{ V}$ | t <sub>wc</sub>     | _    | _   | 10   | ms    | 2 |

|                        | $V_{cc}$ = 1.8 V to 2.7 V                  | t <sub>wc</sub>     | _    | _   | 15   | ms    | 2 |

Notes: 1. This parameter is sampled and not 100% tested.

<sup>2.</sup>  $t_{\mbox{\tiny WC}}$  is the time from a stop condition to the end of internally controlled write cycle.

# **Timing Waveforms**

### **Bus Timing**

### **Write Cycle Timing**

#### **Pin Function**

#### Serial Clock (SCL)

The SCL pin is used to control serial input/output data timing. The SCL input is used to positive edge clock data into EEPROM device and negative edge clock data out of each device. Maximum clock rate is 400 kHz.

#### Serial Input/Output data (SDA)

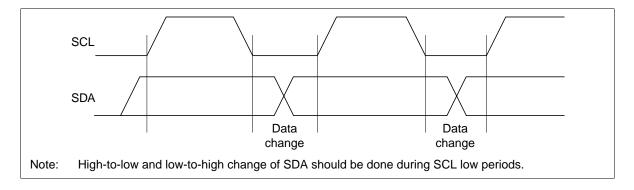

The SDA pin is bidirectional for serial data transfer. The SDA pin needs to be pulled up by resistor as that pin is open-drain driven structure. Use proper resistor value for your system by considering  $V_{OL}$ ,  $I_{OL}$  and the SDA pin capacitance. Except for a start condition and a stop condition which will be discussed later, the SDA transition needs to be completed during SCL low period.

#### **Data Validity** (SDA data change timing waveform)

#### Device Address (A0, A1, A2)

UP to eight devices for 2k, four devices for 4k, can be addressed on the same bus by setting the levels on these pins to different combinations. The levels on these pins are compared with the device address code which are input through the SDA pin. The device is selected if the compare is successfully done. These pins are internally pulled-down to  $V_{SS}$ . The device read these pins as Low if unconnected. As for 4k, it is unnecessary for the A0 pin to be connected because the corresponding device address code is used as memory address a8.

#### Pin Connections for A0 to A2

|             |                    | Pin con                             | nection                          |                                  |                              |

|-------------|--------------------|-------------------------------------|----------------------------------|----------------------------------|------------------------------|

| Memory size | Max connect number | A2                                  | A1                               | Α0                               | Notes                        |

| 2k bit      | 8                  | V <sub>CC</sub> /V <sub>SS</sub> *1 | V <sub>CC</sub> /V <sub>SS</sub> | V <sub>CC</sub> /V <sub>SS</sub> |                              |

| 4k bit      | 4                  | V <sub>cc</sub> /V <sub>ss</sub>    | V <sub>cc</sub> /V <sub>ss</sub> | ×*2                              | Use A0 for memory address a8 |

Notes: 1. "V<sub>CC</sub>/V<sub>SS</sub>" means that the device address pins are connected to V<sub>CC</sub> or V<sub>SS</sub>. These pins are V<sub>SS</sub> if unconnected.

2.  $\times$  = Don't care (Open is also approval.)

#### Write Protect (WP)

When the Write Protect pin (WP) is high, the write protections feature is enabled and operates as shown in the following table. When the WP is low, write operations for all memory array are allowed. The read operation is always activated irrespective of the WP pin status. The WP pin is internally pull-down to  $V_{\rm SS}$ . Write operations for all memory array are allowed if unconnected.

#### Write Protect Area

|                 | Write protect area          |                 |  |  |  |

|-----------------|-----------------------------|-----------------|--|--|--|

| WP pin status   | 2k bit                      | 4k bit          |  |  |  |

| V <sub>IH</sub> | Entire (2k bit)             | Entire (4k bit) |  |  |  |

| $V_{IL}$        | Normal read/write operation | on              |  |  |  |

### **Functional Description**

#### **Start Condition**

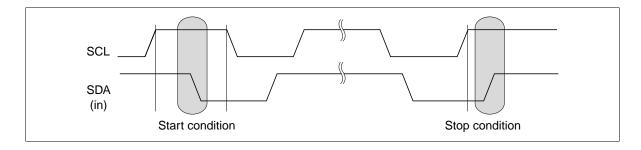

A high-to-low transition of the SDA with the SCL high is needed in order to start read, write operation. (See start condition and stop condition)

#### **Stop Condition**

A low-to-high transition of the SDA with the SCL high is a stop condition. The stand-by operation starts after a read sequence by a stop condition. In the case of write operation, a stop condition terminates the write data inputs and place the device in a internally-timed write cycle to the memories. After the internally-timed write cycle which is specified as  $t_{WC}$ , the device enters a standby mode. (See write cycle timing)

#### **Start Condition and Stop Condition**

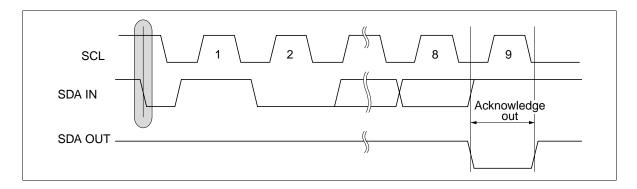

#### Acknowledge

All addresses and data words are serially transmitted to and from in 8-bit words. The receiver sends a zero to acknowledge that it has received each word. This happens during ninth clock cycle. The transmitter keeps bus open to receive acknowledgment from the receiver at the ninth clock. In the write operation, EEPROM sends a zero to acknowledge after receiving every 8-bit words. In the read operation, EEPROM sends a zero to acknowledge after receiving the device address word. After sending read data, the EEPROM waits acknowledgment by keeping bus open. If the EEPROM receives zero as an acknowledge, it sends read data of next address. If the EEPROM receives acknowledgment "1" (no acknowledgment) and a following stop condition, it stops the read operation and enters a stand-by mode. If the EEPROM receives neither acknowledgment "0" nor a stop condition, the EEPROM keeps bus open without sending read data.

#### **Acknowledge Timing Waveform**

#### **Device Addressing**

The EEPROM device requires an 8-bit device address word following a start condition to enable the chip for a read or a write operation. The device address word consists of 4-bit device code, 3-bit device address code and 1-bit read/write(R/W) code. The most significant 4-bit of the device address word are used to distinguish device type and this EEPROM uses "1010" fixed code. The device address word is followed by the 3-bit device address code in the order of A2, A1, A0. The device address code selects one device out of all devices which are connected to the bus. This means that the device is selected if the inputted 3-bit device address code is equal to the corresponding hard-wired A2-A0 pin status. As for the 4kbit EEPROMs, some bits of their device address code may be used as the memory address bits. For example, A0 is used as a8 of memory address for the 4kbit. The eighth bit of the device address word is the read/write(R/W) bit. A write operation is initiated if this bit is low and a read operation is initiated if this bit is high. Upon a compare of the device address word, the EEPROM enters the read or write operation after outputting the zero as an acknowledge. The EEPROM turns to a stand-by state if the device code is not "1010" or device address code doesn't coincide with status of the correspond hard-wired device address pins A0 to A2.

#### Device Address Word

#### Device address word (8-bit)

|    | Devic | e code (fi | xed) |   | Device | Device address code*1 |    |     |  |

|----|-------|------------|------|---|--------|-----------------------|----|-----|--|

| 2k | 1     | 0          | 1    | 0 | A2     | A1                    | A0 | R/W |  |

| 4k | 1     | 0          | 1    | 0 | A2     | A1                    | a8 | R/W |  |

Notes: 1. A2 to A0 are device address and a8 are memory address.

2. R/W="1" is read and R/W = "0" is write.

#### **Write Operations**

#### **Byte Write:**

A write operation requires an 8-bit device address word with R/W = "0". Then the EEPROM sends acknowledgment "0" at the ninth clock cycle. After these, EEPROMs receive 8-bit memory address word. Upon receipt of this memory address, the EEPROM outputs acknowledgment "0" and receives a following 8-bit write data. After receipt of write data, the EEPROM outputs acknowledgment "0". If the EEPROM receives a stop condition, the EEPROM enters an internally-timed write cycle and terminates receipt of SCL, SDA inputs until completion of the write cycle. The EEPROM returns to a standby mode after completion of the write cycle.

#### **Byte Write Operation**

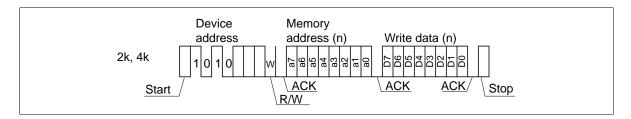

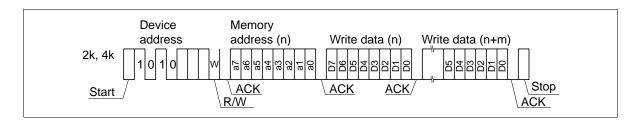

#### Page Write:

The EEPROM is capable of the page write operation which allows any number of bytes up to 8 bytes to be written in a single write cycle. The page write is the same sequence as the byte write except for inputting the more write data. The page write is initiated by a start condition, device address word, memory address(n) and write data(Dn) with every ninth bit acknowledgment. The EEPROM enters the page write operation if the EEPROM receives more write data(Dn+1) instead of receiving a stop condition. The a0 to a2 address bits are automatically incremented upon receiving write data(Dn+1). The EEPROM can continue to receive write data up to 8 bytes. If the a0 to a2 address bits reaches the last address of the page, the a0 to a2 address bits will roll over to the first address of the same page and previous write data will be overwritten. Upon receiving a stop condition, the EEPROM stops receiving write data and enters internally-timed write cycle.

#### **Page Write Operation**

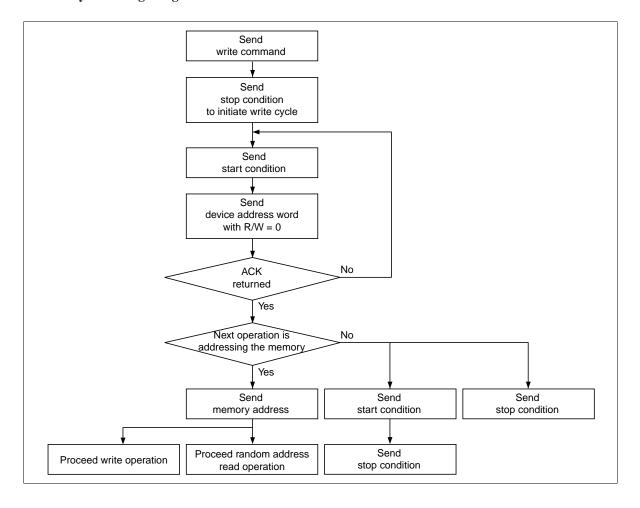

#### Acknowledge Polling:

Acknowledge polling feature is used to show if the EEPROM is in a internally-timed write cycle or not. This features is initiated by the stop condition after inputting write data. This requires the 8-bit device address word following the start condition during a internally-timed write cycle. Acknowledge polling will operate R/W code = "0". Acknowledgment "1" (no acknowledgment) shows the EEPROM is in a internally-timed write cycle and acknowledgment "0" shows that the internally-timed write cycle has completed. See Write Cycle Polling using ACK.

#### Write Cycle Polling using ACK

#### **Read Operation**

There are three read operations: current address read, random read, and sequential read. Read operations are initiated the same way as write operations with the exception of R/W = "1".

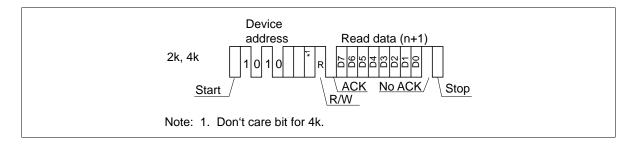

#### **Current Address Read:**

The internal address counter maintains the last address accessed during the last read or write operation, with incremented by one. Current address read accesses the address kept by the internal address counter. After receiving a start condition and the device address word(R/W is "1"), the EEPROM outputs the 8-bit current address data from the most significant bit following acknowledgment "0" If the EEPROM receives acknowledgment "1" (no acknowledgment) and a following stop condition, the EEPROM stops the read operation and is turned to a standby state. In case the EEPROM have accessed the last address of the last page at previous read operation, the current address will roll over and returns to zero address. In case the EEPROM have accessed the last address of the page at previous write operation, the current address will roll over within page addressing and returns to the first address in the same page. The current address is valid while power is on. The current address after power on will be indefinite. The random read operation described below is necessary to define the memory address.

#### **Current Address Read Operation**

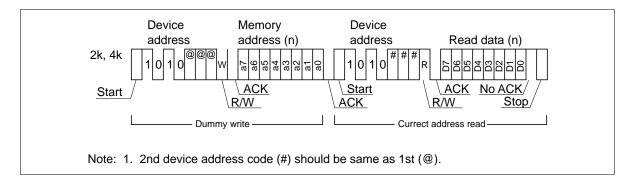

#### Random Read:

This is a read operation with defined read address. A random read requires a dummy write to set read address. The EEPROM receives a start condition, device address word(R/W=0) and memory address sequentially. The EEPROM outputs acknowledgment "0" after receiving memory address then enters a current address read with receiving a start condition. The EEPROM outputs the read data of the address which was defined in the dummy write operation. After receiving acknowledgment "1"(no acknowledgment) and a following stop condition, the EEPROM stops the random read operation and returns to a standby state.

#### **Random Read Operation**

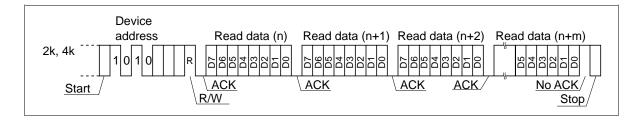

#### **Sequential Read:**

Sequential reads are initiated by either a current address read or a random read. If the EEPROM receives acknowledgment "0" after 8-bit read data, the read address is incremented and the next 8-bit read data are coming out. This operation can be continued as long as the EEPROM receives acknowledgment "0". The address will roll over and returns address zero if it reaches the last address of the last page. The sequential read can be continued after roll over. The sequential read is terminated if the EEPROM receives acknowledgment "1" (no acknowledgment) and a following stop condition.

#### Sequential Read Operation

#### Notes

#### Data protection at V<sub>CC</sub> On/Off

When  $V_{CC}$  is turned on or off, noise on the SCL and SDA inputs generated by external circuits (CPU, etc) may act as a trigger and turn the EEPROM to unintentional program mode. To prevent this unintentional programming, this EEPROM have a power on reset function. Be careful of the notices described below in order for the power on reset function to operate correctly.

- SCL and SDA should be fixed to V<sub>CC</sub> or V<sub>SS</sub> during V<sub>CC</sub> on/off. Low to high or high to low transition during V<sub>CC</sub> on/off may cause the trigger for the unintentional programming.

- V<sub>CC</sub> should be turned off after the EEPROM is placed in a standby state.

- V<sub>CC</sub> should be turned on from the ground level(V<sub>SS</sub>) in order for the EEPROM not to enter the

unintentional programming mode.

- $V_{CC}$  turn on speed should be longer than 10 us.

#### Write/Erase Endurance and Data retention Time

The endurance is 10<sup>5</sup> cycles in case of page programming and 10<sup>4</sup> cycles in case of byte programming (1% cumulative failure rate). The data retention time is more than 10 years when a device is page-programmed less than 10<sup>4</sup> cycles.

#### **Noise Suppression Time**

This EEPROM have a noise suppression function at SCL and SDA inputs, that cut noise of width less than 50 ns. Be careful not to allow noise of width more than 50 ns.

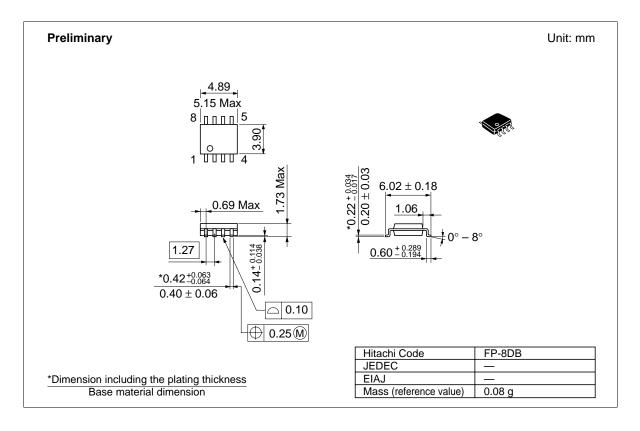

### **Package Dimensions**

### HN58X2402SFPIAG/HN58X2404SFPIAG (FP-8DB)

#### **Cautions**

- 1. Hitachi neither warrants nor grants licenses of any rights of Hitachi's or any third party's patent, copyright, trademark, or other intellectual property rights for information contained in this document. Hitachi bears no responsibility for problems that may arise with third party's rights, including intellectual property rights, in connection with use of the information contained in this document.

- 2. Products and product specifications may be subject to change without notice. Confirm that you have received the latest product standards or specifications before final design, purchase or use.

- 3. Hitachi makes every attempt to ensure that its products are of high quality and reliability. However, contact Hitachi's sales office before using the product in an application that demands especially high quality and reliability or where its failure or malfunction may directly threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation, traffic, safety equipment or medical equipment for life support.

- 4. Design your application so that the product is used within the ranges guaranteed by Hitachi particularly for maximum rating, operating supply voltage range, heat radiation characteristics, installation conditions and other characteristics. Hitachi bears no responsibility for failure or damage when used beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as failsafes, so that the equipment incorporating Hitachi product does not cause bodily injury, fire or other consequential damage due to operation of the Hitachi product.

- 5. This product is not designed to be radiation resistant.

- 6. No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without written approval from Hitachi.

- 7. Contact Hitachi's sales office for any questions regarding this document or Hitachi semiconductor products.

# IITACHI

Semiconductor & Integrated Circuits. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

Tel: Tokyo (03) 3270-2111 Fax: (03) 3270-5109

NorthAmerica http://semiconductor.hitachi.com/ Europe Asia http://www.hitachi-eu.com/hel/ecg http://sicapac.hitachi-asia.com http://www.hitachi.co.jp/Sicd/indx.htm Japan

#### For further information write to:

Hitachi Semiconductor (America) Inc. 179 East Tasman Drive, San Jose.CA 95134

Hitachi Europe Ltd. Electronic Components Group. Whitebrook Park Lower Cookham Road Tel: <1> (408) 433-1990 Maidenhead Tel: <65>-538-6533/538-8577 Fax: <1> (408) 433-0223 Berkshire SL6 8YA, United Kingdom Fax: <65>-538-6933/538-3877

Tel: <44> (1628) 585000 Fax: <44> (1628) 585200

Hitachi Europe GmbH Electronic Components Group Dornacher Straße 3 D-85622 Feldkirchen, Munich Germany

Tel: <49> (89) 9 9180-0 Fax: <49> (89) 9 29 30 00 Hitachi Asia Ltd. Hitachi Tower 16 Collyer Quay #20-00, Singapore 049318

URL: http://www.hitachi.com.sg Hitachi Asia I td

(Taipei Branch Office) 4/F. No. 167. Tun Hwa North Road. Hung-Kuo Building, Taipei (105), Taiwan

Tel: <886>-(2)-2718-3666 Fax: <886>-(2)-2718-8180 Telex: 23222 HAS-TP URL: http://www.hitachi.com.tw

> Copyright © Hitachi, Ltd., 2001. All rights reserved. Printed in Japan. Colophon 3.0

URL: http://semiconductor.hitachi.com.hk

Hitachi Asia (Hong Kong) Ltd.

7/F., North Tower,

Hong Kong

World Finance Centre

Harbour City, Canton Road Tsim Sha Tsui, Kowloon,

Tel: <852>-(2)-735-9218

Fax: <852>-(2)-730-0281

Group III (Electronic Components)