TIA' AANMA MICROELECTRONICS CO. LTD 深圳天马微电子股份有限公司 cheethul.com

#### **REVISION RECORD**

| Date | Ver. | Ref. Page | Revision No. | <b>Revision Item</b> |

|------|------|-----------|--------------|----------------------|

|      |      |           |              |                      |

|      |      |           |              |                      |

|      |      |           |              |                      |

|      |      |           |              |                      |

|      |      |           |              |                      |

|      |      |           |              |                      |

|      |      |           |              |                      |

|      |      |           |              |                      |

|      |      |           |              |                      |

|      |      |           |              |                      |

|      |      |           |              |                      |

|      |      |           |              |                      |

|      |      |           |              |                      |

|      |      |           |              |                      |

|      |      |           |              |                      |

|      |      |           |              |                      |

|      |      |           |              |                      |

|      |      |           |              |                      |

|      |      |           |              |                      |

|      |      |           |              |                      |

#### CONTENTS

- 1. Display characteristics

- 2. Mechanical description

- 3. Limiting values (absolute maximum rating system )

- 4. Operating range and electrical and optical characteristic

- 5. Circuit block diagram

- 6. Interface signal

- 7. Interface timing chart

- 8. Test of reliability

- 9. Inspection requirement

- 10. Quality level

- 11. Precautions for use of LCD modules

# 1. Display characteristics

| Parameter               | Specification       |

|-------------------------|---------------------|

| Resolution              | 128*(RGB)(W)*160(H) |

| Illumination mode       | Transflective       |

| Number of colors        | 65k                 |

| Number of gray scales   | 32                  |

| Normally white or black | black               |

| Viewing direction       | 6:00                |

| Backlight and color     | LED,WHITE           |

| Duty ratio              | 1/160               |

| Application             | MOBILE PHONE        |

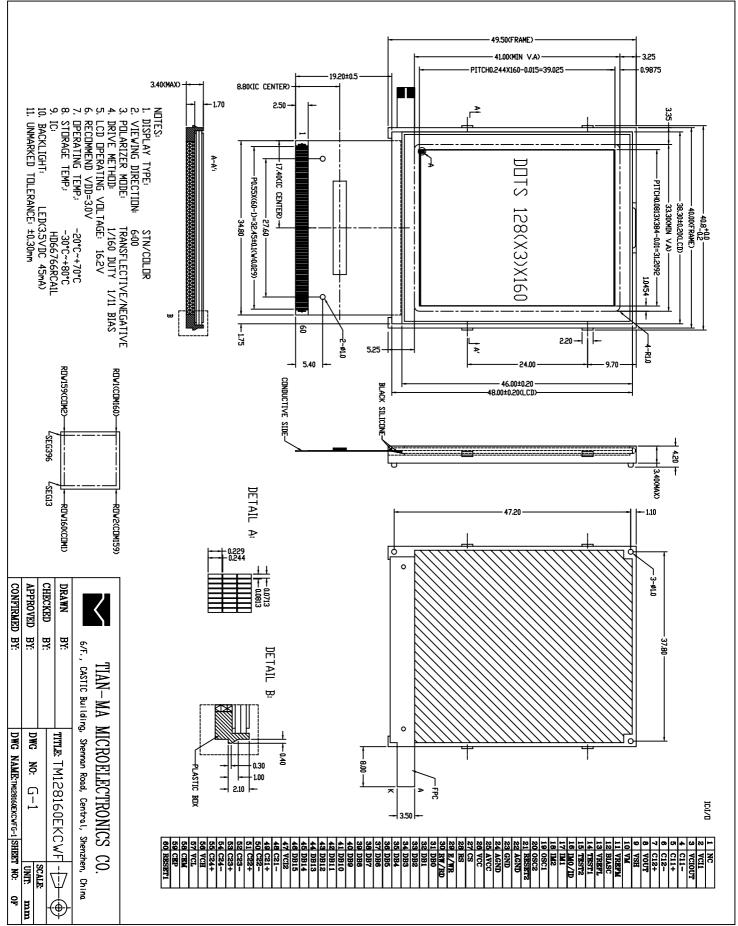

# 2. Mechanical description

## (1) Mechanical data

| Parameter         | Specifications | UNIT |

|-------------------|----------------|------|

| Construction      | COF            | /    |

| Overall dimension | 40.8x49.5x3.4  | mm   |

| Viewing area      | 33.3x41.0      | mm   |

| Active area       | 31.2092x39.025 | mm   |

| Number of dots    | 128x3x160      | Dots |

| Dot pitch         | 0.0813x0.244   | mm   |

| Dot size          | 0.0713x0.229   | mm   |

(2) Outline dimensions

# 3.Limiting values (absolute maximum rating system )

| Subalance | Deveryetava                                                           | S-mah al                                    | V    | alue                 | T Incid |

|-----------|-----------------------------------------------------------------------|---------------------------------------------|------|----------------------|---------|

| Subclause | Parameters                                                            | Symbol                                      | Min. | Max.                 | Unit    |

| 3.1       | Operating ambient temperature                                         | Тор                                         | -20  | 70                   |         |

| 3.2       | Storage temperature                                                   | Tstg                                        | -30  | 80                   |         |

| 3.3       | Supply voltage(s) (select either the pair of 3.3.1 and 3.3.2 or 3.3.3 |                                             |      |                      |         |

| 3.3.1     | Supply voltage for logic drive                                        | $V_{ m DD}	ext{-}V_{ m SS}$                 | -0.3 | 4.0                  | V       |

| 3.3.2     | Supply voltage for LCD drive                                          | $V_{\rm DD}$ - $V_{\rm EE}$                 | -0.3 | 18.0                 | V       |

|           |                                                                       | or $V_{ m EE}$ - $V_{ m SS}$                |      |                      |         |

|           |                                                                       | or                                          |      |                      |         |

|           |                                                                       | $V_{ m DD}$ - $V_{ m o}$                    |      |                      |         |

|           |                                                                       | or<br>V <sub>O</sub> -V <sub>SS</sub>       |      |                      |         |

| 3.3.3     | Supply voltage(s) for module                                          | $V_{ m MDL}$                                | -0.3 | 4.0                  | V       |

|           |                                                                       | or $V_{\text{MDL1},} V_{\text{MDL2},}$ etc. |      |                      |         |

| 3.4       | Input signal voltage                                                  | $V_{ m IN}$                                 | -0.4 | V <sub>DD</sub> +0.3 | V       |

| 3.5       | Voltage of integrated light source                                    |                                             |      | 4.0                  | V       |

|           | (where appropriate)                                                   |                                             |      |                      |         |

| 3.6       | Operation humidity                                                    |                                             | 20   | 65                   | %RH     |

|           | Storage humidity                                                      |                                             | 10   | 80                   | %RH     |

# 4. Operating range and electrical and optical characteristics

## 4.1 Recommended operating range

| Call allowed      | Parameters                                                                                             |                                                         | Va          | <b>TT</b> •                                                        |      |  |

|-------------------|--------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-------------|--------------------------------------------------------------------|------|--|

| Subclause         | (Characteristics at Top=25<br>unless otherwise spectified)                                             | Symbol                                                  | Min.        | lue<br>Max.<br>3.3<br>-<br>3.3<br>-<br>3.3<br>-<br>3.3<br>-<br>3.3 | Unit |  |

| 4.1.1             | Operating voltage range of supply<br>voltage(s) (select either the pair of<br>4.1.1and 4.1.2,or 4.1.3) |                                                         |             |                                                                    |      |  |

| 4.1.1.1           | Supply voltage for logic drive                                                                         | $V_{DD}$ - $V_{SS}$                                     | 1.8         | 3.3                                                                | V    |  |

| 4.1.1.2           | Supply voltage for LCD drive                                                                           | V <sub>DD</sub> -V <sub>EE</sub><br>Or                  | -           | -                                                                  | V    |  |

|                   |                                                                                                        | V <sub>EE</sub> -V <sub>SS</sub><br>Or                  |             |                                                                    |      |  |

|                   |                                                                                                        | V <sub>DD</sub> -V <sub>O</sub><br>Or                   |             |                                                                    |      |  |

| 4.1.1.3           | Supply voltage(s) for module                                                                           | $V_{O}-V_{SS}$ $V_{MDL}$ $Or$ $V_{MDL1}, V_{MDL2}, etc$ | 2.4         | 3.3                                                                | V    |  |

| 4.1.2             | Operating voltage range of input signal voltages                                                       | V <sub>IN</sub>                                         |             |                                                                    |      |  |

| 4.1.2.1           | Input signal voltage, high                                                                             | V <sub>INH</sub>                                        | $0.8V_{DD}$ | $V_{DD}$                                                           | V    |  |

| 4.1.2.2           | Input signal voltage, low                                                                              | V <sub>INL</sub>                                        | -0.3        | $0.2 V_{DD}$                                                       | v    |  |

| 4.1.3             | Operating voltage range of analogue<br>light source(where appropriate)                                 |                                                         | 3.3         | 3.7                                                                | V    |  |

| 4.1.4             | Operating frequency range(s) (where appropriate)                                                       | F <sub>OP</sub>                                         |             |                                                                    | Hz   |  |

| 4.1.4.1<br>and/or | Operating frame frequency range                                                                        | f <sub>FRM</sub>                                        | -           | -                                                                  | Hz   |  |

| 4.1.4.2           | Oscillator frequency range(Line rate)                                                                  | f <sub>OSC</sub>                                        | 28          | 36                                                                 | KHz  |  |

# 4.2 Electrical and optical characteristics

|            | Characteristics at Tar. 25                              |                                  |       | Va                                                                                                                | lue |

|------------|---------------------------------------------------------|----------------------------------|-------|-------------------------------------------------------------------------------------------------------------------|-----|

| Subclasses | Characteristics at Top=25<br>unless otherwise specified | Symbol                           | Unit  | Va           Min.           15           30           -40           -30           TBD           TBD           TBD | Max |

| 4.2.1      | Supply current at specified frame frequency,            | / <sub>tot</sub>                 | mA    |                                                                                                                   | 2.5 |

|            | specified operating supply voltage, with an             | or                               |       |                                                                                                                   |     |

|            | adequate display pattern and other electrical           | $/_{\rm DD}$                     |       |                                                                                                                   |     |

|            | driving conditions chosen in order to                   | and/or                           |       |                                                                                                                   |     |

|            | achieve extreme supply current                          | $/_{\rm EE}$                     |       |                                                                                                                   |     |

| 4.2.2      | Operating current of integrated light source            | (optional)                       | mA    |                                                                                                                   | 60  |

|            | at its specified operating voltage(where appropriate)   | /cs                              |       |                                                                                                                   |     |

| 4.2.3      | Contrast ratio :Top=25 , x=0, y=0                       | <i>CR</i> <sub>dir</sub>         |       | 15                                                                                                                |     |

|            | VLCD=Vop                                                | and/or                           |       |                                                                                                                   |     |

|            |                                                         | $CR_{diff}$                      |       |                                                                                                                   |     |

| 4.2.4.1    | Operating display luminance at specified                | L                                | cd/m2 | 30                                                                                                                |     |

|            | viewing direction and measuring point(s) (where         |                                  |       |                                                                                                                   |     |

|            | appropriate)                                            |                                  |       |                                                                                                                   |     |

| 4.2.4.2    | Luminance uniformity (where appropriate)                | $L_{ m uni}$                     | %     |                                                                                                                   | 60  |

| 4.2.5      | Viewing angle range (Cr 2.0)                            | $\theta_{\rm x}$ and             | deg   | -40                                                                                                               | 35  |

|            |                                                         | $	heta_{ m y}$                   | deg   | -30                                                                                                               | 30  |

| 4.2.6.1    | Rise time at 25                                         | ton                              | ms    |                                                                                                                   | 200 |

| 4.2.6.2    | Fall time at 25                                         | $t_{\rm off}$                    | ms    |                                                                                                                   | 200 |

| 4.2.8.1    | Chromaticity of white (x, y) (where appropriate)        | $X_{\mathrm{W}}, Y_{\mathrm{W}}$ | -     | TBD                                                                                                               | -   |

| 4.2.8.2    | Chromaticity of red (x, y) (where appropriate)          | $X_{\rm R}, Y_{\rm R}$           | -     | TBD                                                                                                               | -   |

| 4.2.8.3    | Chromaticity of blue (x,y) (where appropriate)          | X <sub>B</sub> ,Y <sub>B</sub>   | -     | TBD                                                                                                               | -   |

| 4.2.8.4    | Chromaticity of green (x, y) (where appropriate)        | $X_{\rm G}, Y_{\rm G}$           | -     | TBD                                                                                                               | -   |

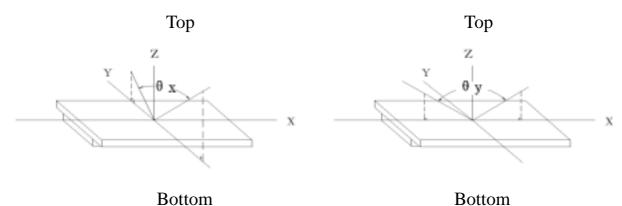

#### 4.3 Definition of optical characteristics

#### 4.3.1 Definition of Viewing Angle

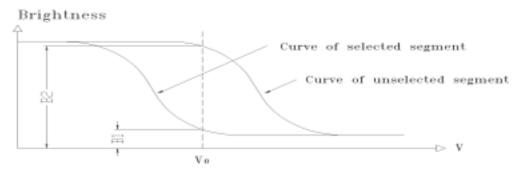

#### 4.3.2 Definition of contrast ratio

Contrast Ratio =  $B2/B1 = \frac{\text{unselected state brightness}}{\text{selected state brightness}}$

#### Measuring Conditions:

1) Ambient Temperature: 25 2) Frame frequency: 70.0Hz

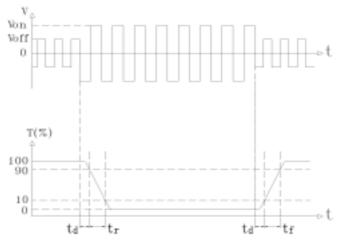

#### 4.3.3 Definition of Response time

Turn on time:  $t_{on} = t_d + t_r$ Measuring Condition:

1) Operating Voltage: 16.2V

Turn off time:  $t_{off} = t_{d} + t_{f}$

2) Frame frequency: 70.0Hz

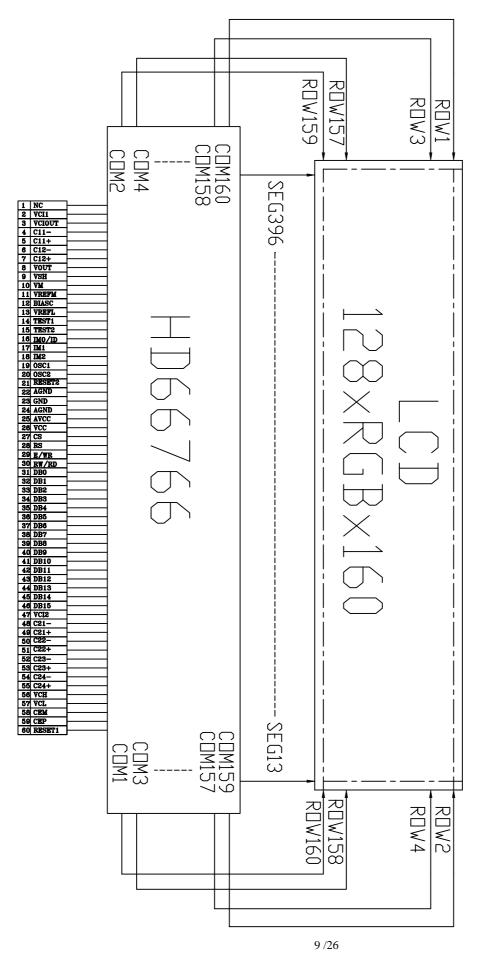

#### 5. Circuit block diagram

# 6. Interface signal

## 6.1 Pin Assignment

| Pin No. | Symbol | Level | Description                                                                                                   |

|---------|--------|-------|---------------------------------------------------------------------------------------------------------------|

| 1       | NC     | -     | Not connect                                                                                                   |

| 2       | VCI1   | -     | Voltage-input pin for step-up circuit 1                                                                       |

| 3       | VCIOUT | -     | Outputs a regulated voltage derived from Vcc                                                                  |

| 4       | C11-   | -     | When step-up circuit is used, connect a step-up                                                               |

| 5       | C11+   | -     | capacitor                                                                                                     |

| 6       | C12-   | -     | When step-up circuit is used, connect a step-up                                                               |

| 7       | C12+   | -     | capacitor                                                                                                     |

| 8       | VOUT   | -     | A voltage that doubles or triples the voltage between<br>Vci1 and GND is output here.                         |

| 9       | VSH    | -     | Selection level for the segment signal                                                                        |

| 10      | VM     | -     | Non-selection level for the common signal                                                                     |

| 11      | VREFM  | -     | Connect capacitor for stabilization for internal power                                                        |

| 12      | BIASC  | -     | supply                                                                                                        |

| 13      | VREFL  | -     | Inputs reference voltage for LCD drives power supply                                                          |

| 14      | TEST1  | -     | Test pin. Must be fixed at GND level.                                                                         |

| 15      | TEST2  | -     | Test pin. Must be fixed at GND level.                                                                         |

| 16      | IM0/ID | H/L   | Selects the MPU interface mode                                                                                |

| 17      | IM1    | H/L   |                                                                                                               |

| 18      | IM2    | H/L   |                                                                                                               |

| 19      | OSC1   | -     | Connect an external resistor for R-C oscillation                                                              |

| 20      | OSC2   | -     | Connect an external resistor for R-C oscillation                                                              |

| 21      | RESET2 | H/L   | 2 RESET pins, use one pin and open unused pin                                                                 |

| 22      | AGND   | 0     | GND for power supply circuit.                                                                                 |

| 23      | GND    | 0     | GND Logic 0 V                                                                                                 |

| 24      | AGND   | 0     | GND for power supply circuit.                                                                                 |

| 25      | AVCC   | -     | VCC for power supply circuit                                                                                  |

| 26      | VCC    | -     | Power supply VCC: + 2.2 V to + 3.6 V                                                                          |

| 27      | CS     | H/L   | Selects the HD66766R,L: HD66766R is selected                                                                  |

| 28      | RS     | H/L   | Selects the register,L: Index/status H: Control                                                               |

| 29      | E/WR   | H/L   | For 68-system bus interface, serves as enable signal<br>For 80-system bus interface, serves as a write strobe |

## Pin Assignment(Continue)

| Pin No. | Symbol | Level | Description                                            |

|---------|--------|-------|--------------------------------------------------------|

| 30      | RW/RD  | H/L   | For 68-system select data read/write operation         |

|         |        |       | For 80-system bus interface, serves as a read strobe   |

| 31      | DB0    | H/L   | For a clock-synchronous serial interface,DB0 serves    |

| 32      | DB1    | H/L   | as the serial data input pin (SDI). The input level is |

| 33      | DB2    | H/L   | read on the rising edge of the SCL signal.             |

| 34      | DB3    | H/L   | For a clock-synchronous serial interface, DB1 serves   |

| 35      | DB4    | H/L   | as a serial data output pin (SDO). Successive bit      |

| 36      | DB5    | H/L   | values are output on the falling edge of the SCL       |

| 37      | DB6    | H/L   | signal.                                                |

| 38      | DB7    | H/L   |                                                        |

| 39      | DB8    | H/L   | For a synchronous clock interface, E/WR                |

| 40      | DB9    | H/L   | serves as the synchronous clock signal:SCL             |

| 41      | DB10   | H/L   |                                                        |

| 42      | DB11   | H/L   | DB2-DB15 Serves as a 16-bit bi-directional data bus.   |

| 43      | DB12   | H/L   | For an 8-bit bus interface, data transfer uses         |

| 44      | DB13   | H/L   | DB15-DB8; fix unused DB7-DB0 to the Vcc or GND         |

| 45      | DB14   | H/L   | level. For a synchronous clock interface or unused     |

| 46      | DB15   | H/L   | pins, fixed to the Vcc or GND level.                   |

| 47      | VCI2   | -     | Connect capacitor for stabilization                    |

| 48      | C21-   | -     | When step-up circuit is used, connect a step-up        |

| 49      | C21+   | -     | capacitor                                              |

| 50      | C22-   | -     | When step-up circuit is used, connect a step-up        |

| 51      | C22+   | -     | capacitor                                              |

| 52      | C23-   | -     | When step-up circuit is used, connect a step-up        |

| 53      | C23+   | -     | capacitor                                              |

| 54      | C24-   | -     | When step-up circuit is used, connect a step-up        |

| 55      | C24+   | -     | capacitor                                              |

| 56      | VCH    | -     | Selection level for the common signal                  |

| 57      | VCL    | -     | Selection level for the common signal                  |

| 58      | CEM    | -     | Connect a step-up capacitor to generate VCL level      |

| 59      | CEP    | -     | Connect a step-up capacitor to generate VCL level      |

| 60      | RESET1 | H/L   | 2 RESET pins, use one pin and open unused pin          |

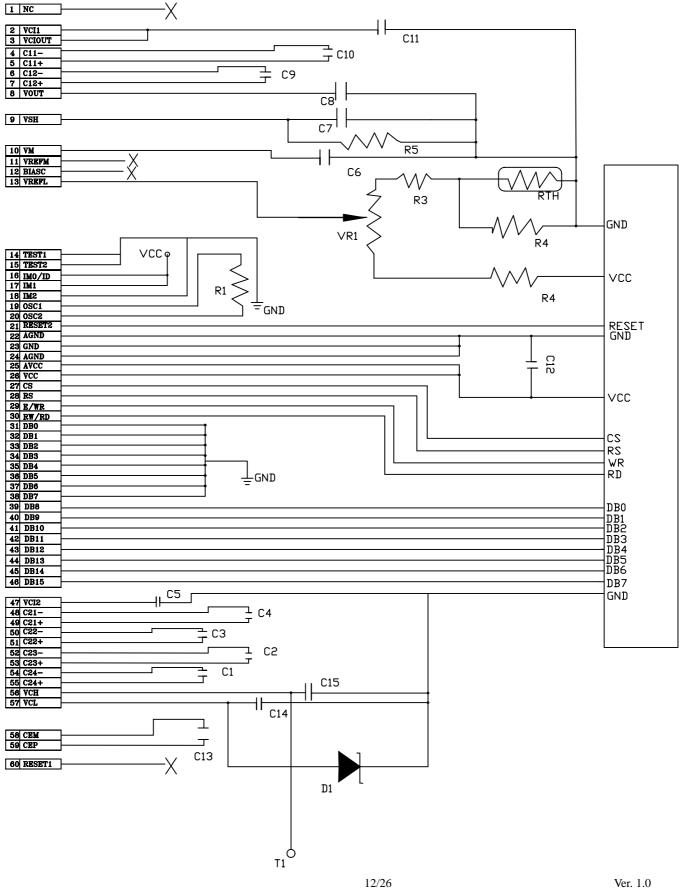

#### 6.2 Example of external Circuit(8080 Mode)

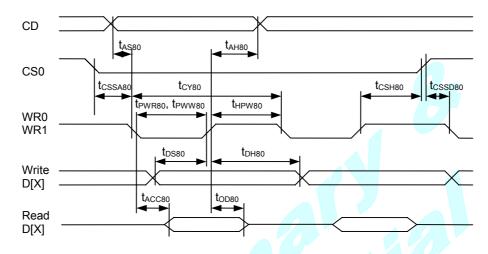

## 7. Interface Timing Chart

#### **AC CHARACTERISTICS**

FIGURE 15: Parallel Bus Timing Characteristics (for 8080 MCU)

<sup>(</sup>V<sub>DD</sub>=2.5V to 3.3V, Ta= -30 to +85°C)

| Symbol                                              | Signal   | Description                                                                       | Condition              | Min.                     | Max.     | Units |

|-----------------------------------------------------|----------|-----------------------------------------------------------------------------------|------------------------|--------------------------|----------|-------|

| t <sub>AS80</sub><br>t <sub>AH80</sub>              | CD       | Address setup time<br>Address hold time                                           |                        | 0<br>10                  | -        | ns    |

| t <sub>CY80</sub>                                   | 0        | System cycle time<br>8 bits bus (read)<br>(write)<br>4 bits bus (read)<br>(write) |                        | 140<br>128<br>128<br>128 | -        | ns    |

| t <sub>PWR80</sub>                                  | WR1      | Pulse width 8 bits (read)<br>4 bits                                               |                        | 65<br>35                 | -        | ns    |

| t <sub>PWW80</sub>                                  | WR0      | Pulse width 8 bits (write)<br>4 bits                                              |                        | 35<br>35                 | -        | ns    |

| t <sub>HPW80</sub>                                  | WR0, WR1 | High pulse width<br>8 bits bus (read)<br>(write)<br>4 bits bus (read)<br>(write)  |                        | 65<br>35<br>35<br>35     | _        | ns    |

| t <sub>DS80</sub><br>t <sub>DH80</sub>              | D0~D7    | Data setup time<br>Data hold time                                                 |                        | 30<br>10                 | -        | ns    |

| t <sub>ACC80</sub><br>t <sub>OD80</sub>             |          | Read access time<br>Output disable time                                           | C <sub>L</sub> = 100pF | -<br>10                  | 50<br>50 | ns    |

| tssaðo<br>t <sub>CSSDðo</sub><br>t <sub>CSHðo</sub> | CS1/CS0  | Chip select setup time                                                            |                        | 10<br>10<br>20           |          | ns    |

13/26

| Symbol                                 | Signal   | Description                             | Condition  | Min.    | Max. | Units |

|----------------------------------------|----------|-----------------------------------------|------------|---------|------|-------|

| t <sub>as80</sub><br>t <sub>ah80</sub> | CD       | Address setup time<br>Address hold time |            | 0<br>10 | -    | ns    |

| t <sub>CY80</sub>                      |          | System cycle time<br>8 bits bus (read)  |            | 210     | _    | ns    |

|                                        |          | (write)                                 |            | 120     |      |       |

|                                        |          | 4 bits bus (read)                       |            | 120     |      |       |

|                                        |          | (write)                                 |            | 120     |      |       |

| t <sub>PWR80</sub>                     | WR1      | Pulse width 8 bits (read)               |            | 100     | -    | ns    |

|                                        | WIXI     | 4 bits (read)                           |            | 55      |      |       |

| t <sub>PWW80</sub>                     | WR0      | Pulse width 8 bits (write)              |            | 55      | -    | ns    |

|                                        |          | 4 bits (write)                          |            | 55      |      |       |

| t <sub>HPW80</sub>                     |          | High pulse width                        |            |         | -    | ns    |

|                                        |          | 8 bits bus (read)                       |            | 100     |      |       |

|                                        | WR0, WR1 | (write)                                 |            | 55      |      |       |

|                                        |          | 4 bits bus (read)                       |            | 55      |      |       |

|                                        |          | (write)                                 |            | 55      |      |       |

| t <sub>DS80</sub>                      | D0~D7    | Data setup time                         |            | 30      | -    | ns    |

| t <sub>DH80</sub>                      | 50 51    | Data hold time                          |            | 10      |      |       |

| t <sub>ACC80</sub>                     |          | Read access time                        | C∟ = 100pF | -       |      | ns    |

| t <sub>OD80</sub>                      |          | Output disable time                     |            | 10      |      |       |

| tcssa80                                |          | Chip select setup time                  |            | 10      |      | ns    |

|                                        | CS1/CS0  |                                         |            | 10      |      |       |

| t <sub>CSH80</sub>                     |          |                                         |            | 20      |      |       |

$(V_{DD}=1.8V \text{ to } 2.5V, \text{ Ta}=-30 \text{ to } +85^{\circ}\text{C})$

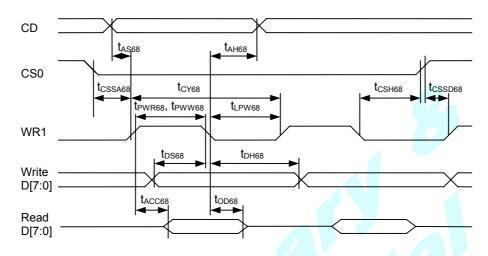

FIGURE 16: Parallel Bus Timing Characteristics (for 6800 MCU)

$<sup>(</sup>V_{DD}=2.5V \text{ to } 3.3V, \text{ Ta}=-30 \text{ to } +85^{\circ}\text{C})$

| Symbol                                  | Signal  | Description                                                                       | Condition              | Min.                     | Max.     | Units |

|-----------------------------------------|---------|-----------------------------------------------------------------------------------|------------------------|--------------------------|----------|-------|

| t <sub>as68</sub><br>t <sub>ah68</sub>  | CD      | Address setup time<br>Address hold time                                           |                        | 0<br>10                  | -        | ns    |

| Тсү68                                   |         | System cycle time<br>8 bits bus (read)<br>(write)<br>4 bits bus (read)<br>(write) |                        | 140<br>128<br>128<br>128 | _        | ns    |

| t <sub>PWR68</sub>                      | WR1     | Pulse width 8 bits (read)<br>4 bits                                               |                        | 65<br>35                 | -        | ns    |

| t <sub>PWW68</sub>                      |         | Pulse width 8 bits (write)<br>4 bits                                              |                        | 35<br>35                 | I        | ns    |

| t∟pw68                                  |         | Low pulse width<br>8 bits bus (read)<br>(write)<br>4 bits bus (read)<br>(write)   |                        | 65<br>35<br>35<br>35     | _        | ns    |

| t <sub>DS68</sub><br>t <sub>DH68</sub>  | D0~D7   | Data setup time<br>Data hold time                                                 |                        | 30<br>10                 | -        | ns    |

| t <sub>ACC68</sub><br>t <sub>OD68</sub> |         | Read access time<br>Output disable time                                           | C <sub>L</sub> = 100pF | -<br>10                  | 50<br>50 | ns    |

| tcssa68<br>tcssd68<br>tcsh68            | CS1/CS0 | Chip select setup time                                                            |                        | 10<br>10<br>20           |          | ns    |

$(V_{DD}=1.8V \text{ to } 2.5V, \text{ Ta}=-30 \text{ to } +85^{\circ}\text{C})$

| Symbol                                               | Signal  | Description                                                                     | Condition              | Min.                  | Max. | Units |

|------------------------------------------------------|---------|---------------------------------------------------------------------------------|------------------------|-----------------------|------|-------|

| t <sub>as68</sub><br>t <sub>ah68</sub>               | CD      | Address setup time<br>Address hold time                                         |                        | 0<br>10               | -    | ns    |

| T <sub>CY68</sub>                                    |         | System cycle time<br>8 bits bus (read)<br>(write)                               |                        | 210<br>120            | -    | ns    |

|                                                      |         | 4 bits bus (read)<br>(write)                                                    |                        | 120<br>120<br>120     |      |       |

| t <sub>PWR68</sub>                                   | WR1     | Pulse width 8 bits (read)<br>4 bits                                             |                        | 100<br>55             | -    | ns    |

| t <sub>PWW68</sub>                                   |         | Pulse width 8 bits (write)<br>4 bits                                            |                        | 55<br>55              | 1    | ns    |

| t <sub>LPW68</sub>                                   |         | Low pulse width<br>8 bits bus (read)<br>(write)<br>4 bits bus (read)<br>(write) |                        | 100<br>55<br>55<br>55 | _    | ns    |

| t <sub>DS68</sub><br>t <sub>DH68</sub>               | D0~D7   | Data setup time<br>Data hold time                                               |                        | 30<br>10              | -    | ns    |

| t <sub>ACC68</sub><br>t <sub>OD68</sub>              |         | Read access time<br>Output disable time                                         | C <sub>L</sub> = 100pF | -<br>10               |      | ns    |

| Tcssa68<br>T <sub>cssd68</sub><br>T <sub>csh68</sub> | CS1/CS0 | Chip select setup time                                                          |                        | 10<br>10<br>20        |      | ns    |

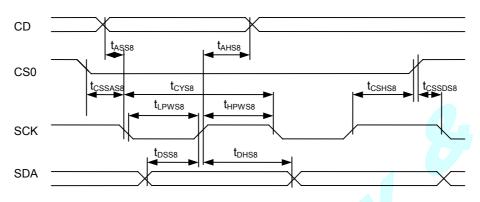

FIGURE 17: Serial Bus Timing Characteristics (for S8)

$(V_{DD}=2.5V \text{ to } 3.3V, \text{ Ta}=-30 \text{ to } +85^{\circ}\text{C})$

| Symbol                                 | Signal  | Description                       | Condition | Min.           | Max. | Units |

|----------------------------------------|---------|-----------------------------------|-----------|----------------|------|-------|

| t <sub>ASS8</sub>                      | CD      | Address setup time                |           | 0              | -    | ns    |

| t <sub>AHS8</sub>                      | CD      | Address hold time                 |           | 40             | -    | ns    |

| t <sub>CYS8</sub>                      |         | System cycle time                 |           | 135            | -    | ns    |

| t <sub>LPWS8</sub>                     | SCK     | Low pulse width                   |           | 65             | -    | ns    |

| t <sub>HPWS8</sub>                     |         | High pulse width                  |           | 65             | -    | ns    |

| t <sub>DSS8</sub><br>t <sub>DHS8</sub> | SDA     | Data setup time<br>Data hold time |           | 30<br>10       | -    | ns    |

| tcssas8<br>tcssds8<br>tcshs8           | CS1/CS0 | Chip select setup time            |           | 10<br>10<br>20 |      | ns    |

#### $(V_{DD}=1.8V \text{ to } 2.5V, \text{ Ta}=-30 \text{ to } +85^{\circ}\text{C})$

| Symbol                                               | Signal  | Description                       | Condition | Min.           | Max. | Units |

|------------------------------------------------------|---------|-----------------------------------|-----------|----------------|------|-------|

| t <sub>ASS8</sub>                                    | CD      | Address setup time                |           | 0              | -    | ns    |

| t <sub>AHS8</sub>                                    | CD      | Address hold time                 |           | 60             | -    | ns    |

| t <sub>CYS8</sub>                                    |         | System cycle time                 |           | 200            | 1    | ns    |

| t <sub>LPWS8</sub>                                   | SCK     | Low pulse width                   |           | 95             | 1    | ns    |

| t <sub>HPWS8</sub>                                   |         | High pulse width                  |           | 95             | 1    | ns    |

| t <sub>DSS8</sub><br>t <sub>DHS8</sub>               | SDA     | Data setup time<br>Data hold time |           | 30<br>10       | Ι    | ns    |

| tcssas8<br>t <sub>cssds8</sub><br>t <sub>cshs8</sub> | CS1/CS0 | Chip select setup time            |           | 10<br>10<br>20 |      | ns    |

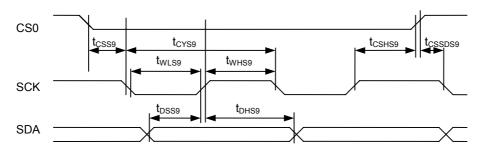

FIGURE 18: Serial Bus Timing Characteristics (for S9)

| $(V_{DD}=2.5V \text{ to } 3.3V, \text{ Ta}=-30 \text{ to } +85^{\circ}\text{C})$ |

|----------------------------------------------------------------------------------|

|----------------------------------------------------------------------------------|

| Symbol                                               | Signal  | Description                       | Condition | Min.           | Max. | Units |

|------------------------------------------------------|---------|-----------------------------------|-----------|----------------|------|-------|

| t <sub>CYS9</sub>                                    |         | System cycle time                 |           | 135            | -    | ns    |

| t <sub>LPWS9</sub>                                   | SCK     | Low pulse width                   |           | 65             | 1    | ns    |

| t <sub>HPWS9</sub>                                   |         | High pulse width                  |           | 65             | 1    | ns    |

| t <sub>DSS9</sub><br>t <sub>DHS9</sub>               | SDA     | Data setup time<br>Data hold time |           | 30<br>10       | -    | ns    |

| tcssas9<br>t <sub>cssds9</sub><br>t <sub>cshs9</sub> | CS1/CS0 | Chip select setup time            |           | 10<br>10<br>20 |      | ns    |

(V<sub>DD</sub>=1.8V to 2.5V, Ta= -30 to +85°C)

| Symbol                                 | Signal  | Description                       | Condition | Min.           | Max. | Units |

|----------------------------------------|---------|-----------------------------------|-----------|----------------|------|-------|

| t <sub>CYS9</sub>                      |         | System cycle time                 |           | 200            | -    | ns    |

| t <sub>LPWS9</sub>                     | SCK     | Low pulse width                   |           | 95             | -    | ns    |

| t <sub>HPWS9</sub>                     |         | High pulse width                  |           | 95             | -    | ns    |

| t <sub>DSS9</sub><br>t <sub>DHS9</sub> | SDA     | Data setup time<br>Data hold time |           | 30<br>10       | -    | ns    |

| tcssas9<br>tcssds9<br>tcshs9           | CS1/CS0 | Chip select setup time            |           | 10<br>10<br>20 |      | ns    |

## 8. Test of reliability

| No. | Test Item         | Content of Test                     | Test condition       |

|-----|-------------------|-------------------------------------|----------------------|

| 1   | High Temperature  | Endurance test applying the high    | 80                   |

|     | Storage           | storage temperature for a long time | 240H                 |

|     | Low Temperature   | Endurance test applying the low     | -30                  |

| 2   | Storage           | storage temperature for a long time | 240H restore 4H      |

|     |                   | Endurance test applying the         |                      |

| 2   | High Temperature  | electric stress (voltage & current) | 70                   |

| 3   | Operation         | and the thermal stress to the       | 70                   |

|     | _                 | element for a long time             | 240H                 |

|     | I T ·             | Endurance test applying the         | 20                   |

| 4   | Low Temperature   | electric stress under low           | -20                  |

|     | Operation         | temperature for a long time         | 240H                 |

|     |                   | Endurance test applying the high    | 60                   |

| 5   | High Temperature  | temperature and high humidity       | 95%RH                |

|     | /Humidity Storage | storage for a long time             | 240H                 |

|     |                   | Endurance test applying the low     |                      |

|     |                   | and high temperature cycle          |                      |

|     | Temperature       | -30 25 80 25                        | -30 /80              |

| 6   | Cycle             | 30min 5min 30min 5min               |                      |

|     |                   |                                     | 10 cycles            |

|     |                   | 1 cycle                             |                      |

|     |                   |                                     | 10Hz~500Hz,          |

| 7   | Vibration Test    | Endurance test applying the         | $100 \text{m/s}^2$ , |

|     | (package state)   | vibration during transportation     | 120min               |

|     |                   |                                     | Half- sine wave,     |

| 8   | Shock Test        | Endurance test applying the shock   | $300 \text{m/s}^2$ , |

|     | (package state)   | during transportation               | 18ms                 |

|     | A. 1 *            | Endurance test applying the         |                      |

| 9   | Atmospheric       | atmospheric pressure during         | 25kPa                |

|     | Pressure Test     | transportation by air               | 16H                  |

# 9. Inspection requirement

| Items                 | Contents                                      |                                 |                      |                        |                    |  |  |  |

|-----------------------|-----------------------------------------------|---------------------------------|----------------------|------------------------|--------------------|--|--|--|

| Protective<br>Glue    |                                               |                                 |                      | No clear defects       |                    |  |  |  |

| Cover tape            | Covering all of the chip and no clear crimple |                                 |                      |                        |                    |  |  |  |

| Leakage               | Not permitted                                 | l                               |                      |                        |                    |  |  |  |

| Rainbow               | According to                                  | the lin                         | nit specimen         |                        |                    |  |  |  |

|                       | Wrong polarizer<br>attachment                 | Not permitted                   |                      |                        |                    |  |  |  |

| Polarizer             | Bubble between                                | Not counted                     |                      | Max. 3 defects allowed |                    |  |  |  |

| I Olarizer            | polarizer and glass                           | ф<0.3mm                         | 0.3mm ø 0.5          |                        | nm                 |  |  |  |

|                       | Scratches of polarizer                        | According to the limit specimen |                      |                        |                    |  |  |  |

| Black spot            |                                               | Not counted                     | Max. 3 spots allowed |                        |                    |  |  |  |

| (in viewing area)     |                                               | X<0.20mm                        | 0.20mm X 0.5mm       |                        | Max. 3             |  |  |  |

|                       | I+0,+I                                        | X=(a+b)/2                       |                      |                        | spots              |  |  |  |

| Black line            | 1                                             | Not counted                     | Max                  | . 3 lines allowed      | (lines)<br>allowed |  |  |  |

| (in viewing area)     | t b                                           | a<0.02mm                        | 0.02mm a 0.05mm      |                        |                    |  |  |  |

|                       |                                               |                                 | <u> </u>             | b 2.0mm                |                    |  |  |  |

| Progressive<br>cracks |                                               | Not permitted                   | l                    |                        |                    |  |  |  |

## 9.1 Inspection items and criteria for appearance defects

| Items           | Contents                   |                                    |       |     | Criteria                                               |                  |         |

|-----------------|----------------------------|------------------------------------|-------|-----|--------------------------------------------------------|------------------|---------|

|                 | Cracks on pads             | a                                  | b     |     | с                                                      |                  |         |

|                 |                            | 3mm                                | W     | V/5 | T/2                                                    | Max. 2<br>Cracks |         |

|                 | +<br>+<br>+                | 2mm                                | V     | V/5 | T/2 <c<t< td=""><td>allowed</td><td></td></c<t<>       | allowed          |         |

|                 | Cracks on contact side     | a                                  |       |     | b                                                      |                  |         |

|                 |                            | 3m                                 | m     |     | T/2                                                    |                  |         |

|                 |                            | 2m                                 | m     | ]   | Г/2 <b<t< td=""><td></td><td></td></b<t<>              |                  |         |

|                 |                            | C shall be not reach the seal area |       |     |                                                        |                  |         |

|                 | Cracks on non-contact side | a b                                |       | b   |                                                        | Max. 5           |         |

|                 |                            | 3m                                 | m     |     | T/2                                                    | Max. 2           | cracks  |

| Glass<br>Cracks |                            | 2m                                 | m     | ]   | Г/2 <b<t< td=""><td>cracks</td><td>allowed</td></b<t<> | cracks           | allowed |

| Clacks          |                            | C 0.5mm                            |       |     | allowed                                                |                  |         |

|                 | - sw -                     | d SW/3                             |       |     |                                                        |                  |         |

|                 | Corner cracks              | e<2.0mn                            | $n^2$ |     |                                                        |                  |         |

|                 |                            | f<2.0mm <sup>2</sup>               |       |     | Max. 3                                                 |                  |         |

|                 |                            |                                    |       |     |                                                        | cracks           |         |

|                 | f-                         |                                    |       |     |                                                        | allowed          |         |

# Inspection item and criteria for appearance defects (continued)

## 9.2Inspection items and criteria for display defects

| <b></b>                            |          |               |                    |                            |               |  |  |  |

|------------------------------------|----------|---------------|--------------------|----------------------------|---------------|--|--|--|

| Items                              |          | Contents      | Critera            |                            |               |  |  |  |

| Open segment or open common        |          | Not permitted |                    |                            |               |  |  |  |

| Short                              |          |               | Not permitted      | l                          |               |  |  |  |

| Wrong viewi                        | ng angle |               | Not permitted      | l                          |               |  |  |  |

| Contrast radi                      | o unever | 1             | According to       | the limit specimen         |               |  |  |  |

| Crosstalk                          |          |               | According to       | the limit specimen         |               |  |  |  |

|                                    | _        |               | Not counted        | Max.3 dots allowed         |               |  |  |  |

|                                    | Ĵ∐<br>⊤⊨ |               | X<0.1mm            | 0.1mm X 0.2mm              | -             |  |  |  |

|                                    |          |               | X=(a+b)/2          |                            |               |  |  |  |

| Pin holes                          | D <      | Not counted   | Max.2 dots allowed | Max.3<br>dots              |               |  |  |  |

| and cracks<br>in segment<br>(DOT)  |          |               | A<0.1mm            | 0.1mm A 0.2mm<br>D<0.25mm  | allowed       |  |  |  |

|                                    |          |               | Not counted        | Max.3 spots allowed        |               |  |  |  |

| Black spot<br>(in viewing          |          |               | X<0.1mm            | 0.1mm X 0.2mm              |               |  |  |  |

| area)                              |          |               | X=(a+b)/2          |                            | Max.3         |  |  |  |

| D1. 1. 1                           |          |               | Not counted        | Max.3 lines allowed        | spots (lines) |  |  |  |

| Black line<br>(in viewing<br>area) | t o      |               | a<0.02mm           | 0.02mm a 0.05mm<br>b 0.5mm | allowed       |  |  |  |

|           | Not counted<br>x < 0.1mm<br>x=(a+b)/2                 | Max. 2 defects allowed<br>0.1mm x 0.2mm      |                                             |  |  |  |

|-----------|-------------------------------------------------------|----------------------------------------------|---------------------------------------------|--|--|--|

|           |                                                       | 0.1mm x 0.2mm                                |                                             |  |  |  |

|           | x=(a+b)/2                                             |                                              |                                             |  |  |  |

|           |                                                       |                                              |                                             |  |  |  |

| D-+1+1+-a | Not counted Max. 1 defects allowed                    |                                              | _                                           |  |  |  |

|           | a < 0.1mm                                             | 0.1mm a 0.2mm                                |                                             |  |  |  |

|           |                                                       | D>0                                          | Max.3                                       |  |  |  |

|           | Max.2 defects allowed<br>0.8W a 1.2W                  |                                              |                                             |  |  |  |

|           | a=measured value of width<br>W=nominal value of width |                                              |                                             |  |  |  |

|           |                                                       | Max.2 defects<br>0.8W a 1.2<br>a=measured va | D>0<br>Max.2 defects allowed<br>0.8W a 1.2W |  |  |  |

# Inspection items and criteria for display defects (continued)

# 10. Quality level

| Examination           | At T <sub>amb</sub> =25                                                      |         | Ι    | nspecti | on    |       |  |  |  |

|-----------------------|------------------------------------------------------------------------------|---------|------|---------|-------|-------|--|--|--|

| or Test               | (unless otherwise stated)                                                    | Min.    | Max. | Unit    | IL    | AQL   |  |  |  |

| External              | Under normal illumination                                                    |         |      |         | Major |       |  |  |  |

| Visual                | and eyesight condition, the                                                  | See 9.1 |      |         | П     | 1.0   |  |  |  |

| Inspection            | distance between eyes and                                                    | See 9.1 |      |         | 11    | Minor |  |  |  |

| Inspection            | LCD is 25cm.                                                                 |         |      |         | 2.5   |       |  |  |  |

|                       | Under normal illumination                                                    |         |      |         | Major |       |  |  |  |

| Display               | and eyesight condition,                                                      | See 9.2 |      |         | п     | 1.0   |  |  |  |

| Defects               | display on inspection.                                                       | 500 9.2 |      |         |       | Minor |  |  |  |

|                       |                                                                              |         |      |         |       | 2.5   |  |  |  |

| Note: Major d         | Note: Major defects: Open segment or common, Short, Serious damages, Leakage |         |      |         |       |       |  |  |  |

| Miner defects: Others |                                                                              |         |      |         |       |       |  |  |  |

| Samplin               | Sampling standard conforms to GB2828                                         |         |      |         |       |       |  |  |  |

- 11. Precautions for Use of LCD Modules

- 11.1 Handling Precautions

- 11.1.1 The display panel is made of glass. Do not subject it to a mechanical shock by dropping it from a high place, etc.

- 11.1.2 If the display panel is damaged and the liquid crystal substance inside it leaks out, be sure not to get any in your mouth, if the substance comes into contact with your skin or clothes, promptly wash it off using soap and water.

- 11.1.3 Do not apply excessive force to the display surface or the adjoining areas since this may cause the color tone to vary.

- 11.1.4 The polarizer covering the display surface of the LCD module is soft and easily scratched. Handle this polarizer carefully.

- 11.1.5 If the display surface is contaminated, breathe on the surface and gently wipe it with a soft dry cloth. If still not completely clear, moisten cloth with one of the following solvents:

- Isopropyl alcohol

- Ethyl alcohol

Solvents other than those mentioned above may damage the polarizer. Especially, do not use the following:

- Water

- Ketone

- Aromatic solvents

- 11.1.6 Do not attempt to disassemble the LCD Module.

- 11.1.7 If the logic circuit power is off, do not apply the input signals.

- 11.1.8 To prevent destruction of the elements by static electricity, be careful to maintain an optimum work environment.

- a. Be sure to ground the body when handling the LCD Modules.

- b. Tools required for assembly, such as soldering irons, must be properly ground.

- c. To reduce the amount of static electricity generated, do not conduct assembly and other work under dry conditions.

- d. The LCD Module is coated with a film to protect the display surface. Be care when peeling off this protective film since static electricity may be generated.

11.2 Storage precautions

11.2.1 When storing the LCD modules, avoid exposure to direct sunlight or to the light of fluorescent lamps.

11.2.2 The LCD modules should be stored under the storage temperature range. If the LCD modules will be stored for a long time, the recommend condition is:

Temperature :0~ 40Relatively humidity:80%

- 11.2.3 The LCD modules should be stored in the room without acid, alkali and harmful gas.

- 11.3 The LCD modules should be no falling and violent shocking during transportation, and also should avoid excessive press, water, damp and sunshine.