## 2.488/2.666GBPS OC-48/STM-16 SONET/SDH TRANSCEIVER

JANUARY 2004 REV. P1.0.3

#### GENERAL DESCRIPTION

**XY** EXAR

The XRT91L81 is a fully integrated SONET/SDH transceiver block for applications in SONET OC-48 allowing the use of Forward Error Correction (FEC) capability. The transceiver includes an on-chip Clock Multiplier Unit (CMU), which uses a high frequency Phase-Locked Loop (PLL) to generate the highspeed transmit serial clock from slower external clock references. It also provides Clock and Data Recovery (CDR) functions by synchronizing its on-chip Voltage Controlled Oscillator (VCO) to the incoming serial data stream. The chip provides serial-to-parallel and parallel-to-serial converters and 4-bit LVDS system interfaces in both receive and transmit directions. The transmit section includes a 4x9 Elastic Buffer (FIFO) to absorb any phase differences between the transmitter input clock and the internally generated transmitter reference clock. In the event of an overflow, an internal FIFO control circuit outputs an OVERFLOW indication. The FIFO under the control of the AUTORST pin can automatically recover from

an overflow condition. The operation of the device can be monitored by checking the status of the LOCKDET and LOSDET output signals. An on-chip phase/frequency detector and charge-pump offers the ability to form a de-jittering PLL with an external VCXO that can be used in loop timing mode to clean up the recovered clock in the receive section.

#### **APPLICATIONS**

- SONET/SDH-based Transmission Systems

- Add/Drop Multiplexers

- Cross Connect Equipment

- ATM and Multi-Service Switches, Routers and Switch/Routers

- DSLAMS

- SONET/SDH Test Equipment

- DWDM Termination Equipment

- Optical Modules and Sub-Systems

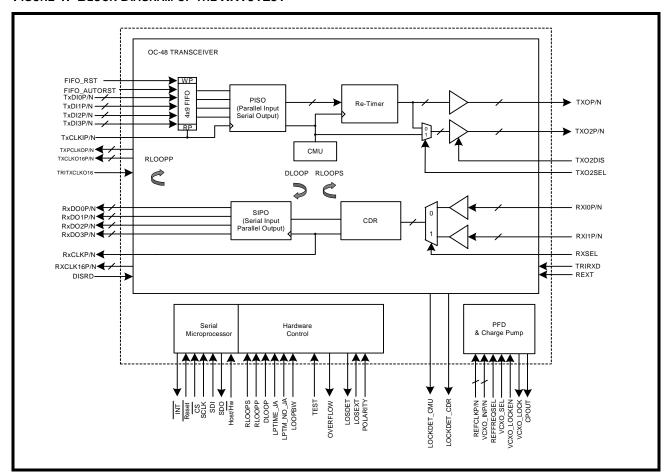

FIGURE 1. BLOCK DIAGRAM OF THE XRT91L81

#### 2.488/2.666GBPS OC-48/STM-16 SONET/SDH TRANSCEIVER

REV. P1.0.3

PRELIMINARY

#### **FEATURES**

- 2.488 / 2.666 Gbps Transceiver

- Single-chip fully integrated solution containing parallel-to-serial converter, clock multiplier unit (CMU), serial-to-parallel converter, limiting amplifier and clock data recovery (CDR) functions

- Host mode serial microprocessor interface simplifies monitor and control

- Provides support for dual fiber rings

- Integrated limiting amplifier accepts differential inputs down to 10mVp-p

- Separate reference and VCXO input ports support multiple de-jittering modes

- On-chip phase detector and charge pump for external VCXO based de-jittering PLL

- Targeted for SONET OC-48/SDH STM-16 Applications

- Selectable full duplex operation between standard rate of 2.488 Gbps or Forward Error Correction rate of 2.666 Gbps

- 4-bit LVDS data paths at 622/666 MHz complies with OIF SFI-4 Implimentation Agreement

- Internal FIFO decouples transmit input and output clocks

- Tx CMU and Rx CDR lock detect

- Provides Local, Remote and Split Loop-Back modes as well as Loop Timing mode

- Diagnostics features include various lock detect functions

- Meets Telcordia, ANSI and ITU-T jitter requirements

- Operates at 1.8V with 3.3V I/O

- 600mW Typical Power Dissipation

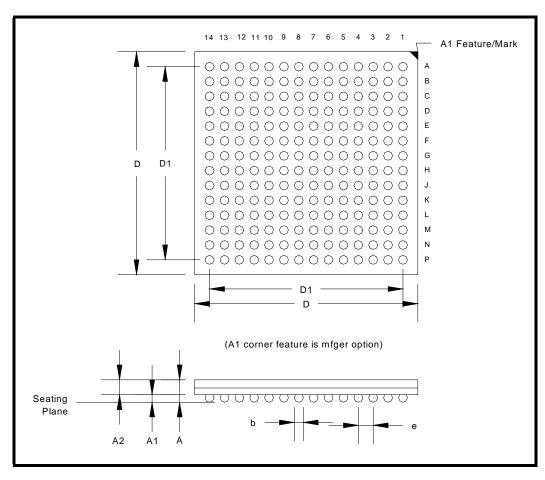

- Package: 12 x 12 mm 196-pin STBGA

## PRODUCT ORDERING INFORMATION

| PRODUCT NUMBER | PACKAGE TYPE | OPERATING TEMPERATURE RANGE |

|----------------|--------------|-----------------------------|

| XRT91L81IB     | 196 STBGA    | -40°C to +85°C              |

**X** EXAR

TABLE 1: 196 BGA PINOUT OF THE XRT91L81 (TOP VIEW)

| _        | Z       | ۵                     | Z                                | δ          | Ž          | ۵          | ΔI      | S          | <u> </u> | Z          | <u>۳</u>                    | Z                                                           | 6.                      |    |

|----------|---------|-----------------------|----------------------------------|------------|------------|------------|---------|------------|----------|------------|-----------------------------|-------------------------------------------------------------|-------------------------|----|

| RXD3P    | RXD3N   | RXD1P                 | RXD1N                            | RXCLKP     | RXCLKN     | DGND       | TXCLKIP | TXCLKIN    | TXDI1P   | TXDI1N     | TXDI3                       | TXDI3N                                                      | VDD3.3                  | 41 |

| VDD3.3   | VDD3.3  | RXD2P                 | RXD2N                            | RXD0P      | RXDON      | DGND       | TXDI0P  | TXDION     | TXDI2P   | TXDI2N     | OVERFLOW                    | FIFO_RESE                                                   | VDD3.3                  | 13 |

| DGND     | DGND    | TRIRXD                | VDD1.8                           | VDD1.8     | DGND       | DGND       | DGND    | DGND       | DGND     | DGND       | TRITXCLKO16 OVERFLOW TXDI3P | /CXO_LOCKAVDD1.8_TXTXCLKO16PTXCLKO16NFIFO_AUTORSTFIFO_RESET | DGND                    | 12 |

| RLOOPP   | DGND    | INTB                  | VDD3.3                           | VDD3.3     | DGND       | DGND       | DGND    | DGND       | VDD1.8   | DGND       | VDD1.8                      | TXCLKO16N                                                   | TXPCLKON                | 11 |

| CSB      | Reset   | RLOOPS                | VDD3.3                           | TGND       | TGND       | TGND       | TGND    | TGND       | TGND     | VDD1.8     | VDD1.8                      | ТХСЬКО16Р                                                   | AVDD3.3_TX TXPCLKOP     | 10 |

| SDI      | SCLK    | HOST/HWB              | v.sdav                           | TGND       | TGND       | TGND       | TGND    | TGND       | TGND     | VDD1.8     | VDD1.8                      | AVDD1.8_TX                                                  | AVDD3.3_TX              | 6  |

| VDD3.3   | DGND    | SDO                   | AVDD1.8_RX                       | TGND       | TGND       | TGND       | TGND    | TGND       | TGND     | AVDD1.8_TX | S<br>S                      | VCXO_LOCK                                                   | CPOUT ,                 | 8  |

| RXCLK16N | VDD1.8  | LPTIME_JA LOCKDET-CDR | AGND_RX ,                        | TGND       | TGND       | TGND       | TGND    | TGND       | TGND     | AVDD1.8_TX | LOOPBW                      | AGND_TX                                                     | AGND_TX                 | 7  |

| RXCLK16P | DLOOP   | LPTIME_JA I           | AVDD1.8_RX                       | TGND       | TGND       | TGND       | TGND    | TGND       | TGND     | AVDD1.8_TX | VCXO_SEL                    | REFCLKN                                                     | REFCLKP                 | 9  |

| DGND     | LOSEXT  | LOSDET                | AVDD1.8_RX AVDD1.8_RX AVDD1.8_RX | TGND       | TGND       | TGND       | TGND    | TGND       | TGND     | AGND_TX    | AGND_TX                     | AGND_TX                                                     | AVDD3.3_TX              | 2  |

| DGND     | DGND    | POLARITY              | AVDD1.8_RX.                      | AGND_RX    | AGND_RX    | AGND_RX    | AGND_RX | AVDD1.8_TX | AGND_TX  | AGND_TX    | AGND_TX                     | VCXO_INN                                                    | VCXO_INP                | 4  |

| DISRD    | DGND    | AGND_RX               | AVDD3.3_RX /                     | AVDD3.3_RX | AVDD1.8_RX | AVDD1.8_RX | AGND_RX | AGND_TX    | AGND_TX  | DGND       | AVDD1.8_TX                  | TXO2_SEL                                                    | VCXO_LOCKEN             | 3  |

| RXSEL    | AGND_RX | AGND_RX               | AGND_RX                          | AGND_RX    | AGND_RX    | AGND_RX    | AGND_RX | AGND_TX    | NOXT     | TXOP       | AVDD3.3_TX                  | LOCKDET-CMU                                                 | LPTIME_NO_JAVCXO_LOCKEN | 2  |

| REXT     | AGND_RX | RXIOP                 | RXION                            | AGND_RX    | RXI1N      | RXI1P      | AGND_RX | AVDD3.3_TX | TXO2P    | TXO2N      | AGND_TX                     | TXO2DIS                                                     | REFFREQSELL             | _  |

|          | m       | ()                    | _                                | 111        | 1.         | ניו        |         |            |          |            | 5                           | 7                                                           | ń                       | -  |

# **TABLE OF CONTENTS**

| GENERAL DESCRIPTION                                            |    |

|----------------------------------------------------------------|----|

| APPLICATIONS                                                   |    |

| FIGURE 1. BLOCK DIAGRAM OF THE XRT91L81                        |    |

| FEATURES                                                       |    |

| PRODUCT ORDERING INFORMATION                                   |    |

| TABLE 1: 196 BGA PINOUT OF THE XRT91L81 (TOP VIEW)             |    |

| TABLE OF CONTENTS                                              |    |

| PIN DESCRIPTIONS                                               |    |

|                                                                |    |

| SERIAL MICROPROCESSOR INTERFACE                                |    |

| HARDWARE CONTROL                                               | -  |

| Transmitter Section                                            | 6  |

| RECEIVER SECTION                                               | 8  |

| POWER AND GROUND                                               | 10 |

| NO CONNECTS                                                    | 11 |

| 1.0 FUNCTIONAL DESCRIPTION                                     |    |

| 1.1 HARDWARE MODE VS. HOST MODE                                |    |

| 1.2 INPUT CLOCK REFERENCE                                      |    |

| 1.3 FORWARD ERROR CORRECTION (FEC)                             |    |

| TABLE 2: REFERENCE FREQUENCY OPTIONS (NORMALMODE/FEC)          |    |

| FIGURE 2. SIMPLIFIED BLOCK DIAGRAM OF FORWARD ERROR CORRECTION |    |

| 2.0 RECEIVE SECTION                                            |    |

| 2.1 RECEIVE SERIAL INPUT                                       |    |

| FIGURE 3. RECEIVE SERIAL INPUT INTERFACE BLOCK                 |    |

| 2.2 RECEIVE CLOCK AND DATA RECOVERY                            |    |

| 2.3 LOSS OF SIGNAL                                             |    |

| 2.4 RECEIVE SERIAL INPUT TO PARALLEL OUTPUT (SIPO)             | 14 |

| FIGURE 4. SIMPLIFIED BLOCK DIAGRAM OF SIPO                     | 14 |

| 2.5 RECEIVE PARALLEL OUTPUT INTERFACE                          |    |

| 2.6 RECEIVE PARALLEL OUTPUT DATA TIMING                        | 15 |

| FIGURE 6. RECEIVE PARALLEL OUTPUT TIMING                       |    |

| TABLE 3: RECEIVE PARALLEL OUTPUT DATA TIMING SPECIFICATIONS    |    |

| 2.7 DISABLE RECEIVE OUTPUT DATA UPON LOS                       |    |

| 2.8 TRI-STATE RECEIVE OUTPUT DATA                              |    |

| FIGURE 5. RECEIVE PARALLEL OUTPUT INTERFACE BLOCK              |    |

| 3.0 TRANSMIT SECTION                                           |    |

| 3.1 TRANSMIT PARALLEL INTERFACE                                |    |

| FIGURE 7. TRANSMIT PARALLEL INPUT INTERFACE BLOCK              |    |

| 3.2 TRANSMIT PARALLEL INPUT DATA TIMING                        |    |

| FIGURE 8. TRANSMIT PARALLEL INPUT TIMING                       |    |

| TABLE 4: TRANSMIT PARALLEL INPUT DATA TIMING SPECIFICATIONS    |    |

| 3.4 FIFO CALIBRATION UPON POWER UP                             |    |

| 3.4 FIFO CALIBRATION UPON POWER UP                             |    |

| 3.5 TRANSMIT PARALLEL INPUT TO SERIAL OUTPUT (PISO)            |    |

| FIGURE 9. SIMPLIFIED BLOCK DIAGRAM OF PISO                     |    |

| FIGURE 9. SIMPLIFIED BLOCK DIAGRAM OF PISO                     |    |

| 3.7 LOOP TIMING AND CLOCK CONTROL                              |    |

| TABLE 5: LOOP TIMING AND REFERENCE DE-JITTER CONFIGURATIONS    |    |

| 3.8 EXTERNAL LOOP FILTER                                       |    |

| FIGURE 12. SIMPLIFIED DIAGRAM OF THE EXTERNAL LOOP FILTER      |    |

| FIGURE 11. LOOP TIMING MODE USING AN EXTERNAL CLEANUP VCXO     |    |

| 3.9 TRANSMIT SERIAL OUTPUT CONTROL                             |    |

| FIGURE 13. TRANSMIT SERIAL OUTPUT INTERFACE                    |    |

| 4.0 DIAGNOSTIC FEATURES                                        | 23 |

| 4.1 SERIAL REMOTE LOOPBACK                                     | 23 |

| 4.2 PARALLEL REMOTE LOOPBACK                                   | 23 |

| FIGURE 14. SERIAL REMOTE LOOPBACK                              |    |

REV. P1.0.3

|     | FIGURE 15. PARALLEL REMOTE LOOPBACK                                                   | 23  |

|-----|---------------------------------------------------------------------------------------|-----|

|     | 4.3 DIGITAL LOCAL LOOPBACK                                                            | 24  |

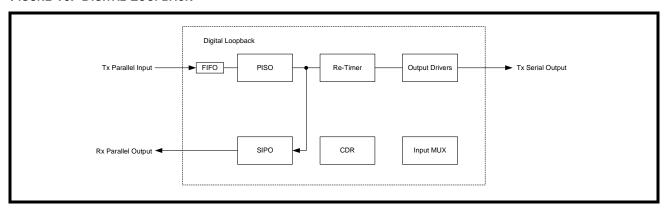

|     | FIGURE 16. DIGITAL LOOPBACK                                                           |     |

|     | 4.4 SONET JITTER REQUIREMENTS                                                         | 25  |

|     | 4.4.1 JITTER TOLERANCE:                                                               | 25  |

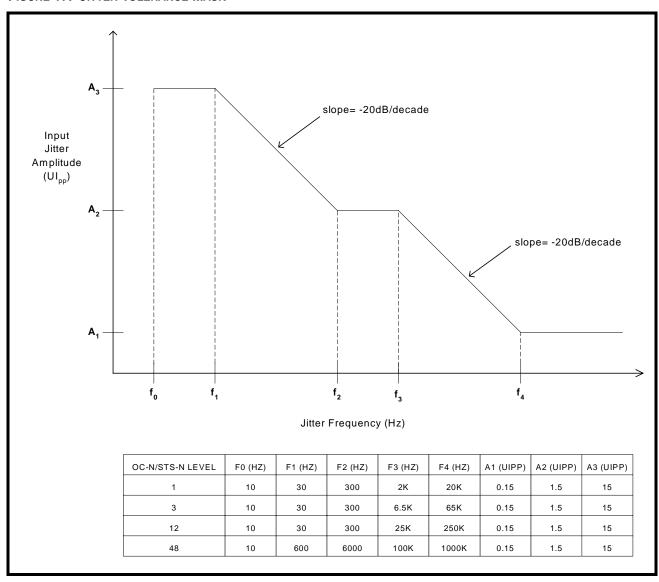

|     | FIGURE 17. JITTER TOLERANCE MASK                                                      |     |

|     | 4.4.2 JITTER TRANSFER                                                                 |     |

|     | 4.4.3 JITTER GENERATION                                                               |     |

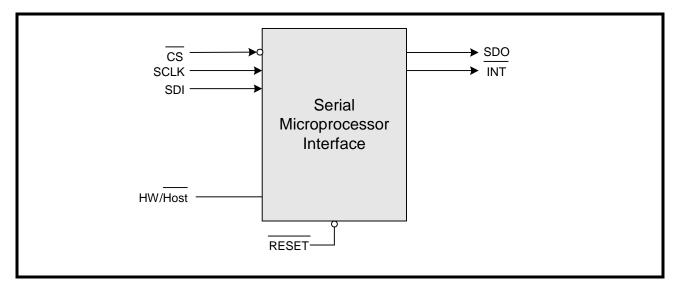

| 5.0 | SERIAL MICROPROCESSOR INTERFACE BLOCK                                                 |     |

|     | FIGURE 18. SIMPLIFIED BLOCK DIAGRAM OF THE SERIAL MICROPROCESSOR INTERFACE            |     |

|     | 5.1 SERIAL TIMING INFORMATION                                                         |     |

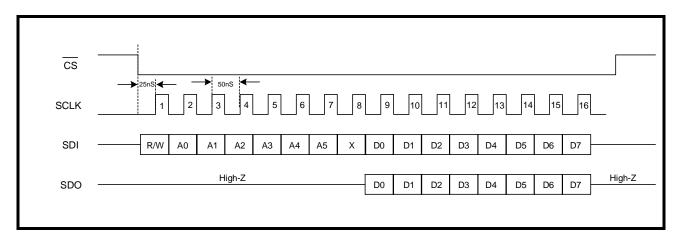

|     | FIGURE 19. TIMING DIAGRAM FOR THE SERIAL MICROPROCESSOR INTERFACE                     |     |

|     | 5.2 16-BIT SERIAL DATA INPUT DESCRITPTION                                             |     |

|     | 5.2.1 R/W (SCLK1)                                                                     |     |

|     | 5.2.2 A[5:0] (SCLK2 - SCLK7)                                                          |     |

|     | 5.2.3 X (DUMMY BIT SCLK8)                                                             |     |

|     | 5.2.4 D[7:0] (SCLK9 - SCLK16)                                                         |     |

|     | 5.3 8-BIT SERIAL DATA OUTPUT DESCRIPTION                                              |     |

| 6.0 |                                                                                       |     |

|     | TABLE 7: MICROPROCESSOR REGISTER BIT DESCRIPTION                                      |     |

|     | TABLE 6: MICROPROCESSOR REGISTER MAP TABLE 9: MICROPROCESSOR REGISTER BIT DESCRIPTION |     |

|     | TABLE 9: MICROPROCESSOR REGISTER BIT DESCRIPTION                                      |     |

|     | TABLE 10: MICROPROCESSOR REGISTER BIT DESCRIPTION                                     |     |

|     | TABLE 11: MICROPROCESSOR REGISTER BIT DESCRIPTION                                     |     |

|     | TABLE 12: MICROPROCESSOR REGISTER BIT DESCRIPTION                                     |     |

|     | TABLE 13: MICROPROCESSOR REGISTER 0x02H BIT DESCRIPTION                               |     |

|     | TABLE 14: MICROPROCESSOR REGISTER 0x01H BIT DESCRIPTION                               |     |

| 7.0 | ) ELECTRICAL CHARACTERISTICS                                                          | 36  |

|     | ABSOLUTE MAXIMUMS                                                                     | 36  |

|     | DC ELECTRICAL CHARACTERISTICS                                                         | .36 |

|     | 196 SHRINK THIN BALL GRID ARRAY                                                       |     |

|     |                                                                                       |     |

|     | (12.0 мм x 12.0 мм, STBGA)                                                            |     |

|     | Rev. 1.00                                                                             |     |

|     | ORDERING INFORMATION                                                                  |     |

|     | REVISION HISTORY                                                                      | 38  |

**PRELIMINARY**

# **PIN DESCRIPTIONS**

## SERIAL MICROPROCESSOR INTERFACE

| NAME    | LEVEL | Түре | Pin | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                     |

|---------|-------|------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Host/Hw | LVTTL | I    | C9  | Host or Hardware Mode Select Input The XRT91L81 offers two modes of operation for interfacing to the device. The Host mode uses a serial microprocessor interface for programming individual registers. The Hardware mode is controlled by the state of the hardware pins set by the user. By default, the device is configured in the Hardware mode.  "Low" = Hardware Mode "High" = Host Mode |

| CS      | LVTTL | I    | A10 | Chip Select Input (Host Mode Only)  Active low signal. This signal enables the serial microprocessor interface by pulling chip select "Low". The serial microprocessor is disabled when the chip select signal returns "High".                                                                                                                                                                  |

| SCLK    | LVTTL | I    | В9  | Serial Clock Input (Host Mode Only)  Once CS is pulled "Low", the serial microprocessor interface requires 16 clock cycles for a complete Read or Write operation.                                                                                                                                                                                                                              |

| SDI     | LVTTL | I    | A9  | Serial Data Input (Host Mode Only) When CS is pulled "Low", the serial input data is sampled on the rising edge of SCLK.                                                                                                                                                                                                                                                                        |

| SDO     | LVTTL | 0    | C8  | Serial Data Output (Host Mode Only)  If a Read function is initiated, the serial output data is updated on the falling edge of SCLK8 through SCLK15, with the LSB (D0) updated first. This enables the data to be sampled on the rising edge of SCLK9 through SCLK16.                                                                                                                           |

| INT     | LVTTL | 0    | C11 | Interrupt Output (Host Mode Only)  Active low signal. This signal is asserted "Low" when a change in alarm status occurs. Once the status registers have been read, the interrupt pin will return "High".                                                                                                                                                                                       |

| Reset   | LVTTL | I    | B10 | Master Reset Input Active low signal. When this pin is pulled "Low" for more than 10μS, the internal registers are set to their default state. See the register description for the default values.                                                                                                                                                                                             |

**X** EXAR

REV. P1.0.3

## HARDWARE CONTROL

| NAME         | LEVEL | Түре | Pin | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------|-------|------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RLOOPS       | LVTTL | I    | C10 | Serial Remote Loopback Hardware Mode The serial remote loopback mode interconnects the receive serial input data to the transmit serial output data. If serial remote loopback is enabled, the 4-bit parallel transmit input data is ignored while the 4-bit parallel receive output data is maintained.  "Low" = Disabled "High" = Serial Remote Loopback Mode Enabled                                                                                                            |

| RLOOPP       | LVTTL | I    | A11 | Parallel Remote Loopback Hardware Mode The parallel remote loopback mode allows the input serial data stream to pass through the clock and data recovery circuit and loopback at the parallel interface to the serial output port. The 4-bit parallel transmit input data is ignored while the 4-bit parallel receive output data is maintained.  "Low" = Disabled "High" = Parallel Remote Loopback Mode Enabled                                                                  |

| DLOOP        | LVTTL | I    | B6  | Digital Loopback Hardware Mode The digital loopback mode interconnects the 4-bit parallel transmit input data and TxCLK to the 4-bit parallel receive output data and RxCLK respectively while maintaining the transmit serial output data. If digital loopback is enabled, the receive serial input data is ignored. "Low" = Disabled "High" = Digital Loopback Mode Enabled  Note: DLOOP and RLOOPS can be enabled simultaneously to achieve a dual loopback diagnostic feature. |

| LPTIME_JA    | LVTTL | I    | C6  | Loop Timing Mode With JA  The LPTIME_JA pin must be set "High" in order to select the recovered receive clock as the reference source for the de-jitter PLL.  "Low" = Disabled  "High" = Enabled                                                                                                                                                                                                                                                                                   |

| LPTIME_NO_JA | LVTTL | I    | P2  | Loop Timing Mode With No JA  When the loop timing mode is activated the external reference clock to the input of the CMU is replaced with the 1/16th or the 1/32nd of the high-speed recovered receive clock from the CDR.  "Low" = Disabled "High" = Loop timing Activated                                                                                                                                                                                                        |

REV. P1.0.3

# 2.488/2.666GBPS OC-48/STM-16 SONET/SDH TRANSCEIVER

**PRELIMINARY**

## TRANSMITTER SECTION

| NAME                                                    | LEVEL   | Түре | Pin                                           | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------------------------------------------|---------|------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TXDIOP TXDION TXDI1P TXDI1N TXDI2P TXDI2N TXDI3P TXDI3N | LVDS    | I    | H13<br>J13<br>K14<br>L14<br>K13<br>L13<br>M14 | Transmit Parallel Data Input The 622Mbps 4-bit parallel transmit input data should be applied to the transmitters simultaneously referenced to the rising edge of the TXCLKI input. The 4-bit parallel interface is multiplexed into the transmit serial output interface MSB first (TXDI3P/N).  Note: The XRT91L81 can accept 666Mbps 4-bit parallel transmit input data for Forward Error Correction (FEC) Applications. |

| TXCLKIP<br>TXCLKIN                                      | LVDS    | I    | H14<br>J14                                    | Transmit Input Clock 622MHz input clock reference for the 4-bit parallel transmit input data TXDIP/N[3:0].  Note: The XRT91L81 can accept a 666MHz transmit input clock for Forward Error Correction (FEC) Applications.                                                                                                                                                                                                   |

| TXOP<br>TXON                                            | CMLDIFF | 0    | L2<br>K2                                      | Transmit Serial Data Output  The transmit serial data stream is generated by multiplexing the 4-bit parallel transmit input data into a 2.488Gbps serial data stream. In Forward Error Correction, the transmit serial data stream is 2.666Gbps.                                                                                                                                                                           |

| TXO2P<br>TXO2N                                          | CMLDIFF | 0    | K1<br>L1                                      | Secondary Transmit Serial Data Output Port The secondary transmit serial data port can output the TXO serial data stream or it can output the transmit output clock. See the pin description of TXO2_SEL and TXO2DIS for more details.                                                                                                                                                                                     |

| TXO2_SEL                                                | LVTTL   | I    | N3                                            | Secondary Transmit Select Hardware Mode The TXO2_SEL pin is used to determine the output contents of the secondary transmit serial data output. "Low" = 2.488Gbit/s Serial Output Data "High" = Transmit Output Clock (2.488/2.666 GHz)                                                                                                                                                                                    |

| TXO2DIS                                                 | LVTTL   | I    | N1                                            | Secondary Transmit Disable Hardware Mode The TXO2DIS pin is used to disable the secondary transmit serial data output pins. If the secondary transmit serial data is disabled, both TXO2P/N are pulled "High".  "Low" = TXO2 is enabled "High" = Diabled                                                                                                                                                                   |

| REFCLKP<br>REFCLKN                                      | LVPECL  | I    | P6<br>N6                                      | Reference Clock Input This differential input clock reference is used for the transmit clock multiplier unit (CMU) to provide the necessary high speed clock reference for this device. Pin REFFREQSEL determines the value used as the reference. See Pin REFFREQSEL for more details.                                                                                                                                    |

| VCXO_INP<br>VCXO_INN                                    | LVPECL  | I    | P4<br>N4                                      | Voltage Controled Oscillator Input This differential input clock is used for the transmit PLL jitter attenuation. Pin REFFREQSEL determines the value used as the reference. See Pin REFFREQSEL for more details.                                                                                                                                                                                                          |

**X** EXAR

REV. P1.0.3

## TRANSMITTER SECTION

| NAME                   | LEVEL | Түре | Pin        | DESCRIPTION                                                                                                                                                                                                                                                                 |

|------------------------|-------|------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REFFREQSEL             | LVTTL | I    | P1         | Reference Clock Frequency Select Hardware Mode This pin is used to select the frequency of the REFCLK input to the CMU. "Low" = 77.76MHz (83.5MHz for FEC) "High" = 155.52MHz (167MHz for FEC)                                                                              |

| VCXO_SEL               | LVTTL | I    | M6         | Selects De-Jitter VCXO Option  Hardware Mode This pin selects either the normal REFCLK or the de-jitter VCXO as a reference clock.  "Low" = Normal REFCLK Mode  "High" = De-Jitter VCXO Mode                                                                                |

| VCXO_LOCK              | LVTTL | 0    | N8         | De-Jitter PLL Lock Detect  If the de-jitter PLL lock detect is enabled with Pin P3 and the de-jitter VCXO mode is selected by Pin M6, this pin will pull "High" when the PLL is locked.  "Low" = VCXO out of Lock "High" = VCXO Locked                                      |

| VCXO_LOCKEN            | LVTTL | I    | P3         | De-Jitter PLL Lock Detect Enable Hardware Mode This pin enables the VCXO lock detect Pin N8 to be active. "Low" = VCXO_LOCK disabled "High" = VCXO_LOCK enabled                                                                                                             |

| CPOUT                  | -     | 0    | P8         | Charge Pump Output (for external VCXO) The nominal output of the charge pump is 250μA                                                                                                                                                                                       |

| LOOPBW                 | LVTTL | I    | M7         | CMU Loop Bandwidth Select  Hardware Mode This pin is used to select the bandwidth of the clock multiplier unit of the transmit path to a narrow or wide band.  "Low" = Narrow Band (1x)  "High" = Wide Band (4x)                                                            |

| TXPCLKOP<br>TXPCLKON   | LVDS  | 0    | P10<br>P11 | Transmit Clock Output (622/666 MHz)  This clock can be used for the downstream device to generate the TXDI data and TXCLK. This enables the downstream device and the OC-48 transceiver to be in synchronization.                                                           |

| TXCLKO16P<br>TXCLKO16N | LVDS  | 0    | N10<br>N11 | Auxillary Clock 155.52(166)MHz auxillary clock derived from CMU output. This clock can also be used for the downstream device as a reference for generating the TXDI data and TXCLK. This enables the downstream device and the OC-48 transceiver to be in synchronization. |

| TRITXCLKO16            | LVTTL | I    | M12        | Tri-State Enable Hardware Mode This pin is used to tri-state the auxillary clock. "Low" = TXCLKO16 Enabled "High" = TXCLKO16 Tri-State                                                                                                                                      |

REV. P1.0.3

**PRELIMINARY**

## TRANSMITTER SECTION

| NAME         | LEVEL | Түре | Pin | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                    |

|--------------|-------|------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LOCKDET_CMU  | LVTTL | 0    | N2  | CMU Lock This pin is used to monitor the lock condition of the clock multiplier unit.  "Low" = CMU out of Lock  "High" = CMU Locked                                                                                                                                                                                                                                            |

| OVERFLOW     | LVTTL | 0    | M13 | Transmit FIFO Overflow This pin is used to monitor the transmit FIFO status. "Low" = Normal Status "High" = Overflow Condition                                                                                                                                                                                                                                                 |

| FIFO_RST     | LVTTL | I    | N13 | FIFO Control Reset  Hardware Mode FIFO_RST should be held "High" for 10 cycles of TXCLK during power-up in order to flush out the FIFO. Upon an interrupt indication that the FIFO has an overflow condition, this pin is used to reset or flush out the FIFO.  Note: To automaically reset the FIFO, see Pin FIFO_AUTORST.                                                    |

| FIFO_AUTORST | LVTTL | I    | N12 | Automatic FIFO Reset  Hardware Mode If this pin is set "High", the OC-48 transceiver will automatically flush the FIFO upon an overflow condition.  Upon power-up, the FIFO should be manually reset by pulling FIFO_RST "High" for 10 cycles of TXCLK.  "Low" = Manual FIFO reset required for overflow conditions "High" = Automatically resets FIFO upon overflow detection |

## **RECEIVER SECTION**

| NAME                                                                 | LEVEL | Түре | Pin                                                  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                 |

|----------------------------------------------------------------------|-------|------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RXD0P<br>RXD0N<br>RXD1P<br>RXD1N<br>RXD2P<br>RXD2N<br>RXD3P<br>RXD3N | LVDS  | 0    | E13<br>F13<br>C14<br>D14<br>C13<br>D13<br>A14<br>B14 | Receive Parallel Data Output 622Mbps 4-bit parallel receive output data is updated simultaneously on the rising edge of the RXCLK output. The 4-bit parallel interface is de-multiplexed from the receive serial input data MSB first (RXD3P/N).  Note: The XRT91L81 can output 666Mbps 4-bit parallel receive output data for Forward Error Correction (FEC) Applications. |

| RXCLKP<br>RXCLKN                                                     | LVDS  | 0    | E14<br>F14                                           | Receive Output Clock 622MHz output clock reference for the 4-bit parallel receive output data RXDP/N[3:0].  Note: The XRT91L81 can output a 666MHz receive output clock for Forward Error Correction (FEC).                                                                                                                                                                 |

| TRIRXD                                                               | LVTTL | I    | C12                                                  | Tri-State Receive Parallel Data Output Hardware Mode This pin is used to control the activity of the 4-bit parallel receive output bus and its reference clock.  "Low" = Normal Mode  "High" = Tri-State RXDP/N[3:0] and RXCLK                                                                                                                                              |

# PRELIMINARY RECEIVER SECTION

| NAME                 | LEVEL   | Түре | Pin      | DESCRIPTION                                                                                                                                                                                                               |

|----------------------|---------|------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RXIOP<br>RXION       | CMLDIFF | I    | C1<br>D1 | Primary Receive Serial Data Input The receive serial data stream of 2.488Gbps is applied to the primary input pins if RXSEL is "Low". In Forward Error Correction, the receive serial data stream is 2.666Gbps.           |

| RXI1P<br>RXI1N       | CMLDIFF | I    | G1<br>F1 | Secondary Receive Serial Data Input Port The receive serial data stream of 2.488Gbps is applied to the secondary input pins if RXSEL is "High". In Forward Error Correction, the receive serial data stream is 2.666Gbps. |

| RXSEL                | LVTTL   | ı    | A2       | Receive Serial Data Select Hardware Mode This pin is used to select the Receive Serial Data Input from the primary or secondary inputs.  "Low" = RXI0 "High" = RXI1                                                       |

| REXT                 | -       | I    | A1       | Limiting Amplifier Biasing Resistor This pin should be pulled "Low" with a $499\Omega$ resistor.                                                                                                                          |

| RXCLK16P<br>RXCLK16N | LVDS    | 0    | A6<br>A7 | 155.52 (166) MHz Reference Clock This output clock reference is derived from the recovered clock from the receive path.                                                                                                   |

| LOCKDET_CDR          | LVTTL   | 0    | C7       | CDR Lock Detect This pin will be pulled "High" to indicate that the CDR is locked.                                                                                                                                        |

| LOSEXT               | LVTTL   | I    | B5       | LOS or SD input from optical module                                                                                                                                                                                       |

| POLARITY             | LVTTL   | I    | C4       | Polarity for LOS input Hardware Mode LOSEXT and POLARITY signals will be Exclussive NORed internally to generate the correct polarity.                                                                                    |

| LOSDET               | LVTTL   | 0    | C5       | LOS Detect Flags LOS condition based on LOS/SD signal from optical module.                                                                                                                                                |

| DISRD                | LVTTL   | I    | А3       | Disable Receive Output Data Upon LOS Hardware Mode If this pin is pulled "High", the receive output data will automically pull "Low" when a LOS condition occurs. "Low" = Disabled "High" = Mute Data Upon LOS            |

**PRELIMINARY**

## **POWER AND GROUND**

| NAME       | Түре | Pin                                                                                                                     | DESCRIPTION                                                                                                                                                                                                                                                                     |

|------------|------|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDDD3.3    | PWR  | A8, A13, B13, D9, D10,<br>D11, E11, P13, P14                                                                            | Digital 3.3V Power Supply  VDDD3.3 should be isolated from the analog power supplies. For best results, use a ferrite bead along with an internal power plane separation. The VDDD3.3 power supply pins should have bypass capacitors to the nearest ground.                    |

| AVDD3.3_Rx | PWR  | D3, E3                                                                                                                  | Analog 3.3V Receiver Power Supply  AVDD3.3_Rx should be isolated from the digital power supplies.  For best results, use a ferrite bead along with an internal power plane separation. The AVDD3.3_Rx power supply pins should have bypass capacitors to the nearest ground.    |

| AVDD3.3_Tx | PWR  | J1, M2, P5, P9                                                                                                          | Analog 3.3V Transmitter Power Supply  AVDD3.3_Tx should be isolated from the digital power supplies.  For best results, use a ferrite bead along with an internal power plane separation. The TVDD3.3_Tx power supply pins should have bypass capacitors to the nearest ground. |

| VDD1.8     | PWR  | B7, D12, E12, K11, L9,<br>L10, M9, M10, M11                                                                             | Digital 1.8V Power Supply  VDDD1.8 should be isolated from the analog power supplies. For best results, use a ferrite bead along with an internal power plane separation. The VDDD1.8 power supply pins should have bypass capacitors to the nearest ground.                    |

| AVDD1.8_Rx | PWR  | D4, D5, D6, D8, F3, G3                                                                                                  | Analog 1.8V Receiver Power Supply  AVDD1.8_Rx should be isolated from the digital power supplies.  For best results, use a ferrite bead along with an internal power plane separation. The AVDD1.8_Rx power supply pins should have bypass capacitors to the nearest ground.    |

| AVDD1.8_Tx | PWR  | J4, L6, L7, L8, M3, N9                                                                                                  | Analog 1.8V Transmitter Power Supply  AVDD1.8_Tx should be isolated from the digital power supplies.  For best results, use a ferrite bead along with an internal power plane separation. The AVDD1.8_Tx power supply pins should have bypass capacitors to the nearest ground. |

| DGND       | GND  | A4, A5, A12, B3, B4, B8,<br>B11, B12, F11, F12, G11,<br>G12, G13, G14, H11, H12,<br>J11, J12, K12, L3, L11,<br>L12, P12 | Digital Ground for 3.3V / 1.8V Digital Power Supplies It is recommended that all ground pins of this device be tied together.                                                                                                                                                   |

| AGND_Rx    | GND  | B1, B2, C2, C3, D2, D7,<br>E1, E2, E4, F2, F4, G2, G4,<br>H1, H2, H3, H4                                                | Receiver Analog Ground for 3.3V / 1.8V Analog Power Supplies It is recommended that all ground pins of this device be tied together.                                                                                                                                            |

PRELIMINARY

## **POWER AND GROUND**

| NAME    | Түре | Pin                                                                                                                                                  | DESCRIPTION                                                                                                                             |

|---------|------|------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| AGND_Tx | GND  | J2, J3, K3, K4, L4, L5, M1, M4, M5, N5, N7, P7                                                                                                       | Transmitter Analog Ground for 3.3V / 1.8V Analog Power Supplies It is recommended that all ground pins of this device be tied together. |

| TGND    | GND  | E5, E6, E7, E8, E9, E10, F5, F6, F7, F8, F9, F10, G5, G6, G7, G8, G9, G10, H5, H6, H7, H8, H9, H10, J5, J6, J7, J8, J9, J10, K5, K6, K7, K8, K9, K10 | It is recommended that all ground pins of this device be tied                                                                           |

## **NO CONNECTS**

| NAME | LEVEL | Түре | PIN | DESCRIPTION                                                 |

|------|-------|------|-----|-------------------------------------------------------------|

| NC   |       | NC   | M8  | No Connect This pin can be left floating or tied to ground. |

#### 1.0 FUNCTIONAL DESCRIPTION

The XRT91L81 Transceiver is designed to operate with a SONET Framer/ASIC device and provide a high-speed serial interface to optical networks. The Transceiver converts 4-bit parallel data at 622/666 MHz to a serial CML bit stream at 2.488/2.666Gbps and vice-versa. It implements a clock multiplier unit (CMU), SONET/SDH serialization/de-serialization (SerDes), limiting amplifier and receive clock and data recovery (CDR) unit. The Transceiver is divided into Transmit and Receive sections and is used to provide the front end component of SONET equipment, which includes primarily serial transmit and receive functions.

#### 1.1 Hardware Mode vs. Host Mode

Functionality of the OC-48 Transceiver can be configured by using either Host mode or Hardware mode. If Hardware mode is selected by pulling Host/HW "Low" or leaving this pin unconnected, the functionality is controlled by the hardware pins described in the Hardware Pin Descriptions. However, if Host mode is selected by pulling Host/HW "High", the functionality is controlled by programming internal R/W registers using the Serial Microprocessor interface. Whether using Host or Hardware mode, the functionality remains the same. Therefore, the following sections describe the functionality rather than how each function is controlled. The Hardware Pin Descriptions and the Register Bit Descriptions concentrate on configuring the device.

## 1.2 Input Clock Reference

The XRT91L81 can accept either a 77.76/83.3MHz or 155.52/166MHz input clock at REFCLKP/N as its internal timing reference for generating higher speed clocks. The reference clock can be provided with one of two frequencies chosen by REFCLKSEL. The reference frequency options for the XRT91L81 are listed in Table 2.

TABLE 2: REFERENCE FREQUENCY OPTIONS (NORMALMODE/FEC)

| REFCLKSEL | REFERENCE CLOCK FREQUENCY | OUTPUT CLOCK FREQUENCY | OPERATING MODE |

|-----------|---------------------------|------------------------|----------------|

| 0         | 77.76/83.3 MHz            | 2.488/2.666 GHz        | OC-48/STM-16   |

| 1         | 155.52/166 MHz            | 2.488/2.666 GHz        | OC-48/STM-16   |

## 1.3 Forward Error Correction (FEC)

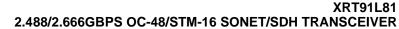

Forward Error Correction is used to control errors along a one-way path of communication. FEC sends extra information along with data which can be used by a receiver to check and correct the data without requesting re-transmission of the original information. It does so by introducing a known structure into a data sequence prior to transmission. The most common methods are to replace a 14-bit data packet with a 15-bit codeword structure, or to replace a 17-bit data packet with an 18-bit codeword structure. To maintain original bandwidth, a higher speed clock reference, derived by the ratio of 15/14 or 18/17 referenced to 77.76MHz or 155.52MHz is applied to the OC-48 transceiver using an external crystal. The XRT91L81 supports FEC by accepting an input clock reference up to 83.3MHz or 166MHz. This allows the Transmit 4-bit Parallel Input Data to be applied to the OC-48 transceiver at 666Mpbs which is converted to a 2.666Gbps serial output stream to an optical module. A simplified block diagram of FEC is shown in Figure 2.

FIGURE 2. SIMPLIFIED BLOCK DIAGRAM OF FORWARD ERROR CORRECTION

#### 2.0 RECEIVE SECTION

The receive section of XRT91L81 includes the differential limiting amplifier inputs RXINP/N, followed by the clock and data recovery unit (CDR) and receive serial-to-parallel converter. The integrated limiting amplifier, designed to be AC coupled at the input, allows the reception of differential signals as low as 10 mV-pp. The receiver accepts the high speed Non-Return to Zero (NRZ) serial data at 2.488/2.666 Gb/s through the differential limiting amplifier input interfaces RXINP/N. The clock and data recovery unit recovers the high-speed receive clock from the incoming scrambled NRZ data stream. The recovered serial data is converted into 4-bit-wide 622.08/666 Mb/s parallel data and presented to the RXD[3:0]P/N LVDS parallel interface. A divide-by-4 version of the high-speed recovered clock RXCLKP/N, is used to synchronize the transfer of the 4-bit RXD[3:0]P/N data with the receive portion of the Upstream device. Upon initialization or loss of signal or loss of lock the 155.52/77.76 MHz (166/83.3 MHz) external reference clock is used to start-up the clock recovery phase-locked loop for proper operation. A special loop-back feature can be configured when RLOOPP is used in conjunction with de-jittered loop-time mode that allows the re-transmitted data to comply with ITU and Bellcore jitter generation specifications.

## 2.1 Receive Serial Input

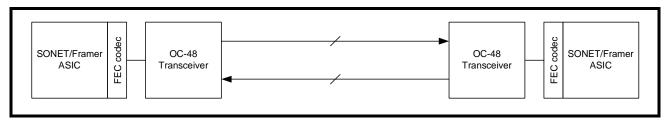

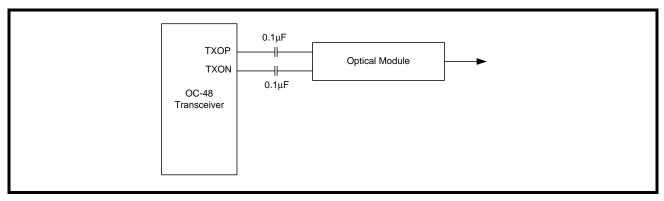

The receive serial inputs can be applied to either the primary or secondary inputs selected by RXSEL. If RXSEL is pulled "Low", the primary channel RXI0P/N is active. If RXSEL is pulled "High", the secondary channel RXI1P/N is active. The receive serial inputs should be AC coupled to an optical module or an electrical interface. A simplified block diagram is shown in Figure 3.

FIGURE 3. RECEIVE SERIAL INPUT INTERFACE BLOCK

**Note:** Some optical modules integrate AC coupled capacitors within the module. If so, the external AC coupled capacitors are not necessary and can be excluded.

#### 2.2 Receive Clock and Data Recovery

The clock and data recovery unit accepts the high speed NRZ serial data from the differential CML receiver and generates a clock that is the same frequency as the incoming data. The clock recovery utilizes the REFCLKP/N to train and monitor its clock recovery PLL. Initially upon startup, the PLL locks to the reference clock. Once this is achieved, the PLL then attempts to lock onto the incoming receive data stream. Whenever the recovered clock frequency deviates from the local reference clock frequency by more than approximately 500 ppm, the clock recovery PLL will switch and lock back onto the local reference clock. When this condition occurs the PLL will declare Loss of Lock and the LOCKDET\_CDR signal will be pulled low. A Loss of Lock condition will also be declared when the external LOSEXT is asserted. Whenever a loss of lock/loss of signal event occurs, the CDR will continue to supply a receive clock (based on the local reference) to the upstream framer device. When the DISRD control is enabled, receive parallel output data will be forced to an all zeroes condition for the entire duration that a LOS condition is detected. This acts as a receive data mute upon LOS function to prevent random noise from being misinterpreted as valid incoming data. When the LOSEXT becomes inactive and the recovered clock is determined to be within 500 ppm accuracy with respect to the local reference source, the lock detect output (LOCKDET CDR) will go active.

#### 2.3 Loss Of Signal

XRT91L81 supports external loss of signal detection (LOS). The external LOS function is supported by the LOSEXT input. The TTL input is coming from the optical module through an output usually called "SD" or "FLAG" which indicates the lack or presence of optical power. Depending on the manufacturer of these devices the polarity of this signal can be either active low or active high. The LOSEXT and POLARITY inputs are Exclusive NORed to generate the external loss control signal with the correct polarity. Whenever an external LOS is detected, the XRT91L81 will automatically output a high level signal on the LOSDET output pin as well as update the control registers whenever the host mode serial microprocessor interface feature is active.

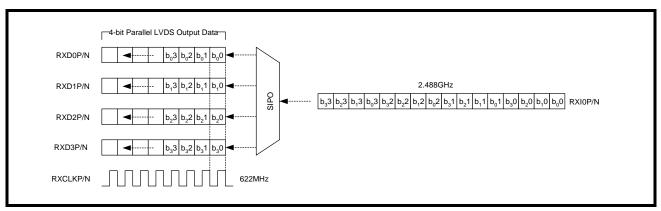

### 2.4 Receive Serial Input to Parallel Output (SIPO)

The SIPO is used to convert the 2.488/2.666GHz serial input data to 622/666MHz parallel output data which can interface to a SONET Framer/ASIC. The SIPO bit de-interleaves the serial input data into a 4-bit parallel output to RXD3P/N. A simplified block diagram is shown in Figure 4.

FIGURE 4. SIMPLIFIED BLOCK DIAGRAM OF SIPO

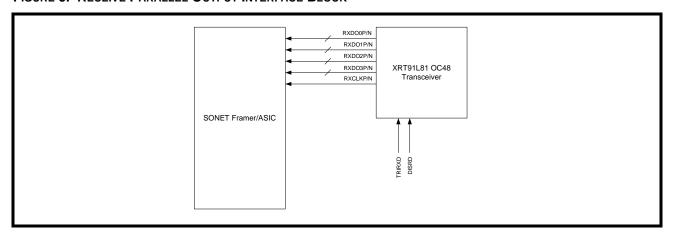

#### 2.5 Receive Parallel Output Interface

The 4-bit LVDS 622/666MHz parallel output data of the receive path is used to interface to a SONET Framer/ASIC synchronized to the recovered clock. A simplified block diagram is shown in Figure X.

#### FIGURE 5. RECEIVE PARALLEL OUTPUT INTERFACE BLOCK

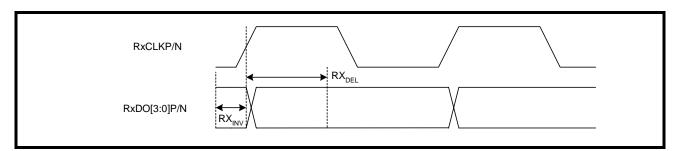

#### 2.6 Receive Parallel Output Data Timing

The receive parallel output data from the OC-48 receiver will adhere to the setup and hold times shown in Figure 6 and Table 3.

FIGURE 6. RECEIVE PARALLEL OUTPUT TIMING

TABLE 3: RECEIVE PARALLEL OUTPUT DATA TIMING SPECIFICATIONS

| Test Condi        | Test Conditions: TA = $25^{\circ}$ C, VDD = $3.3$ V $\pm 5\%$ unless otherwise specified |      |      |      |       |            |  |  |  |  |

|-------------------|------------------------------------------------------------------------------------------|------|------|------|-------|------------|--|--|--|--|

| SYMBOL            | PARAMETER                                                                                | MIN. | Түр. | MAX. | Units | CONDITIONS |  |  |  |  |

| $RX_{INV}$        | RxCLKP/N "High" to data invalid window                                                   |      |      | 200  | pS    |            |  |  |  |  |

| RX <sub>DEL</sub> | RxCLKP/N "High" to data delay                                                            | 45   |      | 55   | %     |            |  |  |  |  |

| RX <sub>DTY</sub> | RxCLKP/N Duty Cycle                                                                      |      | 50   |      | %     |            |  |  |  |  |

#### 2.7 Disable Receive Output Data Upon LOS

The Receiver outputs can automatically be pulled "Low" during a LOS condition to prevent data chattering. By pulling DISRD "High", the Receiver outputs will pull "Low" any time a LOS condition occurs.

#### 2.8 Tri-State Receive Output Data

Unlike DISRD, TRIRXD is used to tri-state the Receiver outputs regardless of the input data stream. By pulling TRIRXD "High", the Receiver outputs will automically tri-state.

#### 3.0 TRANSMIT SECTION

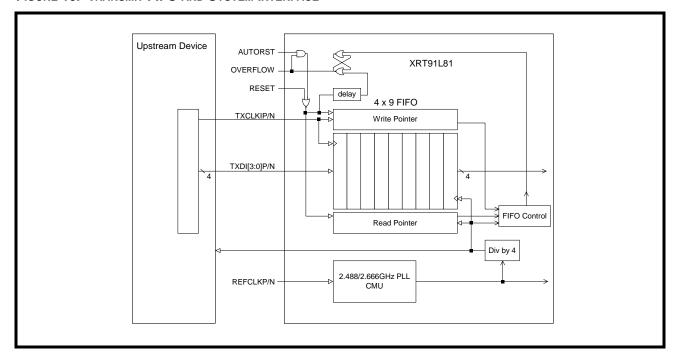

The transmit section of the XRT91L81 accepts 4-bit parallel LVDS data and converts it to serial CML output data intented to interface to an optical module. It consists of a 4-bit parallel LVDS interface, a 4x9 FIFO, Parallel-to-Serial Converter, a clock multiplier unit (CMU), a Current Mode Logic (CML) differential line driver, and Loop Timing modes. The CML serial output data rate is 2.488/2.666Gbps for OC-48 applications. The high frequency serial clock is synthesized by a PLL, which uses a low frequency clock as its input reference. In order to synchronize the data transfer process, the synthesized 2.488/2.666GHz serial output clock is divided by four and the 622/666MHz clock is presented to the upstream device to be used as its timing source.

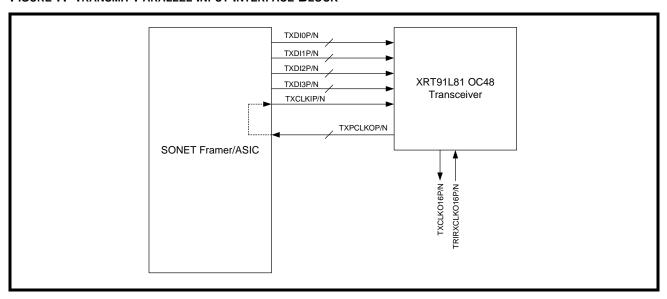

#### 3.1 Transmit Parallel Interface

The parallel data from an upstream device is presented to the XRT91L81 through a 4-bit LVDS parallel bus interface TXDI[3:0]. The data is latched into a parallel input register on the rising edge of TXPCLKIP/N. If the SONET Framer/ASIC is synchronized to the same timing source as the XRT91L81, the transmit input data and clock can directly interface to the OC-48 transceiver. However, if the SONET Framer/ASIC is synchronized to a separate crystal, the XRT91L81 has two output clock references that can be used to synchronize the SONET Framer/ASIC. TXPCLKOP/N is a 622/666MHz LVDS output clock source that is derived from the input clock reference of the transceiver. TXCLKO16P/N is a 155.52/166MHz LVDS auxillary output clock source that is also derived from the input clock reference. Either of these two output clock sources can be used to synchronize the SONET Framer/ASIC to the XRT91L81. If the auxillary clock source is not used, it can be tristated by pulling TRIRXCLKO16 "High". A simplified block diagram of the parallel interface is shown in Figure 7.

FIGURE 7. TRANSMIT PARALLEL INPUT INTERFACE BLOCK

**PRELIMINARY**

#### 3.2 Transmit Parallel Input Data Timing

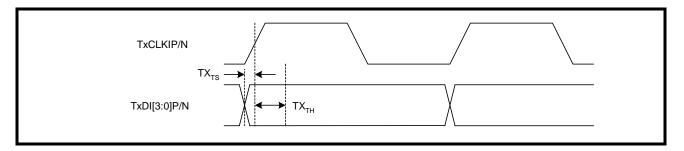

When applying parallel input data to the transmitter, the setup and hold times should be followed as shown in Figure 8 and Table 4.

#### FIGURE 8. TRANSMIT PARALLEL INPUT TIMING

TABLE 4: TRANSMIT PARALLEL INPUT DATA TIMING SPECIFICATIONS

| Test Condi       | Test Conditions: TA = 25°C, VDD = $3.3V \pm 5\%$ unless otherwise specified |      |      |      |       |            |  |  |  |  |

|------------------|-----------------------------------------------------------------------------|------|------|------|-------|------------|--|--|--|--|

| SYMBOL           | PARAMETER                                                                   | MIN. | Түр. | Max. | Units | CONDITIONS |  |  |  |  |

| $TX_{TS}$        | TxCLKIP/N "High" to data setup time                                         | 300  |      |      | pS    |            |  |  |  |  |

| TX <sub>TH</sub> | TxCLKIP/N "High" to data hold time                                          | 300  |      |      | pS    |            |  |  |  |  |

| $TX_{DTY}$       | TxCLKIP/N Duty Cycle                                                        | 40   |      | 60   | %     |            |  |  |  |  |

#### 3.3 Transmit FIFO

The Parallel Interface also includes a 4x9 FIFO that can be used to eliminate difficult timing issues between the input transmit clock and the clock derived from the CMU. The use of the FIFO permits the system to tolerate an arbitrary amount of delay and jitter between TXCLKOP/N and TXCLKIP/N. The FIFO can be initialized when FIFO\_RESET is asserted and held low for 10 cycles of the TXCLKO clock. Once the FIFO is centered, the delay between TXCLKO and TXCLKI can decrease or increase up to two periods of the low-speed clock (TXCLKO). Should the delay exceed this amount, the read and write pointers will point to the same word in the FIFO resulting in a loss of transmitted data (FIFO overflow). In the event of a FIFO overflow the FIFO control logic will initiate an OVERFLOW signal that can be used by an external controller to issue a RESET signal. The chip under the control of the FIFO\_AUTORST pin can automatically recover from an overflow condition. When the FIFO\_AUTORST input is set to a "High" level, once an overflow condition is detected, the chip will set the OVERFLOW pin to a high level and will automatically reset and center the FIFO. For the transparent mode of operation (no FIFO), the RESET should be held at a constant "High" state.

#### 3.4 FIFO Calibration Upon Power Up

It is required that the FIFO\_RST pin be pulled "High" for 10 TXCLK cycles to flush out the FIFO after the device is powered on. If the FIFO experiences an Overflow condition, FIFO\_RST can be used to manually reset the FIFO. However, the OC-48 transceiver has an automatic reset pin that will allow the FIFO to automatically reset upon an Overflow condition. FIFO\_AUTORST should be pulled "High" to enable the automatic FIFO reset function.

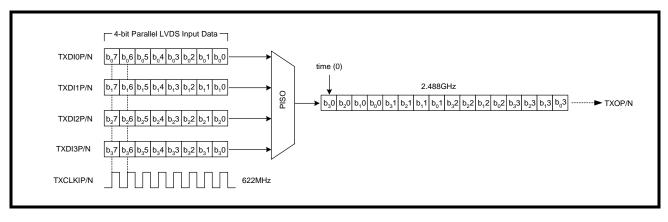

#### 3.5 Transmit Parallel Input to Serial Output (PISO)

The PISO is used to convert 622/666MHz parallel input data to 2.488/2.666GHz serial output data which can interface to an optical module. The PISO bit interleaves parallel input data into a serial bit stream taking the first bit from TXDI3P/N, then the first bit from TXDI2P/N, and so on as shown in Figure 9.

FIGURE 9. SIMPLIFIED BLOCK DIAGRAM OF PISO

## 3.6 Clock Multiplier Unit (CMU) and Re-Timer

The high-speed serial clock synthesized by the CMU is divided by 4, and the TXPCLKOP/N clock is presented to an upstream device. The upstream device should use TXPCLKOP/N as its timing source. The Upstream device then generates the TXCLKIP/N clock that is phase aligned with the transmit data and provides it to the parallel interface of the transmitter. The data must meet setup and hold times with respect to TXCLKIP/N. The XRT91L81 will latch TXDI[3:0]P/N on the falling edge of TXCLKIP/N. The clock synthesizer uses a PLL to lock to the differential input reference clock. It can also be driven by an optional external VCXO for loop timed or local reference de-jitter applications. As an example the REFCLKP/N input can accept a clock from a LVPECL crystal oscillator that has a frequency accuracy better than 20ppm in order for the TXCLKOP/N frequency to have the accuracy required for SONET systems. The other input, VCXO\_INP/N can be connected to the output of a VCXO that can be configured to clean up the recovered received clock in loop timing mode before being applied to the input of the transmit CMU as a reference clock. In addition, the internal phase/frequency detector and charge pump, combined with an external VCXO can alternately be used as a jitter attenuator to de-jitter a noisy system reference clock prior to it being used to time the CMU. Figure 10 provides a detailed overview of the transmit FIFO in a system interface.

FIGURE 10. TRANSMIT FIFO AND SYSTEM INTERFACE

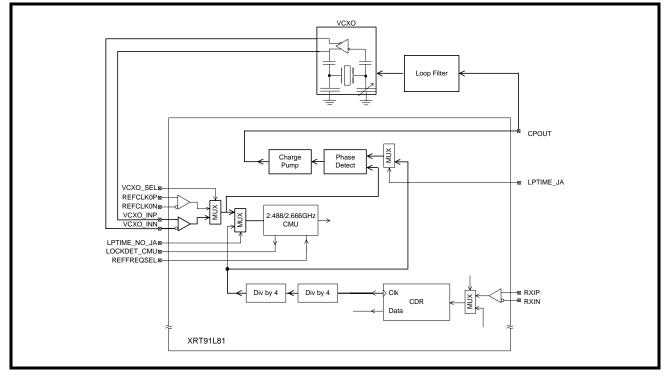

#### 3.7 Loop Timing and clock control

Two types of loop timing are possible in the XRT91L81. In the regular loop timing mode (without an external VCXO), the loop timing is controlled by the LPTIME\_NO\_JA pin. This mode is selected by asserting the LPTIME\_NO\_JA signal to a high level. When the loop timing mode is activated the external reference clock to the input of the CMU is replaced with the 1/16th or the 1/32nd of the high-speed recovered receive clock from the CDR. Under this condition both the transmit and receive sections are synchronized to the recovered receive clock. The normal looptime mode directly locks the CMU to the recovered receive clock with no external de-jittering.

In cases when the jitter of the recovered receive clock does not satisfy the strict ITU and Bellcore jitter generation requirements, an external VCXO-based PLL can be used to clean up the jitter of the recovered receive clock. In this case the VCXO\_SEL pin should be set high. By doing so, the CMU receives its reference clock signal from an external VCXO connected to the VCXO\_INP/N inputs. The LPTIME\_JA pin must also be set high in order to select the recovered receive clock as the reference source for the de-jitter PLL. In this state, the VCXO will be phase locked to the recovered receive clock through a narrowband loop filter. The use of the on-chip phase/frequency detector with charge pump and an external VCXO to remove the transmit jitter due to jitter in the recovered clock is shown in Figure 10. The on-chip phase/frequency detector can also be used to remove the jitter from a noisy reference signal that is applied to the REFCLKP/N inputs. In this case the LPTIME\_NO\_JA pin should be set "Low", the VCXO\_SEL set "High", and the LPTIME\_JA pin set "Low". In this configuration, the REFCLKP/N signal is used as the reference to the de-jitter PLL and the de-jittered output of the phase locked VCXO is used as the timing reference to the CMU. Table 5 provides configuration for selecting the loop timing and reference de-jitter modes.

TABLE 5: LOOP TIMING AND REFERENCE DE-JITTER CONFIGURATIONS

| VCXO_SEL | LPTIME_JA | LPTIME_NO_JA | Action                        |

|----------|-----------|--------------|-------------------------------|

| 0        | 0         | 0            | Normal mode                   |

| 0        | 0         | 1            | Loop timing without de-jitter |

| 1        | 0         | 0            | Reference de-jitter           |

| 1        | 1         | 0            | Loop timing with de-jitter    |

FIGURE 11. LOOP TIMING MODE USING AN EXTERNAL CLEANUP VCXO

#### 3.8 External Loop Filter

As shown in Figure 11, there is an internal charge pump used to drive an external loop filter and external VCXO. The charge pump current is fixed at 250uA. Figure 12 is a simplified block diagram of the external loop filter and recommended values.

FIGURE 12. SIMPLIFIED DIAGRAM OF THE EXTERNAL LOOP FILTER

#### 3.9 Transmit Serial Output Control

The 2.488/2.666GHz transmit serial output has a primary and secondary channel. By default, the serial output stream is multiplexed to both channels. However, the secondary channel can be configured to output the 2.488/2.666GHz serial data stream or the transmit serial clock according to the state of TXO2\_SEL. If TXO2\_SEL is pulled "Low", the secondary channel will output the serial data stream. If TXO2\_SEL is pulled "High", the secondary channel will output the transmit serial clock. In addition, the secondary channel can be disabled by pulling TXO2\_DIS "High". If the secondary channel is disabled, the secondary serial output data will be pulled "High". The transmit serial output should be AC coupled to an optical module or electrical interface. A simplified block diagram is shown in Figure 13.

FIGURE 13. TRANSMIT SERIAL OUTPUT INTERFACE

**Note:** Some optical modules integrate AC coupled capacitors within the module. If so, the external AC coupled capacitors are not necessary and can be excluded.

## **PRELIMINARY**

#### 4.0 DIAGNOSTIC FEATURES

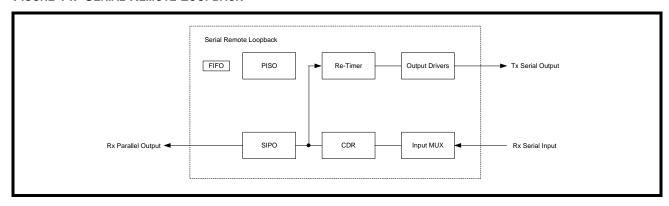

## 4.1 Serial Remote Loopback

The serial remote loopback function is activated by setting RLOOPS "High". When serial remote loopback is activated, the high-speed serial receive data from RXIN is presented at the high speed transmit output TXOP/N, and the high-speed recovered clock is selected and presented to the high-speed transmit clock output TXCLKP/N. During serial remote loopback, the high-speed receive data (RXIN) is also converted to parallel data and presented at the low-speed receive parallel interface RXD[3:0]P/N. The recovered receive clock is also divided by 4 and presented at the low-speed clock output RXCLKP/N to synchronize the transfer of the 4-bit received parallel data. A simplified block diagram of serial remote loopback is shown in Figure 14.

FIGURE 14. SERIAL REMOTE LOOPBACK

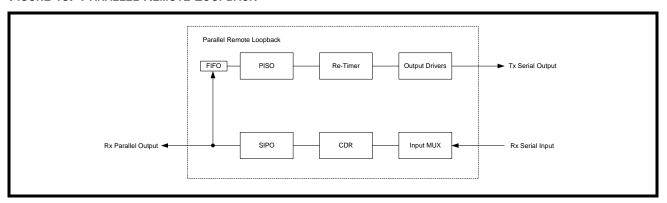

#### 4.2 Parallel Remote Loopback

RLOOPP controls a more comprehensive version of remote loop-back that can also be used in conjunction with the de-jitter PLL that is phase locked to the recovered receive clock. In this mode, the received signal traverses the limiting amplifier, is processed by the CDR, and is sent through the serial to parallel converter. At this point, the 4-bit parallel data and clock are looped back to the transmit FIFO. Concurrently, if receive clock jitter attenuation is also employed, the received clock is divided down in frequency and presented to the input of the integrated phase/frequency detector and is compared to the frequency of a VCXO that is connected to the VCXO\_INP/N inputs. With the LOOPTIME configured to use the recovered receive clock as the reference and VCXO\_SEL asserted, the VCXO is phase locked to the recovered receive clock. The de-jittered clock is then used to retime the transmitter, resulting in the re-transmission of the de-jittered received data out of TXOP/N. A simplified block diagram of parallel remote loopback is shown in Figure 15.

FIGURE 15. PARALLEL REMOTE LOOPBACK

#### 4.3 Digital Local Loopback

The digital local loopback is activated when the DLOOP signal is set high. When digital local loopback is activated, the high-speed data from the output of the parallel to serial converter is looped back and presented to the high-speed input of the receiver serial to parallel converter. The CMU output is also looped back to the receive section and is used to synchronize the transfer of the data through the receiver. In Digital loopback mode the transmit data from the transmit parallel interface TXDI[3:0]P/N is serialized and presented to the high-speed transmit output TXOP/N along with the high-speed transmit clock which is generated from the clock multiplier unit and presented to the TXO2P/N pins. A simplified block diagram of digital loopback is shown in Figure 16.

FIGURE 16. DIGITAL LOOPBACK

# **PRELIMINARY**

#### 4.4 SONET Jitter Requirements

SONET equipment jitter requirements are specified for the following three types of jitter. The definitions of each of these types of jitter are given below. SONET equipment jitter requirements are specified for the following three types of jitter.

#### 4.4.1 Jitter Tolerance:

Jitter tolerance is defined as the peak-to-peak amplitude of sinusoidal jitter applied on the input OC-N equipment interface that causes an equivalent 1dB optical power penalty. OC-1/STS-1, OC-3/STS-3, OC-12 and OC-48 category II SONET interfaces should tolerate, the input jitter applied according to the mask of Figure 17, with the corresponding parameters specified in the figure.

FIGURE 17. JITTER TOLERANCE MASK

#### 4.4.2 Jitter Transfer

Jitter transfer is defined as the ratio of the jitter on the output of OC-N to the jitter applied on the input of OC-N versus frequency. Jitter transfer is important in applications where the system is utilized in the loop-timed mode, where the recovered clock is used as the source of the transmit clock.

#### 4.4.3 Jitter Generation

Jitter generation is defined as the amount of jitter at the OC-N output in the absence of applied input jitter. The Bellcore and ITU requirement for this type jitter is 0.01UI rms measured with a specific band-pass filter.

For more information on these specifications refer to Bellcore TR-NWT-000253 sections 5.6.2-5 and GR-253-CORE section 5.6.

# 5.0 SERIAL MICROPROCESSOR INTERFACE BLOCK

The serial microprocessor uses a standard 3-pin serial port with  $\overline{\text{CS}}$ , SCLK, and SDI for programming the transceiver. Optional pins such as SDO, INT, and RESET allow the ability to read back contents of the registers, monitor the transceiver via an interrupt pin, and reset the transceiver to its default configuration by pulling reset "Low" for more than 10mS. A simplified block diagram of the Serial Microprocessor is shown in Figure 18.

FIGURE 18. SIMPLIFIED BLOCK DIAGRAM OF THE SERIAL MICROPROCESSOR INTERFACE

#### 5.1 SERIAL TIMING INFORMATION

The serial port requires 16 bits of data applied to the SDI (Serial Data Input) pin. The Serial Microprocessor samples SDI on the rising edge of SCLK (Serial Clock Input). The data is not latched into the device until all 16 bits of serial data have been sampled. A timing diagram of the Serial Microprocessor is shown in Figure 19.

FIGURE 19. TIMING DIAGRAM FOR THE SERIAL MICROPROCESSOR INTERFACE

#### 5.2 16-BIT SERIAL DATA INPUT DESCRITPTION

The serial data input is sampled on the rising edge of SCLK. In readback mode, the serial data output is updated on the falling edge of SCLK. The serial data must be applied to the transceiver LSB first. The 16 bits of serial data are described below.

#### 5.2.1 R/W (SCLK1)

The first serial bit applied to the transceiver informs the microprocessor that a Read or Write operation is desired. If the R/W bit is set to "0", the microprocessor is configured for a Write operation. If the R/W bit is set to "1", the microprocessor is configured for a Read operation.

#### 5.2.2 A[5:0] (SCLK2 - SCLK7)

The next 6 SCLK cycles are used to provide the address to which a Read or Write operation will occur. A0 (LSB) must be sent to the transceiver first followed by A1 and so forth until all 6 address bits have been sampled by SCLK.

## 5.2.3 X (Dummy Bit SCLK8)

The dummy bit sampled by SCLK8 is used to allow sufficient time for the serial data output pin to update data if the readback mode is selected by setting R/W = "1". Therefore, the state of this bit is ignored and can hold either "0" or "1" during both Read and Write operations.

## 5.2.4 D[7:0] (SCLK9 - SCLK16)

The next 8 SCLK cycles are used to provide the data to be written into the internal register chosen by the address bits. D0 (LSB) must be sent to the transceiver first followed by D1 and so forth until all 8 data bits have been sampled by SCLK. Once 16 SCLK cycles have been complete, the transceiver holds the data until  $\overline{\text{CS}}$  is pulled "High" whereby, the serial microprocessor latches the data into the selected internal register.

#### 5.3 8-BIT SERIAL DATA OUTPUT DESCRIPTION

The serial data output is updated on the falling edge of SCLK9 - SCLK16 if R/W is set to "1". D0 (LSB) is provided on SCLK9 to the SDO pin first followed by D1 and so forth until all 8 data bits have been updated. The SDO pin allows the user to read the contents stored in individual registers by providing the desired address on the SDI pin during the Read cycle.

## 6.0 REGISTER MAP AND BIT DESCRIPTIONS

TABLE 6: MICROPROCESSOR REGISTER MAP

| REG  | ADDR                                       | Түре | D7                                | D6                              | D5       | D4         | D3       | D2          | D1      | D0       |

|------|--------------------------------------------|------|-----------------------------------|---------------------------------|----------|------------|----------|-------------|---------|----------|

| Chan | Channel 0 Control Register (0x00h - 0x05h) |      |                                   |                                 |          |            |          |             |         |          |

| 0    | 0x00                                       | R/W  | Reserved                          | Reserved                        | Reserved | VCXOIE     | LOSIE    | CDRIE       | CMUIE   | FIFOIE   |

| 1    | 0x01                                       | RUR  | Reserved                          | Reserved                        | Reserved | VCXOIS     | LOSIS    | CDRIS       | CMUIS   | FIFOIS   |

| 2    | 0x02                                       | RO   | Reserved                          | Reserved                        | Reserved | VCXOID     | LOSID    | CDRID       | CMUID   | FIFOID   |

| 3    | 0x03                                       | R/W  | TXO2DIS                           | REFREQSEL                       | TXO2SEL  | LOOPBW     | VCXOSEL  | TRITXCLK016 | AUTORST | FIFORST  |

| 4    | 0x04                                       | R/W  | Reserved                          | POLARITY                        | LOOPTM   | LPTIMJADIS | DISRD    | TRIRXD      | RXSEL   | VCXOLKEN |

| 5    | 0x05                                       | R/W  | Reserved                          | Reserved                        | Reserved | Reserved   | Reserved | DLOOP       | RLOOPS  | RLOOPP   |

| 0x0  | 6 - 0x3D                                   | R/W  | Reserved                          | Reserved                        |          |            |          |             |         |          |

| 62   | 0x3E                                       | RO   | Device ID (                       | Device ID (See Bit Description) |          |            |          |             |         |          |