#### **Features and Benefits**

- Two-wire output enables reduced wiring costs in long wire systems

- Simultaneous programming of PWM carrier frequency, quiescent duty cycle (QDC), and sensitivity for system optimization

- Fully differential signal path increases EMC immunity and reduces output offset drifts

- Factory programmed sensitivity temperature coefficient and quiescent duty cycle drift

- Programmability at end-of-line

- Pulse width modulated (PWM) current output provides increased noise and EMC immunity compared to an analog output

- Precise recoverability after temperature cycling

- Duty cycle clamps provide short circuit diagnostic capabilities

- Optional 50% duty cycle calibration test mode at device power up

- Wide ambient temperature range: -40°C to 150°C

- Resistant to mechanical stress

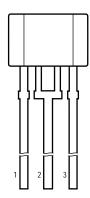

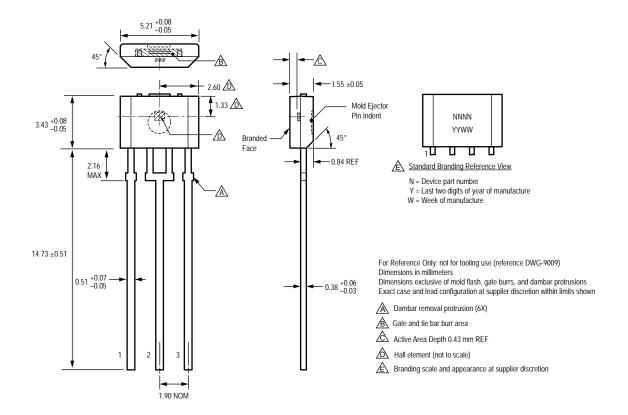

# Package: 3-pin SIP (suffix KB)

Not to scale

## **Description**

The A1357 device is a high precision, programmable two-wire Hall-effect linear sensor IC with a pulse width modulated (PWM) current. The A1357 device converts an analog signal from its internal Hall sensor element to a digitally encoded PWM signal. The coupled noise immunity of the digitally encoded PWM is far superior to the noise immunity of an analog output signal.

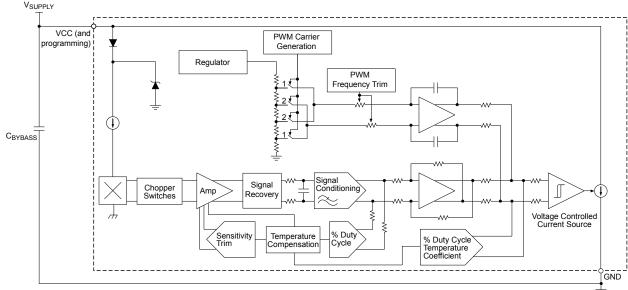

The BiCMOS, monolithic circuit inside of the A1357 integrates a Hall element, precision temperature-compensating circuitry to reduce the intrinsic sensitivity and offset drift of the Hall element, a small-signal high-gain amplifier, proprietary dynamic offset cancellation circuits, and PWM conversion circuitry. The dynamic offset cancellation circuits reduce the residual offset voltage of the Hall element that is normally caused by device overmolding, temperature dependencies, and thermal stress. The high frequency offset cancellation (chopping) clock allows for a greater sampling rate, which increases the accuracy of the output current signal and results in faster signal processing capability.

The A1357 sensor is provided in a lead (Pb) free 3-pin single inline package (KB suffix), with 100% matte tin leadframe plating.

# **Functional Block Diagram**

#### **Selection Guide**

| Part Number  | Packing*                    |

|--------------|-----------------------------|

| A1357LKB-T   | 500 pieces per bag          |

| A1357LKBTN-T | 4000 pieces per 13-in. reel |

<sup>\*</sup>Contact Allegro® for additional packing options

#### **Absolute Maximum Ratings**

| Characteristic                | Symbol               | Notes                 | Rating     | Unit |

|-------------------------------|----------------------|-----------------------|------------|------|

| Forward Supply Voltage        | V <sub>CC</sub>      |                       | 28         | V    |

| Reverse Supply Voltage        | V <sub>RCC</sub>     |                       | -18        | V    |

| Forward Supply Current        | I <sub>CC</sub>      |                       | 50         | mA   |

| Reverse Supply Current        | I <sub>RCC</sub>     |                       | -50        | mA   |

| Operating Ambient Temperature | T <sub>A</sub>       | L temperature range   | -40 to 150 | °C   |

| Maximum Junction Temperature  | T <sub>J</sub> (max) |                       | 165        | °C   |

| Storage Temperature           | T <sub>stg</sub>     | V <sub>CC</sub> = 0 V | -65 to 170 | °C   |

## **Pin-out Diagram**

## **Terminal List Table**

| Number | Name | Function                                                                                 |

|--------|------|------------------------------------------------------------------------------------------|

| 1      | VCC  | Input power supply; use bypass capacitor to connect to ground; also used for programming |

| 2      | GND  | Ground                                                                                   |

| 3      | NC   | No connect                                                                               |

# Two-Wire High Precision Linear Hall-Effect Sensor IC With Pulse Width Modulated Output Current

**OPERATING CHARACTERISTICS** Valid over full operating temperature range,  $T_A$ ,  $V_{CC}$  = 4.5 to 18 V,  $C_{BYPASS}$  = 0.1  $\mu$ F, unless otherwise noted

| Characteristics                                                      | Symbol                 | Test Conditions                                                                                                              | Min.  | Тур.                        | Max.   | Unit <sup>1</sup> |  |

|----------------------------------------------------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------|-------|-----------------------------|--------|-------------------|--|

| Electrical Characteristics                                           |                        |                                                                                                                              |       |                             |        |                   |  |

| Supply Voltage <sup>2</sup>                                          | V <sub>CC</sub>        |                                                                                                                              | 4.5   | _                           | 18     | V                 |  |

| Supply Current                                                       | I <sub>CC_LOW</sub>    |                                                                                                                              | _     | 6                           | 8      | mA                |  |

| Supply Current                                                       | I <sub>CC_HIGH</sub>   |                                                                                                                              | 12    | _                           | 16.5   | mA                |  |

| Supply Current Ratio                                                 |                        |                                                                                                                              | 2     | _                           | -      | -                 |  |

| Supply Zener Clamp Voltage                                           | V <sub>Zsupply</sub>   | I <sub>CC</sub> = 18 mA, T <sub>A</sub> = 25°C                                                                               | 28    | _                           | -      | V                 |  |

| Power-On Time <sup>3,4</sup>                                         | t <sub>PO</sub>        | f <sub>pwm</sub> = 1 kHz                                                                                                     | _     | _                           | 5      | ms                |  |

| Internal Bandwidth                                                   | BWi                    | Small signal $-3$ dB, 100 G <sub>(P-P)</sub> magnetic input signal, $T_A = 25 \text{ C}^{\circ}$                             | _     | 400                         | _      | Hz                |  |

| Chopping Frequency <sup>5</sup>                                      | f <sub>C</sub>         | T <sub>A</sub> = 25°C                                                                                                        | _     | 200                         | -      | kHz               |  |

| Output Current Characteristics                                       |                        |                                                                                                                              |       |                             |        |                   |  |

| PWM <sub>OUT</sub> Rise Time <sup>3,4</sup>                          | t <sub>r</sub>         | VCC pin, No C <sub>BYPASS</sub> or R <sub>SENSE</sub> , T <sub>A</sub> = 25 C°                                               | _     | 6.5                         | _      | mA/µs             |  |

| PWM <sub>OUT</sub> Fall Time <sup>3,4</sup>                          | t <sub>f</sub>         | VCC pin, No C <sub>BYPASS</sub> or R <sub>SENSE</sub> , T <sub>A</sub> = 25 C°                                               | _     | 6.5                         | _      | mA/µs             |  |

| Maximum Propagation Delay <sup>3,4</sup>                             | t <sub>PROP</sub>      | T <sub>A</sub> = 25 C°                                                                                                       | _     | 2                           | 3      | ms                |  |

| Response Time <sup>3,4</sup>                                         | t <sub>RESPONSE</sub>  | Impulse magnetic field of 300 G, $f_{pwm}$ = 1 kHz, slew rate < 120 G/ms, $T_A$ = 25 $C^{\circ}$                             | _     | 2                           | 3.125  | ms                |  |

| Duty Cycle Jitter <sup>3,4,6</sup>                                   | Jitter <sub>PWM</sub>  | Measured over 1000 output PWM clock periods, 3 sigma values, Sens = $60 \text{ m}\% / \text{G}$ , $T_A = 25 \text{ C}^\circ$ | _     | -                           | ±0.090 | % D               |  |

| Claren Duty Cycle                                                    | D <sub>CLP(HIGH)</sub> |                                                                                                                              | 90    | _                           | 95     | % D               |  |

| Clamp Duty Cycle                                                     | D <sub>CLP(LOW)</sub>  |                                                                                                                              | 5     | _                           | 10     | % D               |  |

| Pre-Programming Target <sup>7</sup>                                  |                        |                                                                                                                              |       |                             |        |                   |  |

| Pre-Programming Quiescent Current Duty Cycle                         | D <sub>(Q)PRE</sub>    | B = 0 G, T <sub>A</sub> = 25°C                                                                                               | _     | 50                          | -      | % D               |  |

| Pre-Programming Sensitivity                                          | Sens <sub>PRE</sub>    | T <sub>A</sub> = 25°C                                                                                                        | -     | 25                          | -      | (m% D)/G          |  |

| Pre-Programming PWM <sub>OUT</sub> Carrier Frequency                 | f <sub>PWMPRE</sub>    | T <sub>A</sub> = 25°C                                                                                                        | _     | 1.5                         | -      | kHz               |  |

| Quiescent Current Duty Cycle Progran                                 | nming                  |                                                                                                                              |       |                             |        |                   |  |

| Initial Quiescent Current Duty Cycle                                 | D <sub>(Q)init</sub>   | B = 0 G, T <sub>A</sub> = 25°C                                                                                               | _     | D <sub>(Q)PRE</sub>         | _      | % D               |  |

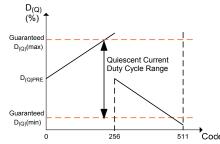

| Guaranteed Quiescent Current Duty<br>Cycle Output Range <sup>8</sup> | D <sub>(Q)</sub>       | B = 0 G, T <sub>A</sub> = 25°C                                                                                               | 40    | _                           | 60     | % D               |  |

| Quiescent Current Duty Cycle<br>Programming Bits                     |                        |                                                                                                                              | _     | 9                           | _      | bit               |  |

| Average Quiescent Current Duty Cycle<br>Step Size <sup>9,10</sup>    | Step <sub>D(Q)</sub>   | T <sub>A</sub> = 25°C                                                                                                        | 0.091 | 0.103                       | 0.115  | % D               |  |

| Quiescent Current Duty Cycle<br>Programming Resolution <sup>11</sup> | Err <sub>PGD(Q)</sub>  | T <sub>A</sub> = 25°C                                                                                                        | _     | Step <sub>D(Q)</sub> × ±0.5 | _      | % D               |  |

Continued on the next page...

3

# Two-Wire High Precision Linear Hall-Effect Sensor IC With Pulse Width Modulated Output Current

## **OPERATING CHARACTERISTICS (continued)** Valid over full operating temperature range, $T_A$ , $V_{CC}$ = 4.5 to 18 V,

$C_{BYPASS}$  = 0.1  $\mu$ F, unless otherwise noted

| Characteristics                                             | Symbol                        | Test Conditions                                   | Min. | Тур.                         | Max. | Unit     |

|-------------------------------------------------------------|-------------------------------|---------------------------------------------------|------|------------------------------|------|----------|

| Sensitivity Programming                                     | •                             |                                                   |      |                              |      | •        |

| Initial Sensitivity                                         | Sens <sub>init</sub>          | T <sub>A</sub> = 25°C                             | _    | Sens <sub>PRE</sub>          | _    | (% D)/G  |

| Sensitivity Programming Bits                                | Range_<br>Selection           | T <sub>A</sub> = 25°C                             | _    | 1                            | -    | bit      |

|                                                             | Fine                          | T <sub>A</sub> = 25°C                             | _    | 8                            | _    | bit      |

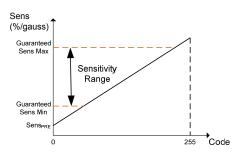

| Guaranteed Sensitivity Range                                | Sens <sub>Range1</sub>        | T <sub>A</sub> = 25°C                             | 35   | _                            | 70   | (m% D)/G |

| Guaranteeu Sensitivity Range                                | Sens <sub>Range2</sub>        | T <sub>A</sub> = 25°C                             | 70   | _                            | 145  | (m% D)/G |

| Average Sensitivity Step Size <sup>9,10</sup>               | Step <sub>SENS1</sub>         | T <sub>A</sub> = 25°C                             | 215  | 300                          | 375  | (μ% D)/G |

| Average Sensitivity Step Size                               | Step <sub>SENS2</sub>         | T <sub>A</sub> = 25°C                             | 430  | 600                          | 750  | (μ% D)/G |

| Sensitivity Programming Resolution <sup>11</sup>            | Err <sub>PGSENS</sub>         | T <sub>A</sub> = 25°C                             | _    | Step <sub>SENS</sub> × ±0. 5 | _    | (μ% D)/G |

| Carrier Frequency Programming                               |                               |                                                   |      |                              |      |          |

| Initial Carrier Frequency                                   | f <sub>PWMinit</sub>          | T <sub>A</sub> = 25°C                             | _    | f <sub>PWMPRE</sub>          | _    | Hz       |

| Carrier Frequency Programming Range                         | f <sub>PWM</sub>              | T <sub>A</sub> = 25°C                             | 0.9  | 1                            | 1.1  | kHz      |

| Carrier Frequency Programming Bits                          |                               |                                                   | _    | 4                            | _    | bit      |

| Average Carrier Frequency Step Size <sup>9,10</sup>         | Step <sub>fPWM</sub>          | T <sub>A</sub> = 25°C                             | 38   | 54                           | 70   | Hz       |

| Carrier Frequency Programming Resolution <sup>11</sup>      | Err <sub>PGfPWM</sub>         | T <sub>A</sub> = 25°C                             | _    | Step <sub>fPWM</sub> × ±0. 5 | _    | Hz       |

| Calibration Test Mode                                       |                               |                                                   |      |                              |      |          |

| Calibration Test Mode Selection Bit                         |                               |                                                   | _    | 1                            | _    | bit      |

| Calibration Test Mode Duration <sup>4</sup>                 | t <sub>CAL</sub>              | f <sub>PWM</sub> = 1 kHz                          | 45   | 50                           | 55   | ms       |

| Output Duty Cycle During Calibration Mode <sup>4</sup>      | D <sub>CAL</sub>              |                                                   | 49   | 50                           | 51   | % D      |

| Lock Bit Programming                                        |                               |                                                   |      |                              |      |          |

| Overall Programming Lock Bit                                | LOCK                          |                                                   | _    | 1                            | _    | bit      |

| Factory Programmed Sensitivity Temperature                  | erature Coe                   | fficient And Drift Characteristics                |      |                              |      |          |

| Sensitivity Temperature Coefficient <sup>12</sup>           | Sens <sub>TC</sub> _<br>NdFeB | T <sub>A</sub> = 150°C                            | _    | 0.11                         | _    | %/°C     |

| Sensitivity Drift Through Temperature Range <sup>13</sup>   | $\Delta Sens_TC$              | T <sub>A</sub> = 150°C                            | _    | < ±3                         | _    | %        |

| Sensitivity Drift Due to Package<br>Hysteresis <sup>3</sup> | ∆Sens <sub>PKG</sub>          | T <sub>A</sub> = 150°C, after temperature cycling | _    | < ±1                         | -    | %        |

$Continued\ on\ the\ next\ page\dots$

# Two-Wire High Precision Linear Hall-Effect Sensor IC With Pulse Width Modulated Output Current

## **OPERATING CHARACTERISTICS (continued)** Valid over full operating temperature range, $T_A$ , $V_{CC}$ = 4.5 to 18 V,

$C_{BYPASS} = 0.1 \mu F$ , unless otherwise noted

| Characteristics                                                               | Symbol                                                | Test Conditions                                     | Min. | Тур.    | Max. | Unit     |  |  |

|-------------------------------------------------------------------------------|-------------------------------------------------------|-----------------------------------------------------|------|---------|------|----------|--|--|

| Factory Programmed Quiescent Curre                                            | Factory Programmed Quiescent Current Duty Cycle Drift |                                                     |      |         |      |          |  |  |

| Quiescent Current Duty Cycle<br>Temperature Coefficient <sup>12</sup>         | D <sub>TC(Q)</sub>                                    | T <sub>A</sub> = 150°C                              | -    | 0       | -    | (% D)/°C |  |  |

| Quiescent Current Duty Cycle Drift<br>Through Temperature Range <sup>14</sup> | $\Delta D_{(Q)}$                                      | Sens = Sens <sub>PRE</sub> , T <sub>A</sub> = 150°C | _    | < ±0.35 | _    | % D      |  |  |

| Error Components                                                              | Error Components                                      |                                                     |      |         |      |          |  |  |

| Linearity Sensitivity Error                                                   | Lin <sub>ERR</sub>                                    |                                                     | _    | < ±1.5  | -    | %        |  |  |

| Symmetry Sensitivity Error                                                    | Sym <sub>ERR</sub>                                    |                                                     | _    | < ±1.5  | -    | %        |  |  |

<sup>&</sup>lt;sup>1</sup>1 G (gauss) = 0.1 mT (millitesla).

5

<sup>&</sup>lt;sup>2</sup>Supply Voltage is the voltage drop between device supply and ground pins. It does not include a drop through a sense resistor.

<sup>&</sup>lt;sup>3</sup>See Characteristic Definitions section.

<sup>&</sup>lt;sup>4</sup>Guarenteed by design only. Characterized but not tested in production.

$<sup>^{5}</sup>f_{C}$  varies up to approximately  $\pm 20\%$  through the full operating ambient temperature range,  $T_{A}$ , and process.

<sup>&</sup>lt;sup>6</sup>Jitter is dependent on the sensitivity of the device.

<sup>&</sup>lt;sup>7</sup>Raw device characteristic values before any programming.

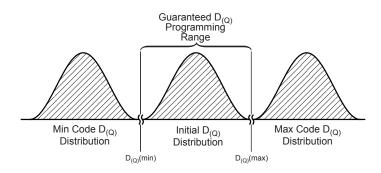

$<sup>^{8}</sup>D_{(Q)}(max)$  is the value available with all programming fuses blown (maximum programming code set). The  $D_{(Q)}$  range is the total range from  $D_{(Q)}(min)$  up to and including  $D_{(Q)}(max)$ . See Characteristic Definitions section.

<sup>9</sup>Step size is larger than required, in order to provide for manufacturing spread. See Characteristic Definitions section.

<sup>&</sup>lt;sup>10</sup>Non-ideal behavior in the programming DAC can cause the step size at each significant bit rollover code to be greater than twice the maximum specified value of Step<sub>D(Q)</sub>, Step<sub>SENS</sub>, or Step<sub>FPWM</sub>.

<sup>&</sup>lt;sup>11</sup>Overall programming value accuracy. See Characteristic Definitions section.

<sup>&</sup>lt;sup>12</sup>Programmed at 150°C and calculated relative to 25°C.

$<sup>^{13}</sup>$ Sensitivity drift from expected value at  $T_A$  after programming SENS $_{TC}$ . See Characteristic Definitions section.

$<sup>^{14}</sup>D_{(Q)}$  drift from expected value at  $T_A$  after programming  $D_{TC(Q)}$ .

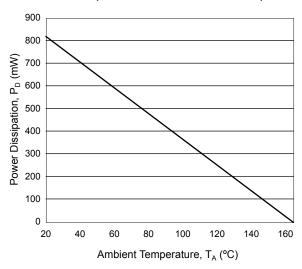

THERMAL CHARACTERISTICS may require derating at maximum conditions, see application information

| Characteristic             | Symbol          | Test Conditions*                               | Value | Units |

|----------------------------|-----------------|------------------------------------------------|-------|-------|

| Package Thermal Resistance | $R_{\theta JA}$ | 1-layer PCB with copper limited to solder pads | 177   | °C/W  |

<sup>\*</sup>Additional thermal data available on the Allegro Web site.

# Power Derating Curve V<sub>CC</sub>(max) V<sub>CC</sub>(min) Ambient Temperature, T<sub>A</sub> (°C)

## Power Dissipation versus Ambient Temperature

#### **Characteristic Definitions**

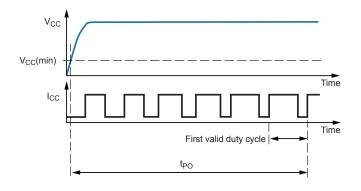

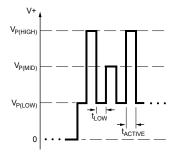

**Power-On Time** When the supply is ramped to its operating voltage, the device requires a finite time to power its internal components before supplying a valid PWM output duty-cycle. Power-On Time,  $t_{PO}$ , is defined as the time it takes for the output voltage to settle within  $\pm 10\%$  of its steady state value after the power supply has reached its minimum specified operating voltage,  $V_{CC}$  (min). (See figure 1.)

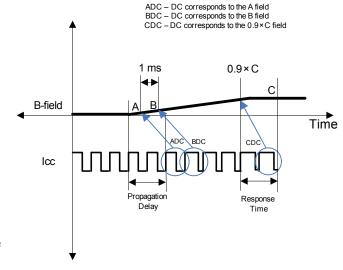

**Propagation Delay** Traveling time of signal from input Hall plate to output stage of device. (See figure 2.)

**Response Time** The time interval,  $t_{RESPONSE}$ , between a) when the applied magnetic field reaches 90% of its final value, and b) when the sensor IC reaches 90% of its output corresponding to the applied magnetic field. (See figure 2.)

**PWM<sub>OUT</sub> Rise Time** The time,  $t_r$ , elapsed between 10% and 90% of the rising signal value when output current switches from low to high states.

**PWM<sub>OUT</sub> Fall Time** The time,  $t_f$ , elapsed between 90% and 10% of the falling signal value when output current switches from high to low states.

**Quiescent Current Duty Cycle** In the quiescent state (no significant magnetic field: B = 0 G), the Quiescent Current Duty Cycle,  $D_{(Q)}$ , equals a specific programmed duty cycle throughout the entire operating ranges of  $V_{CC}$  and ambient temperature,  $T_A$ .

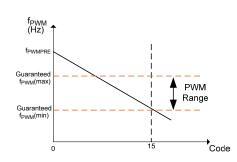

Guaranteed Quiescent Current Duty Cycle Range The Quiescent Current Duty Cycle,  $D_{(Q)}$ , can be programmed around its nominal value of 50% D, within the Guaranteed Quiescent Duty Cycle Range limits:  $D_{(Q)}(\min)$  and  $D_{(Q)}(\max)$ . The available guaranteed programming range for  $D_{(Q)}$  falls within the distributions of the minimum and the maximum programming code for setting  $D_{(Q)}$ . (See figure 3.)

Figure 1. Definition of Power-On Time

Average Quiescent Current Duty Cycle Step Size The Average Quiescent Current Duty Cycle Step Size,  $Step_{D(Q)}$ , for a single device is determined using the following calculation:

$$Step_{D(Q)} = \frac{D_{(Q)}(max) - D_{(Q)}(min)}{2^n - 1} , \qquad (1)$$

where:

n is the number of available programming bits in the trim range,  $2^{n}-1$  is the value of programming steps in the range,

$D_{(Q)}(max)$  is the maximum reached quiescent duty cycle, and  $D_{(Q)}(min)$  is minimum reached quiescent duty cycle.

Figure 2. Definitions of Propagation Delay and Response Time

Figure 3. Definition of Guaranteed Quiescent Voltage Output Range

**Quiescent Current Duty Cycle Output Programming**

**Resolution** The programming resolution for any device is half of its programming step size. Therefore, the typical programming resolution will be:

$$Err_{PGD(O)}(typ) = 0.5 \times Step_{D(O)}(typ) \qquad (2)$$

Quiescent Duty Cycle Output Drift through Temperature Range Due to internal component tolerances and thermal considerations, the Quiescent Duty Cycle Temperature Coefficient,  $D_{TC(Q)}$ , may drift from its nominal value over the operating ambient temperature,  $T_A$ . For purposes of specification, the Quiescent Duty Cycle Output Drift Through Temperature Range,  $\Delta D_{(O)}$  (% D), is defined as:

$$\Delta D_{(Q)} = D_{(Q)(TA)} - D_{(Q)(25^{\circ}C)}$$

, (3)

where  $D_{(Q)(TA)}$  is the quiescent duty cycle measured at  $T_A$  and  $D_{(Q)(25^{\circ}C)}$  is the quiescent duty cycle measured at 25°C.

**Sensitivity** The presence of a south polarity magnetic field, perpendicular to the branded surface of the package face, increases the current duty cycle from its quiescent value toward the maximum duty cycle limit. The amount of the current duty cycle increase is proportional to the magnitude of the magnetic field applied. Conversely, the application of a north polarity field decreases the current duty cycle from its quiescent value. This proportionality is specified as the magnetic Sensitivity, Sens ((% D)/G), of the device, and it is defined for bipolar devices as:

Sens =

$$\frac{D_{\text{(BPOS)}} - D_{\text{(BNEG)}}}{\text{BPOS} - \text{BNEG}} , \tag{4}$$

and for unipolar devices as:

$$Sens = \frac{D_{(BPOS)} - D_{(Q)}}{BPOS} , \qquad (5)$$

where BPOS and BNEG are two magnetic fields with opposite polarities.

**Guaranteed Sensitivity Range** The magnetic Sensitivity can be programmed from its initial value, Sens<sub>init</sub>, to a value within the Guaranteed Sensitivity Range limits: Sens<sub>Range</sub>(min) and Sens<sub>Range</sub>(max).

**Average Sensitivity Step Size** Refer to the Average Quiescent Current Duty Cycle Step Size section for a conceptual explanation.

**Sensitivity Programming Resolution** Refer to the Quiescent Current Duty Cycle Programming Resolution section for a conceptual explanation.

**Carrier Frequency Target** The PWM<sub>OUT</sub> signal Carrier Frequency Programming Range,  $f_{PWM}$ , can be programmed to its typical value of 1 kHz.

**Average Carrier Frequency Step Size** Refer to the Average Quiescent Current Duty Cycle Step Size section for a conceptual explanation.

**Carrier Frequency Programming Resolution** Refer to the Quiescent Durrent Duty Cycle Programming Resolution section for a conceptual explanation.

**Sensitivity Temperature Coefficient** Device sensitivity changes as temperature changes, with respect to its programmed Sensitivity Temperature Coefficient, Sens<sub>TC</sub>. Sens<sub>TC</sub> is programmed at 150°C, and calculated relative to the nominal sensitivity programming temperature of 25°C. Sens<sub>TC</sub> (%/°C) is defined as:

$$Sens_{TC} = \left(\frac{Sens_{T2} - Sens_{T1}}{Sens_{T1}} \times 100\%\right) \left(\frac{1}{T2 - TI}\right) , \qquad (6)$$

where T1 is the nominal Sens programming temperature of 25°C, and T2 is the programming temperature of 150°C. The expected value of Sens through the full ambient temperature range, Sens<sub>EXPECTED(TA)</sub>, is defined as:

$$Sens_{EXPECTED(TA)} = \frac{Sens_{T1} \times [100\% + Sens_{TC} (T_A - TI)]}{100\%} . \tag{7}$$

$Sens_{EXPECTED\ (TA)}$  should be calculated using the actual measured values of  $Sens_{T1}$  and  $Sens_{TC}$  rather than programming target values.

Sensitivity Drift Through Temperature Range Second order Sensitivity Temperature Coefficient effects cause the magnetic Sensitivity, Sens, to drift from its expected value through the operating ambient temperature range,  $T_A$ . For purposes of specification, the Sensitivity Drift Through Temperature Range,  $\Delta Sens_{TC}$ , is defined as:

$$\Delta Sens_{TC} = \frac{Sens_{TA} - Sens_{EXPECTED(TA)}}{Sens_{EXPECTED(TA)}} \times 100\% . \tag{8}$$

Sensitivity Drift Due to Package Hysteresis Package stress and relaxation can cause the device Sensitivity at  $T_A = 25$ °C to change during and after temperature cycling.

For purposes of specification, the Sensitivity Drift Due to Package Hysteresis,  $\Delta Sens_{PKG}$ , is defined as:

$$\Delta Sens_{PKG} = \frac{Sens_{(25^{\circ}C)2} - Sens_{(25^{\circ}C)1}}{Sens_{(25^{\circ}C)1}} \times 100\% , \qquad (9)$$

where  $Sens_{(25^{\circ}C)1}$  is the programmed value of sensitivity at  $T_A =$ 25°C, and Sens<sub>(25°C)2</sub> is the value of sensitivity at  $T_A = 25$ °C, after temperature cycling T<sub>A</sub> up to 150°C, down to -40°C, and back to up 25°C.

**Linearity Sensitivity Error** The A1357 is designed to provide a linear current output in response to a ramping applied magnetic field. Consider two magnetic fields, B1 and B2. Ideally, the sensitivity of a device is the same for both fields, for a given supply voltage and temperature. Linearity error is present when there is a difference between the sensitivities measured at B1 and B2.

Linearity Sensitivity Error is calculated separately for the positive (Lin<sub>ERRPOS</sub>) and negative (Lin<sub>ERRNEG</sub>) applied magnetic fields. Linearity error (%) is measured and defined as:

$$\begin{aligned} & \operatorname{Lin}_{\mathrm{ERRPOS}} = \left(1 - \frac{\operatorname{Sens}_{\mathrm{BPOS2}}}{\operatorname{Sens}_{\mathrm{BPOS1}}}\right) \times 100\% \quad , \\ & \operatorname{Lin}_{\mathrm{ERRNEG}} = \left(1 - \frac{\operatorname{Sens}_{\mathrm{BNEG2}}}{\operatorname{Sens}_{\mathrm{BNEG1}}}\right) \times 100\% \quad , \end{aligned}$$

where:

Sens<sub>Bx</sub> =

$$\frac{|D_{(Bx)} - D_{(Q)}|}{B_x}$$

(11)

and B<sub>POSx</sub> and B<sub>NEGx</sub> are positive and negative magnetic fields, with respect to the quiescent current duty cycle such that  $B_{POS2}$  =  $2 \times B_{POS1}$  and  $B_{NEG2} = 2 \times B_{NEG1}$ .

Then:

$$Lin_{ERR} = max(Lin_{ERRPOS}, Lin_{ERRNEG})$$

(12)

Note that unipolar devices only have positive linearity error  $(Lin_{ERRPOS}).$

Symmetry Sensitivity Error The magnetic sensitivity of the A1357 device is constant for any two applied magnetic fields of equal magnitude and opposite polarities. Symmetry Sensitivity Error, Sym<sub>ERR</sub> (%), is measured and defined as:

$$Sym_{\text{ERR}} = \left(1 - \frac{Sens_{\text{BPOS}}}{Sens_{\text{BNEG}}}\right) \times 100\% \quad , \tag{13}$$

where  $Sens_{Bx}$  is as defined in equation 11, and BPOS and BNEG are positive and negative magnetic fields such that |BPOS| = |BNEG|. Note that the Symmetry Sensitivity Error specification is valid only for bipolar devices.

**Duty Cycle Jitter** The duty cycle of the PWM<sub>OUT</sub> output may vary slightly over time despite the presence of a constant applied magnetic field and a constant Carrier Frequency, f<sub>PWM</sub>, for the PWM<sub>OUT</sub> signal. This phenomenon is known as jitter, and is defined as:

$$\text{Jitter}_{\text{PWM}} = \left(\frac{1}{n} \sum_{i=1}^{n} D_{\text{B}i}\right) \pm 3 \, \sigma \quad , \tag{14}$$

where  $D_{B1},...,D_{Bn}$  are the sampled duty cycles in a constant applied magnetic field, B, measured over 1000 PWM clock periods, and Jitter<sub>PWM</sub> is given in % D.

9

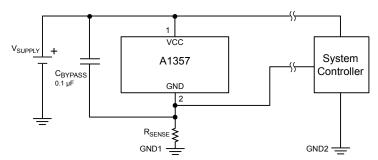

## **Typical Application Circuit**

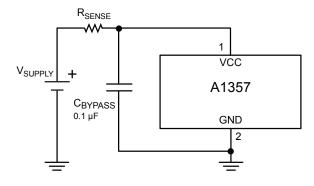

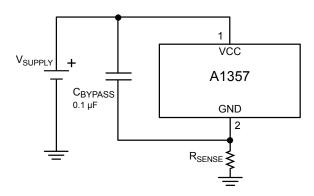

The current switching performed by the Hall sensor IC can be observed as voltage switching. To do so, place a sense resistor, R<sub>SENSE</sub>, between the supply and the A1357 VCC pin (see figure 4), or between the A1357 GND pin and ground (figure 5). There is an advantage to putting the sense resistor between the supply and the A1357 VCC pin, because the resistor can then provide additional device protection from supply transients.

When specifying value of the  $R_{SENSE}$  and the applied supply voltage in the application, the following equation must be applied, in order to provide enough voltage to allow the A1357 to power-up:

$$V_{\rm SUPPLY} > R_{\rm SENSE} \times I_{\rm CC\_HIGH}({\rm max}) + V_{\rm CC}({\rm min})$$

, (15)

where  $I_{\rm CC}({\rm max})$  is the maximum A1357 supply current and

V<sub>CC</sub>(min) is the A1357 minimum supply voltage.

Substituting into equation 15:

$$12 \text{ V} > R_{\text{SENSE}} \times 16.5 \text{ mA} + 4.5 \text{ V}$$

,

therefore:

$$R_{\text{SENSE}} \le (12 - 4.5) \text{ V} / 16.5 \text{ mA}$$

$\le 454 \Omega$ .

It can be seen that  $R_{SENSE}$  is proportional to  $V_{SUPPLY}.$  The higher the value of  $R_{SENSE},$  the higher the application supply voltage required.

The recommended minimum  $C_{BYPASS}$  value is 0.01  $\mu F$ .

Figure 4. High-side PWM voltage sensing configuration

Figure 5. Low-side PWM voltage sensing configuration

# **Programming Guidelines**

#### Overview

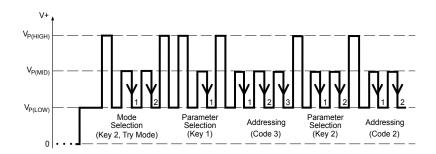

Programming is accomplished by sending a series of input voltage pulses serially through the VCC pin of the device. A unique combination of different voltage level pulses controls the internal programming logic of the device to select a programmable parameter and change its value. There are three voltage levels that must be taken into account when programming. These levels are referred to as *high*, V<sub>P(HIGH)</sub>, *mid*, V<sub>P(MID)</sub>, and *low*, V<sub>P(LOW)</sub>.

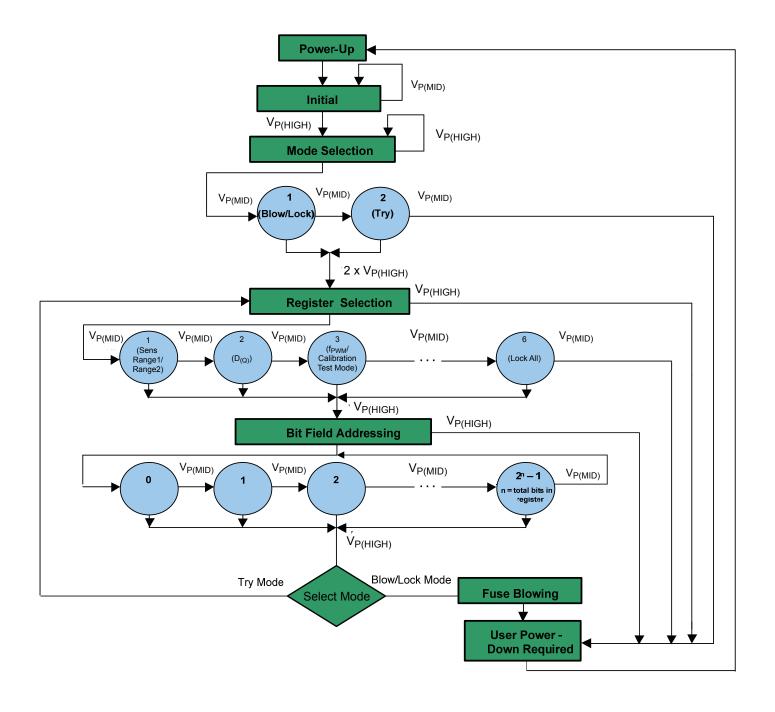

The A1357 features Try mode, Blow mode and Lock mode:

- In Try mode, the value of multiple programmable parameters may be set and measured simultaneously. The parameter values are stored temporarily, and reset after cycling the supply voltage.

- In Blow mode, the value of a single programmable parameter may be set and measured, and then permanently set by blowing solid-state fuses internal to the device. Additional parameters may be blown sequentially. This mode also is used for blowing the device-level fuse (when Lock mode is enabled), which permanently blocks the further programming of all parameters.

- Lock mode prevents all future programming of the device. This is accomplished by blowing a special fuse using Blow mode.

The programming sequence is designed to help prevent the device from being programmed accidentally; for example, as a result of noise on the supply line. Although any programmable variable power supply can be used to generate the pulse waveforms, Allegro highly recommends using the Allegro Sensor Evaluation Kit, available on the Allegro website On-line Store. The manual for that kit is available for download free of charge, and provides additional information on programming this device.

#### **Definition of Terms**

**Register** The section of the programming logic that controls the choice of programmable modes and parameters.

**Bit Field** The internal fuses unique to each register, represented as a binary number. Changing the bit field settings of a particular register causes its programmable parameter to change, based on the internal programming logic.

**Key** A series of mid-level voltage pulses used to select a register, with a value expressed as the decimal equivalent of the binary value. The LSB of a register is denoted as key 1, or bit 0.

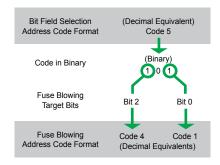

**Code** The number used to identify the combination of fuses activated in a bit field, expressed as the decimal equivalent of the binary value. The LSB of a bit field is denoted as code 1, or bit 0.

**Addressing** Increasing the bit field code of a selected register by serially applying a pulse train through the VCC pin of the device. Each parameter can be measured during the addressing process, but the internal fuses must be blown before the programming code (and parameter value) becomes permanent.

**Fuse Blowing** Applying a high voltage pulse of sufficient duration to permanently set an addressed bit by blowing a fuse internal to the device. After a bit (fuse) has been blown, it cannot be reset.

**Blow Pulse** A high voltage pulse of sufficient duration to blow the addressed fuse.

**Cycling the Supply** Powering-down, and then powering-up the supply voltage. Cycling the supply is used to clear the programming settings in Try mode.

#### Programming Pulse Requirements, Protocol at T<sub>A</sub> = 25 °C

| Characteristic         | Symbol               | Notes                                                                                                                                                                                                                                                                                                                                                                               | Min. | Тур. | Max. | Unit |

|------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

|                        | V <sub>P(LOW)</sub>  |                                                                                                                                                                                                                                                                                                                                                                                     | 4.5  | 5    | 5.5  | V    |

| Programming Voltage    | V <sub>P(MID)</sub>  | Measured at the VCC pin.                                                                                                                                                                                                                                                                                                                                                            |      | 15   | 16   | V    |

| voltago                | V <sub>P(HIGH)</sub> |                                                                                                                                                                                                                                                                                                                                                                                     | 26   | 27   | 28   | V    |

| Programming<br>Current | I <sub>P</sub>       | Minimum supply current required to ensure proper fuse blowing. In addition, a minimum capacitance, $C_{BLOW} = 0.1 \ \mu\text{F}$ , must be connected between the supply and GND pins during programming to provide the current necessary for fuse blowing. The blowing capacitor should be removed and the load capacitance used for properly programming duty cycle measurements. |      | _    | _    | mA   |

|                        | t <sub>LOW</sub>     | Duration of $V_{P(LOW)}$ for separating $V_{P(MID)}$ and $V_{P(HIGH)}$ pulses.                                                                                                                                                                                                                                                                                                      |      | _    | _    | μs   |

| Pulse Width            | t <sub>ACTIVE</sub>  | Duration of $V_{P(MID)}$ and $V_{P(HIGH)}$ pulses for register selection or bit field addressing.                                                                                                                                                                                                                                                                                   |      | _    | _    | μs   |

|                        | t <sub>BLOW</sub>    | Duration of V <sub>P(HIGH)</sub> pulses for fuse blowing.                                                                                                                                                                                                                                                                                                                           |      | _    | _    | μs   |

| Pulse Rise Time        | t <sub>Pr</sub>      | Rise time required for transitions from $V_{P(LOW)}$ to either $V_{P(MID)}$ or $V_{P(HIGH)}$ .                                                                                                                                                                                                                                                                                      |      | _    | 100  | μs   |

| Pulse Fall Time        | t <sub>Pf</sub>      | Fall time required for transitions from $V_{P(HIGH)}$ to either $V_{P(MID)}$ or $V_{P(LOW)}$ .                                                                                                                                                                                                                                                                                      | 5    | _    | 100  | μs   |

## **Programming Procedures**

#### **Mode and Parameter Selection**

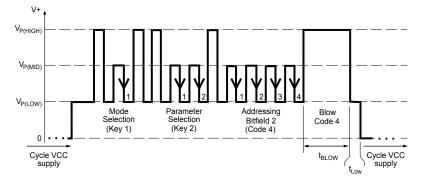

Each programmable mode and parameter can be accessed through specific registers. To select a register, a sequence of voltage pulses consisting of a  $V_{P(\mathrm{HIGH})}$  pulse, a series of  $V_{P(\mathrm{MID})}$  pulses, and a  $V_{P(\mathrm{HIGH})}$  pulse (with no VCC supply interruptions) must be applied serially to the supply pin. The quantity of  $V_{P(\mathrm{MID})}$  pulses is called the key, and uniquely identifies each register. The pulse train used for selection of the first register, key 1, is shown in figure 6.

The A1357 has two registers that select among the three programmable modes:

• Register Mode 1:

Blow and Lock modes

• Register Mode 2:

Try mode

And there are four registers that select among the four programmable parameters:

• Register 1:

Sensitivity, Sens

• Register 2:

Quiescent Current Duty Cycle, D<sub>(O)</sub>

• Register 3:

Pulse width modulated carrier frequency ,  $f_{\text{PWM}}$

• Register 6:

Lock (device locking)

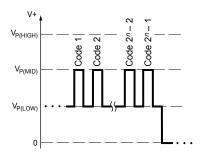

Figure 6. Parameter selection pulse train. This shows the sequence for selecting the register corresponding to key 1, indicated by a single  $V_{P(MID)}$  pulse.

#### Bit Field Addressing

After a programmable parameter has been selected, a  $V_{P(HIGH)}$  pulse transitions the programming logic into the bit field addressing state. Applying a series of  $V_{P(MID)}$  pulses to the VCC pin of the device, as shown in figure 7, increases by one the bit field of the selected parameter.

When addressing the bit field, the quantity of  $V_{P(MID)}$  pulses is represented by a decimal number called a *code*. Addressing activates the corresponding fuse locations in the given bit field by increasing the binary value of an internal DAC. The value of the bit field (and code) increases by one with the falling edge of each  $V_{P(MID)}$  pulse, up to the maximum possible code (see the Programming Logic table). As the value of the bit field code increases, the value of the programmable parameter changes. Measurements can be taken after each pulse to determine if the required result for the programmable parameter has been reached. Cycling the supply voltage resets all the locations in the bit field that have unblown fuses to their initial states.

#### **Fuse Blowing**

After the required code is found for a given parameter, its value can be set permanently by blowing individual fuses in the appropriate register bit field. Blowing is accomplished by applying a  $V_{P(HIGH)}$  pulse, called a *blow* pulse, of sufficient duration at the  $V_{P(HIGH)}$  level to permanently set an addressed bit by blowing a fuse internal to the device. Due to power requirements, the fuse for each bit in the bit field must be blown individually. To accomplish this, the code representing the required parameter value must be translated to a binary number. For example, as shown in figure 8, decimal code 5 is equivalent to the binary number 101. Therefore bit 2 (code 4) must be addressed and blown, the device power supply cycled, and then bit 0 (code 1) addressed

Figure 7. Bit field addressing pulse train. Addressing the bit field by increasing the code causes the programmable parameter value to change. The number of bits available for a given programming code, n, varies among parameters; for example, the bit field for  $D_{(Q)}$  has 8 bits available, which allows 255 separate codes to be used.

and blown. An appropriate sequence for blowing code 5 is shown in figure 9. The order of blowing bits, however, is not important. Blowing bit 0 first, and then bit 2 is acceptable.

Note: After blowing, the programming is not reversible, even after cycling the supply power. Although a register bit field fuse cannot be reset after it is blown, additional bits within the same register can be blown at any time until the device is locked. For example, if bit 1 (binary 10) has been blown, it is still possible to blow bit 0. The end result would be binary 11 (decimal code 3).

#### **Locking the Device**

After the required code for each parameter is programmed, the device can be locked to prevent further programming of any parameters.

#### **Additional Guidelines**

The additional guidelines presented in this section should be followed to ensure the proper behavior of these devices:

A 0.1 μF blowing capacitor, C<sub>BLOW</sub>, must be mounted between the VCC pin and the GND pin during programming, to ensure enough current is available to blow fuses.

Figure 8. Example of code 5 broken into its binary components, which are code 4 and code 1.

- The application load capacitance, C<sub>L</sub>, should be used when measuring the duty cycle during programming. The blowing capacitor, C<sub>BLOW</sub>, should be removed during measurement and should only be applied when blowing fuses.

- The blowing capacitor, C<sub>BLOW</sub>, must be replaced in the final application with the load capacitance, C<sub>L</sub>, for proper operation.

- The power supply used for programming must be capable of delivering at least 26 V and 300 mA.

- Be careful to observe the t<sub>LOW</sub> delay time before powering down the device after blowing each bit.

- The following programming order is recommended:

- $1. f_{PWM}$

- 2. Sens

- 3. D<sub>(O)</sub>

- 4. Lock the device (only after all other parameters have been programmed and validated, because this prevents any further programming of the device)

#### **Programming Modes**

**Try Mode** Try mode allows multiple programmable parameters to be tested simultaneously without permanently setting any values. In this mode, each  $V_{P(HIGH)}$  pulse will indefinitely loop the programming logic through the mode, register, and bit field selection states. There must be no interruptions in the  $V_{CC}$  supply.

After powering the  $V_{CC}$  supply, select mode key 2, followed by the parameter register, and then address its bit field. When addressing the bit field, each  $V_{P(MID)}$  pulse increases the value of the parameter register by one, up to the maximum possible code (see Programming Logic section). The addressed parameter value is stored in the device even after the programming drive voltage is removed from the VCC pin, allowing its value to be measured. To test an additional programmable parameter in

Figure 9. Example of Blow Mode programming pulses applied to the VCC pin. In this example,  $D_{(Q)}$  (Parameter Key 2) is addressed to code 4 (i.e bit 2) and its value is permanently blown.

conjunction with the original, enter an additional  $V_{P(HIGH)}$  pulse on the VCC pin to reenter the parameter selection field. Select a different parameter register, and address its bit field, without any supply interruptions. Both parameter values will be stored and can be measured after removing the programming drive voltage. Multiple programming combinations can be tested to achieve optimal application accuracy. See figure 10 for an example of the Try mode pulse train.

Registers can be addressed and re-addressed an indefinite number of times in any order. After the required code is found for each register, cycle the supply and blow the bit field using Blow mode.

**Blow Mode** After the required value of the programmable parameter is found using Try mode, the corresponding code should be blown to make the value permanent. To do this, first select Blow mode as key 1, then the required parameter register, and address and blow each required bit separately (as described in the Fuse Blowing section). The supply must be cycled between blowing each bit of a given code. After a bit is blown, cycling the supply will not reset its value.

Single parameters can be still addressed in the Blow mode before fuse blowing. Simultaneous addressing of multiple parameters, as in Try mode, is not possible. After powering the  $V_{CC}$  supply, select the desired parameter register and address its bit field. When addressing the bit field, each  $V_{P(MID)}$  pulse increases the value of the parameter register by one, up to the maximum possible code (see Programming Logic table). The addressed parameter value is stored in the device even after the programming drive voltage is removed from the VCC pin, allowing its value to be measured. It is not possible to decrease the value of the register without resetting the parameter bit field. To reset the bit field, and thus the value of the programmable parameter, cycle the supply,  $V_{CC}$ , voltage.

It is possible to switch between Try and Blow modes in that, after individual programmable parameters have been blown in Blow mode, other parameters can be still tested in Try mode.

**Lock Mode** To lock the device, first select Lock mode, then address the Lock bit and apply a blow pulse with  $C_{BLOW}$  in place. After locking the device, no future programming of any parameter is possible.

Figure 10. Example of Try mode programming pulses applied to the VCC pin. In this example, Sensitivity (parameter key 1) is addressed to code 3, and  $D_{(Q)}$  (parameter key 2) is addressed to code 2. The values set in the Sensitivity and  $D_{(Q)}$  registers will be held in the device until the supply is cycled. Permanent fuse blowing cannot be accomplished in Try mode.

# **Programming State Machine**

## **Programming Logic Table**

| Mode or Parameter      | Bit Fie       | eld Address | Description                                                                      |

|------------------------|---------------|-------------|----------------------------------------------------------------------------------|

| Name<br>(Register Key) | Dinami Farmet |             | Description                                                                      |

| Programmable Mode      |               | ·           |                                                                                  |

| Lock, Blow<br>(1)      | 01            | 1           | Entry to Lock or Blow mode                                                       |

| Try<br>(2)             | 10            | 2           | Entry to Try mode                                                                |

| Programmable Parameter |               |             |                                                                                  |

| Sens                   | 0 0000 0000   | 0           | Minimum Sens value in Sens <sub>Range1</sub> , Sens = Sens <sub>PRE</sub>        |

| (Range1/Range2)        | 0 1111 1111   | 255         | Maximum Sens value in Sens <sub>Range1</sub>                                     |

| (1)                    | 1 0000 0000   | 256         | Minimum Sens value in Sens <sub>Range2</sub>                                     |

|                        | 1 1111 1111   | 511         | Maximum Sens value in Sens <sub>Range2</sub>                                     |

|                        | 0 0000 0000   | 0           | Initial value, D <sub>(Q)</sub> = D <sub>(Q)PRE</sub>                            |

| D                      | 0 1111 1111   | 255         | Maximum quiescent current duty cycle in range                                    |

| D <sub>(Q)</sub> (2)   | 1 0000 0000   | 256         | Switch from programming increasing $D_{(Q)}$ to programming decreasing $D_{(Q)}$ |

|                        | 1 1111 1111   | 511         | Minimum quiescent current duty cycle in range                                    |

| f <sub>PWM</sub> /     | 0 0000 0000   | 0           | Initial value; f <sub>PWM</sub> = f <sub>PWMPRE</sub>                            |

| Calibration Test Mode  | 0 0000 1111   | 15          | Minimum PWM frequency in range                                                   |

| (3)                    | 0 0001 0000   | 16          | Enable 50% Duty Cycle Calibration Test Mode                                      |

| Lock All (6)           | 10 0000 0000  | 512         | Enable blowing Lock fuse to lock device                                          |

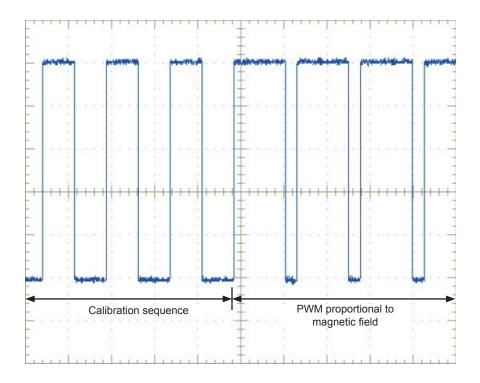

## 50% Duty Cycle Calibration Test Mode

The calibration mode is provided so that the user can compensate for differences in the ground potential between the A1357 and any interface circuitry used to measure the pulse width of the A1357 current. The test mode is optional and must be enabled by blowing programming bits. After the bit for the test mode has been blown, the device enters 50% Duty Cycle Calibration Test mode every time the device is powered-up. The bit enabling test mode is key 3, bit 4.

In customer applications, the PWM interface circuitry (shown as the system controller in figure 11) and the A1357 may be

powered via different power and ground circuits. As a result, the ground reference for the A1357 may differ from the ground reference of the system controller. In some customer applications, this ground difference can be as large as  $\pm 0.5$  V.

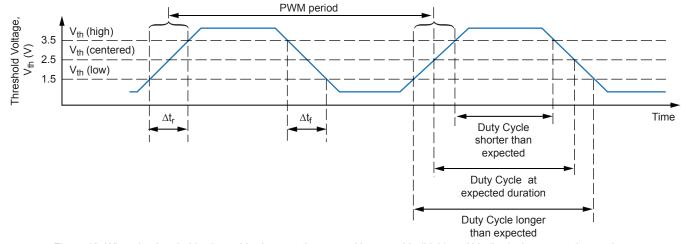

Differences in the ground reference for the A1357 and the system controller can result in variations in the threshold voltage used to measure the duty cycle of the A1357. If the PWM conversion threshold voltage varies, then the duty cycle will vary because there is a finite rise time,  $t_r$ , and fall time,  $t_f$ , in the PWM waveform. This problem is shown in figure 12.

Figure 11. In many applications the A1357 may be powered using a different ground reference than the system controller. This may cause the ground reference for the A1357 (GND1) to differ from the ground reference of the system controller (GND2) by as much as to  $\pm$  0.5 V.

Figure 12. When the threshold voltage,  $V_{th}$ , is correctly centered between  $V_{th}$  (high) and  $V_{th}$  (low), the current duty cycle accurately coincides with the applied magnetic field. If the threshold voltage is raised, the current duty cycle appears shorter than expected. Conversely, if the threshold voltage is lowered, the current duty cycle is longer than expected.

The 50% Duty Cycle Calibration Test mode allows end users to compensate for any threshold errors that result from a difference in system ground potentials. When calibration mode has been enabled, at power-up the device operates initially in calibration mode for  $t_{CAL}$ , 50 ms, during which the device current waveform has a fixed 50% duty cycle (the programmed quiescent duty cycle,  $D_{(Q)}$ , value) regardless of the applied external magnetic field (see figure 13). This allows the system controller to com-

pare the measured quiescent duty cycle with an ideal 50% duty cycle. After  $t_{CAL}$  has elapsed, the duty cycle will correspond to an applied magnetic field as expected. The calibration test time ( $t_{CAL}$ ) corresponds with a target PWM frequency of 1 kHz. If the PWM frequency is programmed away from its target of 1 kHz, the duration of the calibration test time will scale inversely with the change in PWM frequency.

Figure 13. With calibration mode in effect, after powering-on the A1357 outputs a 50% duty cycle for the first 50 ms,  $t_{CAL}$ , regardless of the applied magnetic field. After  $t_{CAL}$  has elapsed, the output responds to a magnetic field as expected. The example in this figure assumes that a large +B field is applied to the device after  $t_{CAL}$  has elapsed.

# Package KB, 3-Pin SIP

# Two-Wire High Precision Linear Hall-Effect Sensor IC With Pulse Width Modulated Output Current

Copyright ©2011, Allegro MicroSystems, Inc.

Allegro MicroSystems, Inc. reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro's products are not to be used in life support devices or systems, if a failure of an Allegro product can reasonably be expected to cause the failure of that life support device or system, or to affect the safety or effectiveness of that device or system.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

For the latest version of this document, visit our website:

www.allegromicro.com