# CXD2508AQ/AR

## **CD Digital Signal Processor**

#### Description

The CXD2508AQ/AR is a digital signal processor for CD players and is equipped with built-in digital filters, no-sound data detection circuit, and 1-bit DAC.

#### Features

- DSP block

- Digital PLL

- EFM frame sync protection

- SEC strategy-based error correction

- Subcode demodulation, CRC checking

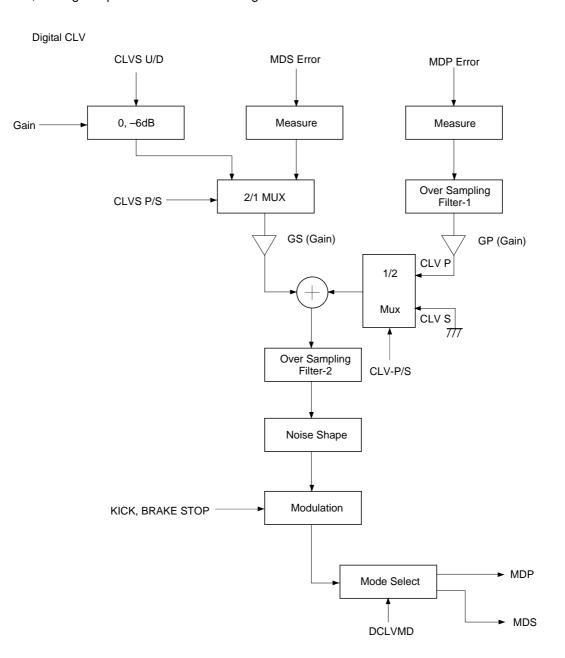

- Digital spindle servo

- Servo auto sequencer

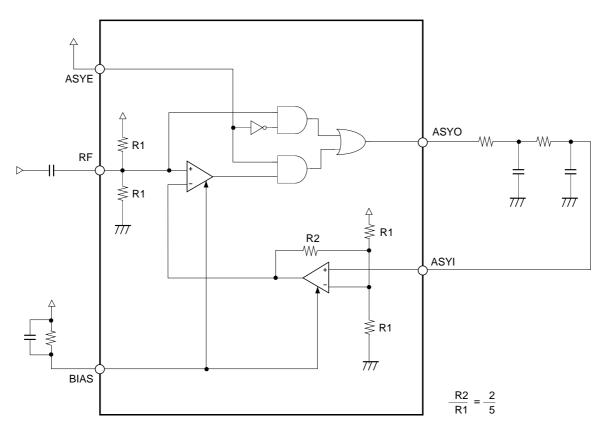

- Asymmetry compensation circuit

- Digital audio interface output

- 16K RAM

- Double-speed playback capability

- New microcomputer interface circuit

- Digital filter, DAC block

- Double-speed playback capability

- Digital de-emphasis

- Digital attenuation

- No-sound data detection circuit

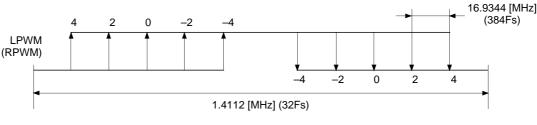

- 4 Fs oversampling filter

- Secondary  $\Delta \Sigma$  noise shaper

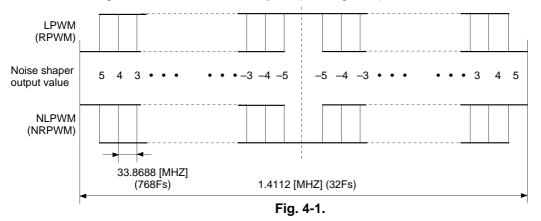

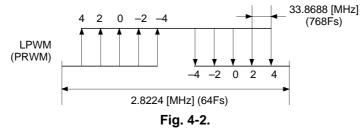

- PWM-system pulse conversion output

#### **Recommended Operating Conditions**

• Supply voltage VDD Note) 4.5 to 5.5V

(double-speed playback) 3.5 to 5.5V (normal-speed playback) 3.4 to 5.5V (low power consumption or special playback mode)

Operating temperature

- Topr –20 (min.) 75 (max.) °C

- **Note)** VDD (min.) is varied by the playback speed and built-in VCO in the CXD2508AQ/AR. 4.5V is the value using the VCO which generates the slower frequency in double-speed playback. The table below shows the VDD (min.) for each condition.

| Playback<br>speed | VDD (min.) [V]    |                     |           |  |  |  |

|-------------------|-------------------|---------------------|-----------|--|--|--|

|                   | VCO<br>high-speed | VCO<br>normal-speed | DAC block |  |  |  |

| × 2               | 3.40              | 4.50                | 3.40      |  |  |  |

| × 1               | 3.40              | 3.50                | 3.40      |  |  |  |

| × 1*              | 3.40              | 3.40                | 3.40      |  |  |  |

\* When the internal operation of the LSI is set to doublespeed mode and the crystal oscillation frequency is halved, normal-speed playback results.

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

#### Applications

CD players

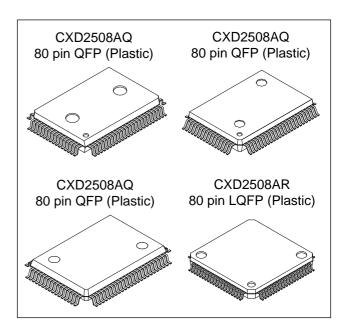

#### Structure

Silicon gate CMOS IC

#### Absolute Maximum Ratings

| <ul> <li>Supply voltage</li> </ul>      | Vdd   | -0.3 to 7.0                  | V     |  |  |  |  |  |

|-----------------------------------------|-------|------------------------------|-------|--|--|--|--|--|

| <ul> <li>Input voltage</li> </ul>       | Vi    | -0.3 to 7.0                  | V     |  |  |  |  |  |

| <ul> <li>Input voltage</li> </ul>       | Vin V | /ss-0.3V (min.) VDD+0.3 (max | (.) V |  |  |  |  |  |

| <ul> <li>Output voltage</li> </ul>      | Vo    | -0.3 to 7.0                  | V     |  |  |  |  |  |

| <ul> <li>Storage temperative</li> </ul> | ature |                              |       |  |  |  |  |  |

| <b>-</b> .                              | Tstg  | -40 to 125                   | °C    |  |  |  |  |  |

| Supply voltage variation                |       |                              |       |  |  |  |  |  |

|                                         |       |                              | ,     |  |  |  |  |  |

Vss-AVss -0.3V (min.) +0.3V (max.) Vdd-AVdd -0.3V (min.) +0.3V (max.)

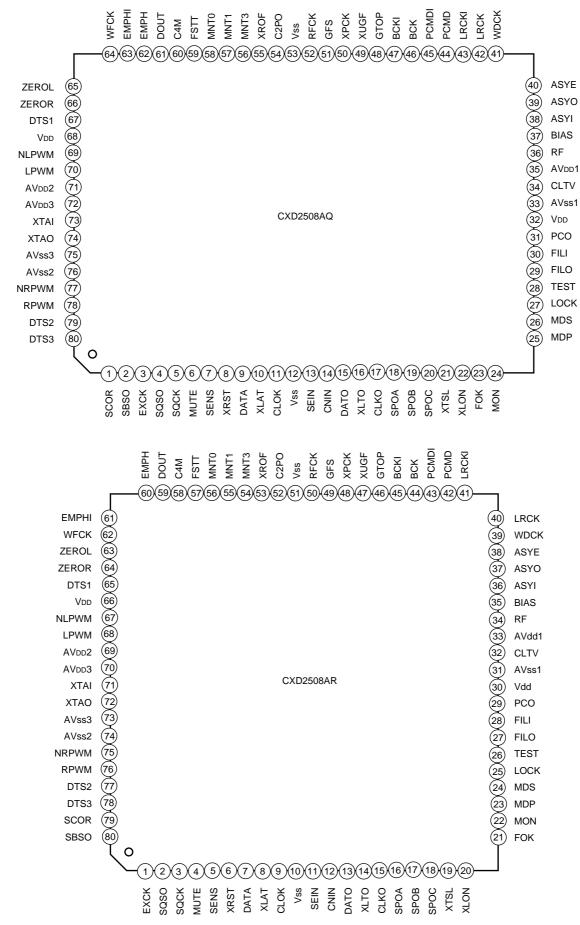

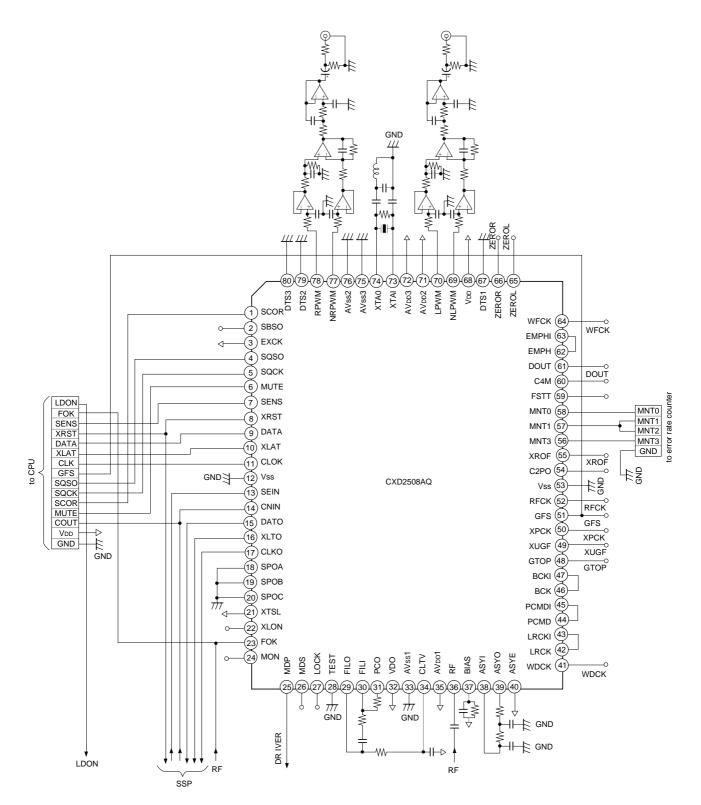

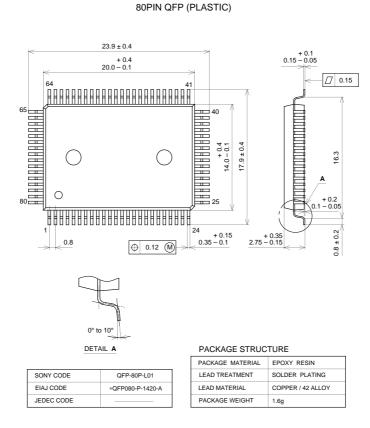

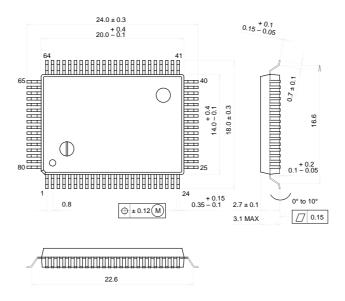

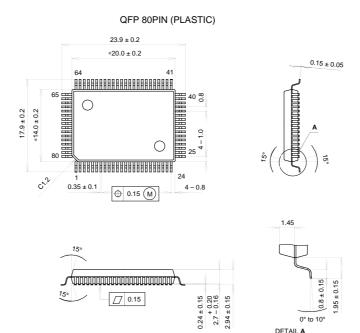

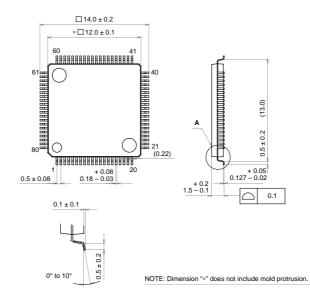

#### **Pin Configuration**

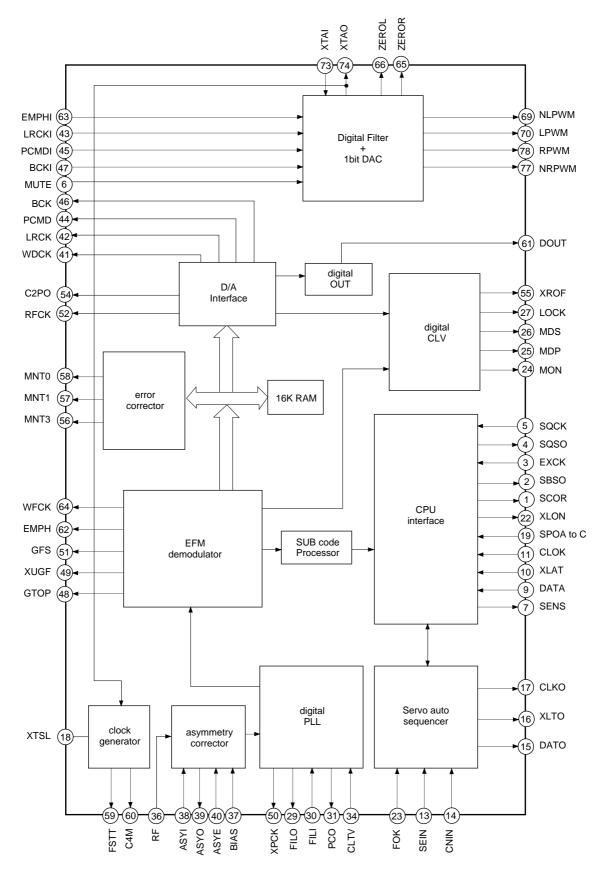

#### **Block Diagram**

Note) The pin numbers are for QFP. Refer to the Pin Description for those of LQFP.

#### **Pin Description**

| Pin No. |    |        |     |                                                                                                                                              |

|---------|----|--------|-----|----------------------------------------------------------------------------------------------------------------------------------------------|

| R       | Q  | Symbol | I/O | Description                                                                                                                                  |

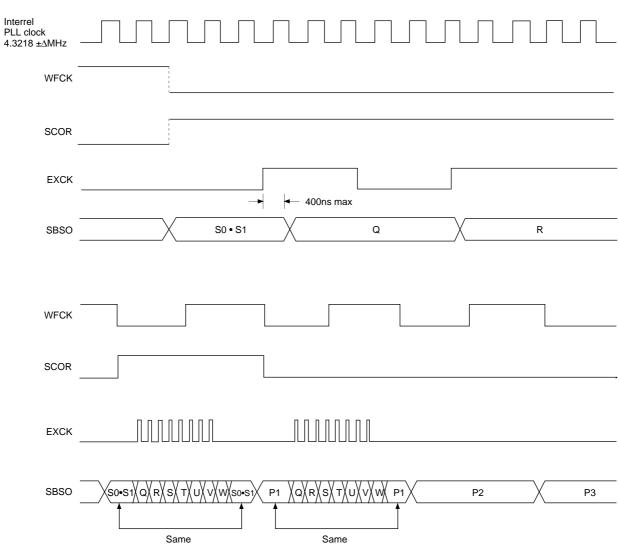

| 79      | 1  | SCOR   | 0   | Outputs a high signal when either subcode sync S0 or S1 is detected.                                                                         |

| 80      | 2  | SBSO   | 0   | Sub P to W serial output.                                                                                                                    |

| 1       | 3  | EXCK   | I   | SBSO readout clock input.                                                                                                                    |

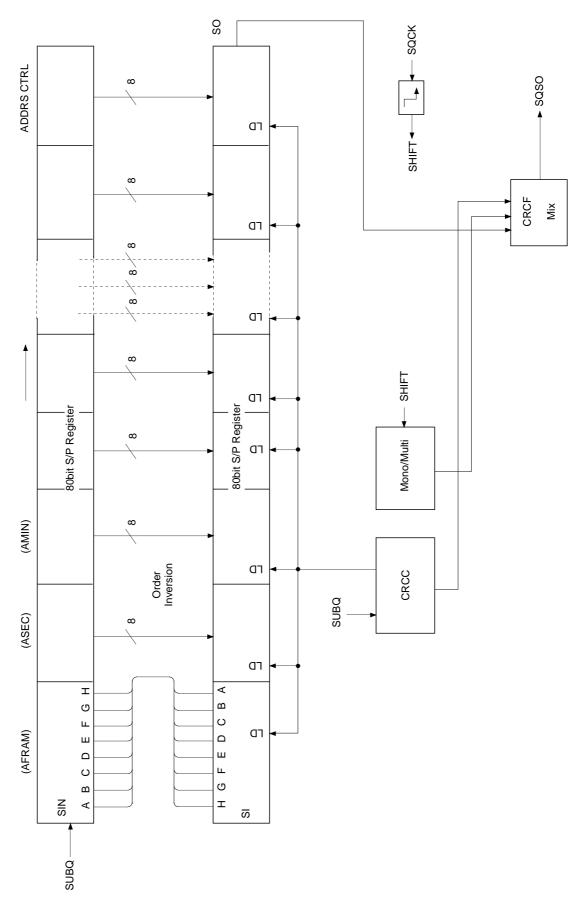

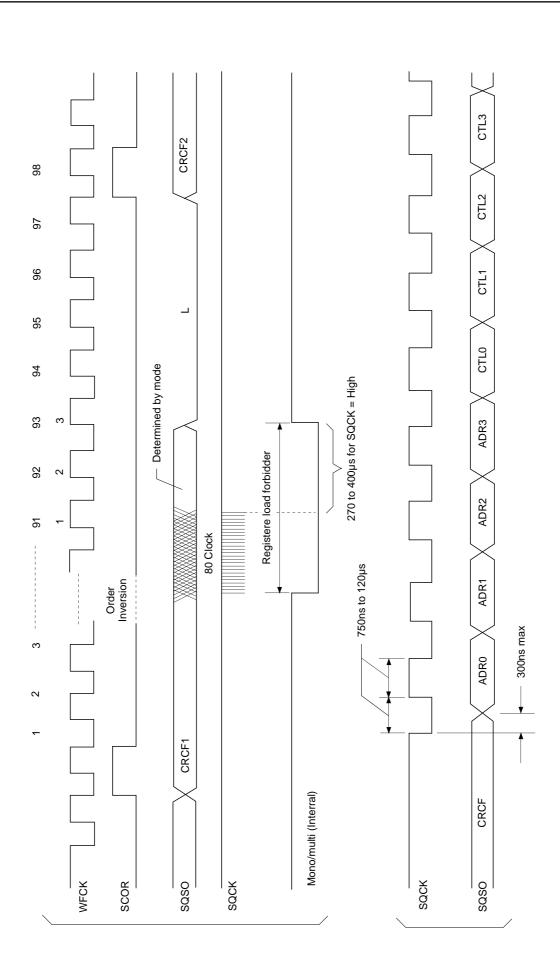

| 2       | 4  | SQSO   | 0   | Sub Q 80-bit serial output.                                                                                                                  |

| 3       | 5  | SQCK   | I   | SQSO readout clock input.                                                                                                                    |

| 4       | 6  | MUTE   | I   | High: mute; low: release                                                                                                                     |

| 5       | 7  | SENS   | 0   | SENS output to CPU.                                                                                                                          |

| 6       | 8  | XRST   | I   | System reset. Reset when low.                                                                                                                |

| 7       | 9  | DATA   | I   | Serial data input from CPU.                                                                                                                  |

| 8       | 10 | XLAT   | I   | Latch input from CPU. Serial data is latched at the falling edge.                                                                            |

| 9       | 11 | CLOK   | I   | Serial data transfer clock input from CPU.                                                                                                   |

| 10      | 12 | Vss    |     | GND.                                                                                                                                         |

| 11      | 13 | SEIN   | I   | Sense input from SSP.                                                                                                                        |

| 12      | 14 | CNIN   | I   | Track jump count signal input.                                                                                                               |

| 13      | 15 | DATO   | 0   | Serial data output to SSP.                                                                                                                   |

| 14      | 16 | XLTO   | 0   | Serial data latch output to SSP. Latched at the falling edge.                                                                                |

| 15      | 17 | CLKO   | 0   | Serial data transfer clock output to SSP.                                                                                                    |

| 16      | 18 | SPOA   | I   | Microcomputer extended interface (input A).                                                                                                  |

| 17      | 19 | SPOB   | I   | Microcomputer extended interface (input B).                                                                                                  |

| 18      | 20 | SPOC   | I   | Microcomputer extended interface (input C).                                                                                                  |

| 19      | 21 | XTSL   | I   | Crystal selection input. Low for 16.9344MHz; high for 33.8688MHz                                                                             |

| 20      | 22 | XLON   | 0   | Microcomputer extended interface (output).                                                                                                   |

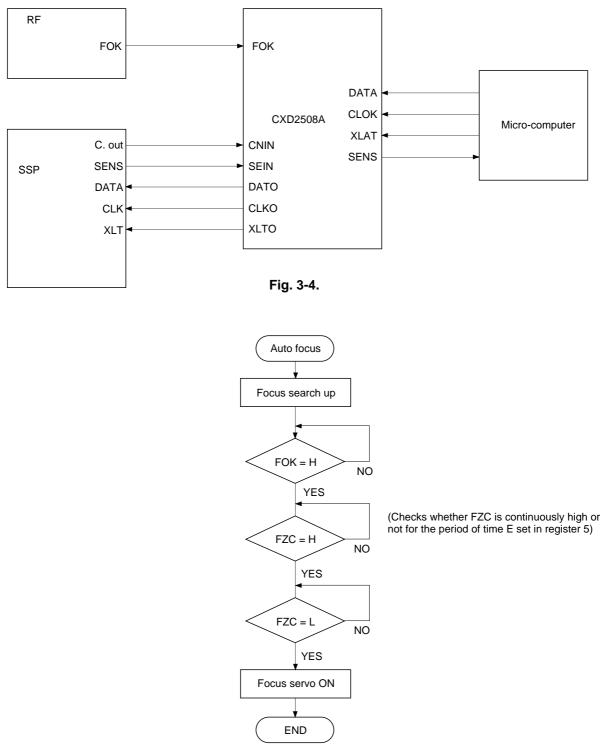

| 21      | 23 | FOK    | I   | Focus OK input. Used for SENS output and the servo auto sequencer.                                                                           |

| 22      | 24 | MON    | 0   | Spindle motor on/off control output.                                                                                                         |

| 23      | 25 | MDP    | 0   | Spindle motor servo control.                                                                                                                 |

| 24      | 26 | MDS    | 0   | Spindle motor servo control.                                                                                                                 |

| 25      | 27 | LOCK   | 0   | GFS is sampled at 460Hz; when GFS is high, this pin outputs a high signal.<br>If GFS is low eight consecutive samples, this pin outputs low. |

| 26      | 28 | TEST   | I   | TEST pin. Normally GND.                                                                                                                      |

| 27      | 29 | FILO   | 0   | Master PLL (slave = digital PLL) filter output.                                                                                              |

| 28      | 30 | FILI   | I   | Master PLL filter input.                                                                                                                     |

| 29      | 31 | PCO    | 0   | Master PLL charge pump output.                                                                                                               |

| 30      | 32 | Vdd    |     | Digital power supply for DSP.                                                                                                                |

| 31      | 33 | AVss1  |     | Analog GND for DSP.                                                                                                                          |

| 32      | 34 | CLTV   | I   | Master PLL VCO control voltage input.                                                                                                        |

| 33 | Q  | Symbol | I/O             |                                                                                         |  |  |  |

|----|----|--------|-----------------|-----------------------------------------------------------------------------------------|--|--|--|

|    |    |        | I/O Description |                                                                                         |  |  |  |

| 34 | 35 | AVDD1  |                 | Analog power supply for DSP.                                                            |  |  |  |

| 1  | 36 | RF     | I               | EFM signal input.                                                                       |  |  |  |

| 35 | 37 | BIAS   | I               | Constant current input of asymmetry compensation circuit.                               |  |  |  |

| 36 | 38 | ASYI   | I               | Comparator voltage input of asymmetry compensation circuit.                             |  |  |  |

| 37 | 39 | ASYO   | 0               | EFM full-swing output (low = Vss, high = VDD).                                          |  |  |  |

| 38 | 40 | ASYE   | I               | Low: asymmetry compensation off; high: asymmetry compensation on.                       |  |  |  |

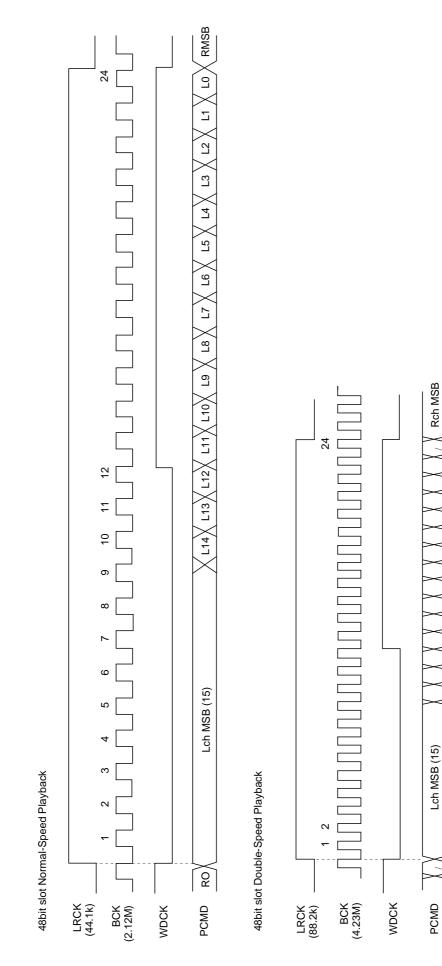

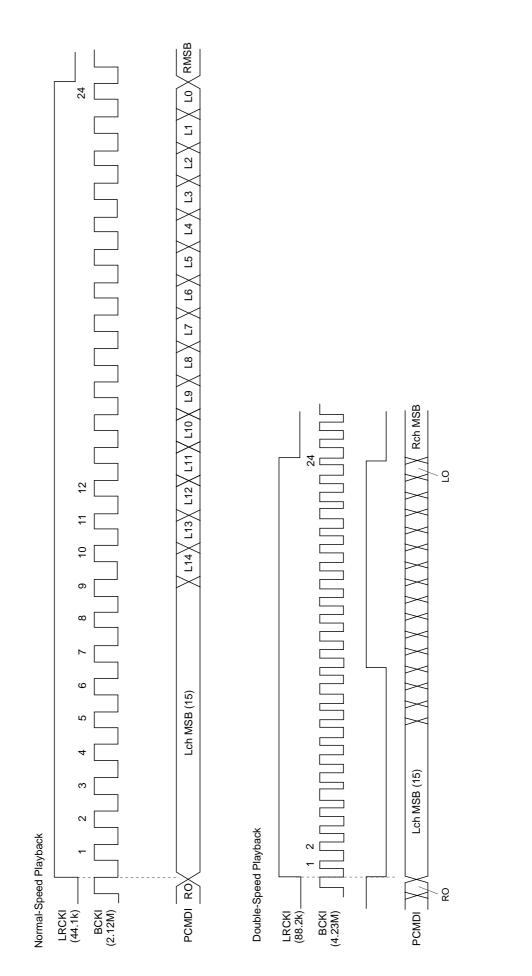

| 39 | 41 | WDCK   | 0               | D/A interface for 48-bit slot. Word clock (2Fs).                                        |  |  |  |

| 40 | 42 | LRCK   | 0               | D/A interface for 48-bit slot. LR clock (Fs).                                           |  |  |  |

| 41 | 43 | LRCKI  | I               | LR clock input for DAC. (48-bit slot)                                                   |  |  |  |

| 42 | 44 | PCMD   | 0               | D/A interface. Serial data (two's complement, MSB first).                               |  |  |  |

| 43 | 45 | PCMDI  | I               | Audio data input for DAC. (48-bit slot)                                                 |  |  |  |

| 44 | 46 | BCK    | 0               | D/A interface. Bit clock.                                                               |  |  |  |

| 45 | 47 | BCKI   | I               | Bit clock input for DAC. (48-bit slot)                                                  |  |  |  |

| 46 | 48 | GTOP   | 0               | GTOP output.                                                                            |  |  |  |

| 47 | 49 | XUGF   | 0               | XUGF output.                                                                            |  |  |  |

| 48 | 50 | XPCK   | 0               | XPLCK output.                                                                           |  |  |  |

| 49 | 51 | GFS    | 0               | GFS output.                                                                             |  |  |  |

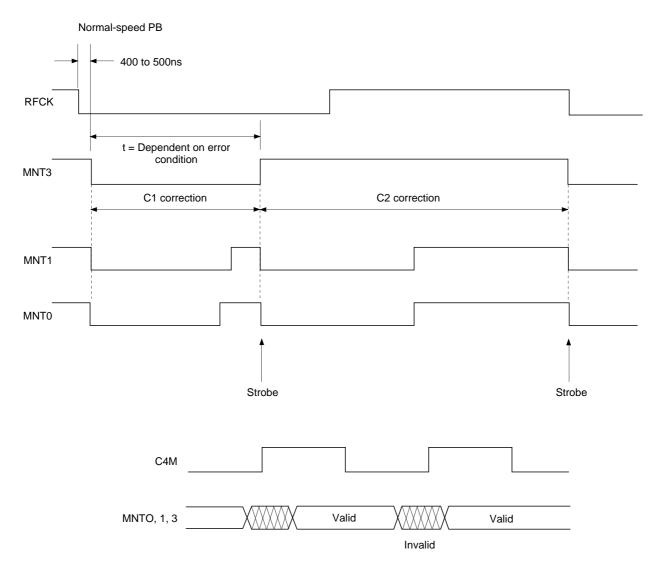

| 50 | 52 | RFCK   | 0               | RFCK output.                                                                            |  |  |  |

| 51 | 53 | Vss    |                 | GND.                                                                                    |  |  |  |

| 52 | 54 | C2PO   | 0               | C2PO output.                                                                            |  |  |  |

| 53 | 55 | XROF   | 0               | XRAOF output.                                                                           |  |  |  |

| 54 | 56 | MNT3   | 0               | MNT3 output.                                                                            |  |  |  |

| 55 | 57 | MNT1   | 0               | MNT1 output.                                                                            |  |  |  |

| 56 | 58 | MNT0   | 0               | MNT0 output.                                                                            |  |  |  |

| 57 | 59 | FSTT   | 0               | 2/3 frequency-divider output for Pins 73 and 74.                                        |  |  |  |

| 58 | 60 | C4M    | 0               | 4.2336MHz output.                                                                       |  |  |  |

| 59 | 61 | DOUT   | 0               | Digital Out output.                                                                     |  |  |  |

| 60 | 62 | EMPH   | 0               | Outputs high signal when the playback disc has emphasis, low signal when no emphasis.   |  |  |  |

| 61 | 63 | EMPHI  | I               | DAC de-emphasis on/off. High: on; low: off.                                             |  |  |  |

| 62 | 64 | WFCK   | 0               | WFCK (write frame clock) output.                                                        |  |  |  |

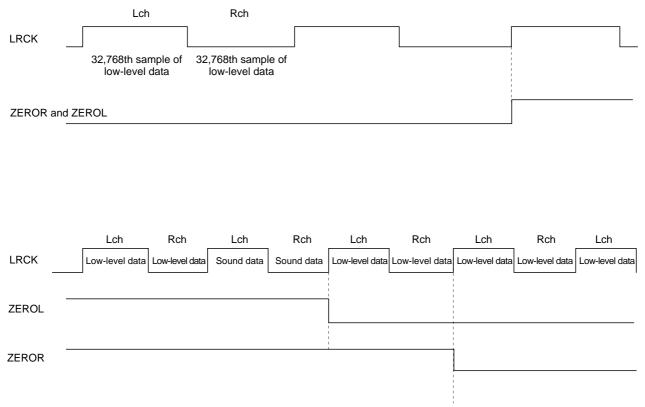

| 63 | 65 | ZEROL  | 0               | No-sound data detection output; high when no sound data is detected.<br>(Left channel)  |  |  |  |

| 64 | 66 | ZEROR  | 0               | No-sound data detection output; high when no sound data is detected.<br>(Right channel) |  |  |  |

| 65 | 67 | DTS1   | I               | Test pin 1 for DAC; normally low.                                                       |  |  |  |

| 66 | 68 | Vdd    |                 | Digital power supply for DAC.                                                           |  |  |  |

| Pin | Pin No. |        | I/O | Description                                    |

|-----|---------|--------|-----|------------------------------------------------|

| R   | Q       | Symbol | 1/0 | Description                                    |

| 67  | 69      | NLPWM  | 0   | Left channel PWM output. (Reverse phase)       |

| 68  | 70      | LPWM   | 0   | Left channel PWM output. (Forward phase)       |

| 69  | 71      | AVdd2  |     | Power supply for PWM driver.                   |

| 70  | 72      | AVdd3  |     | Power supply for crystal.                      |

| 71  | 73      | XTAI   | I   | 33.8688MHz crystal oscillation circuit input.  |

| 72  | 74      | XTAO   | 0   | 33.8688MHz crystal oscillation circuit output. |

| 73  | 75      | AVss3  |     | GND for crystal.                               |

| 74  | 76      | AVss2  |     | GND for PWM driver.                            |

| 75  | 77      | NRPWM  | 0   | Right channel PWM output. (Reverse phase)      |

| 76  | 78      | RPWM   | 0   | Right channel PWM output. (Forward phase)      |

| 77  | 79      | DTS2   | I   | DAC test pin 2; normally low.                  |

| 78  | 80      | DTS3   | I   | DAC test pin 3; normally low.                  |

#### Note)

• PCMD is an MSB first, two's complement output.

- GTOP is used to monitor the frame sync protection status. (High: sync protection window released.)

- XUGF is the negative pulse for the frame sync derived from the EFM signal. It is the signal before sync protection.

- XPLCK is the inverse of the EFM PLL clock. The PLL is designed so that the falling edge of XPLCK and the EFM signal transition point coincide.

- GFS goes high when the frame sync and the insertion protection timing match.

- RFCK is derived with the crystal accuracy. This signal has a cycle of 136µ.

- C2PO represents the data error status.

- XRAOF is generated when the 16K RAM exceeds the ±4F jitter margin.

## Electrical Characteristics

| Elec               | trical Characteristics    |         |                    |                   |            |            |          |                        |  |

|--------------------|---------------------------|---------|--------------------|-------------------|------------|------------|----------|------------------------|--|

| DC                 | Characteristics           |         | (VDD = AVDD = 5.0) | V <b>±</b> 5%, Vs | s = AVss = | • 0V, Topr | = -20 to | +75°C) <sup>NOTE</sup> |  |

|                    | Item                      |         | Conditions         | Min.              | Тур.       | Max.       | Unit     | Applicable<br>pins     |  |

| Input voltage (1)  | High level input voltage  | Vін (1) |                    | 0.7Vdd            |            |            | V        | *1                     |  |

| Input vo           | Low level input voltage   | Vı∟ (1) |                    |                   |            | 0.3Vdd     | V        | -<br>                  |  |

| Input voltage (2)  | High level input voltage  | Vін (2) | Schmitt input      | 0.8Vdd            |            |            | V        | *2                     |  |

| Input vo           | Low level input voltage   | Vı∟ (2) |                    |                   |            | 0.2Vdd     | V        |                        |  |

| Input voltage (3)  | Input voltage             | Vin (3) | Analog input       | Vss               |            | Vdd        | V        | *3                     |  |

| Output voltage (1) | High level output voltage | Vон (1) | Іон = —4mA         | Vdd-0.8           |            | Vdd        | V        | *4                     |  |

| Dutput v           | Low level output voltage  | Vol (1) | IoL = 4mA          | 0                 |            | 0.4        | V        |                        |  |

| oltage (*                                                                 | High level output<br>voltage | Vон (1) | Іон = -4mA           | Vdd-0.8 |  | Vdd | V  | *4         |  |

|---------------------------------------------------------------------------|------------------------------|---------|----------------------|---------|--|-----|----|------------|--|

| Output voltage (4) Output voltage (3) Output voltage (2) Output voltage ( | Low level output voltage     | Vol (1) | IoL = 4mA            | 0       |  | 0.4 | V  |            |  |

| oltage (2)                                                                | High level output<br>voltage | Vон (2) | Іон = –2mA           | Vdd-0.8 |  | Vdd | V  | *5         |  |

| Output ve                                                                 | Low level output voltage     | Vol (2) | IoL = 4mA            | 0       |  | 0.4 | V  |            |  |

| oltage (3)                                                                | High level output voltage    | Vон (3) | Іон = -0.28mA        | Vdd-0.5 |  | Vdd | V  | *6         |  |

| Output ve                                                                 | Low level output voltage     | Vol (3) | lo∟ = 0.36mA         | 0       |  | 0.4 | V  |            |  |

| oltage (4)                                                                | High level output voltage    | Vон (4) | Іон = –10mA          | Vdd-0.4 |  | Vdd | V  | *7         |  |

| Output vo                                                                 | Low level output voltage     | Vol (4) | IoL = 10mA           | 0       |  | 0.4 | V  |            |  |

| Inp                                                                       | ut leak current              | lu      | $V_{I} = 0$ to 5.25V |         |  | ±5  | μA | *1, *2, *3 |  |

| Tri-state pin output leak current                                         |                              | Ilo     | Vo = 0 to 5.25V      |         |  | ±5  | μA | *8         |  |

| -                                                                         |                              |         |                      |         |  |     |    |            |  |

#### Applicable pins

\*1 XTSL, DATA, XLAT, PCMDI, EMPHI, DTS1, DTS2, DTS3, SPOA, SPOB, SPOC

\*2 CLOK, XRST, EXCK, SQCK, MUTE, FOK, SEIN, CNIN, ASYE, LRCKI, BCKI

\*3 CLTV, FILI, RF, BIAS, ASYI

- \*4 MDP, PCO

- \*5 ASYO, DOUT, FSTT, C4M, SBSO, SQSO, SCOR, EMPH, MON, LOCK, WDCK, DATO, CLKO, XLTO, SENS, MDS, LRCK, WFCK, PCMD, BCK, GTOP, XUGF, XPCK, GFS, RFCK, XROF, MNT0, MNT1, MNT3, ZEROL, ZEROR

- \*6 FILO

- \*7 LPWM, NLPWM, RPWM, NRPWM

- \*8 SENS, MDS, MDP Note) "AVDD" refers to AVDD1, AVDD2, and AVDD3. In addition, "AVss" refers to AVss1, AVss2, and AVss3.

## AC Characteristics

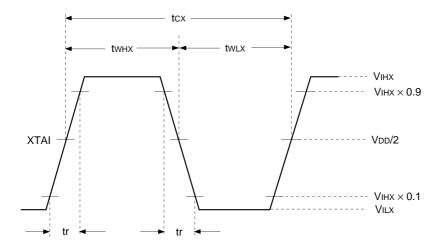

### 1) XTAI pin

(1) When using self-oscillation (Topr = -20 to  $+75^{\circ}$ C, VDD = AVDD =  $5.0V \pm 5\%$ )

| Item                  | Symbol | Min. | Тур. | Max. | Unit |

|-----------------------|--------|------|------|------|------|

| Oscillation frequency | fмах   | 15   |      | 34   | MHz  |

#### (2) When inputting pulses to XTAI

| $(Topr = -20 \text{ to } +75^{\circ}C, VDD = AVDD = 5.0V \pm 5^{\circ}C$ |        |           |      |       |      |  |

|--------------------------------------------------------------------------|--------|-----------|------|-------|------|--|

| Item                                                                     | Symbol | Min.      | Тур. | Max.  | Unit |  |

| High level<br>pulse width                                                | twнx   | 13        |      | 500   | ns   |  |

| Low level<br>pulse width                                                 | tw∟x   | 13        |      | 500   | ns   |  |

| Pulse cycle                                                              | tск    | 26        |      | 1,000 | ns   |  |

| Input high level                                                         | Vінх   | Vdd - 1.0 |      |       | V    |  |

| Input low level                                                          | VILX   |           |      | 0.8   | V    |  |

| Rise time,<br>fall time                                                  | tr, tr |           |      | 10    | ns   |  |

(3) When inputting sine waves to XTAI via a capacitor

| Item            | Symbol | Min. | Тур. | Max.      | Unit |

|-----------------|--------|------|------|-----------|------|

| Input amplitude | V1     | 2.0  |      | Vdd + 0.3 | Vp-p |

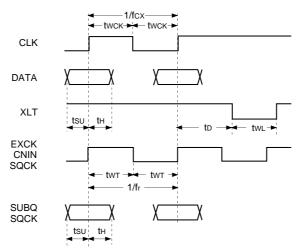

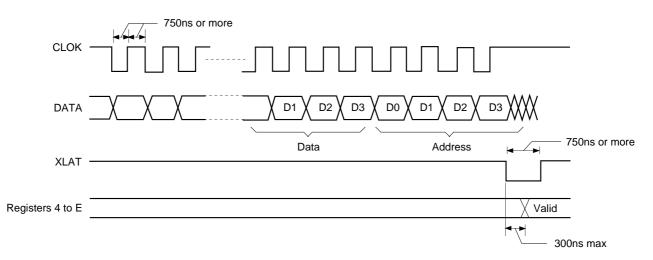

#### 2) CLOK, DATA, XLAT, CNIN, SQCK EXCK pins

| $(V_{DD} = AV_{DD} = 5.0V \pm 5\%, V_{SS} = AV_{SS} = 0V, T_{OPT} = -20 \text{ to } +75^{\circ}\text{C})$ |              |      |      |       |      |  |  |  |

|-----------------------------------------------------------------------------------------------------------|--------------|------|------|-------|------|--|--|--|

| ltem                                                                                                      | Symbol       | Min. | Тур. | Max.  | Unit |  |  |  |

| Clock frequency                                                                                           | fcк          |      |      | 0.65  | MHz  |  |  |  |

| Clock pulse width                                                                                         | <b>t</b> wcк | 750  |      |       | ns   |  |  |  |

| Setup time                                                                                                | <b>t</b> su  | 300  |      |       | ns   |  |  |  |

| Hold time                                                                                                 | tн           | 300  |      |       | ns   |  |  |  |

| Delay time                                                                                                | t⊳           | 300  |      |       | ns   |  |  |  |

| Latch pulse width                                                                                         | tw∟          | 750  |      |       | ns   |  |  |  |

| EXCK SQCK frequency                                                                                       | fτ           |      |      | 0.65* | MHz  |  |  |  |

| EXCK SQCK pulse width                                                                                     | fwт          | 750* |      |       | ns   |  |  |  |

\* In pseudo double-speed playback mode, when SL0 = SL1 = 1, the maximum operating frequency for SQCK is 300kHz and the minimum pulse width is 1.5µs.

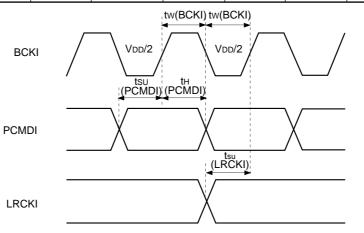

| 3) BCKI, LRCI | (I, and PCMDI) | ins (Vdd = | = AVDD = 5.0 | / ± 5%, V | /ss = AVss = | 0V, Topr | = −20 to +75°C) |

|---------------|----------------|------------|--------------|-----------|--------------|----------|-----------------|

|---------------|----------------|------------|--------------|-----------|--------------|----------|-----------------|

| -                   |             |            |      | -    | -    |      |

|---------------------|-------------|------------|------|------|------|------|

| Item                | Symbol      | Conditions | Min. | Тур. | Max. | Unit |

| BCK pulse width     | tw          |            | 94   | 118  | 141  | nsec |

| DATAL, R setup time | <b>t</b> su |            | 18   |      |      | nsec |

| DATAL, R hold time  | tн          |            | 18   |      |      | nsec |

| LRCK setup time     | <b>t</b> su |            | 18   |      |      | nsec |

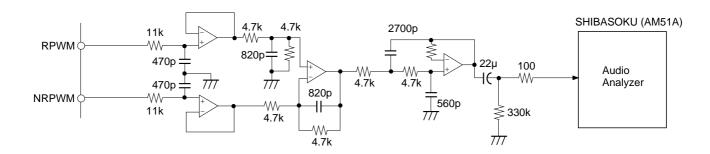

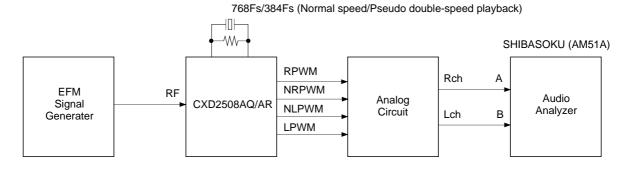

| 1-bit DAC Block Analog | Characteristics |

|------------------------|-----------------|

|------------------------|-----------------|

$(VDD = AVDD = 5.0V, VSS = AVSS = 0V, Ta = 25^{\circ}C)$

| Item           | Symbol | Conditions        | Playback mode                | Min. | Тур. | Max.  | Unit |

|----------------|--------|-------------------|------------------------------|------|------|-------|------|

| Total harmonic | THD    | 1kHz,             | Normal speed                 |      |      | 0.015 | %    |

| distortion     |        | 0dB data          | Pseudo double-speed playback |      |      | 0.025 | 70   |

| S/N ratio      | S/N    | 1kHz,<br>0dB data | Normal speed                 | 87   |      |       | dB   |

| 3/11/14/10     | 5/11   |                   | Pseudo double-speed playback | 83   |      |       | UD   |

For both items, Fs=44.1kHz

The circuits for measuring the total harmonic distortion and S/N ratio are shown below.

#### **Analog LPF Circuit**

#### **Block Diagram for Measuring Analog Characteristics**

#### **Description of Functions**

#### **1. CPU Interface and Instructions**

#### CPU interface

This interface uses DATA, CLOK, and XLAT to set the modes. The interface timing chart is shown below.

• Information on each address and the data is provided in Table 1-1.

• The internal registers are initialized by a reset when XRST = 0; the initialization data is shown in Table 1-2. **Note)** When XLAT is low, EXCK and SQCK must be set high.

| Ð  |

|----|

| đ  |

| Ê  |

| p  |

| an |

| ε  |

| Ĕ  |

| ပိ |

| -  |

| lister<br>me | Command                                       |    | Address | ess |   |                                      | Data 1                      | 1            |              |      | Data 2 | 12   |             |     | Data 3 | e   |     |     | Data 4 | a 4 |              |

|--------------|-----------------------------------------------|----|---------|-----|---|--------------------------------------|-----------------------------|--------------|--------------|------|--------|------|-------------|-----|--------|-----|-----|-----|--------|-----|--------------|

| вn<br>Reg    |                                               | D3 | D2      | 5   | B | D3                                   | D2                          | 5            | 8            | D3   | D2     | 5    | DO          | D3  | D2     | 5   | 8   | D3  | D2     | 5   | DO           |

| 4            | Auto sequence                                 | 0  | -       | 0   | 0 | AS3                                  | AS2                         | AS1          | ASO          |      |        |      | 1           |     |        |     | 1   | I   | 1      | 1   | I            |

| ų            | Blind (A, E), Overflow (C)                    | c  | -       | c   | - | 0.18ms                               | 0.18ms 0.09ms 0.05ms 0.02ms | ).05ms (     | 0.02ms       |      |        |      |             |     |        |     |     |     |        |     |              |

| ה<br>ה       | Brake (B)                                     | >  | -       | 5   | - | 0.36ms                               | 0.36ms 0.18ms 0.09ms 0.05ms | ) Sm90.0     | 0.05ms       |      |        |      |             |     |        |     |     |     |        |     |              |

| 9            | KICK (D)                                      | 0  | -       | -   | 0 | 11.6ms                               | 5.8ms                       | 2.9ms        | 1.45ms       |      |        |      | 1           |     |        |     | 1   | I   | Ι      | 1   | I            |

| 2            | Auto sequence (N)<br>track jump count setting | 0  | -       | -   | - | 32768                                | 16384                       | 8192         | 4096         | 2048 | 1024   | 512  | 256         | 128 | 64     | 32  | 16  | ω   | 4      | N   | <del>.</del> |

| œ            | MODE specification                            | ~  | 0       | 0   | 0 | P<br>M<br>M<br>M<br>M<br>M<br>M<br>M | DOUT<br>MUTE 0              | DOUT WSEL    | WSEL         |      |        |      | VCO<br>SEL  |     |        |     |     | 1   | 1      | 1   |              |

| റ            | Function specification                        | -  | 0       | 0   | - | 0                                    | DSPB<br>ON/OFF              | 0            | 0            | 0    | 0      | 0    | FSTT<br>SEL |     |        |     | 1   | 1   | 1      | 1   | I            |

| A            | Audio CTRL                                    | -  | 0       | -   | 0 | 0                                    | 0                           | Mute         | АТТ          | I    |        | DADS | I           |     | AD6    | AD5 | AD4 | AD3 | AD2    | AD1 | AD0          |

| В            | Serial bus CTRL                               | ~  | 0       | -   | ~ | SL 1                                 | SL 0 0                      | CPUSR        | 0            | 1    |        |      | I           |     |        |     | 1   |     | I      | I   | I            |

| ပ            | Servo coefficient setting                     | -  | -       | 0   | 0 | Gain<br>MDP1                         | Gain<br>MDP0                | Gain<br>MDS1 | Gain<br>MDS0 | 1    | 1      | 1    | 1           |     |        |     | 1   | 1   | I      | 1   | I            |

| ۵            | CLV CTRL                                      | -  | -       | 0   | - | DCLV<br>PWMmod                       | ТВ                          | ТР           | CLVS<br>Gain | I    | I      | I    | I           |     |        | I   | I   | Ι   | Ι      | Ι   | I            |

| ш            | CLV mode                                      | ٢  | -       | 1   | 0 | CM3                                  | CM2                         | CM1          | CMO          | I    | I      | I    | I           |     | I      | I   | I   | I   | I      | I   | I            |

| ш            | TEST mode                                     | -  | -       | -   | - |                                      | Don't Use                   | Use          |              |      |        |      | I           |     |        |     | I   |     | I      |     | I            |

Table 1-1

**Reset Initialization**

| Blind (A, I       5     Blind (A, I       5     Blind (A, I       6     KICK (D)       7     Auto sequencia       7     Auto sequencia       8     MODE spoec       9     Function i       9     Function i       10     C       10     CLV CTR       10     CLV CTR       11     CLV modincia       12     CLV modincia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | reteir | aister<br>gister | Command                                       |    | Address | ess          |              |    | Data 1      | <del>.</del> |   |    | Data 2 | 2 |                |    | Data 3 | 13 |   |    | Data 4 | 4 |    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------------|-----------------------------------------------|----|---------|--------------|--------------|----|-------------|--------------|---|----|--------|---|----------------|----|--------|----|---|----|--------|---|----|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ъя     | ยน<br>วัคม       |                                               | D3 | D2      | 5            | DO           | D3 | D2          | Б            | ß | D3 | D2     | Б | DO             | D3 | D2     | 5  | 8 | D3 | D2     | 5 | DO |

| $ \begin{array}{[[] [] [] [] [] [] [] [] [] [] [] [] [] $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |        | 4                | Auto sequence                                 | 0  | -       | 0            | 0            | 0  | 0           | 0            | 0 | I  | I      | I | 1              | I  | I      | I  | I |    | I      | I | I  |

| Definition       Definition </td <th></th> <td>ų</td> <td>Blind (A, E), Overflow (C)</td> <td>c</td> <td>-</td> <td>c</td> <td>-</td> <td>6</td> <td>-</td> <td>6</td> <td>-</td> <td></td> |        | ų                | Blind (A, E), Overflow (C)                    | c  | -       | c            | -            | 6  | -           | 6            | - |    |        |   |                |    |        |    |   |    |        |   |    |

| 6         KCK (D)         0         1         1         0         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1 <th1< th="">         1<!--</td--><th></th><td>ი</td><td>Brake (B)</td><td>5</td><td>_</td><td>5</td><td>-</td><td>5</td><td><del></del></td><td>5</td><td>-</td><td> </td><td> </td><td></td></th1<>                                                                                                                                                                                                                                                                |        | ი                | Brake (B)                                     | 5  | _       | 5            | -            | 5  | <del></del> | 5            | - |    |        |   |                |    |        |    |   |    |        |   |    |

| 7         Auto sequence (N)         0         1         1         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        | 9                | KICK (D)                                      | 0  | -       | -            | 0            | 0  | -           | -            | - | 1  | 1      | 1 | 1              | 1  | 1      | 1  | 1 |    | I      | 1 | I  |

| MODE specification         1         0         0         0         1         0         1         0         1         0         1         0         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |        | 7                | Auto sequence (N)<br>track jump count setting | 0  | ~       | -            | <del>.</del> | 0  | 0           | 0            | 0 | 0  | 0      | 0 | <del>, -</del> | 0  | 0      | 0  | 0 | 0  | 0      | 0 | 0  |

| 9       Function specification       1       0       0       0       0       0       0       0       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1 <th>I</th> <td>ø</td> <td>MODE specification</td> <td>-</td> <td>0</td> <td>0</td> <td>0</td> <td>0</td> <td>0</td> <td>-</td> <td>0</td> <td>1</td> <td> </td> <td>1</td> <td>0</td> <td>1</td> <td>1</td> <td>1</td> <td>1</td> <td> </td> <td>1</td> <td>1</td> <td> </td>                                                                                                                                                                                                                                                                                                                                                                          | I      | ø                | MODE specification                            | -  | 0       | 0            | 0            | 0  | 0           | -            | 0 | 1  |        | 1 | 0              | 1  | 1      | 1  | 1 |    | 1      | 1 |    |

| A         Audio CTRL         1         0         1         0         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1 <t></t>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | I      | 6                | Function specification                        | ~  | 0       | 0            | -            | 0  | 0           | 0            | 0 | 0  | 0      | 0 | 0              | 1  | 1      | 1  | 1 |    | 1      | 1 |    |

| B         Serial bus CTRL         1         0         1         1         0         1         1         0         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1 <th1< th=""> <th1< th="">         1</th1<></th1<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        | ۲                | Audio CTRL                                    | -  | 0       | -            | 0            | 0  | 0           | -            | ~ | 1  | 1      | 0 | 1              | 1  | -      | -  | - | -  | ~      | ~ | -  |

| C       Servo coefficient setting       1       1       0       0       1       1       0       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        | в                | Serial bus CTRL                               | -  | 0       | -            | -            | 0  | 0           | ~            | 0 | I  | I      | I | I              | I  | I      | I  | I |    | I      | I | I  |

| CLV CTRL       1       0       1       0       1       1         CLV CTRL       1       0       0       0       0       1       1         CLV CTRL       1       1       0       0       0       0       1       1         CLV mode       1       1       1       0       0       0       0       1       1         CLV mode       1       1       1       0       0       0       0       1       1       1         TEST mode       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        | υ                | Servo coefficient setting                     | -  | -       | 0            | 0            | 0  | ~           | ~            | 0 | I  | I      | I | I              | I  | I      | I  | I |    | I      | I | I  |

| CLV mode       1       1       1       0       0       0       0       1       1         CLV mode       1       1       1       0       0       0       1       1       1         TEST mode       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        | ۵                | CLV CTRL                                      | -  | -       | 0            | -            | 0  | 0           | 0            | 0 | I  | I      | I | I              | I  | I      | I  | I |    | I      | I | I  |

| TEST mode     1     1     1     1     1     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -     -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        | ш                | CLV mode                                      | -  | -       | <del>.</del> | 0            | 0  | 0           | 0            | 0 | I  | I      | I | I              | I  | I      | I  | I |    | I      | I | I  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        | ш                | TEST mode                                     | -  | -       | -            | -            |    | Don't I     | Jse          |   | Ι  | 1      | 1 |                | 1  | 1      | 1  | 1 |    | I      | Ι | Ι  |

Table 1-2

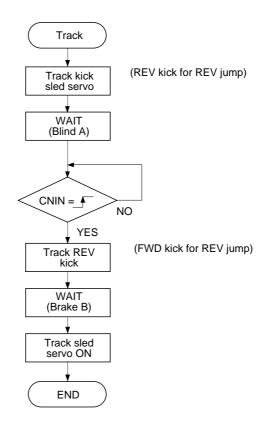

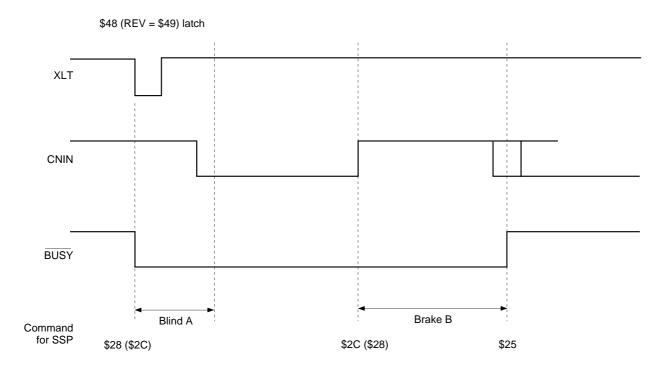

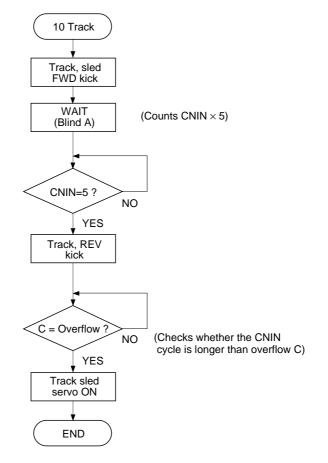

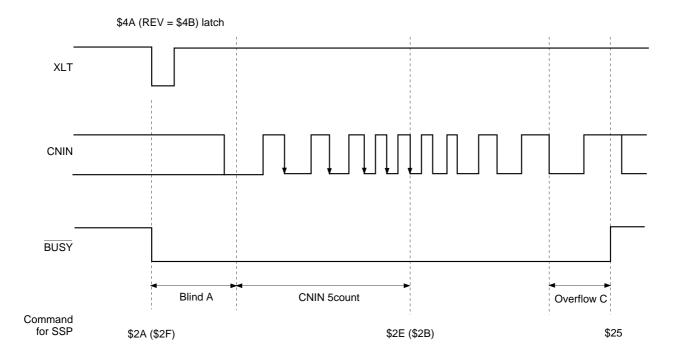

#### 1-1. The meaning of the data for each address is explained below. \$4X commands

| Command       | AS3 | AS2 | AS1      | AS0    |

|---------------|-----|-----|----------|--------|

| CANCEL        | 0   | 0   | 0        | 0      |

| FOCUS-ON      | 0   | 1   | 1        | 1      |

| 1 TRACK JUMP  | 1   | 0   | 0        | RXF    |

| 10 TRACK JUMP | 1   | 0   | 1        | RXF    |

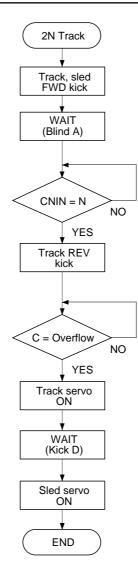

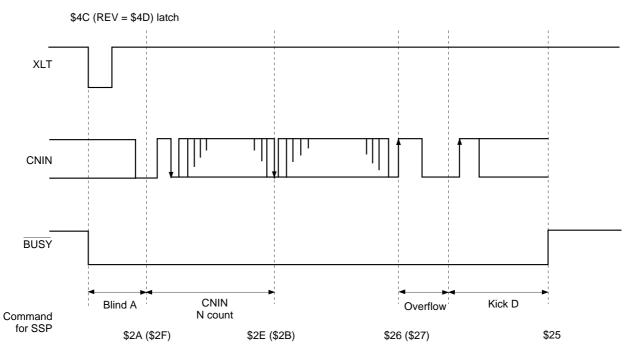

| 2N TRACK JUMP | 1   | 1   | 0        | RXF    |

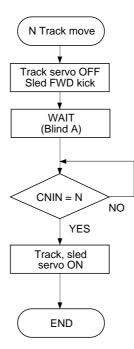

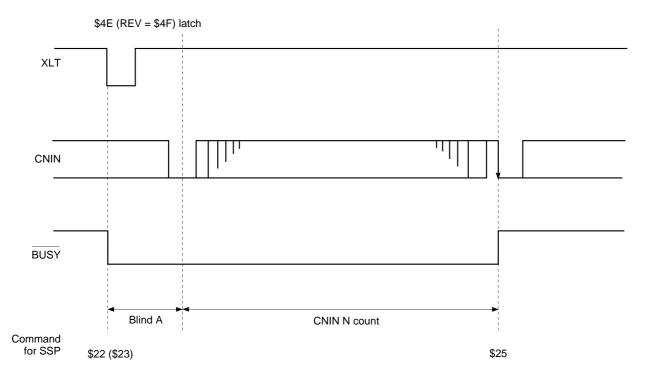

| N TRACK MOVE  | 1   | 1   | 1        | RXF    |

|               |     | R   | XF = 0 F | ORWARD |

RXF = 0 REVERSE

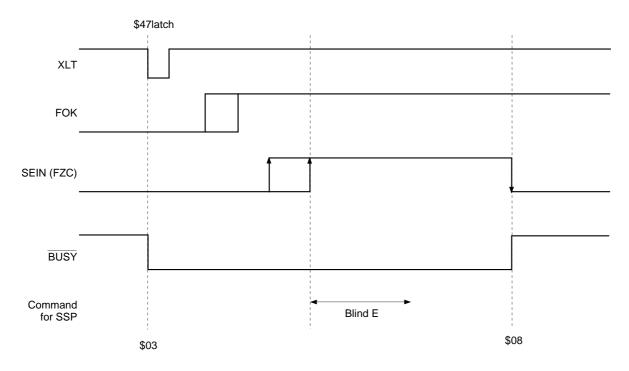

- When the FOCUS-ON command (\$47) is canceled, \$02 is sent and the auto sequence is interrupted.

- When the TRACK JUMP/MOVE commands (\$48 to \$4F) are canceled, \$25 is sent and the auto sequence is interrupted.

#### \$5X commands

Auto sequence timer setting Setting timers: A, E, C, B

| Command                     | D3     | D2     | D1     | D0     |

|-----------------------------|--------|--------|--------|--------|

| Blind (A, E), Over flow (C) | 0.18ms | 0.09ms | 0.05ms | 0.02ms |

| Brake (B)                   | 0.36ms | 0.18ms | 0.09ms | 0.05ms |

Ex.) D2 = D0 = 1, D3 = D1 = 0 (Initial Reset)

A = E = C = 0.11 ms

B = 0.23ms

#### \$6X commands

Auto sequence timer setting

Setting timer: D

| Command  | D3     | D2    | D1    | D0     |

|----------|--------|-------|-------|--------|

| KICK (D) | 11.6ms | 5.8ms | 2.9ms | 1.45ms |

Ex.) D3 = 0, D2 = D1 = D0 = 1 (Initial Reset)

D = 10.15 ms

#### \$7X commands

Auto sequence TRACK JUMP/MOVE count setting (N)

| Command                                 |                 | Dat             | ta 1            |                 |                 | Da              | ta 2           |                |                | Dat            | ta 3           |    |                | Dat            | a 4            |    |

|-----------------------------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|----------------|----------------|----------------|----------------|----------------|----|----------------|----------------|----------------|----|

| Commanu                                 | D3              | D2              | D1              | D0              | D3              | D2              | D1             | D0             | D3             | D2             | D1             | D0 | D3             | D2             | D1             | D0 |

| Auto sequence track jump number setting | 2 <sup>15</sup> | 2 <sup>14</sup> | 2 <sup>13</sup> | 2 <sup>12</sup> | 2 <sup>11</sup> | 2 <sup>10</sup> | 2 <sup>9</sup> | 2 <sup>8</sup> | 2 <sup>7</sup> | 2 <sup>6</sup> | 2 <sup>5</sup> | 24 | 2 <sup>3</sup> | 2 <sup>2</sup> | 2 <sup>1</sup> | 20 |

This command is used to set N when a 2N TRACK JUMP and an N TRACK MOVE are executed for auto sequence.

- The maximum track count is 65,535, but note that with 2N track jumps the maximum track jump count is determined by the mechanical limitations of the optical system.

- The number of track jump is counted according to the signals input from CNIN pin.

#### \$8X commands

| Command               |       | Dat          | ta 1           |      |    | Dat | a 2 |            |

|-----------------------|-------|--------------|----------------|------|----|-----|-----|------------|

| Commanu               | D3    | D2           | D1             | D0   | D3 | D2  | D1  | D0         |

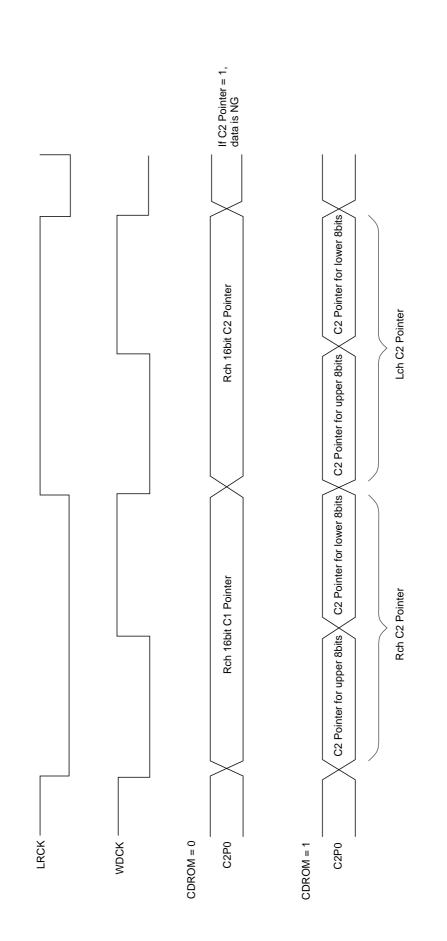

| MODE<br>specification | CDROM | DOUT<br>MUTE | DOUT<br>ON-OFF | WSEL | 0  | 0   | 0   | VCO<br>SEL |

| Command bit | C2PO timing | Processing                                                                    |

|-------------|-------------|-------------------------------------------------------------------------------|

| CDROM = 1   | 1-3         | CDROM mode; average value interpolation and pre-value hold are not performed. |

| CDROM = 0   | 1-3         | Audio mode; average value interpolation and pre-value hold are performed.     |

| Command bit   | Processing                                                              |  |  |

|---------------|-------------------------------------------------------------------------|--|--|

| DOUT MUTE = 1 | Digital Out output is muted. (DA output is not muted.)                  |  |  |

| DOUT MUTE = 0 | When no other mute conditions are set, Digital Out output is not muted. |  |  |

| Command bit     | Processing                                   |  |

|-----------------|----------------------------------------------|--|

| DOUT ON-OFF = 1 | Digital Out is output from the DOUT pin.     |  |

| DOUT ON-OFF = 0 | Digital Out is not output from the DOUT pin. |  |

| Command bit | Sync protection window width | Application                         |

|-------------|------------------------------|-------------------------------------|

| WSEL = 1    | ±26 channel clock*           | Anti-rolling is enhanced.           |

| WSEL = 0    | ±6 channel clock             | Sync window protection is enhanced. |

\* In normal-speed playback, channel clock = 4.3218MHz.

| Command bit | Processing                                 | Application                                                 |  |

|-------------|--------------------------------------------|-------------------------------------------------------------|--|

| VCOSEL = 1  | VCO for double-speed playback is selected. | Double-speed playback or low voltage operation is possible. |  |

| VCOSEL = 0  | VCO for normal-speed playback is selected. | The selection is made for the normal speed playback.        |  |

## \$9X commands

| Command                    | Data 1 |                |    |    | Data 2 |    |    |             |

|----------------------------|--------|----------------|----|----|--------|----|----|-------------|

| Command                    | D3     | D2             | D1 | D0 | D3     | D2 | D1 | D0          |

| Function<br>specifications | 0      | DSPB<br>ON-OFF | 0  | 0  | 0      | 0  | 0  | FSTT<br>SEL |

| Command bit | Processing            |

|-------------|-----------------------|

| DSPB = 0    | Normal-speed playback |

| DSPB = 1    | Double-speed playback |

| Command bit |                                                                       |

|-------------|-----------------------------------------------------------------------|

| FSTTSEL = 0 | The clock with two-thirds frequency of crystal is output to FSTT pin. |

| FSTTSEL = 1 | The clock with the sixth frequency of crystal is output to FSTT pin.  |

#### **\$AX commands**

| Command    | Data 1 |    |      | Data 2 |    |    |      |    |

|------------|--------|----|------|--------|----|----|------|----|

| Command    | D3     | D2 | D1   | D0     | D3 | D2 | D1   | D0 |

| Audio CTRL | 0      | 0  | Mute | ATT    |    |    | DADS | _  |

| Command bit | Meaning                             |

|-------------|-------------------------------------|

| Mute = 0    | Mute off.                           |

| Mute = 1    | Mute on. 0 data is output from DSP. |

| Command bit | Meaning          |

|-------------|------------------|

| ATT = 0     | Attenuation off. |

| ATT = 1     | -12dB            |

| Command bit | Processing                          |

|-------------|-------------------------------------|

| DADS = 0    | Normal-speed playback for DAC block |

| DADS = 1    | Double-speed playback for DAC block |

In the case of using the crystal of 768Fs (Fs = 44.1kHz)

#### **Digital Attenuation**

The audio output level from DAC can be attenuated by setting AD6 to AC0 of register A. (with a built-in primary noise shaper)

| Command    |     | Data 3 |     |     | Dat | a 4 |     |

|------------|-----|--------|-----|-----|-----|-----|-----|

| Command    | D2  | D1     | D0  | D3  | D2  | D1  | D0  |

| Audio CTRL | AD6 | AD5    | AD4 | AD3 | AD2 | AD1 | AD0 |

| Command bit<br>AD6 to AD0 | Audio output |

|---------------------------|--------------|

| 7F (H)                    | 0dB          |

| 7E (H)                    | -0.13dB      |

| to                        | to           |

| 01 (H)                    | –42.144dB    |

| 00 (H)                    | -∞           |

The attenuation data consists of seven bits (AD6 to AC0), and 127 settings are possible.

Audio output from 01 (H) to 7E (H) is determined according to the following formula:

Audio output = 20 log (

$$\frac{\text{attenuation data}}{128}$$

) dB

Ex.) When the attenuation data is 7A (H)

Audio output=20 log  $(\frac{122}{128})$  dB = -0.417dB

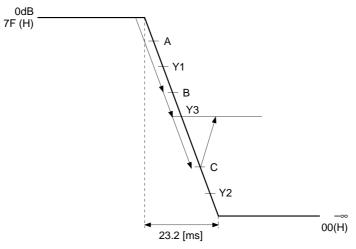

#### Soft Mute

With soft mute function, when the attenuation data goes from 7F (H) (0dB) to 00 (H) ( $-\infty$ ) or vice versa, muting is turned on/off with a muting time of 1024/Fs [s] = 23.2 [ms] (Fs = 44.1kHz).

#### Attenuation Operation

Assume attenuation data X1, X2, and X3, where X1 > X3 > X2, and audio output Y1, Y2, and Y3, where Y1 > Y3 > Y2. First, assume X1 is transferred and then X2 is transferred. If X2 is transferred before Y1 is reached (state "A" in the diagram), then the value continues approaching Y2. Next, if X3 is transferred before Y2 is reached (either state "B" or "C" in the diagram), the value begins approaching Y3 from the current value at that point.

#### **\$BX commands**

| Command         | D3  | D2  | D1    | D0 |

|-----------------|-----|-----|-------|----|

| Serial bus CTRL | SL1 | SL0 | CPUSR | 0  |

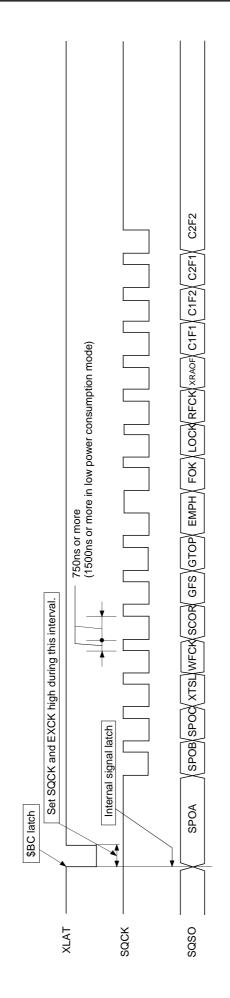

This command switches the method of interfacing with the CPU. With the CDL500 series, the number of signal lines between the CPU and the DSP can be reduced in comparison with the CDL40 series. Also, the error rate can be measured with the CPU.

| Comm | and bits | Processing                                                                                                             |  |  |

|------|----------|------------------------------------------------------------------------------------------------------------------------|--|--|

| SL1  | SL0      | - Flucessing                                                                                                           |  |  |

| 0    | 0        | Same interface mode as the CDL40 series.                                                                               |  |  |

| 0    | 1        | SBSO is output from SQSO pin. In other words, subcodes P to W are read out from SQSO. Input the readout clock to SQCK. |  |  |

| 1    | 0        | SENS is output from SQSO pin.                                                                                          |  |  |

| 1    | 1        | Each output signal is output from SQSO pin.<br>Input the readout clock to SQCK.<br>(See the Timing Chart 1-2.)         |  |  |

| Command bits | Processing        |

|--------------|-------------------|

| CPUSR = 1    | XLON pin is high. |

| CPUSR = 0    | XLON pin is low.  |

#### **\$CX commands**

| Command                   | D3           | D2           | D1           | D0           |

|---------------------------|--------------|--------------|--------------|--------------|

| Servo coefficient setting | Gain<br>MDP1 | Gain<br>MDP0 | Gain<br>MDS1 | Gain<br>MDS0 |

| CLV CTRL (\$DX)           |              |              |              | Gain<br>CLVS |

## CLVS mode gain setting: GCLVS

| Gain<br>MDS1 | Gain<br>MDS0 | Gain<br>CLVS | GCLVS |

|--------------|--------------|--------------|-------|

| 0            | 0            | 0            | –12dB |

| 0            | 0            | 1            | –6dB  |

| 0            | 1            | 0            | –6dB  |

| 0            | 1            | 1            | 0dB   |

| 1            | 0            | 0            | 0dB   |

| 1            | 0            | 1            | +6dB  |

## • CLVP mode gain setting: GMDP, GMDS

| Gain<br>MDP1 | Gain<br>MDP0 | GMDP |

|--------------|--------------|------|

| 0            | 0            | –6dB |

| 0            | 1            | 0dB  |

| 1            | 0            | +6dB |

| Gain<br>MDS1 | Gain<br>MDS0 | GMDS |

|--------------|--------------|------|

| 0            | 0            | –6dB |

| 0            | 1            | 0dB  |

| 1            | 0            | +6dB |

#### **\$DX commands**

| Command  | D3             | D2 | D1 | D0           |

|----------|----------------|----|----|--------------|

| CLV CTRL | DCLV<br>PWM MD | ТВ | TP | CLVS<br>Gain |

- See the \$CX command.

| Command bit     | Explanation (See the Timing Chart 1-3.)                |

|-----------------|--------------------------------------------------------|

| DCLV PWM MD = 1 | CLV PWM mode specified. Both MDS and MDP are used.     |

| DCLV PWM MD = 0 | CLV PWM mode specified. Ternary MDP values are output. |

| Command bit | Explanation                                  |

|-------------|----------------------------------------------|

| TB = 0      | Bottom hold in CLVS mode at cycle of RFCK/32 |

| TB = 1      | Bottom hold in CLVS mode at cycle of RFCK/16 |

| TP = 0      | Peak hold in CLVS mode at cycle of RFCK/4    |

| TP = 1      | Peak hold in CLVS mode at cycle of RFCK/2    |

#### \$EX commands

| Command  | D3  | D2  | D1  | D0   |

|----------|-----|-----|-----|------|

| CLV mode | CM3 | CM2 | CM1 | CM10 |

| CM3 | CM2 | CM1 | CM0 | Mode  | Explanation               |

|-----|-----|-----|-----|-------|---------------------------|

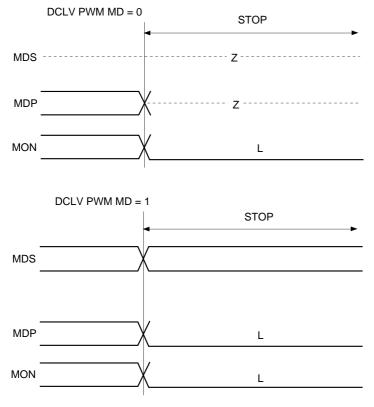

| 0   | 0   | 0   | 0   | STOP  | See the Timing Chart 1-4. |

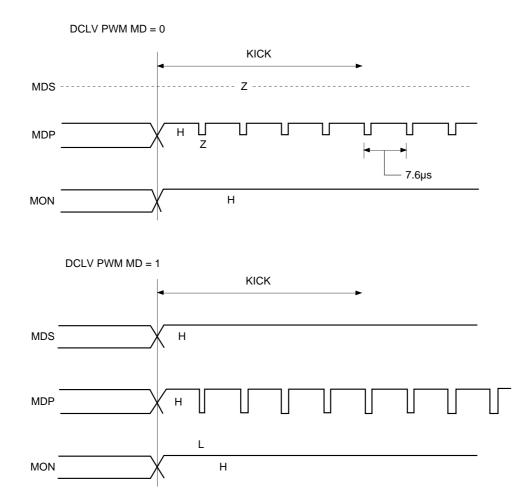

| 1   | 0   | 0   | 0   | KICK  | See the Timing Chart 1-5. |

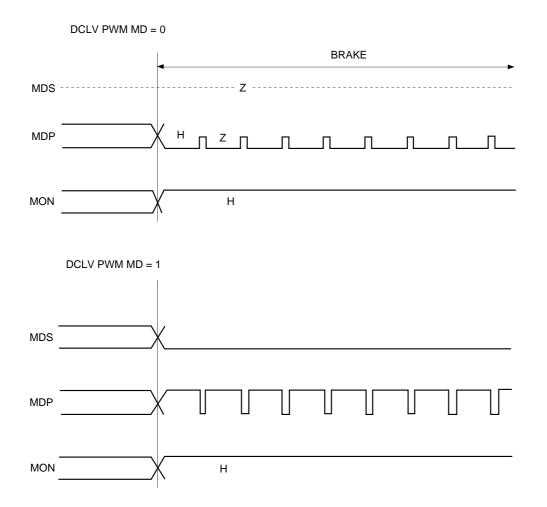

| 1   | 0   | 1   | 0   | BRAKE | See the Timing Chart 1-6. |

| 1   | 1   | 1   | 0   | CLVS  |                           |

| 1   | 1   | 1   | 1   | CLVP  |                           |

| 0   | 1   | 1   | 0   | CLVA  |                           |

STOP : Spindle motor stop mode

KICK : Spindle motor forward rotation mode

BRAKE : Spindle motor reverse rotation mode

CLVS : Rough servo mode. When RF-PLL circuit lock is disengaged, this mode is used to pull the disc rotations within the RF-PLL capture range.

CLVP : PLL servo mode.

CLVA : Automatic CLVS/CLVP switching mode. This mode is normally used during playback.

| 1-2   |

|-------|

| chart |

| ing C |

| Tim   |

| C2 correction status | No Error | Single error correction | Irretrievable error |

|----------------------|----------|-------------------------|---------------------|

| C2F2                 | 0        | 0                       | 1                   |

| C2F1 C2F2            | 0        | -                       | 1                   |

|                      |          |                         |                     |

|                      |          |                         |                     |

| C1 correction status | No Error | Single error correction | Irretrievable error |

|----------------------|----------|-------------------------|---------------------|

| C1F1 C1F2            | 0        | 0                       | -                   |

| C1F1                 | 0        | -                       | -                   |

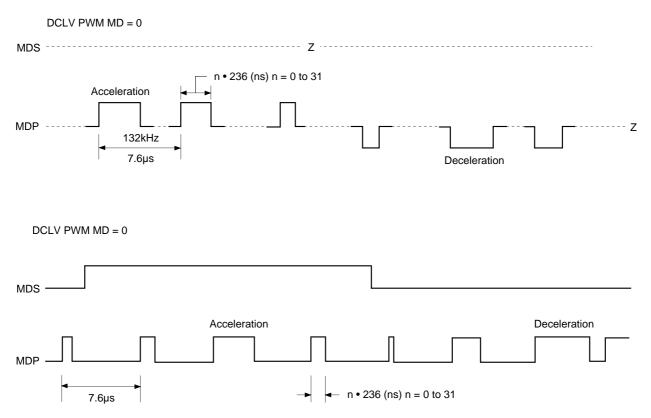

#### **Timing Chart 1-3**

**Timing Chart 1-4**

## Timing Chart 1-5

## **Timing Chart 1-6**

#### 1-2. Description of SENS Output

The following signals are output from SENS, depending on the microcomputer serial register value (latching not required).

| Microcomputer serial register value (latching not required) | SENS<br>output | Meaning                                                                                                                     |  |

|-------------------------------------------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------|--|

| \$0X, 1X, 2X, 3X                                            | SEIN           | SEIN, a signal input to the this IC from the SSP, is output.                                                                |  |

| \$4X                                                        | XBUSY          | Low while the auto sequencer is in operation, high when operation terminates.                                               |  |

| \$5X                                                        | FOK            | Outputs the signal input to the FOK pin. Normally, FOK (from RF) is input. High for "focus OK".                             |  |

| \$6X                                                        | SEIN           | SEIN, a signal input to this IC from the SSP, is output.                                                                    |  |

| \$AX                                                        | GFS            | High when the played back frame sync is obtained with the correct timing.                                                   |  |