## **Advanced Analog**

a division of Intech

## **DESCRIPTION**

The RGB DAC 3405S Series combines three video speed digital-to-analog converters, three static RAM arrays organized 32 x 4, internal temperature compensated reference and all the control lines necessary for a full graphics/color monitor interface. All this is contained in a single monolithic low power CMOS/TTL compatible IC.

In a typical application, each of three independent red, green and blue analog outputs will drive a 75 ohm source and load terminated coax that supplies a high resolution video monitor with a palette of 4096 colors. Any of 32 colors are available at a 60 MHz rate.

The RGB DAC 3405S Series can be directly interfaced to CMOS, HCT, TTL and advanced TTL logic families. It is also capable of developing signals in conformance with EIA standards 170/343. Features include small size, synchronous data and control lines for minimal skew and glitch, built-in temperature compensated reference, guaranteed linearity, offset, and gain; plus superior temperature coefficients to make the RGB DAC 3405S Series a state-of-the-art industry leader.

## **RGB DAC 3405S Series**

MONOLITHIC CMOS, TRIPLE 4-BIT VIDEO DAC WITH LOOKUP TABLE

## **FEATURES**

- □ Triple 32 x 4 SRAM lookup table

- □ Internal reference, temperature compensated

- □ Small size

- □ Single +5V operation

- Fully synchronous operation for minimal skew

- □ Low power CMOS circuitry

- Ideal for videotex systems

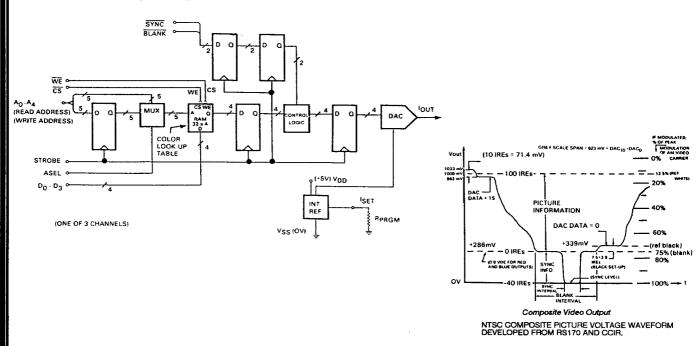

## **BLOCK DIAGRAM**

## **SPECIFICATIONS**

#### **ABSOLUTE MAXIMUM RATINGS**

Supply Voltage (VDD-VSs)

Supply current (75\Omega loads)

Full Scale output current

Drive into any digital input (clamped)

Output voltage compliance range (each channel)

Logic input voltage range "0"

Logic input voltage range "1"

Ambient operating temperature range

Ambient storage temperature range

6 VDC max. 60 mA max. 40 mA max. ±10 mA max. -0.3 to +2.5 volts instantaneous Vss -0.3 Vdc min. VDD +0.3 Vdc max. 0°C to +70°C -55°C to +125°C

| Recommended Operating Conditions               | Min  |                     | Max  | Units          |  |

|------------------------------------------------|------|---------------------|------|----------------|--|

| Supply voltage (VDD-Vss) RL (output load) RSET | 4.75 | 5.00<br>37.5<br>2.9 | 5.25 | Vdc<br>Ω<br>KΩ |  |

| Characteristics                                                                                                                                                                                                                                                                                          | Min                  | Тур                                                                | Max                                                           | Units                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------------------------------------------------------------------|---------------------------------------------------------------|----------------------------------------------------------------|

| INPUT CHARACTERISTICS Digital Coding Compatibility                                                                                                                                                                                                                                                       | TTL                  | 4<br>Binary<br>or CMOS                                             | Bits                                                          |                                                                |

| Loading<br>Logic "0" @ 10μÄ max.)<br>Logic "1" @ 10μA max.                                                                                                                                                                                                                                               | One eq<br>Vss<br>2.0 | uivalent H<br>0.4<br>2.4                                           | CT unit load<br>0.8<br>Voo                                    | Voc<br>Voc                                                     |

| OUTPUT CHARACTERISTICS Offset all current sources OFF Offset - Tc Gain (Relative to RSET) <sup>1</sup> Gain Tc Gain, variance (each channel, relative to the average of all three) Linearity Integral Differential Linearity TC Monotonicity                                                             | Guar                 | ±1.0<br>±5.0<br>±5<br>±50<br>±2.0<br>±0.1<br>±0.1<br>±20<br>anteed | ±10.0<br>±15.0<br>±10<br>±200<br>±6.0<br>±0.5<br>±0.5<br>±100 | μΑ ppmFS/°C % ppm/°C % LSB LSB ppmFS/°C                        |

| DYNAMIC CHARACTERISTICS  Conversion rate - max. over operating temperature & supply Settling time (to 0.5 LSB) Set-up time Hold time Output transient glitch energy Output transient glitch amplitude                                                                                                    | 60<br>2<br>2         | 12<br>50<br>60                                                     |                                                               | MHz<br>ns<br>ns<br>ns<br>pV-sec<br>mV                          |

| GENERAL INFORMATION Internal voltage reference Color palette Internal static RAM (32 x 4) (x 3 channels) Max. output current drive capability (for combinations of RSET and RL) Max. output voltage drive capability (for combinations of RSET and RL) Power supply current Power supply rejection ratio | 1.26<br>33<br>1.5    | 1.40<br>4096<br>32<br>30<br>(-66dB<br>0.0005                       |                                                               | voits<br>colors<br>colors<br>mA<br>volts<br>mA<br>%/%(VDD-VSS) |

| DIGITAL OUTPUT CHARACTERISTICS Do to D3 - When OE is enabled. Coding Compatibility Drive  Logic "0" - 0 to 20mA sink Logic "1" - 0 to 4mA source                                                                                                                                                         | Two "7               | Binary<br>TL or CM0<br>'4S" Schot<br>ICT equiv.<br>  0.1<br>  4.9  | Vdc<br>Vdc                                                    |                                                                |

|         | BI-DIR<br>Data Bu<br>OE |     | WHT | ASEL | BLANK<br>ADJ | REF<br>RGB | MPLX<br>ADDR | SYNC<br>ADJ |

|---------|-------------------------|-----|-----|------|--------------|------------|--------------|-------------|

| 3405SWM | yes                     | yes | yes | yes  | yes          | yes        | yes          | yes         |

| 3405SW  | yes                     | no  | no  | yes  | yes          | no         | no           | yes         |

| 3405S   | no                      | no  | กด  | yes  | no           | no         | no           | no          |

**RGBDAC3405S Series Product Guide**

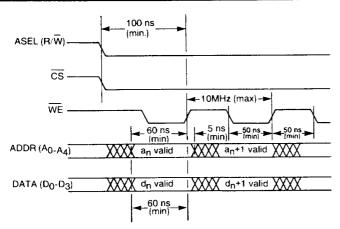

Write Mode Timing Diagram

## **DEVICE OPERATION**

The output of the RGB DAC 3405S is a current source whose full scale value is set by an external resistor. This resistor is connected to an internal reference (1.4V nominal), and the current through the resistor represents 7/16 LSBs of output current. Thus, for a full scale current of 15 LSBs, IO = 1.4R  $\times$  16  $\times$  15/7 = 48/R, where IO = full scale output current, R = current settling resistor (ohms). This resistor is connected from lset to ground.

Example:  $RL = 37.5\Omega$ , IO = .0166 (VO = 637.5 mV from black to white level.)

$$R = 48 = 48 = 0.0166 = 2890 \text{ (ohm)}$$

The value of R would be  $5780\Omega$  nominal if RL were  $75\Omega$ .

### PIN DESCRIPTION

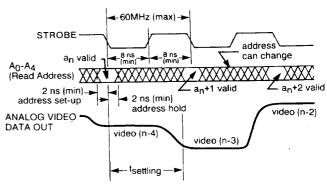

#### Read Address (Ao - A4)

This provides address information for the lookup tables during read operations through an edge triggered register. This path to the LUT is enabled by a logic "1" level at the ADDRESS SELECT line. The setup and hold times from valid address to the falling edge of strobe are 2 nanoseconds and 2 nanoseconds minimum, respectively. This input also provides address information for the LUT during write operations. This path to the LUT is enabled by a logic "0" level at the ADDRESS SELECT line. These lines are buffered internally and provide asynchronous access to the LUT.

#### Address Select (ASEL)

A logic "1" enables the READ ADDRESS path to the LUT. A logic "0" enables the WRITE ADDRESS path to the LUT. This input does not modify the contents of the LUT and is used to select between display mode (READ ADDRESS) and modify mode (WRITE ADDRESS) operations.

#### **DATA (Do - D3)**

This input provides LUT data in nibble form during write operations when used in conjunction with WRITE ADDRESS, WE and CSR, CSG or CSB.

Read Mode Timing Diagram

### **CHIP SELECT (CSR, CSG, CSB)**

The active portion of the LUT is selected with these inputs. During write mode operations the desired LUT location may be modified by a logic "0"at the appropriate CS line, enabling the WRITE ADDRESS lines with the correct LUT address with the new value on the DATA lines and activating the WE line.

During display mode, all three CS lines are held at logic "0" to enable all three channel outputs to the DAC internal registers.

#### WRITE ENABLE (WE)

A logic "1" selects read or display mode, a logic "0" selects write mode. When used in conjunction with the WRITE ADDRESS, CS and DATA inputs a modification of a location in the LUT may be made.

#### **BLANK (BLANK)**

A logic "0" on this input synchronously sets all three channels to the blank level. This input overrides data from the LUT and is used to blank the screen. This input may be overridden by the OVERLAY and REF combination. This input is latched into an edge triggered register on the falling edge of STROBE.

## SYNC (SYNC)

The sync amplitude (40 IRE units) is synchronously subtracted from the green DAC output when a logic "0" appears at this input. This input is used to generate composite sync and blank signals to the monitor. This input is latched into an edge triggered register on the falling edge of STROBE.

#### STRORE

This is the main clock input of which the falling edge is used to strobe the data and control inputs into an edge triggered register, as well as move this information in a synchronous pipeline fashion.

#### ISET (programs gain)

An external resistor connected from this point to Vss programs the DAC full scale outputs in the following manner: lout = 48/R mA, where R is the external resistor value in  $k\Omega$ .

#### **BIAS**

This is the control amplifier output and should be bypassed to VDD with  $0.1\mu F$  capacitor. External loading at this point is not recommended.

#### RED, GRN, BLU OUTPUT

These are the current outputs for the three channels and are normally resistively connected to Vss with either 75 or 37.5 ohms.

#### **VDD**

This is the most positive supply pin and is normally connected to +5V.

#### **VSS**

This is the most negative supply pin and is normally connected to ground.

## **BLANK ADJ (RGBDAC3405SW/SWM)**

This input may be used to adjust the black level of the three DAC channels and is normally left unconnected. The nominal black value is 7.5 IRE units above the blank level. To adjust this level, connect a  $10k\Omega$  potentiometer from VDD to Vss and a  $10k\Omega$  resistor from the wiper of the potentiometer to the BLANK ADJ pin.

### SYNC ADJ (RGBDAC3405SW/SWM)

In precision applications, this input may be used to adjust the sync amplitude (nominally 40 IREs) on the green DAC channel. It is normally left unconnected. To adjust this level, connect a  $10k\Omega$  potentiometer from VDD to Vss and a  $10k\Omega$  resistor from the wiper of the potentimeter to the SYNC ADJ pin.

#### OUTPUT ENABLE (OE) (RGBDAC3405SW/SWM)

A logic "0" at this input enables output buffers from the selected LUT color channel to the DATA lines during read back operation. If more than one CS line is at logic "0" the output buffers will be disabled to avoid a bus conflict.

## WHT CONTROL, REF WHITE FUNCTION (RGBDAC3405SWM)

When enabled by both OVLY and REF being active; a logic "0" at this input sets reference white to the DAC full scale and a logic "1" sets reference white to the DAC full scale value plus 10 IREs.

#### **OVERLAY (OVLY) (RGBDAC3405SWM)**

A logic "0" on this line synchronously forces all three DAC outputs to the black level unless the REF line for that channel is active. A logic "1" on this line synchronously disables the REF input for all three channels. This input is latched into an edge triggered register on the falling edge of STROBE.

## REFERENCE (REF RED, GRN, BLU) (RGBDAC3405SWM)

These inputs are inactive if the OVERLAY line is held at logic "1." If the OVERLAY line is at logic "0" then a logic "0" at any of these inputs synchronously sets the corresponding channel to the reference white level as defined by the WHT CONTROL input. The OVERLAY and REF inputs

combine to synchronously override all LUT and control (blank and sync) inputs to the DAC. These inputs are normally used as a 4-bit data bus to overlay text on the graphics display. These inputs are latched into an edge triggered register on the falling edge of STROBE.

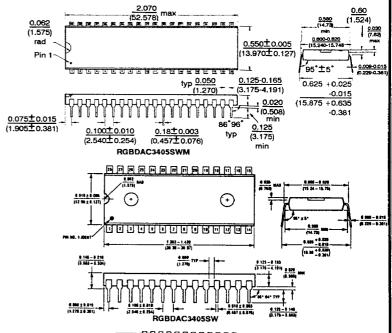

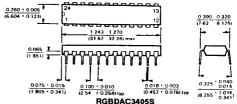

## **MECHANICAL OUTLINE**

## PIN DESIGNATIONS

| Function       | SWM | SW | S  | Function       | SWM | sw | s  |

|----------------|-----|----|----|----------------|-----|----|----|

| Blank Adj      | 1   | 1  | -  | VDD            | 21  | -  | -  |

| Grn Out        | 2   | 2  | 1  | Wo             | 22  | 17 | 15 |

| Blu Out        | 3   | 3  | 2  | Ao             | 23  | 17 | 15 |

| Red Out        | 4   | 4  | 3  | W <sub>1</sub> | 24  | 18 | 16 |

| Vss            | 5   | -  | -  | A1             | 25  | 18 | 16 |

| <u>Str</u> obe | 6   | 5  | 4  | W <sub>2</sub> | 26  | 19 | 17 |

| <u>ŌĒ</u>      | 7   | 6  | -  | A2             | 27  | 19 | 17 |

| WE             | 8   | 7  | 5  | Wз             | 28  | 20 | 18 |

| Ref Grn        | 9   | -  | -  | Аз             | 29  | 20 | 18 |

| Ref Blu        | 10  | -  | -  | W4             | 30  | 21 | 19 |

| Ref Red        | 11  | -  | -  | A4             | 31  | 21 | 19 |

| CSG            | 12  | 8  | 6  | ÖVLY           | 32  | -  | -  |

| CSB            | 13  | 9  | 7  | Wht Ctl        | 33  | 22 | -  |

| CSR            | 14  | 10 | 8  | Blank          | 34  | 23 | 20 |

| Do             | 15  | 11 | 9  | Sync           | 35  | 24 | 21 |

| D <sub>1</sub> | 16  | 12 | 10 | Vss            | 36  | -  | -  |

| D <sub>2</sub> | 17  | 13 | 11 | ISET (VRef)    | 37  | 25 | 22 |

| Dз             | 18  | 14 | 12 | Bias           | 38  | 26 | 23 |

| Addr Sel       | 19  | 15 | 13 | Sync Adj       | 39  | 27 | -  |

| Vss            | 20  | 16 | 14 | VDD            | 40  | 28 | 24 |

4-8908

# **Advanced Analog**

a division of Intech

MIL-STD-1772 Qualified

2270 Martin Avenue Santa Clara CA 95050-2781 (408) 988-4930 FAX (408) 988-2702

015761 X \_ X