19-2463; Rev 2; 3/03

EVALUATION KIT AVAILABLE

# Arbitrary Graphics On-Screen Display Video Generator

## **General Description**

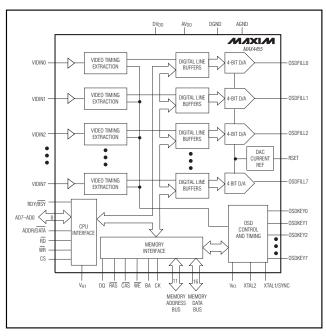

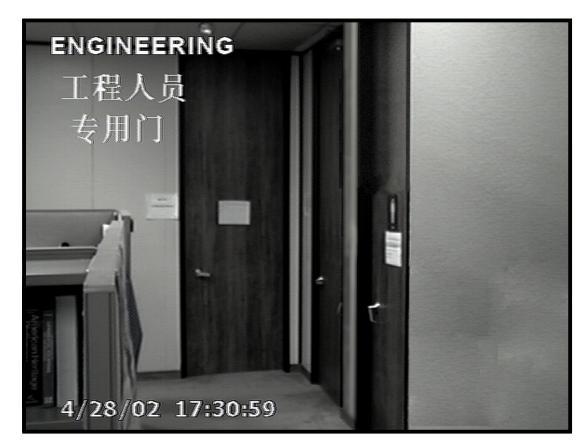

The MAX4455 is an eight-channel arbitrary graphics on-screen display (OSD) video generator that inserts arbitrary gray-scale bit-mapped graphics into eight asynchronous composite video sources. Ideal for security camera surveillance systems, the MAX4455 supports the insertion of graphics and text on up to eight video output channels in 15 levels of brightness. It easily displays information such as company logo, camera location, time, and date with arbitrary fonts and sizes. Arbitrary graphics capability enables the display of unique languages and fonts, allowing manufacturers to tailor their system for any geographic market. The MAX4455 is designed to work with Maxim's video crosspoint switches, such as the MAX4356 and MAX4358, which include circuitry that simplifies the insertion of the OSD information. The MAX4455 can also be used with discrete fast mux switches.

The MAX4455 operates from a 3V to 3.6V digital supply, and a 2.7V to 5.5V analog supply. Independent interface supplies enable the MAX4455 to communicate with microprocessors and OSD crosspoint switch logic with logic levels ranging from 2.7V to 5.5V. The MAX4455 uses an external 16Mb SDRAM for graphical image storage for all eight video channels. The MAX4455 manages all memory interface functions, allowing a simple host  $\mu$ P interface. The MAX4455's multiple-channel memory sharing and multiple-location write function allow fast memory updates of shared graphics information necessary for rapidly changing OSD information, such as a time stamp.

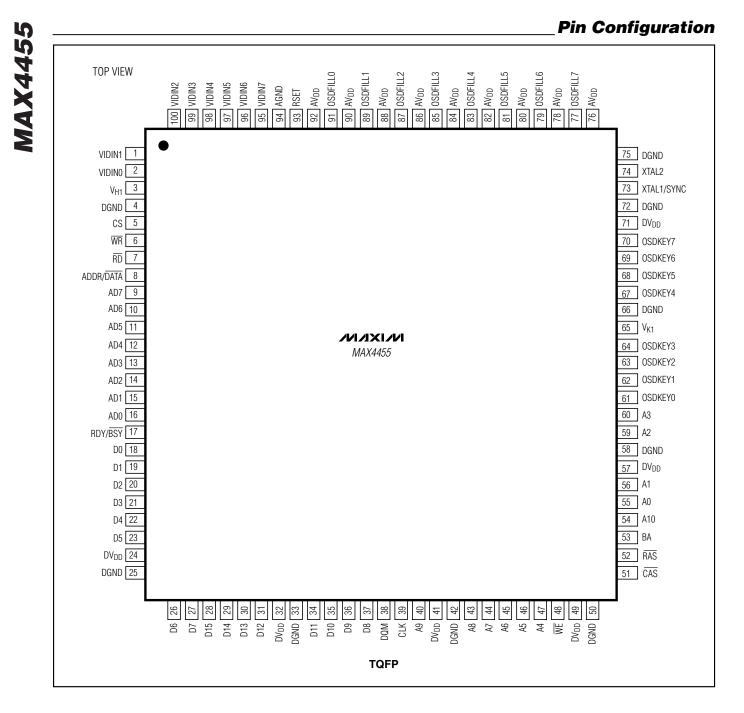

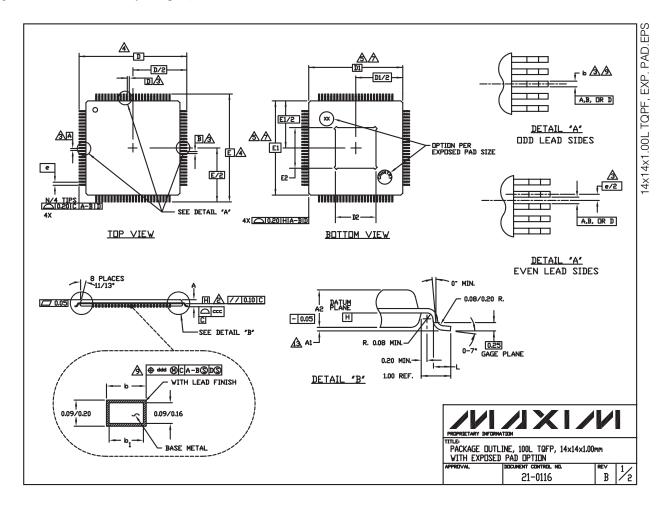

The MAX4455 is available in a thin 100-pin TQFP package (200mm<sup>2</sup> area), and is fully specified over the extended temperature range (-40°C to +85°C). The MAX4455EVSYS is available to evaluate the MAX4455 along with the MAX4358 ( $32 \times 16$  video crosspoint switch with OSD).

**Applications**

Security Systems Video Routing Industrial Applications

Pin Configuration appears at end of data sheet.

### **Features**

- Generates Arbitrary Graphics Images

- 15-Level Gray Scale

- 8 Channels of Bit-Mapped OSD

- Loss-of-Signal Detector for All Channels

- Graphics Updatable Within the Vertical Interval

- Update Time Stamp on All Eight Channels Simultaneously

- 3V and 5V Single-Supply Operation

- Works with MAX4356/MAX4358 Video Crosspoint Devices and Fast Mux Switches

- Small 100-Pin TQFP Package (200mm<sup>2</sup>)

## **Ordering Information**

| PART       | TEMP RANGE     | PIN-PACKAGE |

|------------|----------------|-------------|

| MAX4455ECQ | -40°C to +85°C | 100 TQFP    |

### \_Functional Diagram

# MAX4455

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

## **ABSOLUTE MAXIMUM RATINGS**

| AV <sub>DD</sub> to DV <sub>DD</sub><br>AV <sub>DD</sub> to AGND |                                   |

|------------------------------------------------------------------|-----------------------------------|

| AV <sub>DD</sub> to DGND                                         |                                   |

| DV <sub>DD</sub> to AGND                                         | 0.3V to +6V                       |

| DV <sub>DD</sub> to DGND                                         | 0.3V to +6V                       |

| V <sub>H1</sub> , V <sub>K1</sub> to DGND                        | 0.3V to +6V                       |

| V <sub>H1</sub> , V <sub>K1</sub> to AGND                        | 0.3V to +6V                       |

| AGND to DGND                                                     | 0.3V to +0.3V                     |

| Analog Inputs (VIDIN_) to AGND                                   | 0.3V to (AV <sub>DD</sub> + 0.3V) |

| Analog Outputs (OSDFILL_) to AGND                                | 0.3V to (AV <sub>DD</sub> + 0.3V) |

| RSET to AGND                       | 0.3V to (AV <sub>DD</sub> + 0.3V) |

|------------------------------------|-----------------------------------|

| Memory Interface to DGND           | 0.3V to (DV <sub>DD</sub> + 0.3V) |

| Host Interface to DGND             | 0.3V to (V <sub>H1</sub> + 0.3V)  |

| OSDKEY_ to DGND                    | 0.3V to (V <sub>K1</sub> + 0.3V)  |

| Continuous Power Dissipation (TA = | = +70°C)                          |

| 100-Pin TQFP (derate 37.0mW/°C     | 2 above +70°C)2963mW              |

| Operating Temperature Range        | 40°C to +85°C                     |

| Storage Temperature Range          |                                   |

| Lead Temperature (soldering, 10s)  | +300°C                            |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **ELECTRICAL CHARACTERISTICS**

$(DV_{DD} = 3.0V \text{ to } 3.6V, \text{ } AV_{DD} = 2.7V \text{ to } 5.5V, \text{ } V_{K1} = V_{H1} = 2.7V \text{ to } 5.5V, \text{ } \text{AGND} = \text{DGND} = 0, \text{ } \text{R}_{\text{RSET}} = 11.75 \text{k} \Omega \pm 1\%, \text{ } \text{R}_{\text{OSDFILL}} = 75 \Omega, \text{ } \text{f}_{\text{XTAL1/SYNC}} = 40.5\text{MHz}, \text{ } \text{T}_{\text{A}} = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ } \text{unless otherwise noted}. \text{ } \text{Typical values are at } \text{T}_{\text{A}} = +25^{\circ}\text{C}.) \text{ (Note 1)}$

| PARAMETER                               | SYMBOL           | CON                                     | DITIONS                       | MIN  | ТҮР  | MAX  | UNITS |

|-----------------------------------------|------------------|-----------------------------------------|-------------------------------|------|------|------|-------|

| Analog Supply Voltage                   | AV <sub>DD</sub> |                                         |                               | 2.7  |      | 5.5  | V     |

| Digital Supply Voltage                  | DVDD             |                                         |                               | 3.0  |      | 3.6  | V     |

| Host Supply Voltage                     | V <sub>H1</sub>  |                                         |                               | 2.7  |      | 5.5  | V     |

| OSDKEY Logic Supply Voltage             | V <sub>K1</sub>  |                                         |                               | 2.7  |      | 5.5  | V     |

| Analog Supply Current                   | AI <sub>DD</sub> | All OSDFILL_ output                     | ts at 100 IRE                 |      |      | 190  | mA    |

| Digital Supply Current                  | DI <sub>DD</sub> | fXTAL1/SYNC = 40.5M                     | ЛНz                           |      | 30   |      | mA    |

| Host Interface Static Supply<br>Current | Ivh1             | Host interface logic<br>V <sub>H1</sub> | levels driven to GND or       |      |      | 10   | μA    |

| Analog Power-Supply Rejection<br>Ratio  | PSRR             | At DC                                   |                               |      | 35   |      | dB    |

| VIDIN_ Input Resistance                 |                  |                                         |                               |      | 100  |      | kΩ    |

| OSDFILL Slew Rate                       | SR               | Output V <sub>P-P</sub> = 0.7V          |                               |      | 140  |      | V/µs  |

|                                         |                  | Pixel data = 1111                       | $AV_{DD} = 2.7V$              | -8.2 |      | +8.2 | IRE   |

| White Output Voltage Accuracy           | FSR              | Pixel dala = $1111$                     | $AV_{DD} = 5.5V$              | -7.5 |      | +7.5 | IKE   |

| Black Output Voltage                    |                  | Pixel data = 0001                       |                               |      | ±1.5 |      | IRE   |

| OSDFILL DAC Linearity                   |                  | (Guaranteed monoto                      | onic)                         |      |      | ±5   | %FSR  |

| Channel-to-Channel Crosstalk            |                  | At 6MHz V <sub>OUT</sub> = 0.7          | VP-P                          |      | 60   |      | dB    |

| Key-to-Fill Timing Delay                |                  |                                         |                               |      | ±1   |      | ns    |

| RSET Pin Voltage                        |                  | 1                                       |                               |      | 0.80 |      | V     |

| OSDKEY_ Logic Output Low                | Vol              | $V_{K1} = 5V$ , $I_{SINK} = 4r$         | nA                            |      |      | 0.45 | V     |

| OSDKEY_ Logic Output High               | VOH              | V <sub>K1</sub> = 5V, ISOURCE =         | = 4mA                         | 2.4  |      |      | V     |

| OSDKEY_Logic Supply Current             | IVK1             | OSDKEY_ logic leve                      | els driven to GND or $V_{K1}$ |      |      | 10   | μA    |

## µP HOST INTERFACE—DC CHARACTERISTICS

$(DV_{DD} = 3.0V \text{ to } 3.6V, \text{ AV}_{DD} = 2.7V \text{ to } 5.5V, \text{ V}_{K1} = \text{V}_{H1} = 2.7V \text{ to } 5.5V, \text{ AGND} = \text{DGND} = 0, \text{R}_{\text{RSET}} = 11.75 \text{k}\Omega \pm 1\%, \text{R}_{\text{OSDFILL}} = 75\Omega, \text{f}_{\text{XTAL1/SYNC}} = 40.5\text{MHz}, \text{T}_{A} = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted}. Typical values are at T_{A} = +25^{\circ}\text{C}.) (Note 2)$

| PARAMETER                | SYMBOL    | CONDITIONS                         | MIN                             | ТҮР | MAX                               | UNITS |

|--------------------------|-----------|------------------------------------|---------------------------------|-----|-----------------------------------|-------|

| Logic Input Voltage Low  | VIL       |                                    |                                 |     | (0.2 × V <sub>H1</sub> )<br>- 0.1 | V     |

| Logic Input Voltage High | VIH       |                                    | (0.2×V <sub>H1</sub> )<br>+ 1.2 |     |                                   | V     |

| Logic Input Current      | lil / lih | Sinking or sourcing                |                                 |     | 10                                | μA    |

| Logic Output Low         | Vol       | $V_{H1} = 5V$ , $I_{SINK} = 4mA$   |                                 |     | 0.45                              | V     |

| Logic Output High        | Voh       | $V_{H1} = 5V$ , $I_{SOURCE} = 4mA$ | 2.4                             |     |                                   | V     |

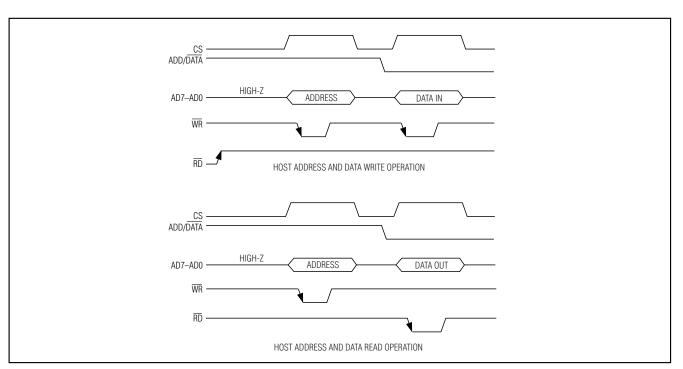

## **µP HOST INTERFACE**—AC CHARACTERISTICS

$(DV_{DD} = 3.0V \text{ to } 3.6V, \text{AV}_{DD} = 2.7V \text{ to } 5.5V, \text{V}_{K1} = \text{V}_{H1} = 2.7V \text{ to } 5.5V, \text{AGND} = \text{DGND} = 0, \text{R}_{RSET} = 11.75\text{k}\Omega \pm 1\%, \text{R}_{OSDFILL} = 75\Omega, \text{f}_{XTAL1/SYNC} = 40.5\text{MHz}, \text{C}_{HOST} = 50\text{pF}, \text{T}_{A} = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted}. Typical values are at T_{A} = +25^{\circ}\text{C}.) (Note 2) (Figure 1)$

| PARAMETER                                                 | SYMBOL | CONDITIONS | MIN | TYP | МАХ | UNITS |

|-----------------------------------------------------------|--------|------------|-----|-----|-----|-------|

| CS, ADD/DATA, AD7–AD0 Setup<br>Time Before WR Deassertion | t1     |            | 30  |     |     | ns    |

| CS Hold After WR Deassertion                              | t2     |            | 30  |     |     | ns    |

| Read Data Access Time                                     | t4     | (Note 3)   |     |     | 50  | ns    |

| Read Data Out to High-Z Time                              | t5     |            |     | 15  | 25  | ns    |

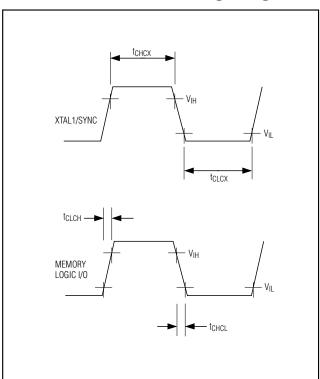

## **CLOCK TIMING CHARACTERISTICS**

$(DV_{DD} = 3.0 \text{ to } 3.6V, AV_{DD} = 2.7V \text{ to } 5.5V, V_{K1} = V_{H1} = 2.7V \text{ to } 5.5V, AGND = DGND = 0, R_{RSET} = 11.75k\Omega \pm 1\%, R_{OSDFILL} = 75\Omega, f_{XTAL1/SYNC} = 40.5MHz, T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ , unless otherwise noted. Typical values are at T\_A = +25^{\circ}C.) (Note 4) (Figure 2)

| PARAMETER                    | SYMBOL         | MBOL CONDITIONS                                                   |    | TYP  | MAX  | UNITS |

|------------------------------|----------------|-------------------------------------------------------------------|----|------|------|-------|

| Master Clock Frequency       | <b>f</b> CLKIN | Crystal oscillator or externally driven for specified performance |    | 40.5 | 40.6 | MHz   |

| Master Clock Input Low Time  | tCLCX          | t <sub>CLKIN</sub> = 1 / f <sub>CLKIN</sub> (Note 6)              | 10 |      |      | ns    |

| Master Clock Input High Time | <b>t</b> CHCX  | t <sub>CLKIN</sub> = 1 / f <sub>CLKIN</sub> (Note 6)              | 10 |      |      | ns    |

## MEMORY INTERFACE—DC CHARACTERISTICS

$(DV_{DD} = 3.0V \text{ to } 3.6V, AV_{DD} = 2.7V \text{ to } 5.5V, V_{K1} = V_{H1} = 2.7V \text{ to } 5.5V, AGND = DGND = 0, R_{RSET} = 11.75k\Omega \pm 1\%, R_{OSDFILL} = 75\Omega, f_{XTAL1/SYNC} = 40.5MHz, T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ , unless otherwise noted. Typical values are at T\_A = +25^{\circ}C.) (Note 2)

| PARAMETER                | SYMBOL          | CONDITIONS                              | MIN                                | TYP MAX                            | UNITS |

|--------------------------|-----------------|-----------------------------------------|------------------------------------|------------------------------------|-------|

| Logic Input Voltage Low  | VIL             |                                         |                                    | (0.2 × DV <sub>DD</sub> )<br>- 0.1 | V     |

| Logic Input Voltage High | VIH             |                                         | (0.2 × DV <sub>DD</sub> )<br>+ 1.3 |                                    | V     |

| Logic Input Current      | lil / lih       | Sinking or sourcing                     |                                    | 10                                 | μA    |

| Logic Output Low         | V <sub>OL</sub> | $DV_{DD} = 3.3V$ , $I_{SINK} = 4mA$     |                                    | 0.45                               | V     |

| Logic Output High        | VOH             | $DV_{DD} = 3.3V$ , $I_{SOURCE} = 0.5mA$ | 2.4                                |                                    | V     |

## MEMORY INTERFACE TIMING CHARACTERISTICS

$(DV_{DD} = 3.0V \text{ to } 3.6V, AV_{DD} = 2.7V \text{ to } 5.5V, V_{K1} = V_{H1} = 2.7V \text{ to } 5.5V, AGND = DGND = 0, R_{RSET} = 11.75k\Omega \pm 1\%, R_{OSDFILL} = 75\Omega, f_{XTAL1/SYNC} = 40.5MHz, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted. Typical values are at } T_A = +25^{\circ}C.)$

| PARAMETER                                  | SYMBOL        | CONDITIONS               | MIN | ТҮР  | MAX | UNITS |

|--------------------------------------------|---------------|--------------------------|-----|------|-----|-------|

| Digital Output Maximum Rise<br>Time        | <b>t</b> CLCH | 15pF load (Note 5)       |     | 3    |     | ns    |

| Digital Output Maximum Fall Time           | <b>t</b> CHCL | 15pF load (Note 5)       |     | 3    |     | ns    |

| Maximum Digital Out to Digital<br>Out Skew | <b>t</b> SKEW | 15pF load, except D0-D15 |     | ±2.5 |     | ns    |

**Note 1:** f<sub>XTAL1/SYNC</sub> is production tested at 1MHz. Application operating frequency is f<sub>XTAL1/SYNC</sub> = 40.5MHz.

Note 2: Pertains to host interface pins: ADDR/DATA, CS, WR, RD, AD7–AD0, RDY/BSY. V<sub>H1</sub> is connected to µP host power supply rail (2.7V to 5.5V).

Note 3: Read operation is combinational. Access time is from the latter of either  $\overline{RD}$  or CS.

Note 4: Pertains to XTAL1/SYNCIN and XTAL2 pins (external clock is supplied to XTAL1/SYNCIN pin). All input signals are specified with t<sub>R</sub> = t<sub>F</sub> = 5ns (10% to 90% of DV<sub>DD</sub>), and timed from a voltage level of 1.6V.

Note 5: Specified using 10% and 90% points.

CS ADD/DATA

AD7-AD0

ADD/DATA

CS

RD

AD7-AD0

WR

t<sub>1</sub>

ADDR/DATA IN

· to

t5

HOST ADDRESS OR DATA WRITE OPERATION

READ DATA OUT

HOST DATA READ OPERATION

## **Timing Diagrams**

Figure 2. Clock and Memory Timing Diagram

Figure 1. µP Host Interface Timing

t⊿

**MAX4455**

M / X I / M

0

0

0

0

10µs/div

NOTE: MEASUREMENT MADE WITH MAX4455EVSYS.

A: VCAMERA (NTSC COMPOSITE), 500mV/div

B: VCAMERA + OSDFILL, 500mV/div

C: VOSDFILL, 500mV/div

D: VOSDKEY, 5V/div

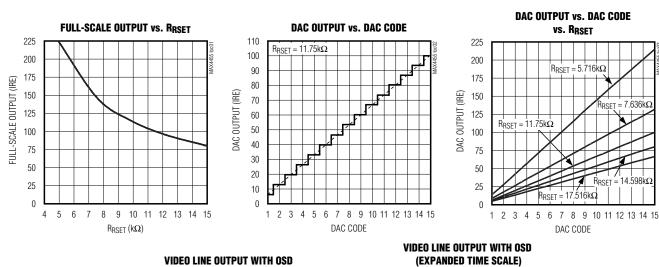

## **Typical Operating Characteristics**

$(AV_{DD} = 5V, DV_{DD} = 3.3V, R_{RSET} = 11.75k\Omega, T_A = +25^{\circ}C$ , unless otherwise noted.)

A

В

С

D

А 0 В 0 mi С 0 Λ D 1µs/div A: VCAMERA (NTSC COMPOSITE), 500mV/div B: VCAMERA + OSDFILL, 500mV/div

C: VOSDFILL, 500mV/div

D: V<sub>OSDKEY</sub>, 5V/div NOTE: MEASUREMENT MADE WITH MAX4455EVSYS.

**MAX4455**

## \_Typical Operating Characteristics (continued)

$(AV_{DD} = 5V, DV_{DD} = 3.3V, R_{RSET} = 11.75k\Omega, T_A = +25^{\circ}C, unless otherwise noted.)$

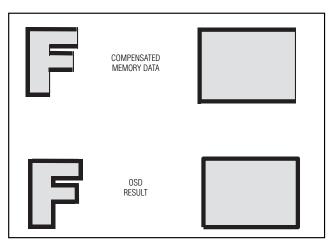

Figure 3. On-Screen Display Capability of the MAX4455

## Pin Description

| PIN                                                 | NAME                  | FUNCTION                                                                                                                                                                                                                                                                                                            |

|-----------------------------------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2, 1, 100, 99, 98, 97,<br>96, 95                    | VIDIN0-VIDIN7         | Analog Video Inputs. The MAX4455 extracts video timing information from each VIDIN_<br>input. AC-couple the input signal with a 0.1µF capacitor.                                                                                                                                                                    |

| 3                                                   | V <sub>H1</sub>       | Host Interface Supply Voltage Input. V <sub>H1</sub> supplies the level shifters for logic outputs to the host $\mu$ P interface. Connect V <sub>H1</sub> to the $\mu$ P logic supply.                                                                                                                              |

| 4, 25, 33, 42, 50, 58,<br>66, 72, 75                | DGND                  | Digital Ground                                                                                                                                                                                                                                                                                                      |

| 5                                                   | CS                    | Host Chip Select Digital Input. Drive CS logic high to enable the host data interface.                                                                                                                                                                                                                              |

| 6                                                   | WR                    | Host Write Strobe Digital Input                                                                                                                                                                                                                                                                                     |

| 7                                                   | RD                    | Host Read Strobe Digital Input                                                                                                                                                                                                                                                                                      |

| 8                                                   | ADDR/DATA             | Host Address or Data Select Digital Input                                                                                                                                                                                                                                                                           |

| 9–16                                                | AD7-AD0               | Host Address/Data Bus Digital I/O                                                                                                                                                                                                                                                                                   |

| 17                                                  | RDY/BSY               | Host Ready/Busy Handshake Digital Output                                                                                                                                                                                                                                                                            |

| 18–23, 26, 27, 37,<br>36, 35, 34, 31, 30,<br>29, 28 | D0-D15                | Memory Data Digital I/O                                                                                                                                                                                                                                                                                             |

| 24, 32, 41, 49, 57, 71                              | DV <sub>DD</sub>      | Positive Digital Power Supply. Bypass each DV <sub>DD</sub> pin with a 0.1µF capacitor to DGND.                                                                                                                                                                                                                     |

| 38                                                  | DQM                   | Memory DQM Digital Output. DQM controls the memory output buffer in read mode, and masks input data in write mode.                                                                                                                                                                                                  |

| 39                                                  | CLK                   | Memory Clock Digital Output                                                                                                                                                                                                                                                                                         |

| 48                                                  | WE                    | Memory Write Enable Digital Output                                                                                                                                                                                                                                                                                  |

| 51                                                  | CAS                   | Memory Column Address Strobe Digital Output                                                                                                                                                                                                                                                                         |

| 52                                                  | RAS                   | Memory Row Address Strobe Digital Output                                                                                                                                                                                                                                                                            |

| 53                                                  | BA                    | Memory Bank Address Digital Output                                                                                                                                                                                                                                                                                  |

| 55, 56, 59, 60, 47,<br>46, 45, 44, 43, 40, 54       | A0-A10                | Memory Address Digital Outputs                                                                                                                                                                                                                                                                                      |

| 61–64, 67–70                                        | OSDKEY0–<br>OSDKEY7   | OSDKEY Digital Outputs. OSDKEY_ logic low controls the fast mux switches (available in the Maxim crosspoint switches, MAX4356/MAX4358) to insert OSDFILL_ signal.                                                                                                                                                   |

| 65                                                  | V <sub>K1</sub>       | OSDKEY Interface Power-Supply Input. V <sub>K1</sub> supplies the level shifters for OSDKEY_ logic outputs to the fast mux switches (available in the Maxim crosspoint switches, MAX4356/MAX4358). Connect V <sub>K1</sub> to the digital supply of the fast mux switches (V <sub>DD</sub> of the MAX4356/MAX4358). |

| 73                                                  | XTAL1/SYNC            | Crystal Oscillator/External Clock Input. Connect a crystal oscillator module to XTAL1/SYNC, or connect a fundamental mode crystal oscillator between XTAL1/SYNC and XTAL2.                                                                                                                                          |

| 74                                                  | XTAL2                 | Crystal Oscillator Output. Leave XTAL2 unconnected when using a crystal oscillator module, or connect a fundamental mode crystal oscillator between XTAL1/SYNC and XTAL2.                                                                                                                                           |

| 76, 78, 80, 82, 84,<br>86, 88, 90, 92               | AV <sub>DD</sub>      | Positive Analog Power Supply. Bypass each AV_DD pin with a $0.1\mu F$ capacitor to AGND.                                                                                                                                                                                                                            |

| 77, 79, 81, 83, 85,<br>87, 89, 91                   | OSDFILL7-<br>OSDFILL0 | OSDFILL Analog Outputs. OSDFILL_ are video DAC current outputs and require a termination resistor (nominally 75 $\Omega$ ) to AGND.                                                                                                                                                                                 |

## **Pin Description (continued)**

| PIN | NAME | FUNCTION                                                                                                                                                        |

|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 93  | RSET | OSDFILL Reference Voltage. Connect a resistor (typically $11.75k\Omega$ ) from RSET to AGND to set the full-scale output current of all eight OSDFILL_ outputs. |

| 94  | AGND | Analog Ground                                                                                                                                                   |

### **Detailed Description**

The MAX4455 provides 4-bit gray-scale graphics video to eight simultaneous independent composite video inputs. The bit-mapped approach allows an arbitrary message to be inserted into the camera video when used in conjunction with the MAX4356/MAX4358 video crosspoint switch or discrete fast mux switch. The inserted graphics can include camera location, date, time, company logo, or warning prompts.

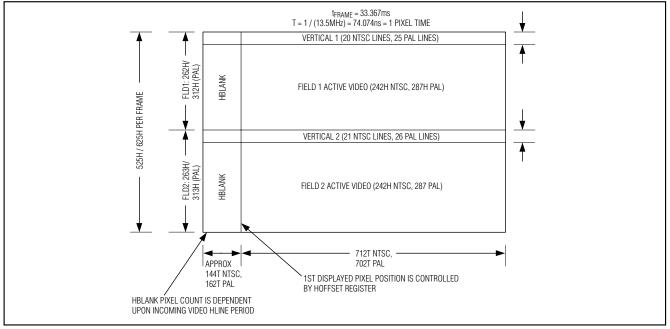

The graphics palette for each of the eight video channels in the MAX4455 is logically organized into 1024 pixels by 512 lines. This memory arrangement facilitates easy row/column pixel addressing by the host processor. The actual displayed area is  $712 \times 484$  NTSC ( $712 \times 512$  PAL) pixels. The remaining 312 logical pixels per line are blanked. The remaining 28 NTSC (0 PAL) horizontal lines are also blanked as shown in Figure 4.

The MAX4455 controls a 16Mb SDRAM (such as MT48LC1M16A) that stores video graphics insertion data. The MAX4455 performs all SDRAM support functions, including refresh, RAS/CAS timing, video addressing, and CPU access cycles for host processor read/write support.

Since the SDRAM is organized as a 16-bit wide × 1 million deep array, each SDRAM memory location holds 4 pixels (based on the fact that a pixel is 4 bits and memory is 16 bits wide). The host processor thus accesses pixels four at a time. The host processor interface is 8 bits wide so the 16 bit wide SDRAM data is written into (or read from) the pixel data register as two separate 8-bit bytes.

The MAX4455 establishes a video raster time base by sensing the video signal on either the output of the Maxim crosspoint switch, or the output buffer of the fast mux switch. The MAX4455 uses this raster timing to produce an OSD image signal that can be inserted into the camera video by controlling the OSDKEY input to the Maxim crosspoint switch or fast mux switch. The OSD image is inserted wherever the OSD video level pixel code has a nonzero value, and the crosspoint switch or discrete fast mux is made to pass the original video wherever the OSD video level pixel code is zero. When the OSD video level is nonzero, it represents a gray-level code such that level 1 is near black and code 15 (the maximum possible with a 4-bits-per-pixel code) is maximally white (Table 1). The host computer fills the external OSD frame memory with a bit-mapped image such that each pixel has a value between zero and 15, controlling both insertion locations and the brightness levels within an inserted video image. There are eight channels in the MAX4455 that share memory resources but are logically completely independent. Writing/reading image data to/from any channel's memory does not disrupt other channels.

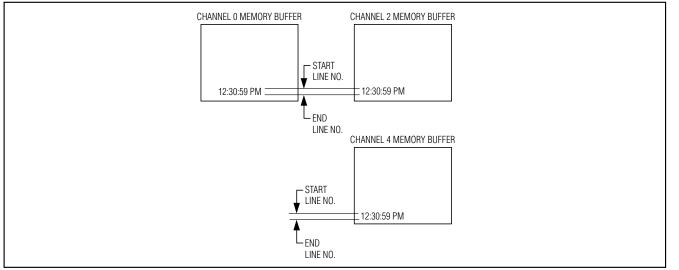

The MAX4455 features a memory-sharing function where the even channels or the odd channels can be updated simultaneously by writing to a designated source channel. The memory-sharing function minimizes the number of memory writes by the host processor. This is useful for updating information that changes rapidly (i.e., time stamp).

### **Video Inputs**

The MAX4455's eight VIDIN\_ inputs include circuitry to extract video timing from each asynchronous video channel for proper display of the OSD specific to that channel. Each VIDIN\_ time-base circuitry includes a horizontal sync detector, vertical sync detector, vertical interval detector, horizontal line counter, and even/odd field counter. The VIDIN\_ inputs sense a standard 1VP-P video signal at the output of the crosspoint switch, or fast mux buffer in order to make video timing insensitive to delays through the switch/mux. AC-couple the input with a 0.1 $\mu$ F capacitor.

### **OSDFILL\_** Video Outputs

The MAX4455 has eight independent current output video DACs that provide 7 IRE to 100 IRE video levels (R<sub>RSET</sub> = 11.75k $\Omega$ ) when terminated with 75 $\Omega$  to AGND. Connect OSDFILL\_ to either the OSDFILL\_ input of the Maxim crosspoint switch (MAX4356/MAX4358) or to one of the inputs of the fast mux switch.

### **OSDKEY** Control Outputs

Each OSD channel has an OSDKEY\_ logic output that drives low when OSDFILL\_ output video is to be multiplexed into the active video. The OSDKEY\_ output interfaces directly to the OSDKEY\_ inputs of the MAX4356/MAX4358 or control inputs of the fast mux switch to allow pixel-by-pixel OSD insertion. The V<sub>K1</sub> supply sets the OSDKEY\_ logic output voltage levels.

**MAX4455**

# Table 1. Pixel Data Mapping (4 Bits per Pixel)

| PIXEL DATA | GRAY SCALE | DESCRIPTION                                                            |

|------------|------------|------------------------------------------------------------------------|

| 0000       | 0          | Transparent—no OSD<br>insertion. Background<br>video appears normally. |

| 0001       | 1          | 7 IRE (black)                                                          |

| 0010       | 2          | 13 IRE                                                                 |

| 0011       | 3          | 20 IRE                                                                 |

| 0100       | 4          | 27 IRE                                                                 |

| 0101       | 5          | 33 IRE                                                                 |

| 0110       | 6          | 40 IRE                                                                 |

| 0111       | 7          | 47 IRE                                                                 |

| 1000       | 8          | 53 IRE                                                                 |

| 1001       | 9          | 60 IRE                                                                 |

| 1010       | 10         | 67 IRE                                                                 |

| 1011       | 11         | 73 IRE                                                                 |

| 1100       | 12         | 80 IRE                                                                 |

| 1101       | 13         | 87 IRE                                                                 |

| 1110       | 14         | 93 IRE                                                                 |

| 1111       | 15         | 100 IRE (white)                                                        |

Connect  $V_{K1}$  to the MAX4356/MAX4358  $V_{DD}$  logic supply, or a 5V logic supply for TTL output compatibility.

### **OSDFILL\_ Reference Voltage (RSET)**

Set the video DAC's full-scale output current for all eight channels by connecting a resistor between RSET and ground. The nominal 11.75k $\Omega$  R<sub>RSET</sub> provides a 100 IRE video output level when OSDFILL\_ outputs are terminated with 75 $\Omega$  resistors to ground. R<sub>RSET</sub> can typically range between 5k $\Omega$  and 15k $\Omega$ .

The full-scale OSD DAC output current = (106.5) / R<sub>RSET</sub>. The full-scale OSD DAC output voltage is the OSD DAC output current × R<sub>OSDFILL</sub>, where ROSDFILL\_ is the termination resistor to AGND at OSDFILL\_.

### **Crystal Oscillator**

The MAX4455 requires a 40.5MHz clock. Connect a 3.3V crystal oscillator module to XTAL1/SYNC and leave XTAL2 unconnected, or connect a lower cost 40.5MHz fundamental mode crystal between XTAL1/SYNC and XTAL2. The MAX4455 is designed to operate with a 50% clock duty cycle, but typically operates with up to 40% to 60% duty cycles. The oscillator circuitry typically requires 10ms to settle after the DV<sub>DD</sub> supply is powered up.

### **Microprocessor Interface**

**MAX4455**

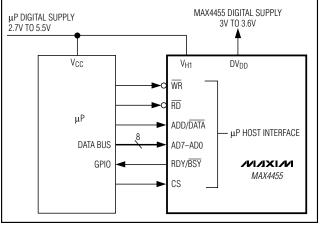

The MAX4455  $\mu$ P interface includes a byte-wide address/data bus (AD7–AD0) for parallel programming of the MAX4455, write strobe input (WR), read strobe input (RD), active-high chip-select input (CS), address or data-select input (ADDR/DATA), and a ready/busy hand-shaking output (RDY/BSY) (Figures 5 and 6). The MAX4455 allows for interfacing to a  $\mu$ P powered from a different supply than the MAX4455 by connecting V<sub>H1</sub> to the  $\mu$ P supply. For example, the MAX4455 can be operated with a single 3.3V supply, while the  $\mu$ P interface can be operated with 3.3V or 5V logic levels by connecting V<sub>H1</sub> to the  $\mu$ P power supply.

### **Host Access Protocol Sequence**

- 1) Host sets  $ADD/\overline{DATA} = 1$ .

- 2) Host outputs register address on AD7-AD0.

- 3) Host pulses WR low, then high to write register address.

- 4) Host checks  $RDY/\overline{BSY} = 1$  (host waits if  $RDY/\overline{BSY} = 0$ ).

For register data writes:

- 1) Host sets  $ADD/\overline{DATA} = 0$ .

- 2) Host drives register data on AD7-AD0.

- 3) Host pulses  $\overline{WR}$  low, then high.

- For register data reads:

- Host removes drive from AD7–AD0 in anticipation of register read operation and sets ADD/DATA = 0.

- 2) Host then pulses  $\overline{RD}$  low and reads register data.

- 3) The MAX4455 three states when RD is deasserted (high).

### **SDRAM Memory Interface**

The MAX4455 interfaces directly to a 16Mb SDRAM with 16-bit-wide data bus. The MAX4455 performs all SDRAM support functions, including refresh, RAS/CAS timing, data addressing, and CPU access cycles for host processor read/write support.

## \_MAX4455 Register Description

### **OSD** Register Organization

The host processor controls each of the MAX4455's eight video channels through eight groups (blocks) of 8bit command, status, data, and address registers, plus one multichannel register block. The register set description for a single channel is described in Table 2. The eight identical sets of 16 registers (14, plus 2 reserved) are selected by 4 LSB bits in the host interface address field as described in Tables 3 and 4. The lower address bits select which register is accessed within any given channel. Even channels can share buffer data for display

**MAX4455**

Figure 4. OSD Raster Dimensions

among even channels. Odd channels can also share buffer data for display among odd channels (see the *Memory Sharing* section).

### Detailed Description of the Channel-N Block Registers

### QPH, QPL (Quad Pixel Register)

Read/write pixel data 16-bits at a time to the quad pixel registers due to the SDRAM memory organization. The 4 MSBs (nybble) of QPH represent the left-most pixel and the 4 LSBs of QPL represent the right-most pixel (4 bits per pixel). To transfer the QPH/QPL value into display memory, set the QPHORIZ/QPLINE registers and then write 0000 0010 to the command register (see *Command Register* section).

### QPHORIZ

This 8-bit value is the address of the quad pixel within the line specified by QPLINE HI and QPLINE LO. A zero in QPHORIZ addresses the leftmost displayed quad pixel in the specified line, and increasing QPHORIZ addresses indexes towards the right-hand side of the video screen. Valid values range from zero to 177. Write a 1 in the HINC bit of the channel status register to enable autoincrement of QPHORIZ. QPHORIZ autoincrement saturates at 177.

Figure 5. µP Host Interface

### QPLINEH, QPLINEL

The QPLINE\_ 9-bit address specifies the horizontal line of the quad pixel to be accessed (host read or write). The 9th bit resides in the LSB position (bit 0) of the QPLINEH register. The lower 8 bits of the 9-bit address are specified by QPLINEL. Table 5 shows valid displayed line numbers. Note that for NTSC, lines 1 through 20 are never valid, as this is the vertical blank interval. Write a 1 in the VINC bit of the channel status register to enable autoincrement of QPLINE\_. QPLINE\_ autoincrement saturates at 511.

### STATUS

The channel status register contains a group of individual control bits and a loss-of-sync (LOS) flag bit. BLANK (when set to 1) forces suppression of the OSD insertion graphics, independent of the memory contents. ASYNC (when set to 1) enables the SHRxxxx registers to be updated by the host immediately; otherwise, they are updated at the next complete video field. HINC (when set to 1) enables autoincrement of the QPHORIZ register after each host read/write to OSD memory. VINC (when set to 1) enables autoincrement of QPLINEH/L after each host read/write to OSD memory. The LOS flag is useful in detecting the presence (or absence) of composite video at the channel VIDIN\_. LOS is a 1 if the channel's valid composite sync is lost for more than one horizontal line period. It resets back to zero once a valid sync pulse is detected.

The channel status register is described below:

| BIT7 |   |   |      |      |       |       | BIT0 |

|------|---|---|------|------|-------|-------|------|

| 0    | 0 | 0 | VINC | HINC | ASYNC | BLANK | LOS  |

|      |   |   |      |      |       |       |      |

Figure 6. Host Data Write and Read Sequences

| ADDRESS  | NAME     | DESCRIPTION                                                                                |

|----------|----------|--------------------------------------------------------------------------------------------|

| 0nnn0000 | QPH      | Quad pixel high data read/write. Most significant nybble = leftmost pixel.                 |

| 0nnn0001 | QPL      | Quad pixel low data read/write. Least significant nybble = rightmost pixel.                |

| 0nnn0010 | QPHORIZ  | Quad pixel within H line address                                                           |

| 0nnn0011 | QPLINEH  | Quad pixel line address high                                                               |

| 0nnn0100 | QPLINEL  | Quad pixel line address low                                                                |

| 0nnn0101 | STATUS   | Loss of sync for channel N, control bits                                                   |

| 0nnn0110 | COMMAND  | Command register                                                                           |

| 0nnn0111 | HOFFSET  | Horizontal offset                                                                          |

| 0nnn1000 | VOFFSET  | Vertical offset                                                                            |

| 0nnn1001 | SHRSRC   | Shared buffer source channel (0, 2, 4, 6) for even channels, (1, 3, 5, 7) for odd channels |

| 0nnn1010 | SHRBEGH  | Shared buffer beginning line high                                                          |

| 0nnn1011 | SHRBEGL  | Shared buffer beginning line low                                                           |

| 0nnn1100 | SHRENDH  | Shared buffer end line high                                                                |

| 0nnn1101 | SHRENDL  | Shared buffer end line low                                                                 |

| 0nnn1110 | Reserved | Reserved                                                                                   |

| Onnn1111 | Reserved | Reserved                                                                                   |

## Table 2. Channel-N Block Register Map

Note: nnn = 000 to 111 for channels 0 to 7, respectively.

## Table 3. Channel Block Addressing

| ADDRESS              | CHANNEL            |

|----------------------|--------------------|

| 0000xxxx             | 0                  |

| 0001xxxx             | 1                  |

| 0010xxxx             | 2                  |

| 0011xxxx             | 3                  |

| 0100xxxx             | 4                  |

| 0101xxxx             | 5                  |

| 0110xxxx             | 6                  |

| 0111xxxx             | 7                  |

| 1000xxxx             | Multichannel       |

| 1001xxxx to 1111xxxx | Reserved addresses |

## Table 4. Multichannel Block Register Map (Common to All Eight Channels)

| ADDRESS              | NAME     | DESCRIPTION                                        |  |  |  |  |

|----------------------|----------|----------------------------------------------------|--|--|--|--|

| 1000000              | QPH      | Quad pixel high data read/write for multiple write |  |  |  |  |

| 10000001             | QPL      | Quad pixel low data read/write for multiple write  |  |  |  |  |

| 10000010             | QPHORIZ  | Quad pixel within H line address                   |  |  |  |  |

| 10000011             | QPLINEH  | Quad pixel line address high                       |  |  |  |  |

| 10000100             | QPLINEL  | Quad pixel line address low                        |  |  |  |  |

| 10000101             | LOSALL   | Loss-of-sync flags for channels 0 through 7        |  |  |  |  |

| 10000110             | MWRITE   | Command register, triggers multiple write(s)       |  |  |  |  |

| 10000111             | CONTROL  | Control bits                                       |  |  |  |  |

| 10001000 TO 10001111 | Reserved | Reserved registers                                 |  |  |  |  |

## Table 5. QPLINE Mapping

| QPLINE      | NTSC (VOFFSET = 128)<br>FIELD, LINE | PAL (VOFFSET = 133)<br>FIELD, LINE |

|-------------|-------------------------------------|------------------------------------|

| 0 0000 0000 | Field 1, line 21                    | Field 1, line 26                   |

| 0 0000 0001 | Field 2, line 21                    | Field 2, line 26                   |

| 0 0000 0010 | Field 1, line 22                    | Field 1, line 27                   |

| 0 0000 0011 | Field 2, line 22                    | Field 2, line 27                   |

| 0 1111 1110 | Field 1, line 148                   | Field 1, line 153                  |

| 0 1111 1111 | Field 2, line 148                   | Field 2, line 153                  |

| 1 1111 0010 | Field 2, line 263                   |                                    |

| 1 1111 1111 | _                                   | Field 2, line 276                  |

### COMMAND

The channel command register allows writing and reading of quad pixel data into external SDRAM memory. The read and write operations are described below:

Writing 0000 0010 to the COMMAND register causes the pixel data in QPH and QPL to be stored into external SDRAM memory.

The command register is described below:

| • | Writing 0000 0001 to the COMMAND register copies |

|---|--------------------------------------------------|

| t | from external SDRAM memory the quad pixels spec- |

| i | ified by QPHORIZ/QPLINE into QPH/QPL.            |

• Writing 0000 0011 to COMMAND register causes a write followed by a readback to verify the data.

| BIT7 |   |   |   |   |   |       | BIT0 |

|------|---|---|---|---|---|-------|------|

| 0    | 0 | 0 | 0 | 0 | 0 | WRITE | READ |

#### HOFFSET

The channel horizontal offset register defaults at powerup to 128. Values less than 128 shift the OSD image to the left (as viewed on the display), while values greater than 128 shift the OSD image to the right. For example, changing HOFFSET from 128 to 110 shifts the image to the left by approximately 10% of the visible display. Changing HOFFSET from 128 to 156 shifts the image to the right by approximately 10% of the visible display. The image portion shifted beyond the active video is automatically blanked on any edge. The units of HOFF-SET are in quad pixels. Horizontal offset is used to allow flexibility in the video timing for various video sources. Horizontal offset ensures that the first logical OSD pixel is visible on the left-hand edge of the video monitor screen.

# **MAX4455**

### VOFFSET

The channel vertical offset register defaults at power-up to 128. Values less than 128 shift the image up while values greater than 128 shift the OSD image down. For example, changing VOFFSET from 128 to 80 shifts the image up by approximately 10% of the visible display. Changing VOFFSET from 128 to 176 shifts the image

down by approximately 10% of the visible display. This register controls the vertical offset of the OSD graphics insertion video. The units of VOFFSET are logical lines. Vertical offset ensures that the first logical OSD graphics line is visible on the video monitor screen. Updates to VOFFSET can take up to two full frame periods to take effect.

SHRSRC Shared memory source channel. A nonzero value in SHRSRC replaces a horizontal band of display with data from another channel. When an SHRSRC channel is selected (nonzero value in the SHRSRC register), the channel's graphics video is generated from the channel's memory, except for the horizontal video lines between (and including) SHRBEGH/L and SHRENDH/L, which instead comes from the memory channel specified by the SHRSRC register (see *Applications*  *Information* for more details on how video memory sharing works). Time of actual update, either immediate (asynchronous) or field synchronous, is controlled by the ASYNC flag in the channel command register. Even channels can only be shared with even channels. Odd channels can only be shared with odd channels.

**Note:** If multiple even or odd channels are set to 1, data is taken from the lowest even channel and shared with the higher even channels. This is also true for the odd channels.

The shared memory source channel register is described below:

| BIT7 |     |     |     |     |     |     | BIT0 |

|------|-----|-----|-----|-----|-----|-----|------|

| Ch7  | Ch6 | Ch5 | Ch4 | Ch3 | Ch2 | Ch1 | Ch0  |

### SHRBEGH, SHRBEGL

Share begin line HI, share begin line LO. This register pair contains a 9-bit address, which specifies the starting horizontal line to be used from the shared video frame buffer memory. SHRBEG HI contains only 1 bit, which resides in the LSB position (bit 0) of the SHRBEG HI register. The lower 8 bits of the 9-bit address are specified by SHRBEG LO. Valid shared line numbers range from 0 to 483 NTSC (511 PAL). The ASYNC flag in the channel status register controls the time of actual update, either immediate (asynchronous) or video field synchronous. SHRBEGH contains the upper bits of the starting line address and SHRBEGL contains the lower bits of the line starting address. To allow the entire value to be changed at once, the internal value of SHRBEG (which uses both SHRBEGH and SHRBEGL) is not updated until SHRBEGL is written. A write to SHRBEGH alone does not trigger an update of the internal SHRBEG value.

### SHRENDH, SHRENDL

This register pair, share end line HI, share end line LO, contains a 9-bit address, which specifies the ending horizontal line to be used from the shared video frame buffer memory. SHREND HI contains only 1 bit, which resides in the LSB position (bit 0) of the SHREND HI register. The lower 8 bits of the 9-bit address are specified by SHREND LO. Valid shared line numbers range from 0 to 483 visible NTSC (511 PAL). The ASYNC flag in the channel status register controls the time of actual update, either immediate (asynchronous) or video field synchronous. To allow the entire value to be changed at once, the internal value of SHREND (which uses both SHRENDH and SHRENDL) is not updated until SHRENDL is written. A write to SHRENDH alone does not trigger an update of the internal SHREND value.

### **Detailed Description of the Multichannel Block Registers**

### QPH, QPL

Pixel data is read/written 16 bits at a time to the quad pixel registers due to the SDRAM memory organization. The most significant 4 bits (nybble) of QPH represents the leftmost pixel and the least significant 4 bits of QPL represents the rightmost pixel (4 bits per pixel). Table 1 shows pixel data mapping. QPH and QPL for the multichannel block is read/written the same as the individual channel-N register function, except multichannel pixel data is used for multiple write operations to selected channels.

**QPHORIZ**

This 8-bit value is the address of the guad pixel within the line specified by QPLINE HI and QPLINE LO. A zero value in QPHORIZ addresses the leftmost displayed guad pixel in the specified line and increasing QPHORIZ addresses indexes towards the right-hand side of the video screen. This register addresses multichannel write operations. Valid values range from zero to 177. Write a 1 in the HINC bit of the multichannel CONTROL register to enable autoincrement of QPHORIZ. QPHORIZ autoincrement saturates at 177.

### **QPLINEH. QPLINEL**

This 9-bit address specifies the horizontal line of the quad pixel to be accessed (host read or write). QPLINE HI is only 1 bit that resides in the LSB (bit 0) of the QPLINE HI register. The lower 8 bits of the 9-bit address are specified by QPLINE LO. Valid displayed line numbers range from 0 to 483 NTSC (511 PAL). This register is used for addressing for multichannel write operations. Write a 1 in the VINC bit of the channel CONTROL register to enable autoincrement of QPLINE\_. QPLINE\_ autoincrement saturates at 511.

### LOSALL

This register is common to all eight channels and reflects the status of sync presence on each of the eight VIDIN\_ inputs. If valid composite sync is present at each of the eight VIDIN\_ inputs, this register contains all zeros. If any channel loses sync for more than one horizontal line period, a flag is set for that respective

channel indicating sync loss. Normally, the host processor polls this register periodically and checks for nonzero flag bits, indicating loss of video on any or all channels. This feature detects vandalism, security threats, or simple camera/link failure. The loss of sync register is described below:

| BIT7 |     |     |        |              |               |                  | BIT0          |

|------|-----|-----|--------|--------------|---------------|------------------|---------------|

| Ch7  | Ch6 | Ch5 | Ch4    | Ch3          | Ch2           | Ch1              | Ch0           |

|      |     |     | MWRITE | multiple cha | nnels (i.e. t | ime of day, etc. | ) Writing a 1 |

#### **MWRITE**

Multiple write command register. Trigger multiple write operations to OSD frame buffer memory by writing to MWRITE, specifying which channels should receive data. This is useful in updating graphics common to

| multiple channels (i.e., time of day, etc.). Writing a f     |

|--------------------------------------------------------------|

| triggers writes to the desired channel as defined below.     |

| This register autoclears itself after a multiple write cycle |

| completes. The multiple write register is described          |

| below:                                                       |

|                                                              |

| BIT7 |     |     |     |     |     |     | BIT0 |

|------|-----|-----|-----|-----|-----|-----|------|

| Ch7  | Ch6 | Ch5 | Ch4 | Ch3 | Ch2 | Ch1 | Ch0  |

### Control

Control bits for the multichannel block register. VINC, when set to 1, enables autoincrement of QPLINEH/L in the multichannel block after each host multichannel write to OSD memory. HINC, when set to 1, enables autoincrement of QPHORIZ in the multichannel block after each host multichannel write operation to OSD buffer memory. The control register is described below:

| BIT7 |   |   |      |      |   |   | BIT0 |

|------|---|---|------|------|---|---|------|

| 0    | 0 | 0 | VINC | HINC | 0 | 0 | 0    |

**MAX4455**

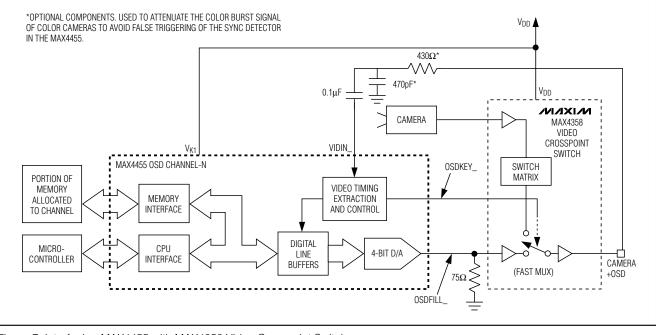

Figure 7. Interfacing MAX4455 with MAX4358 Video Crosspoint Switch

## \_Applications Information

### Interfacing to Maxim Video Crosspoint Switches

The MAX4455 interfaces directly to MAX4356/MAX4358 video crosspoint switches with OSD insertion function (Figure 7). The MAX4455 OSDKEY\_ and OSDFILL\_ outputs connect directly to the OSDKEY\_ and OSDFILL\_ inputs on the MAX4356/MAX4358 and utilize the internal fast mux in the MAX4356/MAX4358 to implement the OSD insertion. To ensure correct video timing, the MAX4455 VIDIN\_ input senses and extracts the video timing directly from the crosspoint switch output.

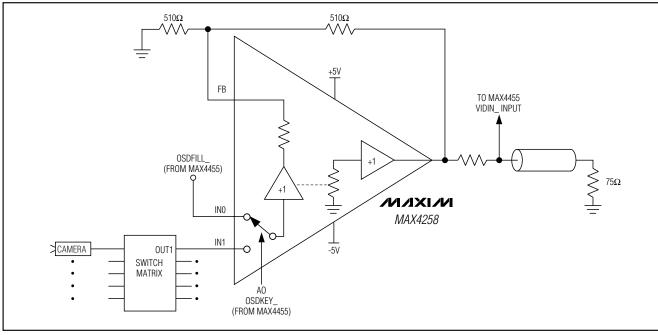

### Interfacing the MAX4455 with a Fast Mux Switch

The MAX4455 interfaces directly to a fast mux switch, as shown in Figure 8. Choose a device with a switch time of less than 30ns, such as the MAX4258, for accurate OSD insertion. The MAX4258 is a single-channel wideband video amplifier with input multiplexing and a channel-to-channel switching time of 20ns. Configure the amplifier using external resistors for a 6dB gain to drive a 75 $\Omega$  back-terminated video line. Connect the OSDFILL\_output of the MAX4455 to IN0 of the MAX4258 and connect the video source (camera output) to IN1. Connect the OSDKEY\_ output of the MAX4258. When the OSDKEY\_ signal

is low, the OSDFILL\_ analog signal on channel INO passes through the mux and the OSD information is inserted into the video image. When the OSDKEY\_ signal is high, the camera video output passes through the mux and is displayed on the monitor.

### Channel Blanking During Video Input Source Switching

Before switching input video sources on a channel with active OSD, set the BLANK bit to 1 in the channel status register to prevent OSDKEY assertion during the video blanking interval. Failure to blank the OSD prior to switching input video sources can cause OSD information to be inserted over the new video input's vertical blanking interval, resulting in a loss of sync on that channel. The MAX4455 timing synchronizes to the video output of the channel, such that switching another asynchronous input video source can cause writing of OSD information over the new video source with unpredictable results (i.e., OSD insertion over the vertical blanking interval).

The channel blanking procedure follows:

- 1) Set BLANK = 1.

- 2) Switch camera/video source input.

- 3) Set BLANK = 0.

Figure 8. Interfacing MAX4455 with a Fast Mux Switch

The result of writing OSD over the vertical blanking interval is a rolling picture that the display monitor cannot sync to, and the MAX4455 loss-of-sync flag is set for that channel. Reestablish sync by blanking the channel's OSD for at least one full video frame period, allowing the MAX4455's sync timing circuitry to correctly sense the new video source's timing, and reset the LOS flag.

### Optimizing OSDFILL Load Termination and RRSET

The MAX4455 provides standard 100 IRE (0.714V) fullscale OSDFILL\_ output levels with  $R_{RSET} = 11.75k\Omega$  and OSDFILL\_ terminated with  $R_{OSDFILL} = 75\Omega$  to AGND. The MAX4455 OSDFILL\_ outputs can drive as high as 1.5V by selecting a lower  $R_{RSET}$  value, or increasing the value of  $R_{OSDFILL}$ , or a combination of both. OSDFILL output levels higher than 0.714V can have increased distortion and degraded linearity (see the *OSDFILL\_ Reference Voltage (RSET)* section).

### **SDRAM Memory Selection**

The MAX4455 EV kit uses the Micron MT48LC1M16TG-7S SDRAM. The MAX4455 has not been tested with, but is designed to operate with the following SDRAMS: Micron MT48LC1M16A1-8 or faster, VIS VG3617161DT-8 or faster, Hyundai HY57V161610D or HY57V161610C, Mitsubishi M2V64S40DTP, Micron MT48LC4M16A2, and Hitachi HM5264165F.

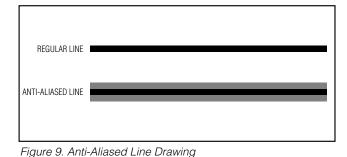

### **Anti-Aliasing and Flicker**

The MAX4455 is a high-resolution graphics system capable of accurately displaying a single pixel line. A line with the height of one pixel, by definition, occurs only on one of the two interlaced fields that make up the standard interlaced video signal. Since the interlaced system has a frame rate of about 60Hz, the field rate is half of this (30Hz). Any object occurring only on one field is displayed at a 30Hz rate, resulting in a flickering image. Any signal displayed at less than a 50Hz rate is perceived to visibly flicker. The slower the display rate is, the higher the perceived flicker.

The amount of flicker in a one-pixel-high horizontal line is dependent on the length of the line. The flicker associated with very short lines that are part of another shape are typically very minimal. For example, the flicker of the legs of the letter F is almost imperceptible. At the other extreme, a one-pixel horizontal line that spans the width of a display exhibits flicker that can be very noticeable.

The perceived flicker due to thin horizontal lines can be minimized by making the line thicker or by using antialiasing techniques. For the best results, these two

### techniques can be used in conjunction. A thicker line exhibits much less of the flicker effect. Once the line is from five to six lines thick, the additional improvement from thicker lines is negligible.

Anti-aliasing is a fairly well-known technique that involves decreasing the severity of the transition of the graphic or font structure. Here, it involves bracketing a horizontal line with two or more other lines that have a relative brightness that is between the brightness level of the line and the background. This is illustrated in Figure 9.

The proper application of this technique softens the look of the line, which can be undesirable in some cases. In general, it makes the display easier to read.

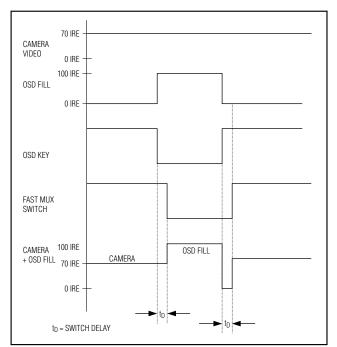

### **Finite Switch Time Effects**

The MAX4455 generates the OSDFILL\_ and OSDKEY\_ signals time coincident with each other within a few nanoseconds. Since the OSDKEY\_ signal controls when the external fast mux switch switches from normal camera video to the OSDFILL signal, any finite delay in the response time of this fast mux switch has an effect on the resulting OSD insertion (Figure 10).

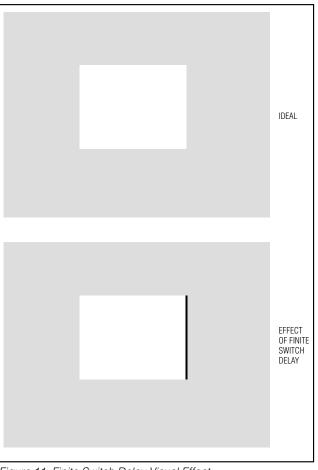

Due to the finite switching time of the fast mux switch, both the leading and trailing portions of the OSDFILL\_ are inserted slightly later in time. The leading edge does not create a visible artifact on the screen since it only shifts the image to the right an amount equal to the switch delay. The trailing edge of the OSDFILL\_ can result in a visible artifact because the OSDFILL\_ signal has already returned to 0 IRE before the fast mux switch can transition back to the camera video signal. This effect is shown in Figure 11.

In a typical NTSC system with a bandwidth of 4.2MHz, the narrowest resolved image is about 120ns wide. If the delay of the fast mux switch is less than half of this, 60ns or less, no visible artifact should be seen on the display.

The displayed information can be designed to dramatically minimize the adverse effect of the finite switch time, if desired. For example, virtually all fonts and graphics that are overlayed on normal video need to be outlined for good readability. A very common technique is to use white structures with a black outline border. To compensate for the above finite switch time effect, construct the graphic or font with a thinner trailing edge. When displayed, it looks symmetrical with the trailing edge appearing normal. Figure 12 illustrates this technique.

#### **Memory Sharing** Memory sharing is a feature that reduces the host processor burden for tasks such as time-stamp update. The MAX4455 supports user-specified starting and ending lines to be shared by any number of channels. In Figure 13, the time stamp is written only to channel 0 on line start through line end. Graphics data stored in lines outside of start and end remain unique for each of

In Figure 13, channel 0's start line number through end line number are duplicated onto channel 2 and channel 4's display. The source of shared data is defined in the SHRSHC register (see the *MAX4455 Registed Description* section). For example, channel 15 can be programmed to display channel 7's graphics beginning at channel 7 start line #n through end line #m, etc.

the eight video channels (Figure 13).

Sharing is restricted to even channels with even channels and odd channels with odd channels. For example, channels 1, 3, 5, 7 can share lines and channels 0, 2, 4, 6 can share lines in any combination.

### **Power Supplies and Bypassing**

The MAX4455 operates from a single 2.7V to 5.5V analog supply and a 3V to 3.6V digital supply. Additional logic supplies for host  $\mu P$  interface (V<sub>H1</sub>) and the OSDKEY\_ interface (V<sub>K1</sub>) allow the MAX4455 to interface with other logic supplies from 2.7V to 5.5V. Bypass each supply pin with a 0.1 $\mu F$  capacitor to ground.

### Layout Concerns

For best performance, make the OSDFILL\_ and OSD-KEY\_ output traces as short as possible, and place the 75 $\Omega$  termination resistor close to the crosspoint switch OSDFILL\_ input with the resistor terminated to the solid analog ground plane. The SDRAM interface is the highest speed connection and therefore requires careful layout. Place the SDRAM close to the MAX4455 to minimize trace lengths. The MAX4455 pinout is optimized for memory bus trace routing to the SDRAM without crossing traces. Refer to the MAX4455 EV kit for a proven PC board layout.

Figure 10. Finite Switch Time Effects

Figure 11. Finite Switch Delay Visual Effect

Figure 12. Compensated Graphics Example

# **MAX4455**

## **Programming Examples**

The MAX4455 EV kit provides a high-level user interface with free-hand drawing, bit-mapped graphics, and text-insertion tools. Listings 1 through 5 show some pseudocode examples based on the MAX4455 EV kit source code for low-level register access, line drawing, RGB-to-gray-scale conversion, and block memory transfer to the OSD.

## Listing 1. Constant Definitions

| <pre>// MAX4455 per-channel registers<br/>const unsignedint8 ch_QPH = 0x00; // quad pixel high (msb = left pixel)<br/>const unsignedint8 ch_QPHORIZ = 0x02; // quad pixel horizontal address 0.177<br/>const unsignedint8 ch_QPLINEL = 0x02; // quad pixel line address 0.483 (511 PAL)<br/>const unsignedint8 ch_QPLINEL = 0x04; // low byte of QPLINE<br/>const unsignedint8 ch_STATUS = 0x05; // status (0 0 0 VINC HINC ASYNC BLANK LOS )<br/>const unsignedint8 ch_STATUS = 0x05; // status (0 0 0 VINC HINC ASYNC BLANK LOS )<br/>const unsignedint8 ch_STATUS_HINC = 0x10; // auto-increment vertical<br/>const unsignedint8 ch_STATUS_BLANK = 0x02; // supress on-Screen display<br/>const unsignedint8 ch_STATUS_BLANK = 0x02; // supress on-Screen display<br/>const unsignedint8 ch_STATUS_BLANK = 0x02; // supress on-Screen display<br/>const unsignedint8 ch_COMMAND_EALD = 0x01; // (read-only) loss of sync<br/>const unsignedint8 ch_COMMAND_REALD = 0x02;<br/>const unsignedint8 ch_COMMAND_REALD = 0x02;<br/>const unsignedint8 ch_COMMAND_REALD = 0x02;<br/>const unsignedint8 ch_SHRESCH = 0x02;<br/>const unsignedint8 ch_SHRESCH = 0x02; // shared buffer source<br/>const unsignedint8 ch_SHRESCH = 0x02; // shared buffer source<br/>const unsignedint8 ch_SHRESCH = 0x02; // shared buffer source<br/>const unsignedint8 ch_SHRESCH = 0x02; // shared buffer end line<br/>const unsignedint8 ch_SHRESCH = 0x02; // shared buffer end line<br/>const unsignedint8 ch_SHRESCH = 0x00; //<br/>// // MAX4455 channel register banks<br/>const unsignedint8 CH_regs = 0x10; // register base for channel 0 registers<br/>const unsignedint8 CH_regs = 0x20; // register base for channel 1 registers<br/>const unsignedint8 CH_regs = 0x20; // register base for channel 1 registers<br/>const unsignedint8 CH_regs = 0x20; // register base for channel 3 registers<br/>const unsignedint8 CH_regs = 0x20; // register base for channel 3 registers<br/>const unsignedint8 CH_regs = 0x20; // register base for channel 7 registers<br/>const unsignedint8 CH_regs = 0x50; // register base for channel 7 registers<br/>const unsignedint</pre> | //                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| <pre>const unsignedint8 ch_QPH = 0x00; // quad pixel high (msb = left pixel)<br/>const unsignedint8 ch_QPL = 0x01; // quad pixel low (lsb = right pixel)<br/>const unsignedint8 ch_QPLINEH = 0x02; // quad pixel horizontal address 0.177<br/>const unsignedint8 ch_QPLINEH = 0x03; // quad pixel horizontal address 0.483 (511 PAL)<br/>const unsignedint8 ch_QPLINEH = 0x03; // quad pixel horizontal address 0.483 (511 PAL)<br/>const unsignedint8 ch_QPLINEH = 0x03; // quad-pixel line address 0.483 (511 PAL)<br/>const unsignedint8 ch_STATUS = 0x05; // status { 0 0 0 VINC HINC ASYNC BLANK LOS }<br/>const unsignedint8 ch_STATUS_HINC = 0x00; // auto-increment vertical<br/>const unsignedint8 ch_STATUS_ASYNC = 0x04; // asynchronous write<br/>const unsignedint8 ch_STATUS_LOS = 0x01; // (read-only) loss of sync<br/>const unsignedint8 ch_COMMAND = 0x06; // command { 0 0 0 0 0 0 0 WRITE READ }<br/>const unsignedint8 ch_COMMAND = 0x06; // command { 0 0 0 0 0 0 0 WRITE READ }<br/>const unsignedint8 ch_COMMAND_WRITE = 0x02;<br/>const unsignedint8 ch_COMMAND_WRITE = 0x02;<br/>const unsignedint8 ch_COMMAND_WRITE = 0x02;<br/>const unsignedint8 ch_SHREET = 0x07; // horizontal offset (128U = zero offset)<br/>const unsignedint8 ch_SHREET = 0x08; // vertical offset (128U = zero offset)<br/>const unsignedint8 ch_SHREET = 0x00; // shared buffer source<br/>const unsignedint8 ch_SHREED = 0x00; // shared buffer source<br/>const unsignedint8 ch_SHREED = 0x00; // shared buffer end line<br/>const unsignedint8 ch_SHREED = 0x00; //<br/>// MAX4455 channel register banks<br/>const unsignedint8 Ch_SHREED = 0x00; //<br/>// MAX4455 channel register banks<br/>const unsignedint8 CH3_regs = 0x10; // register base for channel 0 registers<br/>const unsignedint8 CH3_regs = 0x20; // register base for channel 1 registers<br/>const unsignedint8 CH3_regs = 0x20; // register base for channel 3 registers<br/>const unsignedint8 CH3_regs = 0x20; // register base for channel 3 registers<br/>const unsignedint8 CH3_regs = 0x20; // register base for channel 4 registers<br/>const unsignedint8 CH4_regs = 0x2</pre>  | // MAX4455 per-channel registers                                                              |

| <pre>const unsignedint8 ch_OPHORIZ = 0x02; // quad pixel horizontal address 0.177 const unsignedint8 ch_OPLINEH = 0x03; // quad pixel horizontal address 0.483 (511 PAL) const unsignedint8 ch_OPLINEL = 0x04; // low byte of OPLINE const unsignedint8 ch_STATUS = 0x05; // status { 0 0 0 VINC HINC ASYNC BLANK LOS } const unsignedint8 ch_STATUS_VINC = 0x10; // auto-increment vertical const unsignedint8 ch_STATUS_VINC = 0x04; // auto-increment vertical const unsignedint8 ch_STATUS_HINC = 0x02; // supress on-screen display const unsignedint8 ch_STATUS_BLANK = 0x02; // supress on-screen display const unsignedint8 ch_STATUS_LOS = 0x01; // (red-only) loss of sync const unsignedint8 ch_COMMAND = 0x06; // command { 0 0 0 0 0 0 WRITE READ } const unsignedint8 ch_COMMAND = 0x01; // (red-only) loss of sync const unsignedint8 ch_COMMAND = 0x01; // command { 0 0 0 0 0 0 WRITE READ } const unsignedint8 ch_COMMAND = 0x01; // horizontal offset (128U = zero offset) const unsignedint8 ch_OPFSET = 0x07; // horizontal offset (128U = zero offset) const unsignedint8 ch_SHREGH = 0x04; // shared buffer source const unsignedint8 ch_SHREGH = 0x00; // shared buffer source const unsignedint8 ch_SHREDEL = 0x00; // shared buffer pegining line const unsignedint8 ch_SHREDEL = 0x00; // MAX4455 channel register bank const unsignedint8 ch_SHREDEL = 0x00; // shared buffer end line const unsignedint8 ch_SHRENDE = 0x00; // register base for channel 0 registers const unsignedint8 CH0_regs = 0x10; // register base for channel 1 registers const unsignedint8 CH2_regs = 0x20; // register base for channel 1 registers const unsignedint8 CH2_regs = 0x20; // register base for channel 1 registers const unsignedint8 CH3_regs = 0x30; // register base for channel 1 registers const unsignedint8 CH3_regs = 0x30; // register base for channel 3 registers const unsignedint8 CH3_regs = 0x30; // register base for channel 5 registers const unsignedint8 CH3_regs = 0x30; // register base for chan</pre>                                                                                                                   |                                                                                               |

| <pre>const unsignedint8 ch_QPLINEH = 0x03; // quad pixel line address 0.483 (511 PAL)<br/>const unsignedint8 ch_QPLINEL = 0x04; // low byte of QPLINE<br/>const unsignedint8 ch_STATUS = 0x05; // status { 0 0 0 VINC HINC ASYNC BLANK LOS }<br/>const unsignedint8 ch_STATUS_VINC = 0x10; // auto-increment vertical<br/>const unsignedint8 ch_STATUS_HINC = 0x08; // auto-increment horizontal<br/>const unsignedint8 ch_STATUS_BLANK = 0x02; // supress on-screen display<br/>const unsignedint8 ch_STATUS_LOS = 0x01; // (read-only) loss of sync<br/>const unsignedint8 ch_COMMAND = 0x06; // command { 0 0 0 0 0 0 WRITE READ }<br/>const unsignedint8 ch_COMMAND = 0x06; // command { 0 0 0 0 0 0 WRITE READ }<br/>const unsignedint8 ch_COMMAND = 0x00; // command { 0 0 0 0 0 0 WRITE READ }<br/>const unsignedint8 ch_COMMAND wRITE = 0x02;<br/>const unsignedint8 ch_COMMAND_WRITE = 0x02;<br/>const unsignedint8 ch_COMMAND_READ = 0x01;<br/>const unsignedint8 ch_OFFSET = 0x07; // horizontal offset (128U = zero offset)<br/>const unsignedint8 ch_SHRESC = 0x09; // shared buffer source<br/>const unsignedint8 ch_SHREGE = 0x00; // shared buffer source<br/>const unsignedint8 ch_SHREGE = 0x00; // shared buffer beginning line<br/>const unsignedint8 ch_SHREBEL = 0x00; // shared buffer end line<br/>const unsignedint8 ch_SHRENDH = 0x0C; // shared buffer end line<br/>const unsignedint8 CH0_regs = 0x00; // register base for channel 0 registers<br/>const unsignedint8 CH0_regs = 0x00; // register base for channel 1 registers<br/>const unsignedint8 CH0_regs = 0x00; // register base for channel 1 registers<br/>const unsignedint8 CH3_regs = 0x20; // register base for channel 3 registers<br/>const unsignedint8 CH3_regs = 0x30; // register base for channel 3 registers<br/>const unsignedint8 CH4_regs = 0x40; // register base for channel 4 registers<br/>const unsignedint8 CH4_regs = 0x50; // register base for channel 4 registers<br/>const unsignedint8 CH5_regs = 0x50; // register base for channel 6 registers<br/>const unsignedint8 CH5_regs = 0x50; // register base for channel 7 registers<br/>co</pre>      | const unsignedint8 ch_QPL = 0x01; // quad pixel low (lsb = right pixel)                       |