|                                                    |              |        |      |                  |      |               | F   | REVISI | IONS |    |                 |       |        |          |     |      |              |        |    |

|----------------------------------------------------|--------------|--------|------|------------------|------|---------------|-----|--------|------|----|-----------------|-------|--------|----------|-----|------|--------------|--------|----|

| LTR                                                |              |        |      | D                | ESCR | IPTIO         | N   |        |      |    |                 | D/    | ATE (Y | 'R-MO-I  | DA) |      | APPF         | ROVE   | )  |

| A Add de                                           | evice        | type ( | 02.  |                  |      |               |     |        |      |    |                 |       | 98-1   | 2-10     |     | ŀ    | (. A. C      | ottong | im |

|                                                    |              |        |      |                  |      |               |     |        |      |    |                 |       |        |          |     |      |              |        |    |

| REV A                                              | ΑТ           | А      | Α    | А                | Α    | Α             | Α   | Α      | А    | А  | А               | А     | А      | А        | ΙA  | A    | A            | А      |    |

| <del>                                     </del>   | 36           | 37     | 38   | 39               | 40   | 41            | 42  | 43     | 44   | 45 | 46              | 47    | 48     | 49       | 50  | 51   | 52           | 53     |    |

|                                                    | A            | А      | Α    | Α                | Α    | Α             | Α   | Α      | Α    | Α  | Α               | Α     | A      | Α        | Α   | Α    | Α            | A      | А  |

| SHEET 15                                           | 16           | 17     | 18   | 19               | 20   | 21            | 22  | 23     | 24   | 25 | 26              | 27    | 28     | 29       | 30  | 31   | 32           | 33     | 34 |

| REV STATUS                                         |              |        | RE\  | /<br>/           |      | Α             | Α   | Α      | Α    | Α  | Α               | Α     | Α      | А        | А   | А    | А            | А      | Α  |

| OF SHEETS                                          |              | Ì      | SHE  | ET               |      | 1             | 2   | 3      | 4    | 5  | 6               | 7     | 8      | 9        | 10  | 11   | 12           | 13     | 14 |

| PMIC N/A                                           | _            |        |      | PARED<br>y Zahn  | ВҮ   |               |     |        |      | DE | FENS            |       | P. O.  | BOX      |     |      |              |        |    |

| STANDAR<br>MICROCIRC                               | UIT          | •      |      | CKED E           |      |               |     |        |      |    |                 |       |        | ,        |     |      |              |        |    |

| DRAWING THIS DRAWING IS AVA FOR USE BY AL          | AILABI<br>.L | LE     |      | ROVED<br>dall A. |      | gim           |     |        | (4)  |    | IRCUI<br>BIT) N |       |        |          |     |      | JAD,<br>3 VO | LT     |    |

| DEPARTMENTS<br>AND AGENCIES OF<br>DEPARTMENT OF DE | THE          | iΕ     | DRA  | WING A           |      | VAL D<br>3-23 | ATE |        | SIZE |    | CAG             | E COD |        |          |     |      | 075          |        |    |

| AMSC N/A                                           |              | j      | REVI | SION L           | EVEL |               |     |        | _    | 4  |                 | 726   |        | <u> </u> |     | 102· | 975          | )U/    |    |

| ĺ                                                  |              |        |      |                  |      |               |     |        |      |    |                 |       |        |          |     |      |              |        |    |

DSCC FORM 2233

APR 97

DISTRIBUTION STATEMENT A. Approved for public release; distribution is unlimited.

5962-E063-99

#### 1. SCOPE

- 1.1 <u>Scope</u>. This drawing documents five product assurance classes, class D (lowest reliability), class E, (exceptions), class G (lowest high reliability), class H (high reliability), and class K, (highest reliability) and a choice of case outlines and lead finishes are available and are reflected in the Part or Identifying Number (PIN). When available, a choice of radiation hardness assurance levels are reflected in the PIN.

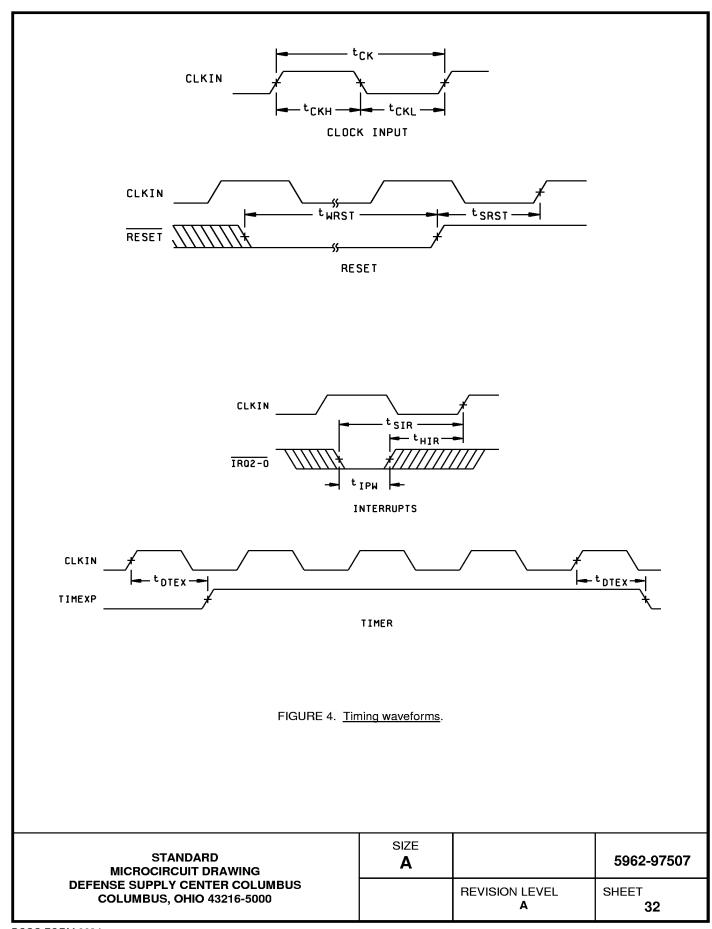

- 1.2 PIN. The PIN shall be as shown in the following example:

- 1.2.1 <u>Radiation hardness assurance (RHA) designator</u>. Device classes H and K RHA marked devices shall meet the MIL-PRF-38534 specified RHA levels and shall be marked with the appropriate RHA designator. A dash (-) indicates a non-RHA device.

- 1.2.2 <u>Device type(s)</u>. The device type(s) shall identify the circuit function as follows:

| Device type | Generic number   | Circuit function                                                                                                                                                                                                                                        |

|-------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 01          | AD14060LBF/QML-4 | Quad digital signal processor, +3.3 V supply, 40 MHz, Twelve, 40 megabyte/s link ports (3 from each processor),                                                                                                                                         |

| 02          | AD14060LTF/QML-4 | Four, 40 megabit/s independent serial ports (1 from each processor) Quad digital signal processor, +3.3 V supply, 37 MHz, Twelve, 37 megabyte/s link ports (3 from each processor), Four, 37 megabit/s independent serial ports (1 from each processor) |

1.2.3 <u>Device class designator</u>. This device class designator shall be a single letter identifying the product assurance level as follows:

Device class

Device performance documentation

D, E, G, H, or K

Certification and qualification to MIL-PRF-38534

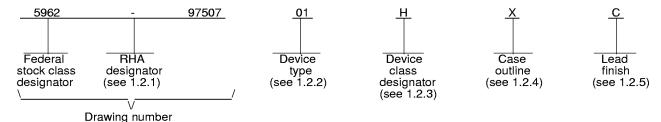

1.2.4 <u>Case outline(s)</u>. The case outline(s) shall be as designated in MIL-STD-1835 and as follows:

| Outline letter | Descriptive designator | <u>Terminals</u> | Package style          |

|----------------|------------------------|------------------|------------------------|

| X              | See figure 1           | 308              | Quad ceramic flat pack |

- 1.2.5 Lead finish. The lead finish shall be as specified in MIL-PRF-38534.

- 1.3 Absolute maximum ratings. 1/

| Supply voltage (V <sub>DD</sub> )                 | -0.3 V dc to +4.6 V dc                  |

|---------------------------------------------------|-----------------------------------------|

| Input voltage (V <sub>IN</sub> )                  | -0.5 V dc to V <sub>DD</sub> + 0.5 V dc |

| Output voltage swing (VOUT)                       | -0.3 V dc to VDD + 0.5 V dc             |

| Load capacitance                                  | 200 pF                                  |

| Junction temperature under bias (T <sub>I</sub> ) | +130°C                                  |

| Junction to case temperature $(\theta_{JC})$      | 0.36° C/W                               |

| Lead temperature soldering (5 seconds)            | +280°C                                  |

| Storage temperature range                         | -65°C to +150°C                         |

|                                                   |                                         |

Stresses above the absolute maximum rating may cause permanent damage to the device. Extended operation at the maximum levels may degrade performance and affect reliability.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                     | 5962-97507 |

|-------------------------------------------------------------|------------------|---------------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL<br>A | SHEET 2    |

| 1.4 Recommended operating conditions.               |                          |

|-----------------------------------------------------|--------------------------|

| Supply voltage (VDD):                               |                          |

| Device type 01                                      | +3.15 V dc to +3.6 V dc  |

| Device type 02                                      | +3.13 V dc to +3.47 V dc |

| Case operating temperature range (T <sub>C</sub> ): |                          |

| Device type 01                                      | -40° C to +100° C        |

| Device type 02                                      | -55°C to +125°C          |

|                                                     |                          |

# 2. APPLICABLE DOCUMENTS

2.1 <u>Government specification, standards, and handbook.</u> The following specification, standards, and handbook form a part of this drawing to the extent specified herein. Unless otherwise specified, the issues of these documents are those listed in the issue of the Department of Defense Index of Specifications and Standards (DoDISS) and supplement thereto, cited in the solitation.

#### **SPECIFICATION**

#### DEPARTMENT OF DEFENSE

MIL-PRF-38534 - Hybrid Microcircuits, General Specification for.

#### **STANDARDS**

#### DEPARTMENT OF DEFENSE

MIL-STD-883 - Test Methods and Procedures for Microelectronics.

MIL-STD-973 - Configuration Management. MIL-STD-1835 - Microcircuit Case Outlines.

#### **HANDBOOK**

#### DEPARTMENT OF DEFENSE

MIL-HDBK-780 - Standard Microcircuit Drawings.

(Unless otherwise indicated, copies of the specification, standards, and handbook are available from the Standardization Document Order Desk, 700 Robbins Avenue, Building 4D, Philadelphia, PA 19111-5094.)

2.2 <u>Order of precedence</u>. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing takes precedence. Nothing in this document, however, supersedes applicable laws and regulations unless a specific exemption has been obtained.

### 3. REQUIREMENTS

- 3.1 <u>Item requirements</u>. The individual item performance requirements for device classes D, E, G, H, and K shall be in accordance with MIL-PRF-38534. Compliance with MIL-PRF-38534 may include the performance of all tests herein or as designated in the device manufacturer's Quality Management (QM) plan or as designated for the applicable device class. Therefore, the tests and inspections herein may not be performed for the applicable device class (see MIL-PRF-38534). Futhermore, the manufacturers may take exceptions or use alternate methods to the tests and inspections herein and not perform them. However, the performance requirements as defined in MIL-PRF-38534 shall be met for the applicable device class.

- 3.2 <u>Design, construction, and physical dimensions</u>. The design, construction, and physical dimensions shall be as specified in MIL-PRF-38534 and herein.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                     | 5962-97507 |

|-------------------------------------------------------------|------------------|---------------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL<br>A | SHEET 3    |

- 3.2.1 Case outline(s). The case outline(s) shall be in accordance with 1.2.4 herein and figure 1.

- 3.2.2 Terminal connections. The terminal connections shall be as specified on figure 2.

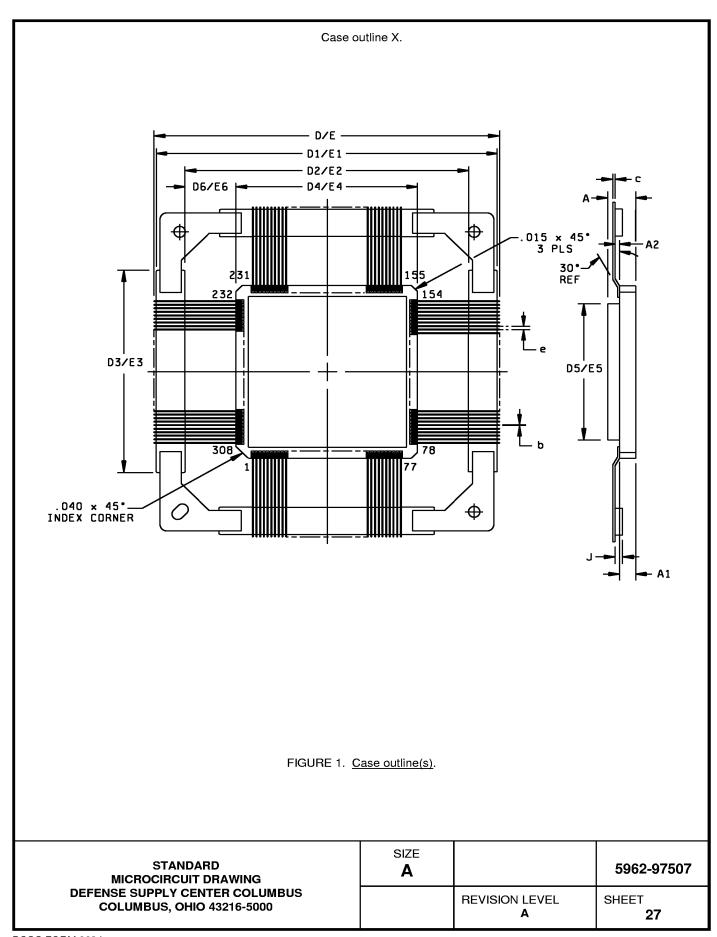

- 3.2.3 Block diagram(s). The block diagram(s) shall be as specified on figure 3.

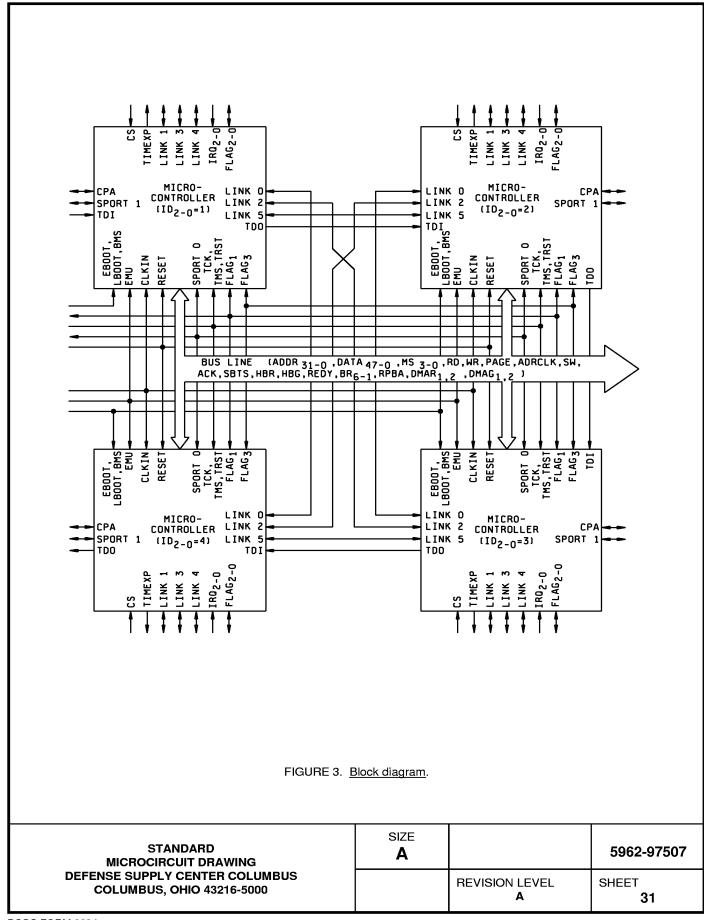

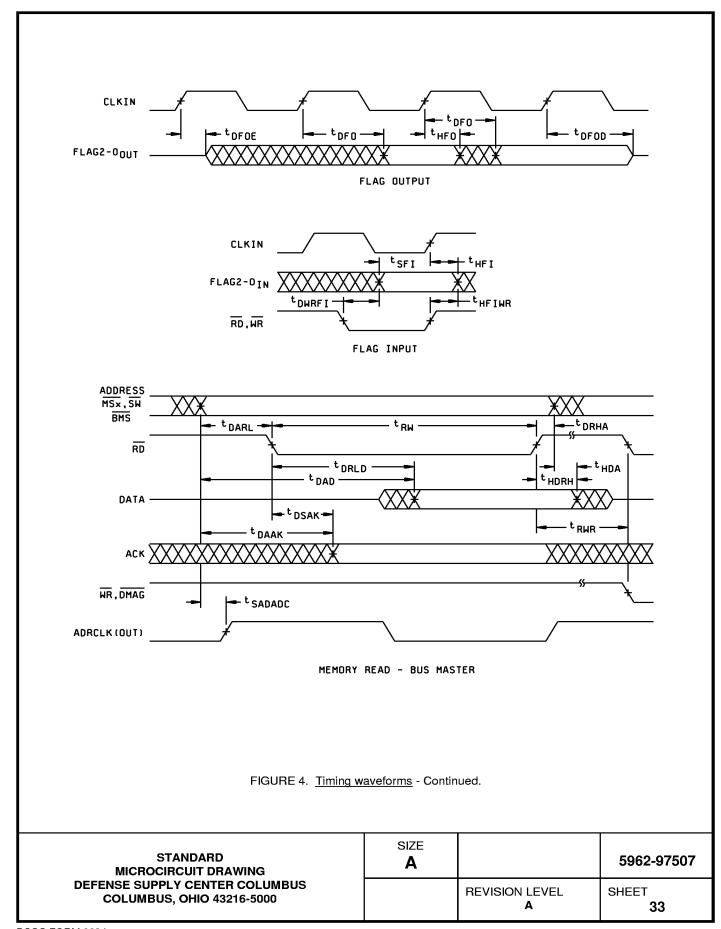

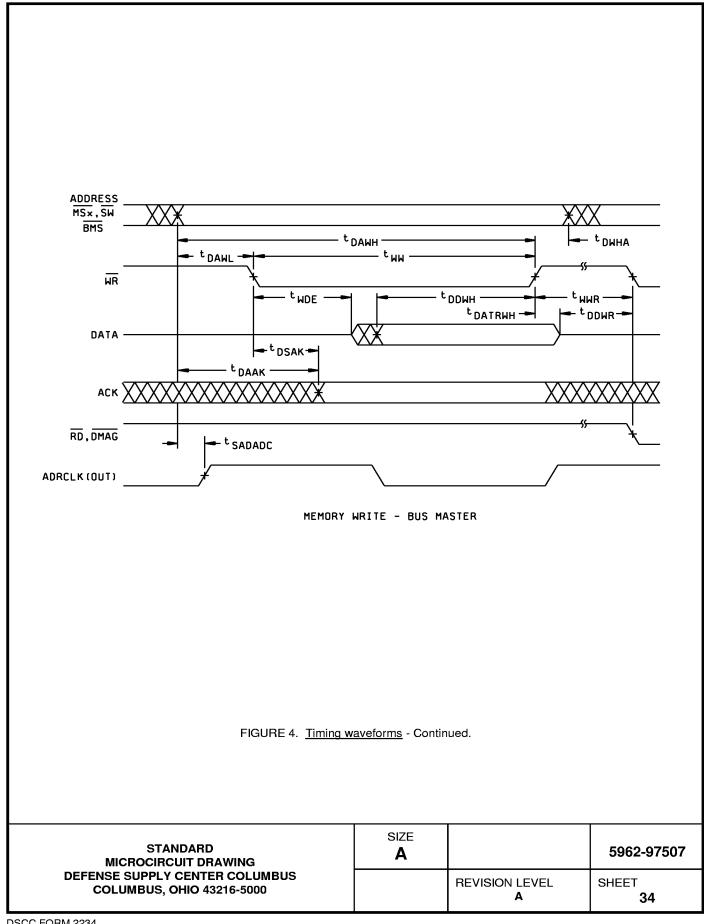

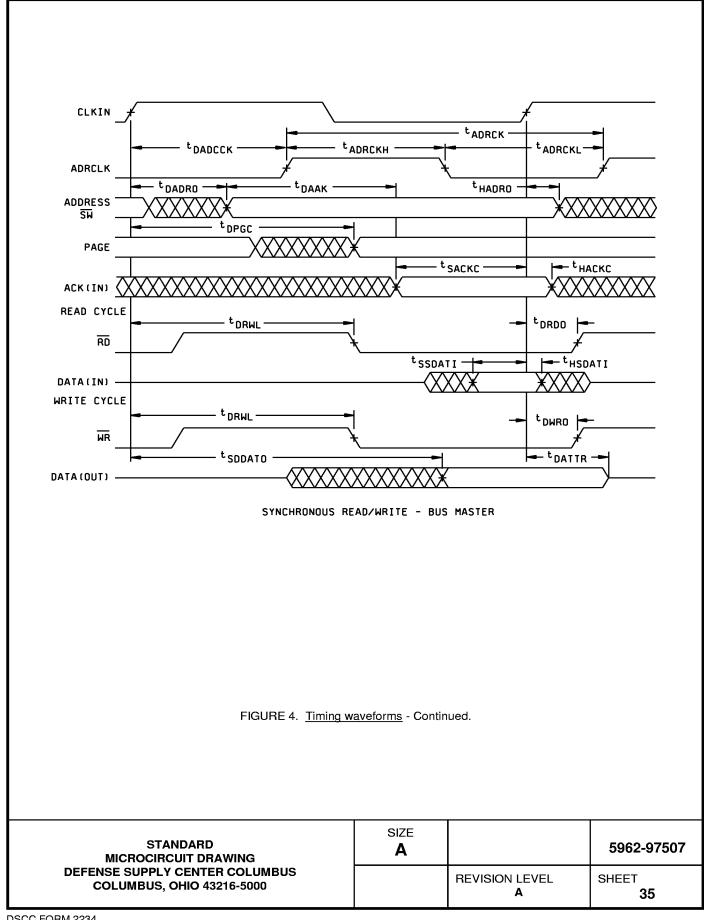

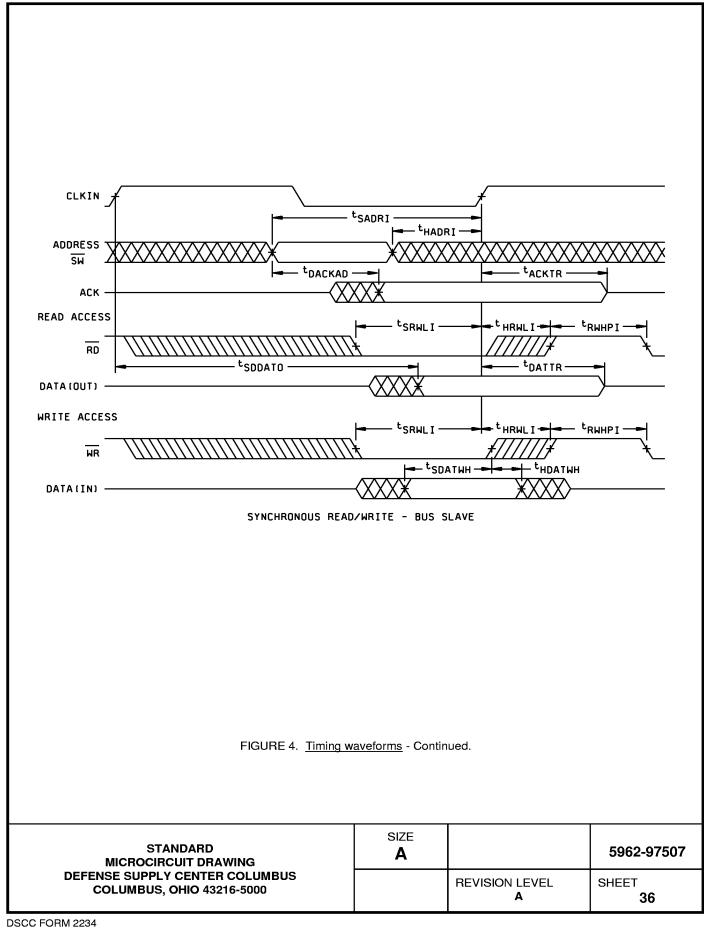

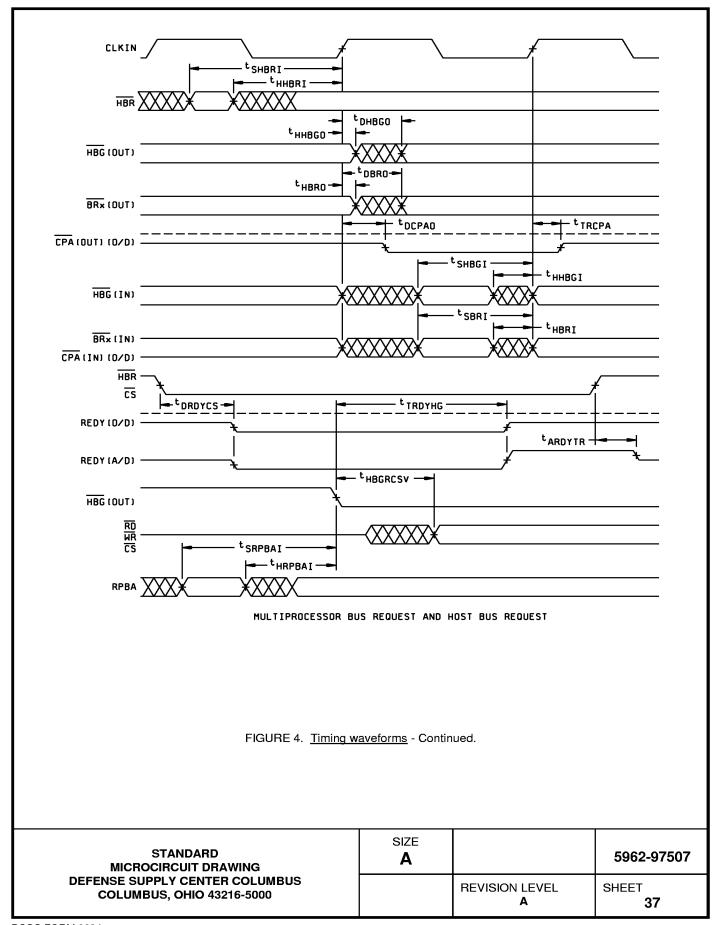

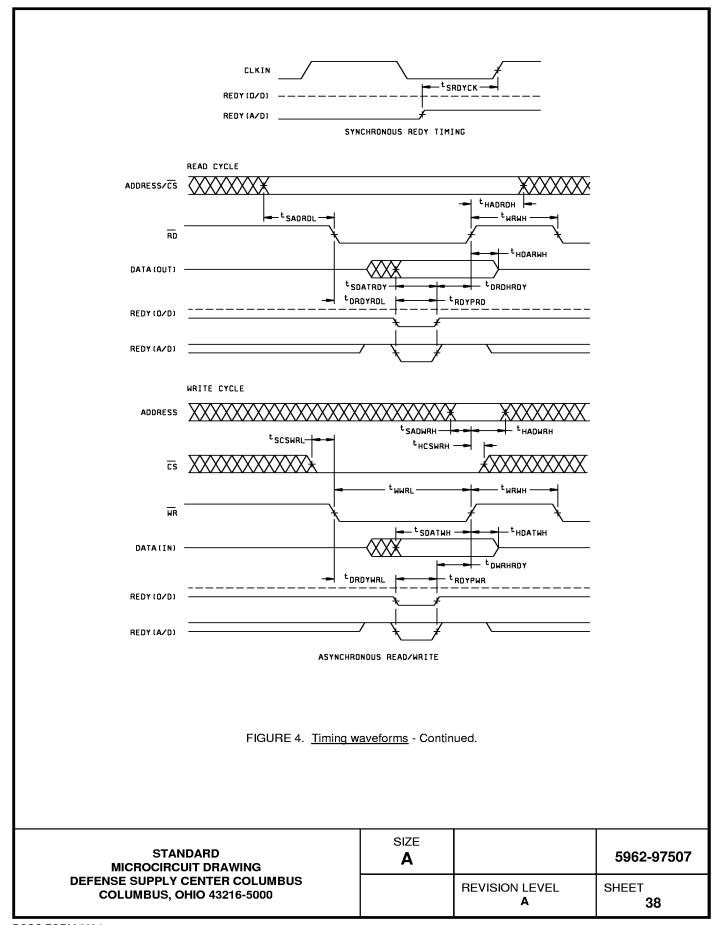

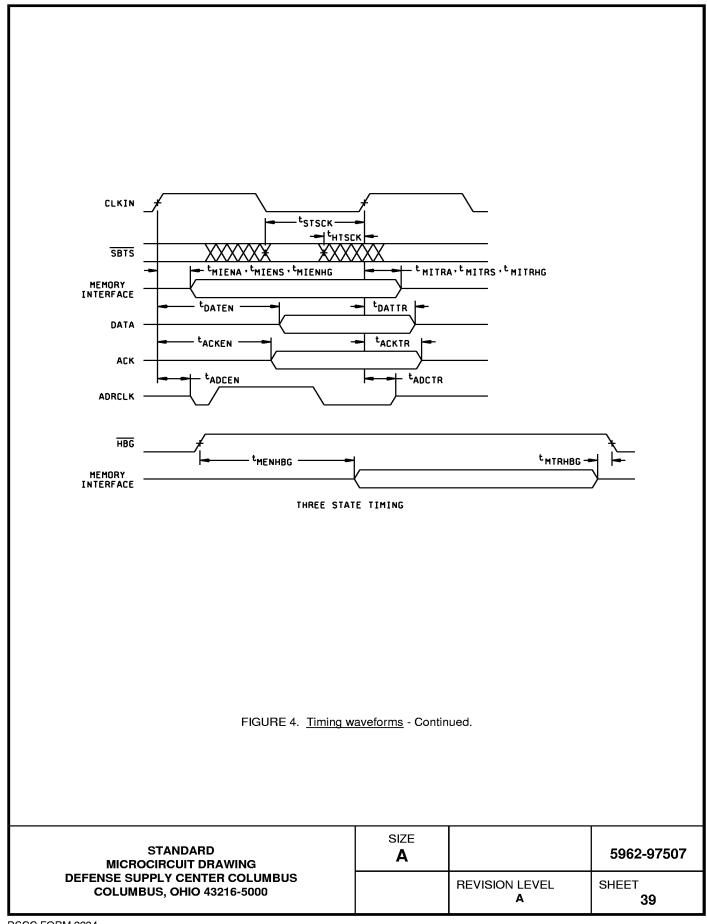

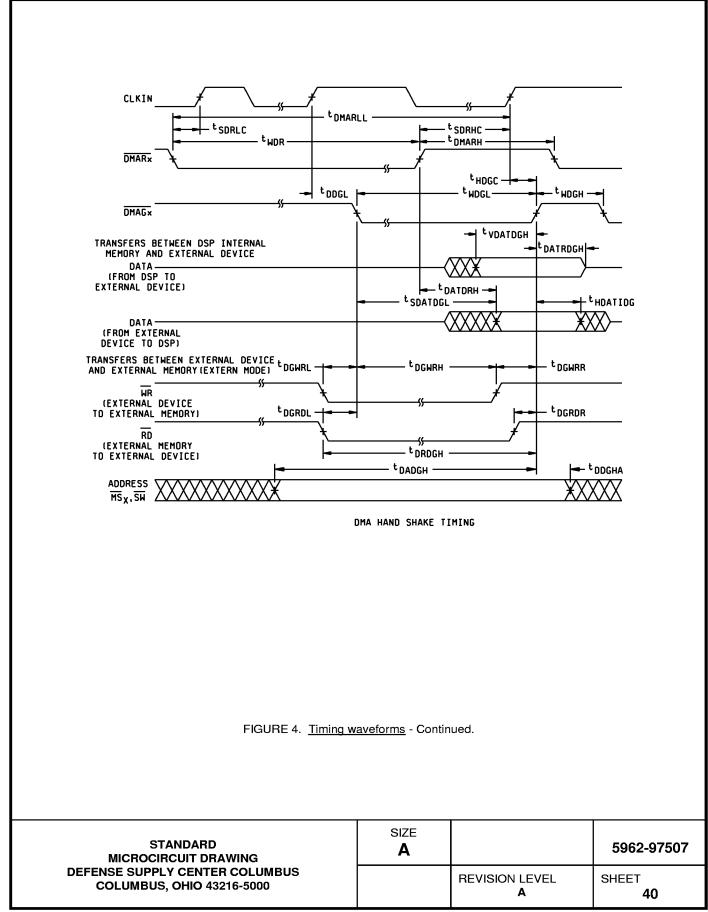

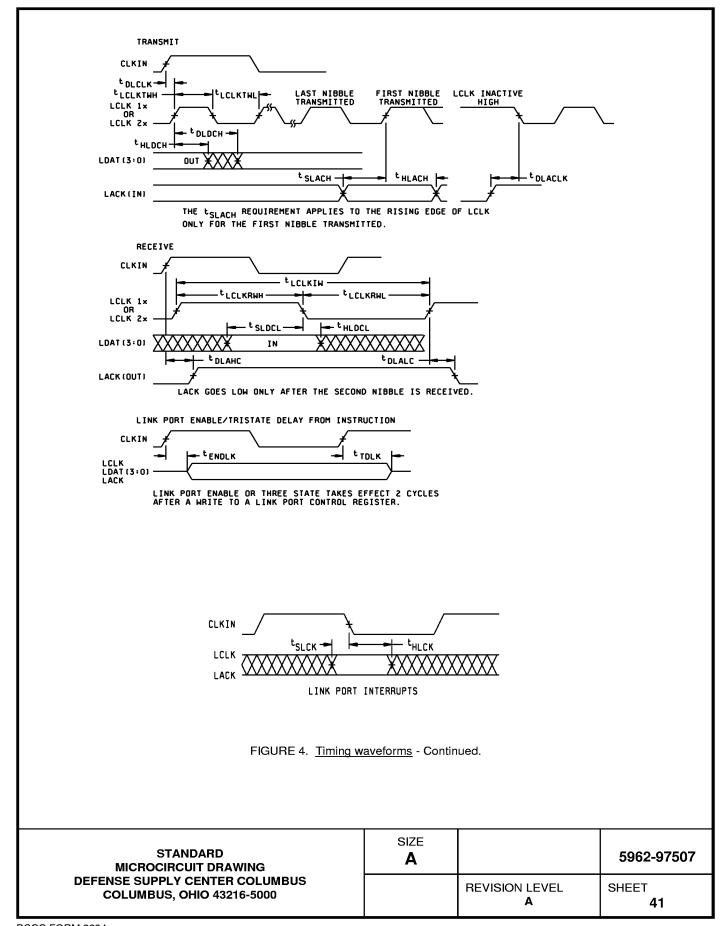

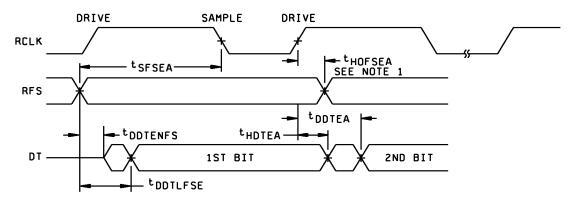

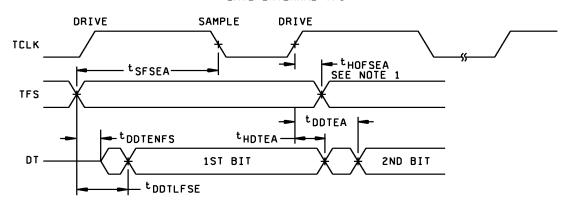

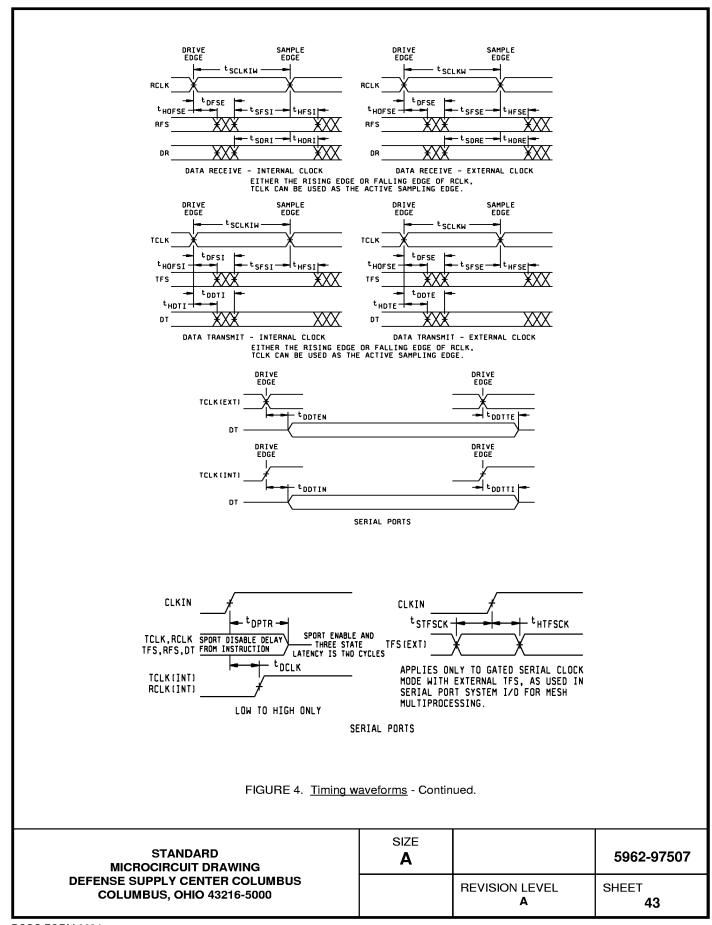

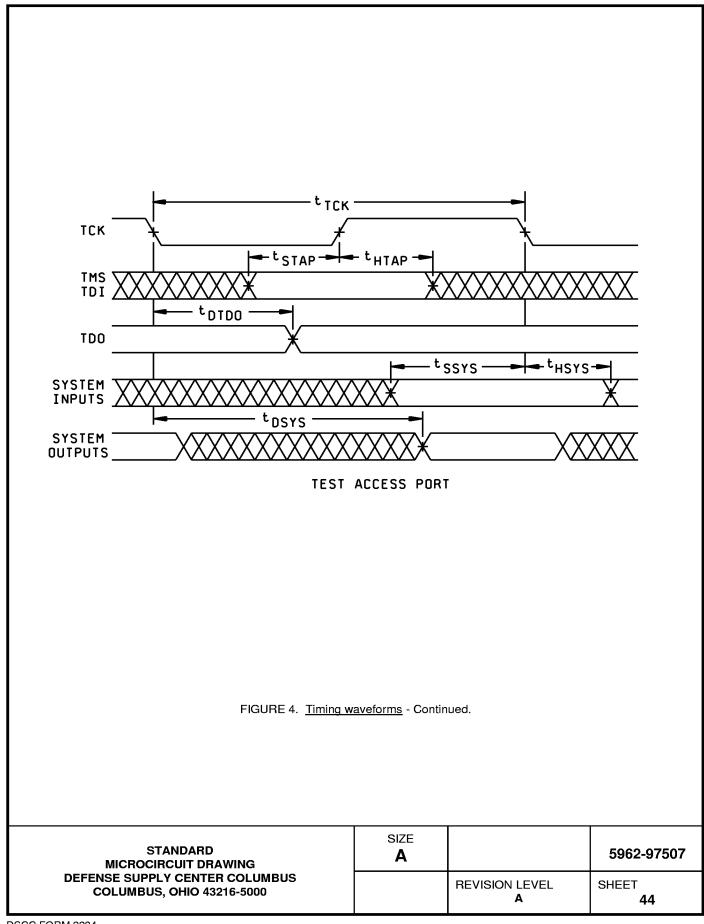

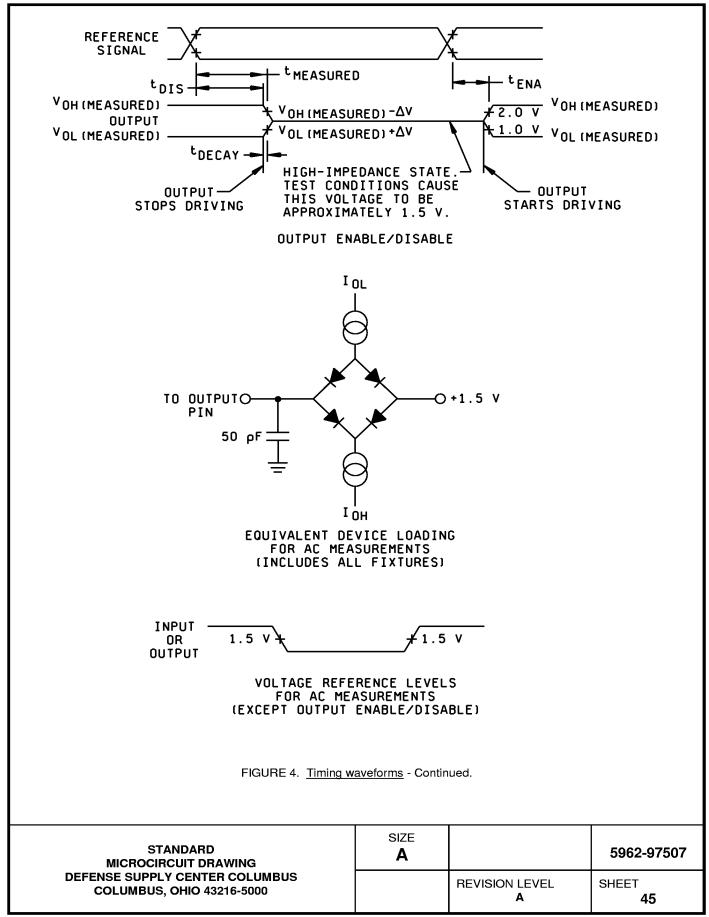

- 3.2.4 Timing waveform(s). The timing waveform(s) shall be as specified on figure 4.

- 3.3 <u>Electrical performance characteristics</u>. Unless otherwise specified herein, the electrical performance characteristics are as specified in table I and shall apply over the full specified operating temperature range.

- 3.4 <u>Electrical test requirements</u>. The electrical test requirements shall be the subgroups specified in table II. The electrical tests for each subgroup are defined in table I.

- 3.5 <u>Marking of Device(s)</u>. Marking of device(s) shall be in accordance with MIL-PRF-38534. The device shall be marked with the PIN listed in 1.2 herein. In addition, the manufacturer's vendor similar PIN may also be marked as listed in QML-38534.

- 3.6 <u>Data</u>. In addition to the general performance requirements of MIL-PRF-38534, the manufacturer of the device described herein shall maintain the electrical test data (variables format) from the initial quality conformance inspection group A lot sample, for each device type listed herein. Also, the data should include a summary of all parameters manually tested, and for those which, if any, are guaranteed. This data shall be maintained under document revision level control by the manufacturer and be made available to the preparing activity (DSCC-VA) upon request.

- 3.7 <u>Certificate of compliance</u>. A certificate of compliance shall be required from a manufacturer in order to supply to this drawing. The certificate of compliance (original copy) submitted to DSCC-VA shall affirm that the manufacturer's product meets the performance requirements of MIL-PRF-38534 and herein.

- 3.8 <u>Certificate of conformance</u>. A certificate of conformance as required in MIL-PRF-38534 shall be provided with each lot of microcircuits delivered to this drawing.

### 4. QUALITY ASSURANCE PROVISIONS

- 4.1 <u>Sampling and inspection</u>. Sampling and inspection procedures shall be in accordance with MIL-PRF-38534 or as modified in the device manufacturer's Quality Management (QM) plan. The modification in the QM plan shall not affect the form, fit, or function as described herein.

- 4.2 Screening. Screening shall be in accordance with MIL-PRF-38534. The following additional criteria shall apply:

- a. Burn-in test, method 1015 of MIL-STD-883.

- (1) Test condition A, B, C, or D. The test circuit shall be maintained by the manufacturer under document revision level control and shall be made available to either DSCC-VA or the acquiring activity upon request. Also, the test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in test method 1015 of MIL-STD-883.

- (2) T<sub>C</sub> as specified in accordance with table I of method 1015 of MIL-STD-883.

STANDARD

MICROCIRCUIT DRAWING

DEFENSE SUPPLY CENTER COLUMBUS

COLUMBUS, OHIO 43216-5000

SIZE

A

5962-97507

REVISION LEVEL

A

SHEET

4

- b. Interim test parameters shall be as specified in table II herein, except interim electrical parameter tests prior to burn-in are optional at the discretion of the manufacturer.

- (1) Static supply current (IDDq).

Checks that current draw is not grossly excessive. Current exceeding 1.3 amperes on the module indicates failure. Normal measured current is about 0.5 amperes.

(2) Interconnects.

Checks for electrical continuity through the package leads and wirebonds, along with continuity of internal wiring within the module.

(3) Single processor functional.

A collection of test routines perform a rudimentary check of the basic functionally of each individual processor. The following individual processor units are tested: DAGs 1 and 2, timer, program sequencer, PX register, multiplier, data register file, shifter, ALU, link ports, serial ports, DMA, IOP registers, and memory.

(a) Serial port test.

This routine uses internal loopback to test basic operation of serial port 0 and serial port 1, by transmitting and receiving 16-bit words. In addition, the COMPare operation of the ALU and BitSET operation of the shifter are tested. Serial ports are tested at a clock rate of 10 MHz.

(b) Computation routine.

The routine tests basic operation of the ALU through ADD, SUBTRACT, and COMPare functions. In addition, the multiplier and DAGs are tested usings floating point multiply and load/write functions, while the shifter is tested with a BitSET function. All operations use 32-bit words.

(c) Link routine.

Using 32-bit data and internal memory to memory receive, basic operation of Link buffers 0 - 5 is tested. In addition, the ALU, COMPare, and shifter BitSET functions are tested.

(d) PX routine.

This routine tests basic operation of the PX register and short word addressing. The PX register is loaded with a 48-bit word, then the PX is read into memory. Short word addressing is used to read back, in 16-bit word segments, the 48-bit word from memory. In addition, the ALU, COMPare, and shifter BitSET functions are tested.

(e) Timer routine.

This routine will count down the timer until  $t_{COUNT} = 0$ , at which time an interrupt will occur, followed by a return to the code. This test will verify operation of the program sequencer, timer, ALU, COMPare function, and shifter BitSET function.

- (4) Multiprocessor functional.

- (a) Interprocessor links: all tested using 2 times the clock rate (80 MHz for device type 01) and (74 MHz for device type 02).

- (b) Multiprocessor memory space: each processor accesses and checks memory of the other three processors.

- c. Final electrical test parameters shall be as specified in table II herein.

STANDARD

MICROCIRCUIT DRAWING

DEFENSE SUPPLY CENTER COLUMBUS

COLUMBUS, OHIO 43216-5000

SIZE

A

5962-97507

REVISION LEVEL

A

SHEET

5

|                                   | Т                | ABLE I. Electrical performance                                        | <u>characteristic</u> | <u>s</u> .      |     |      |      |

|-----------------------------------|------------------|-----------------------------------------------------------------------|-----------------------|-----------------|-----|------|------|

| Test                              | Symbol           | Conditions 1/                                                         | Group A subgroups     | Device<br>types | Lim | nits | Unit |

|                                   |                  | unless otherwise specified                                            |                       | <u> </u>        | Min | Max  |      |

| High level input voltage 2/       | V <sub>IH1</sub> | V <sub>DD</sub> = +3.6 V dc                                           | 1, 2, 3               | 01              | 2.0 |      | _ v  |

|                                   |                  | V <sub>DD</sub> = +3.47 V dc                                          |                       | 02              | 2.0 |      |      |

| High level input voltage 3/       | V <sub>IH2</sub> | V <sub>DD</sub> = +3.6 V dc                                           | 1, 2, 3               | 01              | 2.2 |      | V    |

|                                   |                  | V <sub>DD</sub> = +3.47 V dc                                          |                       | 02              | 2.2 |      |      |

| Low level input 2/3/voltage       | V <sub>IL</sub>  | V <sub>DD</sub> = +3.15 V dc                                          | 1, 2, 3               | 01              |     | 0.8  | V    |

|                                   |                  | V <sub>DD</sub> = +3.13 V dc                                          |                       | 02              |     | 0.8  |      |

| High level output voltage 4/      | VOH              | V <sub>DD</sub> = +3.15 V dc, <u>5/</u><br>I <sub>OH</sub> = -2.0 mA  | 1, 2, 3               | 01              | 2.4 |      | V    |

|                                   |                  | V <sub>DD</sub> = +3.13 V dc<br>I <sub>OH</sub> = -2.0 mA             |                       | 02              | 2.4 |      |      |

| Low level output voltage 4/       | V <sub>OL</sub>  | V <sub>DD</sub> = +3.15 V dc, <u>5/</u><br>I <sub>OL</sub> = 4.0 mA   | 1, 2, 3               | 01              |     | 0.4  | V    |

|                                   |                  | V <sub>DD</sub> = +3.13 V dc<br>I <sub>OL</sub> = 4.0 mA              |                       | 02              |     | 0.4  |      |

| High level input 6/ 7/ 8/ current | I <sub>IH</sub>  | $V_{DD}$ = +3.6 V dc,<br>$V_{IN}$ = $V_{DD}$ MAX                      | 1, 2, 3               | 01              |     | 10   | μА   |

|                                   |                  | V <sub>DD</sub> = +3.47 V dc<br>V <sub>IN</sub> = V <sub>DD</sub> MAX |                       | 02              |     | 10   |      |

|                                   |                  |                                                                       |                       | +               | +   | +    | +    |

See footnotes at end of table.

STANDARD

MICROCIRCUIT DRAWING

DEFENSE SUPPLY CENTER COLUMBUS

COLUMBUS, OHIO 43216-5000

SIZE

A

5962-97507

REVISION LEVEL

A

SHEET

6

|                                       | TABLE              | I. Electrical performance charac                                      | <u>teristics</u> - Cor | ntinued.        |     |      |      |

|---------------------------------------|--------------------|-----------------------------------------------------------------------|------------------------|-----------------|-----|------|------|

| Test                                  | Symbol             | Conditions <u>1</u> /                                                 | Group A subgroups      | Device<br>types | Lim | nits | Unit |

|                                       |                    | unless otherwise specified                                            |                        |                 | Min | Max  |      |

| High level input 8/ 9/ 10/<br>current | I <sub>IHx4</sub>  | V <sub>DD</sub> = +3.6 V dc,<br>V <sub>IN</sub> = V <sub>DD</sub> MAX | 1, 2, 3                | 01              |     | 40   | μΑ   |

|                                       |                    | $V_{DD}$ = +3.47 V dc<br>$V_{IN}$ = V <sub>DD</sub> MAX               |                        | 02              |     | 40   |      |

| Low level input current 6/            | IIL                | V <sub>DD</sub> = +3.6 V dc, V <sub>IN</sub> = 0 V                    | 1, 2, 3                | 01              |     | 10   | μА   |

|                                       |                    | $V_{DD} = +3.47 \text{ V dc}, V_{IN} = 0 \text{ V}$                   |                        | 02              |     | 10   |      |

| Low level input current 9/            | I <sub>ILx4</sub>  | V <sub>DD</sub> = +3.6 V dc, V <sub>IN</sub> = 0 V                    | 1, 2, 3                | 01              |     | 40   | μА   |

|                                       |                    | $V_{DD} = +3.47 \text{ V dc}, V_{IN} = 0 \text{ V}$                   |                        | 02              |     | 40   |      |

| Low level input current 7/            | I <sub>ILP</sub>   | V <sub>DD</sub> = +3.6 V dc, V <sub>IN</sub> = 0 V                    | 1, 2, 3                | 01              |     | 150  | μА   |

|                                       |                    | $V_{DD} = +3.47 \text{ V dc}, V_{IN} = 0 \text{ V}$                   |                        | 02              |     | 150  |      |

| Low level input 8/ 10/<br>current     | I <sub>ILPx4</sub> | $V_{DD} = +3.6 \text{ V dc}, V_{IN} = 0 \text{ V}$                    | 1, 2, 3                | 01              |     | 600  | μА   |

|                                       |                    | $V_{DD} = +3.47 \text{ V dc}, V_{IN} = 0 \text{ V}$                   |                        | 02              |     | 600  |      |

See footnotes at end of table.

STANDARD

MICROCIRCUIT DRAWING

DEFENSE SUPPLY CENTER COLUMBUS

COLUMBUS, OHIO 43216-5000

SIZE

A

5962-97507

REVISION LEVEL

A

7

|                                                                     | TABLE              | I. Electrical performance charac                                      | teristics - Cor   | ntinued.        |     |      |      |

|---------------------------------------------------------------------|--------------------|-----------------------------------------------------------------------|-------------------|-----------------|-----|------|------|

| Test                                                                | Symbol             | Conditions <u>1</u> /                                                 | Group A subgroups | Device<br>types | Lim | nits | Unit |

|                                                                     |                    | unless otherwise specified                                            | _                 |                 | Min | Max  |      |

| Three state <u>11/ 12</u> / <u>13</u> / <u>14</u> / leakage current | Гохн               | V <sub>DD</sub> = +3.6 V dc,<br>V <sub>IN</sub> = V <sub>DD</sub> MAX | 1, 2, 3           | 01,02           |     | 10   | μΑ   |

| Three state <u>15</u> / <u>16</u> /<br>leakage current              | I <sub>OZHx4</sub> | V <sub>DD</sub> = +3.6 V dc,<br>V <sub>IN</sub> = V <sub>DD</sub> MAX | 1, 2, 3           | 01,02           |     | 40   | μА   |

| Three state leakage <u>11</u> / <u>17</u> /<br>_current             | lozL               | $V_{DD} = +3.6 \text{ V dc}, V_{IN} = 0 \text{ V}$                    | 1, 2, 3           | 01,02           |     | 10   | μА   |

| Three state leakage <u>15</u> /<br>_current                         | l <sub>OZLx4</sub> | $V_{DD} = +3.6 \text{ V dc}, V_{IN} = 0 \text{ V}$                    | 1, 2, 3           | 01,02           |     | 40   | μА   |

| Three state leakage <u>17</u> /<br>current                          | IOZHP              | $V_{DD}$ = +3.6 V dc,<br>$V_{IN}$ = $V_{DD}$ MAX                      | 1, 2, 3           | 01,02           |     | 350  | μА   |

| Three state leakage <u>14</u> /<br>_current                         | lozLC              | $V_{DD} = +3.6 \text{ V dc}, V_{IN} = 0 \text{ V}$                    | 1, 2, 3           | 01,02           |     | 1.5  | mA   |

| Three state leakage <u>18</u> /<br>_current                         | IOZLA              | $V_{DD} = +3.6 \text{ V dc}, V_{IN} = 2 \text{ V}$                    | 1, 2, 3           | 01,02           |     | 350  | μА   |

| Three state leakage <u>13</u> /<br>current                          | lozlar             | V <sub>DD</sub> = +3.6 V dc,<br>V <sub>IN</sub> = 0 V dc              | 1, 2, 3           | 01,02           |     | 4.2  | mA   |

| Three state leakage <u>12</u> /<br>current                          | lozLS              | $V_{DD} = +3.6 \text{ V dc}, V_{IN} = 0 \text{ V}$                    | 1, 2, 3           | 01,02           |     | 150  | μА   |

| Three state leakage <u>16</u> /<br>_current                         | lOZLSx4            | $V_{DD} = +3.6 \text{ V dc}, V_{IN} = 0 \text{ V}$                    | 1, 2, 3           | 01,02           |     | 600  | μА   |

| Supply current (internal) 19/                                       | IDDIN              | t <sub>CK</sub> = 25 ns, V <sub>DD</sub> = MAX                        | 1, 2, 3           | 01,02           |     | 2.2  | А    |

See footnotes at end of table.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                     | 5962-97507 |

|-------------------------------------------------------------|------------------|---------------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL<br>A | SHEET 8    |

| Supply current (idle) 20/ Input capacitance  Functional tests Clock Input Timing Require CLKIN period | IDDIDLE  C <sub>IN</sub> | unless otherwise specifi $V_{DD} = MAX$ $f = 1 \text{ MHz}, \ T_{C} = +25^{\circ}\text{C},$ $V_{IN} = 2.5 \text{ V dc}$ See 4.3.1.c | 1, 2, 3                               | 01<br>02<br>01,02 | Min               | Max<br>760<br>780 | mA   |

|-------------------------------------------------------------------------------------------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-------------------|-------------------|-------------------|------|

| Input capacitance  Functional tests  Clock Input Timing Require                                       | C <sub>IN</sub>          | f = 1 MHz, T <sub>C</sub> = +25°C,<br>V <sub>IN</sub> = 2.5 V dc                                                                    |                                       | 02                |                   | 780               | mA   |

| Functional tests<br>Clock Input Timing Require                                                        | ements                   | V <sub>IN</sub> = 2.5 V dc                                                                                                          |                                       |                   |                   | •                 |      |

| Functional tests<br>Clock Input Timing Require                                                        | ements                   | V <sub>IN</sub> = 2.5 V dc                                                                                                          |                                       | 01,02             |                   | <u>21</u> /       |      |

| Clock Input Timing Require                                                                            |                          | See 4.3.1.c                                                                                                                         |                                       |                   |                   |                   |      |

|                                                                                                       |                          | ·<br>                                                                                                                               | 7, 8                                  | 01,02             |                   |                   |      |

| CLKIN period                                                                                          | t <sub>CK</sub>          |                                                                                                                                     | · · · · · · · · · · · · · · · · · · · | <u> </u>          | <u> </u>          | <u> </u>          | 1    |

|                                                                                                       |                          | See figure 4.                                                                                                                       | 9, 10, 11                             | 01                | 25                | 100               | ns   |

|                                                                                                       |                          | -                                                                                                                                   |                                       | 02                | 27                | 100               |      |

| CLKIN width low                                                                                       | <sup>t</sup> CKL         |                                                                                                                                     |                                       | 01,02             | 9.5               |                   |      |

| CLKIN width high                                                                                      | <sup>t</sup> CKH         |                                                                                                                                     |                                       |                   | 5                 |                   |      |

| CLKIN rise/fall<br>(0.4 V - 2.0 V)                                                                    | tCKRF                    | -                                                                                                                                   |                                       |                   |                   | 3                 |      |

| Reset Timing Requirement                                                                              | <u>s</u>                 |                                                                                                                                     | 1                                     | 1                 | 1                 | 1                 | 1    |

| RESET pulse width low 23/                                                                             | twrst                    | See figure 4. <u>22</u> /                                                                                                           | 9, 10, 11                             | 01,02             | <sup>4t</sup> CK  |                   | ns   |

| RESET setup before 24/<br>CLKIN high                                                                  | <sup>t</sup> SRST        |                                                                                                                                     |                                       |                   | 14+DT/2           | <sup>t</sup> CK   |      |

| Interrupts Timing Requiren                                                                            | nents                    |                                                                                                                                     |                                       |                   |                   |                   |      |

| IRQ2-0 setup before 25/<br>CLKIN high                                                                 | t <sub>SIR</sub>         | See figure 4. <u>22</u> /                                                                                                           | 9, 10 ,11                             | 01,02             | 18+3DT/4          |                   | ns   |

| IRQ2-0 hold before 25/<br>CLKIN high                                                                  | tHIR                     | _                                                                                                                                   |                                       |                   |                   | 11.5+3DT<br>/ 4   |      |

| IRQ2-0 width pulse 26/                                                                                | <sup>t</sup> IPW         |                                                                                                                                     |                                       |                   | 2+t <sub>CK</sub> |                   |      |

| See footnotes at end of table                                                                         |                          |                                                                                                                                     |                                       |                   |                   |                   |      |

| STA<br>MICROCIRO<br>DEFENSE SUPPLY                                                                    |                          |                                                                                                                                     | SIZE<br><b>A</b>                      |                   |                   | 5962-9            | 7507 |

9

DSCC FORM 2234 APR 97

**COLUMBUS, OHIO 43216-5000**

| Test                                                             | Symbol             | Conditions 1                        | _               | Group A subgroups | Device<br>types | Lin        | nits                     | Unit |

|------------------------------------------------------------------|--------------------|-------------------------------------|-----------------|-------------------|-----------------|------------|--------------------------|------|

| Timer Switching Characteris                                      | tio                | unless otherwise spe                | ecified         |                   |                 | Min        | Max                      |      |

| CLKIN high to TIMEXP                                             | tDTEX              | See figure 4. 22/                   |                 | 9, 10, 11         | 01,02           |            | 16                       | ns   |

| FLAGS Timing and Switchin                                        |                    |                                     |                 | 3, 13, 11         |                 |            |                          |      |

| FLAG2-0 <sub>IN</sub> setup <u>27</u> /<br>before CLKIN high     | <sup>t</sup> SFI   | See figure 4. 22/                   |                 | 9, 10, 11         | 01,02           | 8+5DT/16   |                          | ns   |

| FLAG2-0 <sub>IN</sub> hold after 27/<br>CLKIN high               | <sup>t</sup> HFI   |                                     |                 |                   |                 | 0.5-5DT/16 |                          |      |

| F <u>LAG2-0<sub>IN</sub></u> delay after 27/<br>RD/ WR low       | <sup>t</sup> DWRFI |                                     |                 |                   |                 |            | 4.5+7DT/16               |      |

| F <u>LAG2-0<sub>IN</sub> hold after 27/</u><br>RD/ WR deasserted | <sup>t</sup> HFIWR |                                     |                 |                   |                 | 0.5        |                          |      |

| FLAG2-0 <sub>OUT</sub> delay after                               | t <sub>DFO</sub>   |                                     |                 |                   | 01              |            | 17                       |      |

| CLKIN high                                                       |                    |                                     |                 |                   | 02              |            | 17.5                     |      |

| FLAG2-0 <sub>OUT</sub> hold after CLKIN high                     | <sup>t</sup> HFO   |                                     |                 |                   | 01,02           | 4          |                          |      |

| CLKIN high to FLAG2-0 <sub>OUT</sub>                             | <sup>t</sup> DFOE  |                                     |                 |                   |                 | 3          |                          |      |

| CLKIN high to FLAG2-0 <sub>OUT</sub>                             | <sup>t</sup> DFOD  |                                     |                 |                   |                 |            | 15                       |      |

| Memory Read - Bus Master                                         | Timing and         |                                     |                 |                   |                 |            |                          |      |

| Address delay to 29/ 30/ data valid                              | <sup>t</sup> DAD   | See figure 4. <u>22</u> / <u>28</u> | /               | 9, 10, 11         | 01,02           |            | 17.5+DT<br>+W            | ns   |

| RD low to data valid 29/                                         | <sup>t</sup> DRLD  |                                     |                 |                   |                 |            | 11.5+5DT/8<br>+ <b>W</b> |      |

| Data hold from address 31/                                       | <sup>t</sup> HDA   |                                     |                 |                   |                 | 1          |                          |      |

| Data hold from RD high 31/                                       | <sup>t</sup> HDRH  |                                     |                 |                   |                 | 2.5        |                          |      |

| ACK delay from 30/32/<br>address                                 | <sup>t</sup> DAAK  |                                     |                 |                   |                 |            | 13.5+7DT/8<br>+ <b>W</b> |      |

| ACK delay from RD low 31/                                        | <sup>t</sup> DSAK  |                                     |                 |                   |                 |            | 7.5+DT/2<br>+W           |      |

| See footnotes at end of table.                                   |                    |                                     |                 |                   |                 |            |                          |      |

| STANDARD<br>MICROCIRCUIT DRAWING                                 |                    |                                     | IZE<br><b>A</b> |                   |                 | 5962-9     | 7507                     |      |

| DEFENSE SUPPLY<br>COLUMBUS, C                                    | CENTER C           | OLUMBUS                             |                 | F                 | REVISION        | LEVEL<br>A | SHEET 10                 |      |

| Test                                                      | Symbol              | Conditions 1/                         | Group A subgroups | Device<br>types | Lim                | its                      | Unit |

|-----------------------------------------------------------|---------------------|---------------------------------------|-------------------|-----------------|--------------------|--------------------------|------|

| Marraw Dood - Due Moster                                  | Time in a cons      | unless otherwise spec                 | ified             | 1,950           | Min                | Max                      |      |

| Memory Read - Bus Master  Address hold after RD high      | _                   | See figure 4. 22/ 28/                 | 9, 10, 11         | 01,02           | -0.5 + H           |                          | ns   |

|                                                           | <sup>t</sup> DRHA   | See ligure 4. <u>22</u> / <u>20</u> / | 9, 10, 11         | 01,02           | -0.5 + 11          |                          | -    |

| Address to RD low 30/                                     | <sup>t</sup> DARL   |                                       |                   |                 | 1.5+3DT/8          |                          |      |

| RD pulse width                                            | <sup>t</sup> RW     |                                       |                   |                 | 12.5+5DT/8<br>+W   |                          |      |

| RD high to WR, RD,<br>DMAGx low                           | tRWR                |                                       |                   |                 | 8+3DT/8<br>+HI     |                          |      |

| Address setup before 30/<br>ADRCLK high                   | tSADADC             |                                       |                   |                 | -0.5 + DT/4        |                          |      |

| Memory Write - Bus Master                                 | Timing and          | Switching Requireme                   | nts               | 1               |                    |                          |      |

| ACK delay from 30/32/<br>address selects                  | <sup>t</sup> DAAK   | See figure 4. 22/ 28/                 | 9, 10, 11         | 01,02           |                    | 13.5+7DT/8<br>+ <b>W</b> | ns   |

| ACK delay from WR 32/<br>low                              | <sup>t</sup> DSAK   |                                       |                   |                 |                    | 7.5+DT/2<br>+W           | _    |

| A <u>ddr</u> ess, selects to <u>30</u> /<br>WR deasserted | <sup>t</sup> DAWH   |                                       |                   |                 | 16.5+15DT/16<br>+W |                          | _    |

| Address, selects to 30/<br>WR low                         | <sup>t</sup> DAWL   |                                       |                   |                 | 2.5+3DT/8          |                          | _    |

| WR pulse width                                            | tww                 |                                       |                   |                 | 12+9DT/16<br>+W    |                          | _    |

| Data setup before WR high                                 | tDDWH               |                                       |                   |                 | 6.5+DT/2<br>+W     |                          | _    |

| Address hold after WR deasserted                          | <sup>t</sup> DWHA   |                                       |                   |                 | 0 + DT/16<br>+H    |                          | _    |

| D <u>ata</u> disabled after 33/<br>WR deasserted          | <sup>t</sup> DATRWH |                                       |                   |                 | 0.5+DT/16<br>+H    | 6.5+DT/16<br>+H          | _    |

| WR high to WR, RD,<br>DMAGx low                           | twwr                |                                       |                   |                 | 8 + 7DT/16<br>+H   |                          | _    |

| D <u>ata</u> dis <u>abl</u> e before<br>WR or RD low      | tDDWR               |                                       |                   |                 | 4.5+3DT/8<br>+I    |                          |      |

|                                                           |                     |                                       |                   |                 |                    |                          |      |

|                                                           | NDARD               |                                       | SIZE              |                 |                    | 5962-9                   |      |

**REVISION LEVEL**

Α

SHEET

11

DSCC FORM 2234 APR 97

MICROCIRCUIT DRAWING

DEFENSE SUPPLY CENTER COLUMBUS

**COLUMBUS, OHIO 43216-5000**

| Test                                                                                | Symbol                 | Conditions <u>1</u>             |                  | Group A subgroups | Device<br>types   | Lir         | nits                     | Unit     |

|-------------------------------------------------------------------------------------|------------------------|---------------------------------|------------------|-------------------|-------------------|-------------|--------------------------|----------|

|                                                                                     |                        | unless otherwise spe            |                  |                   |                   | Min         | Max                      |          |

| Memory Write - Bus Master                                                           | <u>Timing and</u><br>∣ | <u>l Switching Requirem</u><br> | <u>nents - C</u> | ontinued.         | 1                 | <u> </u>    | 1                        | 1        |

| WR low to data enabled                                                              | tWDE                   | See figure 4. 22/ 28/           |                  | 9, 10, 11         | 01,02             | -1.5+DT/16  |                          | ns       |

| Address, selects to 30/<br>ADRCLK high                                              | tsadadc                |                                 |                  |                   |                   | -0.5 + DT/4 |                          |          |

| Synchronous Read/Write - E                                                          | us Master              | Timing and Switchin             | g Requi          | rements           | ·<br>             | I           | 1                        | <u> </u> |

| Data setup before CLKIN                                                             | <sup>t</sup> SSDATI    | See figure 4. 22/ 28/           | ,                | 9, 10, 11         | 01,02             | 3 + DT/8    |                          | ns       |

| Data hold after CLKIN                                                               | <sup>t</sup> HSDATI    |                                 |                  |                   |                   | 4 - DT/8    |                          |          |

| ACK delay after 30/32/address, MSx, SW, BMS                                         | <sup>t</sup> DAAK      |                                 |                  |                   |                   |             | 13.5+7DT/8<br>+ <b>W</b> |          |

| ACK setup before CLKIN <u>32</u> /                                                  | <sup>t</sup> SACKC     |                                 |                  |                   |                   | 6.5 + DT/4  |                          |          |

| ACK hold after CLKIN                                                                | <sup>t</sup> HACKC     |                                 |                  |                   |                   | -0.5 - DT/4 |                          |          |

| Address, MSx,BMS,SW, 30/<br>delay after CLKIN                                       | <sup>t</sup> DADRO     |                                 |                  |                   |                   |             | 8 - DT/8                 |          |

| Address, MSx,BMS,SW, 30/<br>hold after CLKIN                                        | <sup>t</sup> HADRO     |                                 |                  |                   |                   | -1 - DT/8   |                          |          |

| PAGE delay after CLKIN                                                              | t <sub>DPGC</sub>      |                                 |                  |                   |                   | 9 + DT/8    | 17 + DT/8                |          |

| RD high delay after CLKIN                                                           | <sup>t</sup> DRDO      |                                 |                  |                   |                   | -2 - DT/8   | 5 - DT/8                 |          |

| WR high delay after CLKIN                                                           | <sup>t</sup> DWRO      |                                 |                  |                   |                   | -3 - 3DT/16 | 5 - 3DT/16               |          |

| RD / WR low delay                                                                   | <sup>t</sup> DRWL      |                                 |                  |                   |                   | 8 + DT/4    | 13.5 + DT/4              |          |

| Data delay after CLKIN                                                              | <sup>t</sup> SDDATO    |                                 |                  |                   | 01                |             | 20.25 + 5DT<br>/16       |          |

|                                                                                     |                        |                                 |                  |                   | 02                |             | 20.5 + 5DT<br>/16        |          |

| See footnotes at end of table.                                                      |                        |                                 |                  |                   |                   |             |                          |          |

| STANDARD                                                                            |                        |                                 |                  | ZE<br><b>A</b>    |                   |             | 5962-97                  | 7507     |

| MICROCIRCUIT DRAWING<br>DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                        |                                 | F                | REVISION          | LEVEL<br><b>A</b> | SHEET 12    |                          |          |

| Test                                               | Symbol                                                                                          | Conditions 1                       |            | Group A subgroups | Device<br>types | Lir                      | nits              | Unit    |

|----------------------------------------------------|-------------------------------------------------------------------------------------------------|------------------------------------|------------|-------------------|-----------------|--------------------------|-------------------|---------|

| Synchronous Read/Write - E                         | Rue Maeter                                                                                      | unless otherwise sp                |            | rements - C       | Continued       | Min                      | Max               |         |

| Data disable after CLKIN <u>33</u> /               | <sup>t</sup> DATTR                                                                              | See figure 4. <u>22</u> / <u>2</u> |            | 9, 10, 11         | 01,02           | 0 - DT/8                 | 8 - DT/8          | ns      |

| ADRCLK delay after CLKIN                           | †DADCCK                                                                                         |                                    |            |                   |                 | 4 + DT/8                 | 11 + DT/8         |         |

| ADRCLK period                                      | <sup>t</sup> ADRCK                                                                              |                                    |            |                   |                 | t <sub>CK</sub>          |                   |         |

| ADRCLK width high                                  | <sup>t</sup> ADRCKH                                                                             |                                    |            |                   |                 | (t <sub>CK</sub> /2 - 2) |                   |         |

| ADRCLK width low                                   | <sup>t</sup> ADRCKL                                                                             |                                    |            |                   |                 | (t <sub>CK</sub> /2 - 2) |                   |         |

| Synchronous Read/Write - E                         | Bus Slave T                                                                                     | _                                  | -          |                   |                 |                          |                   | T       |

| Address, SW setup before CLKIN                     | <sup>t</sup> SADRI                                                                              | See figure 4. 22/ 2                | <u>8</u> / | 9, 10, 11         | 01,02           | 15.5 + DT/2              |                   | ns<br>- |

| Address, SW hold before CLKIN                      | <sup>t</sup> HADRI                                                                              |                                    |            |                   |                 |                          | 4.5 + DT/2        |         |

| RD / WR low setup 34/<br>before CLKIN              | <sup>t</sup> SRWLI                                                                              |                                    |            |                   |                 | 9.5+5DT/16               |                   |         |

| RD / WR low hold after CLKIN                       | tHRWLI                                                                                          |                                    |            |                   | 01              | -3.25 - 5DT<br>/ 16      | 8 + 7DT/16        |         |

|                                                    |                                                                                                 |                                    |            |                   | 02              | -3 - 5DT<br>/ 16         | 8 + 7DT/16        |         |

| RD / WR pulse high                                 | <sup>t</sup> RWHPI                                                                              |                                    |            |                   | 01,02           | 3                        |                   |         |

| Data setup before WR high                          | <sup>t</sup> SDATWH                                                                             |                                    |            |                   |                 | 5.5                      |                   |         |

| Data hold after WR high                            | tHDATWH                                                                                         |                                    |            |                   |                 | 1.5                      |                   |         |

| Data delay after CLKIN                             | tSDDATO                                                                                         |                                    |            |                   | 01              |                          | 20.25 +5DT<br>/16 |         |

|                                                    |                                                                                                 |                                    |            |                   | 02              |                          | 20.5+5DT/16       |         |

| Data disable after CLKIN 33/                       | tDATTR                                                                                          |                                    |            |                   | 01,02           | 0 - DT/8                 | 8 - DT/8          |         |

| A <u>CK</u> delay after address <u>35</u> /<br>_SW | <sup>t</sup> DACKAD                                                                             |                                    |            |                   |                 |                          | 10                |         |

| ACK disable after CLKIN <u>35</u> /                | <sup>t</sup> ACKTR                                                                              |                                    |            |                   |                 | -1 - DT/8                | 7 - DT/8          |         |

| See footnotes at end of table.                     |                                                                                                 |                                    | Q          | ZE ZE             |                 |                          |                   |         |

| MICROCIRC                                          | STANDARD<br>MICROCIRCUIT DRAWING<br>DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                                    |            | A                 |                 |                          | 5962-97           | 7507    |

|                                                    |                                                                                                 |                                    |            | F                 | REVISION        | LEVEL<br>A               | SHEET 13          |         |

| Test                                    | Symbol                                                                        | Conditions _        | <u>1</u> /  | Group A<br>subgroups | Device<br>types | Li                | mits            | Unit     |

|-----------------------------------------|-------------------------------------------------------------------------------|---------------------|-------------|----------------------|-----------------|-------------------|-----------------|----------|

|                                         |                                                                               | unless otherwise sp |             |                      |                 | Min               | Max             |          |

| Multiprocessor Bus Reques               | st and Host<br>                                                               | Request Timing and  | Switchi     | ng Require           | ments<br>       | <u> </u>          |                 | <u> </u> |

| HBG low to RD/WR/CS, valid              | tHBGRCSV                                                                      | See figure 4. 22/ 2 | <u>28</u> / | 9, 10, 11            | 01,02           |                   | 19.5+5DT/4      | ns       |

| HBR setup before 37/<br>CLKIN           | <sup>t</sup> SHBRI                                                            |                     |             |                      |                 | 20+3DT/4          |                 |          |

| HBR hold before 37/<br>CLKIN            | <sup>t</sup> HHBRI                                                            |                     |             |                      |                 |                   | 13.5+3DT<br>/ 4 |          |

| HBG setup before CLKIN                  | <sup>t</sup> SHBGI                                                            |                     |             |                      |                 | 13+DT/2           |                 |          |

| HBG hold before CLKIN high              | <sup>t</sup> HHBGI                                                            |                     |             |                      | 01              |                   | 5.5+DT/2        |          |

|                                         |                                                                               |                     |             |                      | 02              | i                 | 5.25+DT/2       |          |

| BRx, CPA setup before 38/<br>CLKIN high | <sup>t</sup> SBRI                                                             |                     |             |                      | 01,02           | 13+DT/2           |                 |          |

| BRx, CPA hold before CLKIN high         | tHBRI                                                                         |                     |             |                      |                 |                   | 5.5+DT/2        |          |

| RPBA setup before CLKIN                 | <sup>t</sup> SRPBAI                                                           |                     |             |                      |                 | 21+3DT/4          |                 |          |

| RPBA hold before CLKIN                  | <sup>t</sup> HRPBAI                                                           |                     |             |                      |                 |                   | 11.5+3DT<br>/ 4 |          |

| HBG delay after CLKIN                   | <sup>t</sup> DHBGO                                                            |                     |             |                      |                 |                   | 8 - DT/8        |          |

| HBG hold after CLKIN                    | <sup>t</sup> HHBGO                                                            |                     |             |                      |                 | -2 - DT/8         |                 |          |

| BRx delay after CLKIN                   | <sup>t</sup> DBRO                                                             |                     |             |                      |                 |                   | 8 - DT/8        |          |

| BRx hold after CLKIN                    | <sup>t</sup> HBRO                                                             |                     |             |                      |                 | -2 - DT/8         |                 |          |

| CPA low delay after CLKIN               | <sup>t</sup> DCPAO                                                            |                     |             |                      |                 |                   | 9.5 - DT/8      |          |

| CPA disable after CLKIN                 | <sup>t</sup> TRCPA                                                            |                     |             |                      |                 | -2 - DT/8         | 5.5 - DT/8      |          |

| See footnotes at end of table           |                                                                               |                     |             |                      |                 |                   |                 |          |

|                                         | NDARD                                                                         | ING                 |             | IZE<br><b>A</b>      |                 |                   | 5962-97         | 7507     |

| DEFENSE SUPPLY                          | MICROCIRCUIT DRAWING DEFENSE SUPPLY CENTER COLUMBUS COLUMBUS, OHIO 43216-5000 |                     |             | F                    | REVISION        | LEVEL<br><b>A</b> | SHEET 14        |          |

| Test                                                             | Symbol                 | Condit                     |             | _           | Group A subgroups | Device<br>types | Lim              | nits              | Unit     |

|------------------------------------------------------------------|------------------------|----------------------------|-------------|-------------|-------------------|-----------------|------------------|-------------------|----------|

| Multiprocessor Bus Reques                                        | t and Host             | unless other  Request Timi |             | •           | ing Require       | ments - C       | Min<br>ontinued. | Max               |          |

| REDY (O/ <u>D)</u> or (A/ <u>D) 39</u> / low from CS and HBR low | tDRDYCS                | See figure 4.              |             |             | 9, 10, 11         | 01,02           |                  | 12                | ns       |

| REDY (O/D) disable or 39/<br>REDY (A/D) high from HBG            | <sup>t</sup> TRDYHG    |                            |             |             |                   |                 | 40+27DT/16       |                   |          |

| · · · · ·                                                        | <sup>t</sup> ARDYTR    |                            |             |             |                   |                 |                  | 11                |          |

| Asynchronous Read Cycle T                                        | iming and              | Switching Re               | quire       | ements (H   | ost to Devic      | e type 01)      |                  |                   |          |

| Address <u>se</u> tup/CS low <u>40</u> /<br>before RD low        | <sup>t</sup> SADRDL    | See figure 4.              | <u>22</u> / | <u>28</u> / | 9, 10, 11         | 01,02           | 0.5              |                   | ns       |

| Address h <u>old</u> /CS hold<br>low after RD                    | <sup>t</sup> HADRDH    |                            |             |             |                   |                 | 0.5              |                   |          |

| RD/WR high width                                                 | <sup>t</sup> WRWH      |                            |             |             |                   |                 | 6                |                   |          |

| <br>RD high delay after REDY<br>(O/D) disable                    | t <sub>DRDHRDY</sub>   |                            |             |             |                   |                 | 0.5              |                   |          |

| RD high delay after REDY<br>(A/D) disable                        | t <sub>DRDHRDY</sub>   |                            |             |             |                   |                 | 0.5              |                   |          |

| Data valid before REDY<br>disable from low                       | t <sub>SDATRDY</sub>   |                            |             |             |                   |                 | 1.5              |                   |          |

| REDY (O/D <u>) or (</u> A/D) low<br>delay after RD low           | t <sub>DRDYRDL</sub>   |                            |             |             |                   |                 |                  | 13.5              |          |

| REDY (O/D) or (A/D) low<br>pulse width for read                  | t <sub>RDYPRD</sub>    |                            |             |             |                   |                 | 45 + DT          |                   |          |

| Data disable after RD high                                       | tHDARWH                |                            |             |             |                   |                 | 1.5              | 9.5               |          |

| Asynchronous Write Cycle T                                       | <u>「iming and</u><br>│ | Switching Re               | quire       | ements (H   | ost to Devic      | e type 01)      | <u> </u>         |                   | <u> </u> |

| CS low setup before WR low                                       | tscswrl                | See figure 4.              | <u>22</u> / | <u>28</u> / | 9, 10, 11         | 01,02           | 0.5              |                   | ns<br>—  |

| CS low hold after WR high                                        | tHCSWRH                |                            |             |             |                   |                 | 0.5              |                   | _        |

| Address setup before WR high See footnotes at end of table.      | <sup>t</sup> SADWRH    |                            |             |             |                   |                 | 5.5              |                   |          |

|                                                                  | IDARD                  |                            |             |             | SIZE              |                 |                  | F000              | 750-     |

| STANDARD MICROCIRCUIT DRAWING DEFENSE SUPPLY CENTER COLUMBUS     |                        |                            |             | A           |                   |                 | 5962-9           | <del>3</del> 7507 |          |

| Test                                                                                | Symbol                 | Conditions _        | <u>1</u> /  | Group A<br>subgroups | Device<br>s types | Lin                      | nits        | Unit |

|-------------------------------------------------------------------------------------|------------------------|---------------------|-------------|----------------------|-------------------|--------------------------|-------------|------|

|                                                                                     |                        | unless otherwise sp |             |                      |                   | Min                      | Max         |      |

| Asynchronous Write Cycle                                                            | <u>Fiming and</u><br>│ | Switching Requiren  | nents (Ho   | ost to Devi          | ce type 01)       | - Continued              | <u>.</u>    | 1    |

| Address hold after WR<br>high                                                       | tHADWRH                | See figure 4. 22/ 2 | <u>28</u> / | 9, 10, 11            | 01,02             | 2.5                      |             | ns   |

| WR low width                                                                        | twwRL                  |                     |             |                      |                   | 7                        |             | _    |

| RD/WR high width                                                                    | twrwh                  |                     |             |                      |                   | 6                        |             |      |

| WR high delay after REDY (O/D) or (A/D) disable                                     | t <sub>DWRHRDY</sub>   |                     |             |                      |                   | 0.5                      |             |      |

| Data setup before WR high                                                           | <sup>t</sup> SDATWH    |                     |             |                      |                   | 5.5                      |             |      |

| Data hold after WR high                                                             | tHDATWH                |                     |             |                      |                   | 1.5                      |             |      |

| REDY (O/D) or (A/D) low delay after WR/CS low                                       | t <sub>DRDYWRL</sub>   |                     |             |                      |                   |                          | 13.5        | _    |

| REDY (O/D) or (A/D) low pulse width for write                                       | t <sub>RDYPWR</sub>    |                     |             |                      |                   | 15                       |             | _    |

| REDY (O/D) or (A/D) disable to CLKIN                                                | t <sub>SRDYCK</sub>    |                     |             |                      |                   | 0+7DT/16                 | 8+7DT/16    |      |

| Three State Timing - (Bus M                                                         | aster, Bus             | Slave, HBR, SBTS)   | Timing a    | nd Switchi           | ng Require        | ments                    | ·<br>       | 1    |

| SBTS setup before CLKIN                                                             | tSTSCK                 | See figure 4. 22/ 2 | <u>28</u> / | 9, 10, 11            | 01,02             | 12 + DT/2                |             | ns   |

| SBTS hold before CLKIN                                                              | tHTSCK                 |                     |             |                      |                   |                          | 5.5 + DT/2  | _    |

| Address/select enable after<br>CLKIN                                                | <sup>t</sup> MIENA     |                     |             |                      |                   | -1.25 - DT<br><u>/</u> 8 |             | -    |

| Strobes enable after 41/<br>CLKIN                                                   | tMIENS                 |                     |             |                      |                   | -1.5 - DT/8              |             | -    |

| HBG enable after CLKIN                                                              | tMIENHG                |                     |             |                      |                   | -1.5 - DT/8              |             | _    |

| Address select/disable after CLKIN                                                  | <sup>t</sup> MITRA     |                     |             |                      |                   |                          | 1.25 - DT/4 |      |

| See footnotes at end of table.                                                      | <u> </u>               |                     |             |                      |                   |                          |             |      |

|                                                                                     |                        |                     |             |                      |                   |                          |             |      |

| STANDARD                                                                            |                        |                     | 1           | IZE<br><b>A</b>      |                   |                          | 5962-9      | 7507 |

| MICROCIRCUIT DRAWING<br>DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                        |                     |             | REVISION             | LEVEL<br><b>A</b> | SHEET 16                 |             |      |

|                                                      | TABLE                                                                                           | I. Electrical performan                 | nce chara  | acteristics -     | Continued.      |                   |                 |      |

|------------------------------------------------------|-------------------------------------------------------------------------------------------------|-----------------------------------------|------------|-------------------|-----------------|-------------------|-----------------|------|

| Test                                                 | Symbol                                                                                          | Conditions <u>1</u> unless otherwise sp | _          | Group A subgroup  | Device<br>types | Lir               | nits            | Unit |