# XRK49911

REV. 1.0.1

#### 3.3V HIGH-SPEED (110 MHZ) PROGRAMMABLE SKEW CLOCK BUFFER

#### OCTOBER 2005

# FUNCTIONAL DESCRIPTION

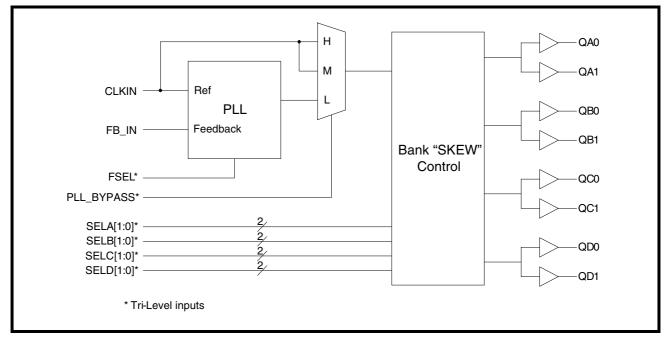

The XRK49911 is a 3.3V High-Speed Low-Voltage Programmable Skew Clock Buffer. It is intended for high-performance computer systems and offers user selectable control over system clock functions to optimize timing. Eight outputs, arranged in four banks, can each drive  $50\Omega$  terminated transmission lines while delivering minimal and specified output skews and full-swing Low Voltage TTL logic levels.

Each bank (two outputs per bank) can be individually selected for one of nine delay or function configurations through two dedicated tri-level inputs. These outputs are able to lead or lag the CLKIN input reference clock by up to 6 time units from their nominal "zero" skew position. The integrated PLL allows external load and transmission line delay effects to be canceled achieving zero delay capability. Combining the zero delay capability with the selectable output skew functions, output-to-output delays of up to  $\pm 12$  time units can be created.

The XRK49911's divide functions (divide-by-two and divide-by-four) allow distribution of a low-frequency clock that can be multiplied by two or four at the clock destination. This feature facilitates clock distribution while allowing maximum system clock flexibility.

#### FEATURES

- 3.75- to 110-MHz output operation

- All output pair skew <100 ps typical

- Three skew grades

- -2: t<sub>SKEW0</sub><250ps

- -5 : t<sub>SKEW0</sub><500ps

- -7:t<sub>SKEW0</sub><700ps

- Selectable output functions

Skew adjustments of +/- 6t<sub>U</sub> (up to 18 ns)

Inverted and non-inverted

Operation at 1/2 and 1/4 input frequency

Operation at 2x and 4x input frequency

- Cycle-Cycle Jitter

- < 25 ps (rms)

- < 200 ps (pk-pk)

- Zero input-to-output delay

- 50% duty-cycle outputs

- LVTTL outputs drive  $50\Omega$  terminated lines

- Operates from a single 3.3V supply

- 32-pin PLCC package

- Green packaging

- Lead free lead frame available

FIGURE 1. BLOCK DIAGRAM OF THE XRK49911

# **PRODUCT ORDERING INFORMATION**

| PRODUCT NUMBER | ACCURACY | TEMPERATURE RANGE |

|----------------|----------|-------------------|

| XRK49911IJ-2   | 250 ps   | -40°C to +85°C    |

| XRK49911CJ-2   | 250 ps   | 0°C to +70°C      |

| XRK49911IJ-5   | 500 ps   | -40°C to +85°C    |

| XRK49911CJ-5   | 500 ps   | 0°C to +70°C      |

| XRK49911CJ-7   | 750 ps   | 0°C to +70°C      |

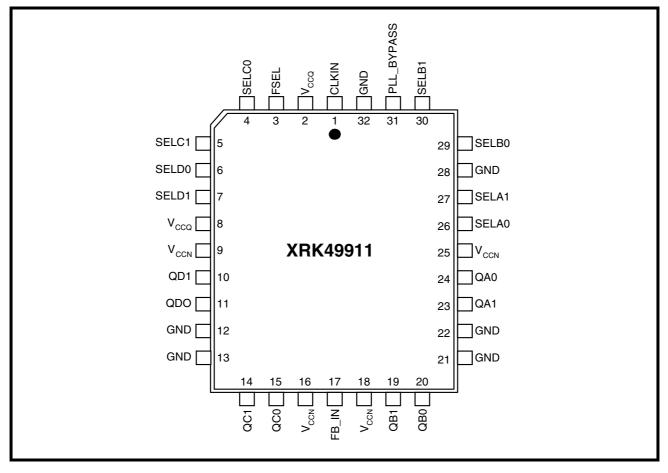

# FIGURE 2. PIN OUT OF THE XRK49911

# XRK49911 3.3V HIGH-SPEED (110 MHZ) PROGRAMMABLE SKEW CLOCK BUFFER

# **PIN DESCRIPTIONS**

| PIN NAME         | PIN #                            | Түре | DESCRIPTION                                                            |

|------------------|----------------------------------|------|------------------------------------------------------------------------|

| CLKIN            | 1                                | I    | Reference clock input.                                                 |

| FB_IN            | 17                               | I    | PLL's feedback input. (Normally connected to one of the eight outputs) |

| FSEL             | 3                                | I    | Tri-level frequency range select. See Table 1                          |

| PLL_BYPASS       | 31                               | I    | Tri-level select. See PLL_BYPASS section.                              |

| SELA0<br>SELA1   | 26<br>27                         | I    | Tri-level select inputs for Bank A outputs (QA0, QA1). See Table 2.    |

| SELB0<br>SELB1   | 29<br>30                         | I    | Tri-level select inputs for Bank B outputs (QB0, QB1). See Table 2.    |

| SELC0<br>SELC1   | 4<br>5                           | I    | Tri-level select inputs for Bank C outputs (QC0, QC1). See Table 2.    |

| SELD0<br>SELD1   | 6<br>7                           | I    | Tri-level select inputs for Bank D outputs (QD0, QD1). See Table 2.    |

| QA0<br>QA1       | 24<br>23                         | 0    | Bank A output pair. See Table 2.                                       |

| QB0<br>QB1       | 20<br>19                         | 0    | Bank B output pair. See Table 2.                                       |

| QC0<br>QC1       | 15<br>14                         | 0    | Bank C output pair. See Table 2.                                       |

| QD0<br>QD1       | 11<br>10                         | 0    | Bank D output pair. See Table 2.                                       |

| V <sub>CCN</sub> | 9<br>16<br>18<br>25              | PWR  | Power supply for output drivers.                                       |

| V <sub>CCQ</sub> | 2<br>8                           | PWR  | Power supply for internal circuitry.                                   |

| GND              | 12<br>13<br>21<br>22<br>28<br>32 | PWR  | Ground.                                                                |

|                     | f <sub>NOM</sub> (MHz) |     | t <sub>U</sub> = 1 / (f <sub>NOM</sub> x N) |                                                    |  |

|---------------------|------------------------|-----|---------------------------------------------|----------------------------------------------------|--|

| FSEL <sup>[2]</sup> | Min                    | Мах | WHERE N =                                   | FREQUENCY (MHZ) AT<br>WHICH t <sub>U</sub> = 1.0ns |  |

| LOW                 | 15                     | 30  | 44                                          | 22.7                                               |  |

| MID                 | 25                     | 50  | 26                                          | 38.5                                               |  |

| HIGH <sup>[3]</sup> | 40                     | 110 | 16                                          | 62.5                                               |  |

# TABLE 1: FREQUENCY RANGE SELECT AND tU CALCULATION [1]

#### SKEW SELECT CONTROL

The skew select control consists of four independent banks. Each bank has two low-skew, high-fanout drivers (Qx0, Qx1), and two corresponding tri-level function select (SELx0, SELx1) inputs. The nine possible output states for each bank are shown in Table 2 as determined by each bank's select inputs. All timing measurements are made with respect to the CLKIN input with the output connected to the FB\_IN input configured for 0 t<sub>U</sub> operation.

| FUNCTION SE | FUNCTION SELECT INPUTS |                  | OUTPUT FUNCTIONS |                  |  |

|-------------|------------------------|------------------|------------------|------------------|--|

| SELx1       | SELx0                  | QA[1:0], QB[1:0] | QC[1:0]          | QD[1:0]          |  |

| LOW         | LOW                    | -4t <sub>U</sub> | ÷ 2              | ÷2               |  |

| LOW         | MID                    | -3t <sub>U</sub> | -6t <sub>U</sub> | -6t <sub>U</sub> |  |

| LOW         | HIGH                   | -2t <sub>U</sub> | -4t <sub>U</sub> | -4t <sub>U</sub> |  |

| MID         | LOW                    | -1t <sub>U</sub> | -2t <sub>U</sub> | -2t <sub>U</sub> |  |

| MID         | MID                    | Ot <sub>U</sub>  | Ot <sub>U</sub>  | 0t <sub>U</sub>  |  |

| MID         | HIGH                   | +1t <sub>U</sub> | +2tU             | +2t <sub>U</sub> |  |

| HIGH        | LOW                    | +2t <sub>U</sub> | +4t <sub>U</sub> | +4t <sub>U</sub> |  |

| HIGH        | MID                    | +3t <sub>U</sub> | +6t <sub>U</sub> | +6t <sub>U</sub> |  |

| HIGH        | HIGH                   | +4t <sub>U</sub> | ÷ 4              | Inverted         |  |

#### TABLE 2: PROGRAMMABLE SKEW CONFIGURATIONS<sup>[1]</sup>

#### Notes:

- For all tri-level (three-state) inputs, HIGH indicates a connection to V<sub>CC</sub>, LOW indicates a connection to GND, and MID indicates an open connection. Internal termination circuitry holds an unconnected input to V<sub>CC</sub>/2.

- 2. The level to be set on FSEL is determined by the "normal" operating frequency (f<sub>NOM</sub>) of the PLL. Nominal frequency (f<sub>NOM</sub>) always appears at QA0 and the other outputs when they are operated in their undivided modes (see Table 2). The frequency appearing at the CLKIN and FB\_IN inputs will be f<sub>NOM</sub> when the output connected to FB\_IN is undivided. The frequency of the CLKIN and FB\_IN inputs will be f<sub>NOM</sub> ÷ 2 or f<sub>NOM</sub> ÷ 4 when the part is configured for a frequency multiplication.

*3.* When the FSEL pin is selected HIGH, the CLKIN input must not transition upon power-up until V<sub>CC</sub> has reached 2.8V.

|                        |                        | !                  | $-1_{0}-6t_{U}$<br>$-1_{0}-5t_{U}$<br>$-1_{0}-5t_{U}$<br>$-1_{0}-4t_{U}$<br>$-1_{0}-3t_{U}$<br>$-1_{0}-1t_{U}$<br>$-1_{0}+1t_{U}$<br>$-1_{0}+3t_{U}$<br>$-1_{0}+5t_{U}$<br>$-1_{0}+6t_{U}$<br>$-1_{0}+6t_{U}$ |

|------------------------|------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        |                        | FB_IN              |                                                                                                                                                                                                               |

| SELA[1:0]<br>SELB[1:0] | SELC[1:0]<br>SELD[1:0] | CLKIN-             |                                                                                                                                                                                                               |

| (N/A)                  | LM                     | -6t <sub>u</sub> – |                                                                                                                                                                                                               |

| LL                     | LH                     | -4t <sub>0</sub>   |                                                                                                                                                                                                               |

| LM                     | (N/A)                  | -3t <sub>u</sub>   |                                                                                                                                                                                                               |

| LH                     | ML                     | -2t <sub>u</sub>   |                                                                                                                                                                                                               |

| ML                     | (N/A)                  | -1t <sub>u</sub> – |                                                                                                                                                                                                               |

| MM                     | MM                     | 0t <sub>∪</sub> ⊢  |                                                                                                                                                                                                               |

| MH                     | (N/A)                  | +1t <sub>u</sub>   |                                                                                                                                                                                                               |

| HL                     | MH                     | +2t <sub>u</sub>   |                                                                                                                                                                                                               |

| HM                     | (N/A)                  | +3t <sub>u</sub> – |                                                                                                                                                                                                               |

| HH                     | HL                     | +4t <sub>u</sub>   |                                                                                                                                                                                                               |

| (N/A)                  | HM                     | +6t <sub>u</sub>   |                                                                                                                                                                                                               |

| (N/A)                  | LL/HH [                |                    |                                                                                                                                                                                                               |

| (N/A)                  | HH(D)                  |                    |                                                                                                                                                                                                               |

|                        |                        | I                  |                                                                                                                                                                                                               |

FIGURE 3. TYPICAL OUTPUTS WITH FB\_IN CONNECTED TO A ZERO-SKEW OUTPUT

### PLL\_BYPASS

The PLL\_BYPASS input is a tri-level input. In normal system operation, this pin is connected to ground.

In normal operation (tied LOW) all outputs will function based only on the connection of their own function select inputs (SELx[1:0]) and the waveform characteristics of the PLL.

If the PLL\_BYPASS input is forced to its MID or HIGH state the device will operate in PLL bypass mode, with the phase locked loop disconnected, and CLKIN waveforms will directly control all outputs. Relative output to output timing is controlled by the SELx[1:0], the same as in normal mode.

# **ELECTRICAL SPECIFICATIONS**

# ABSOLUTE MAXIMUM RATINGS

| Storage Temperature                                     | –65°C to +150°C |

|---------------------------------------------------------|-----------------|

| Ambient Temperature with Power Applied                  | –55°C to +125°C |

| Supply Voltage to Ground Potential                      | -0.5V to +7.0V  |

| DC Input Voltage                                        | -0.5V to +7.0V  |

| Output Current into Outputs (LOW)                       | 64 mA           |

| Static Discharge Voltage (per MIL-STD-883, Method 3015) | >3000V          |

| Latch-Up Current.                                       | >200 mA         |

# **OPERATING RANGE**

| RANGE      | Ambient Temperature | VCC              |

|------------|---------------------|------------------|

| Industrial | -40°C to +85°C      | 3.3 <u>+</u> 10% |

| Commercial | 0°C to +70°C        | 3.3 <u>+</u> 10% |

# ELECTRICAL CHARACTERISTICS OVER THE 3.3V ± 10% OPERATING RANGE

| SYMBOL           | DESCRIPTION                                                            | Min                  | Мах                    | Unit | CONDITION                                       |  |

|------------------|------------------------------------------------------------------------|----------------------|------------------------|------|-------------------------------------------------|--|

| V <sub>OH</sub>  | Output HIGH Voltage                                                    | 2.4                  |                        | V    | V <sub>CC</sub> = Min., I <sub>OH</sub> = -18mA |  |

| V <sub>OL</sub>  | Output LOW Voltage                                                     |                      | 0.45                   | V    | V <sub>CC</sub> = Min., I <sub>OL</sub> = 35mA  |  |

| V <sub>IH</sub>  | Input HIGH Voltage                                                     | 2.0                  | V <sub>CC</sub>        | V    | (CLKIN and FB_IN inputs                         |  |

| $V_{\text{IL}}$  | Input LOW Voltage                                                      | -0.5                 | 0.8                    | V    | only)                                           |  |

| V <sub>IHH</sub> | tri-level Input HIGH Voltage<br>(FSEL, SELx[1:0], Test) <sup>[4]</sup> | 0.87*V <sub>CC</sub> | V <sub>CC</sub>        | V    | $Min. \leq V_{CC} \leq Max.$                    |  |

| V <sub>IMM</sub> | tri-level Input MID Voltage<br>(FSEL, SELx[1:0], Test) <sup>[4]</sup>  | 0.47*V <sub>CC</sub> | 0.53 * V <sub>CC</sub> | V    | $Min. \leq V_{CC} \leq Max.$                    |  |

| V <sub>ILL</sub> | tri-level Input LOW Voltage<br>(FSEL, SELx[1:0], Test) <sup>[4]</sup>  | 0.0                  | 0.13 * V <sub>CC</sub> | V    | $Min. \leq V_{CC} \leq Max.$                    |  |

| Ι <sub>ΙΗ</sub>  | Input HIGH Leakage Current<br>(CLKIN and FB_IN inputs only)            |                      | 20                     | μA   | V <sub>CC</sub> = Max., V <sub>IN</sub> = Max.  |  |

| Ι <sub>ΙL</sub>  | Input LOW Leakage Current<br>(CLKIN and FB_IN inputs only)             | -20                  |                        | μΑ   | $V_{CC} = Max., V_{IN} = 0.4V$                  |  |

| I <sub>IHH</sub> | Input HIGH Current<br>(FSEL, SELx[1:0], Test)                          |                      | 200                    | μΑ   | V <sub>IN</sub> = V <sub>CC</sub>               |  |

| I <sub>IMM</sub> | Input MID Current<br>(FSEL, SELx[1:0], Test)                           | -50                  | 50                     | μA   | $V_{IN} = V_{CC}/2$                             |  |

| I <sub>ILL</sub> | Input LOW Current<br>(FSEL, SELx[1:0], Test)                           |                      | -200                   | μA   | V <sub>IN</sub> = GND                           |  |

#### XRK49911 3.3V HIGH-SPEED (110 MHZ) PROGRAMMABLE SKEW CLOCK BUFFER

#### ELECTRICAL CHARACTERISTICS OVER THE 3.3V ± 10% OPERATING RANGE

| Symbol           | DESCRIPTION                                          |       | Μιν | Мах  | Unit | CONDITION                                                                                                       |

|------------------|------------------------------------------------------|-------|-----|------|------|-----------------------------------------------------------------------------------------------------------------|

| I <sub>OS</sub>  | Short Circuit Current <sup>[5]</sup>                 |       |     | -200 | mA   | V <sub>CC</sub> = Max,<br>V <sub>OUT</sub> = GND (25° only)                                                     |

| I <sub>CCQ</sub> | Operating Current Used by Inter-                     | Com'l |     | 95   | mA   | $V_{CCN} = V_{CCQ} = Max.,$                                                                                     |

|                  | nal Circuitry                                        |       |     | 100  |      | All Inputs Selects Open                                                                                         |

| I <sub>CCN</sub> | Output Buffer Current per Output Pair <sup>[6]</sup> |       |     | 19   | mA   | V <sub>CCN</sub> = V <sub>CCQ</sub> = Max.,<br>I <sub>OUT</sub> = 0 mA<br>Inputs Selects Open, f <sub>MAX</sub> |

| PD               | Power Dissipation per Output Pair <sup>[7]</sup>     |       |     | 104  | mW   | V <sub>CCN</sub> = V <sub>CCQ</sub> = Max.,<br>I <sub>OUT</sub> = 0 mA<br>Input Selects Open, f <sub>MAX</sub>  |

#### CAPACITANCE<sup>[8]</sup>

| SYMBOL          | DESCRIPTION       | MAX. | Unit | CONDITION                                               |

|-----------------|-------------------|------|------|---------------------------------------------------------|

| C <sub>IN</sub> | Input Capacitance | 10   | pF   | T <sub>A</sub> = 25°C,<br>f=1MHz, V <sub>CC</sub> =3.3V |

Notes:

- 4. These inputs are normally wired to V<sub>CC</sub>, GND or left unconnected (actual threshold voltages vary as a percentage of V<sub>CC</sub>). Internal termination resistors hold unconnected inputs at V<sub>CC</sub>/2. If these inputs are switched, the function and timing of the outputs may glitch and the PLL may require an additional t<sub>LOCK</sub> time before all data sheet limits are achieved.

- 5. XRK49911 should be tested one output at a time, output shorted for less than one second, less than 10% duty cycle. Room temperature only.

- 6. Total output current per output pair can be approximated by the following expression that includes device current plus load current:

$XRK49911: I_{CCN} = \{(4+0.11F) + [(835-3F)/Z + (.0022FC)]N\} \times 1.1$

Where:

F = frequency in MHz

- C = capacitive load in pF

- Z = line impedance in ohms

- N = number of loaded outputs; 0, 1, or 2

- 7. Total power dissipation per output pair can be approximated by the following expression that includes device power dissipation plus power dissipation due to the load circuit:

PD = {(22 + 0.61F) + [(1550 + 2.7F)/Z) + .0125FC]N} x 1.1

See note 6 for variable definition.

8. Applies to CLKIN and FB\_IN inputs only.

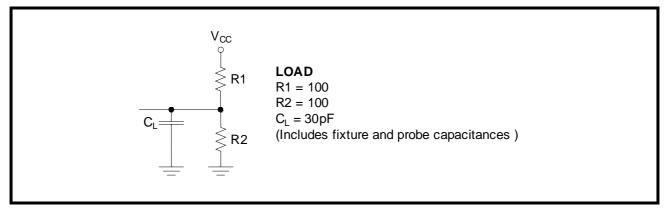

# FIGURE 4. AC TEST LOAD

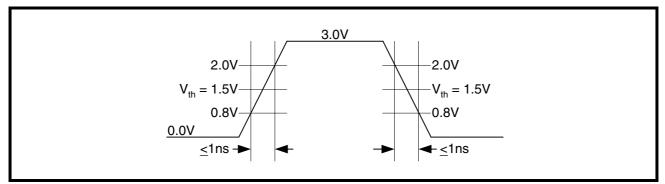

# FIGURE 5. INPUT TEST WAVEFORM

# SWITCHING CHARACTERISTICS OVER THE OPERATING RANGE <sup>[2,9]</sup>

| SYMBOL           | DESCRIPTION                      |                                  |    | Мах | Unit |

|------------------|----------------------------------|----------------------------------|----|-----|------|

| f <sub>NOM</sub> | Operating Clock Frequency in MHz | FSEL = LOW <sup>[1, 2]</sup>     | 15 | 30  | MHz  |

|                  |                                  | FSEL = MID <sup>[1, 2]</sup>     | 25 | 50  |      |

|                  |                                  | FSEL = HIGH <sup>[1, 2, 3]</sup> | 40 | 110 |      |

# REV. 1.0.1

#### XRK49911 3.3V HIGH-SPEED (110 MHZ) PROGRAMMABLE SKEW CLOCK BUFFER

#### XRK49911-2 XRK49911-5 XRK49911-7 SYMBOL DESCRIPTION Unit ΜιΝ Түр MAX ΜιΝ Түр MAX ΜιΝ Түр MAX **CLKIN Pulse Width HIGH** 4 4 4 ns t<sub>RPWH</sub> **CLKIN Pulse Width LOW** 4 4 4 t<sub>RPWL</sub> ns Programmable Skew Unit See Table 1 t<sub>u</sub> Zero Output Matched-Pair Skew 0.05 0.2 0.25 0.1 0.25 0.1 ns **t<sub>SKEWPR</sub>** (Qx[1:0])<sup>[10, 11]</sup> Zero Output Skew (All Outputs) [10, 12] 0.1 0.25 0.25 0.5 0.3 0.75 ns t<sub>SKEW0</sub> Output Skew (Rise-Rise, Fall-Fall, 0.25 0.5 0.7 1 0.6 0.6 ns t<sub>SKEW1</sub> Same Class Outputs) [10, 13] Output Skew (Rise-Fall, Nominal-0.3 1 0.5 1 1 1.5 ns t<sub>SKEW2</sub> Inverted, Divided-Divided) [10, 13] Output Skew (Rise-Rise, Fall-Fall, 0.25 0.5 0.5 0.7 0.7 1.2 ns t<sub>SKEW3</sub> Different Class Outputs) [10, 13] Output Skew (Rise-Fall, Nominal-0.9 0.5 0.5 1.2 1.7 t<sub>SKFW4</sub> 1 ns Divided, Divided-Inverted [10, 13] Device-to-Device Skew [14, 15] 0.75 1.25 1.65 ns t<sub>DFV</sub> -0.7 Propagation Delay, CLKIN Rise to -0.25 0 0.25 -0.5 0 0.5 0 0.7 ns t<sub>PD</sub> FB IN Rise Output Duty Cycle Variation [16] -0.65 0 0.65 0 -1.2 0 1.2 -1 1 topcv ns t<sub>PWH</sub> Output HIGH Time Deviation from 50% 2.0 2.5 3 ns [17] Output LOW Time Deviation from 50% 1.5 3 3.5 t<sub>PWL</sub> ns [17] Output Rise Time [17, 18] 0.15 1 1.2 0.15 1 1.5 0.15 1.5 2.5 ns **t**ORISE 0.15 Output Fall Time [17, 18] 0.15 1 1.2 1 1.5 0.15 1.5 2.5 ns tOFALL

#### SWITCHING CHARACTERISTICS OVER THE 3.3V ± 10% OPERATING RANGE [2,9]

#### NOTES:

**t**LOCK

t<sub>JR</sub>

PLL Lock Time [19]

Jitter

Cycle-to-Cycle Output

RMS<sup>[14]</sup>

[14]

Peak-to-Peak

9. Test measurement levels for the XRK49911 are TTL levels (1.5V to 1.5V). Test conditions assume signal transition times of 2 ns or less and output loading as shown in the AC Test Loads and Waveforms unless otherwise specified.

0.5

25

200

0.5

25

200

0.5

25

200

ms

ps

10. SKEW is defined as the time between the earliest and the latest output transition among all outputs for which the same  $t_{IJ}$  delay has been selected when all are loaded with 30pF and terminated with 50 $\Omega$  to  $V_{CC}/2$ .

#### XRK49911 3.3V HIGH-SPEED (110 MHZ) PROGRAMMABLE SKEW CLOCK BUFFER

- 11. *t*<sub>SKEWPR</sub> is defined as the skew between a pair of outputs (Qx0 and Qx1) when all eight outputs are selected for 0*t*<sub>U</sub>.

- 12. t<sub>SKEW0</sub> is defined as the skew between outputs when they are selected for 0t<sub>U</sub>. Other outputs are divided or inverted but not shifted

- 13. There are three classes of outputs: Nominal (multiple of  $t_U$  delay), Inverted (QD[1:0] only with SELD0 = SELD1 = HIGH), and Divided (QC[1:0] and QD[1:0] only in Divide-by-2 or Divide-by-4 mode).

- 14. Guaranteed by statistical correlation. Tested initially and after any design or process changes that may affect these parameters.

- 15. *t*<sub>DEV</sub> is the output-to-output skew between any two devices operating under the same conditions (V<sub>CC</sub> ambient temperature, air flow, etc.)

- 16.  $t_{ODCV}$  is the deviation of the output from a 50% duty cycle. Output pulse width variations are included in  $t_{SKEW2}$  and  $t_{SKEW4}$  specifications.

- Specified with outputs loaded with 30pF for the XRK49911-5 and -7 devices. Devices are terminated through 50Ω to V<sub>CC</sub>/2. t<sub>PWH</sub> is measured at 2.0V. t<sub>PWL</sub> is measured at 0.8V.

- 18. t<sub>ORISE</sub> and t<sub>OFALL</sub> measured between 0.8V and 2.0V.

- 19. t<sub>LOCK</sub> is the time that is required before synchronization is achieved. This specification is valid only after V<sub>CC</sub> is stable and within normal operating limits. This parameter is measured from the application of a new signal or frequency at CLKIN or FB\_IN until t<sub>PD</sub> is within specified limits

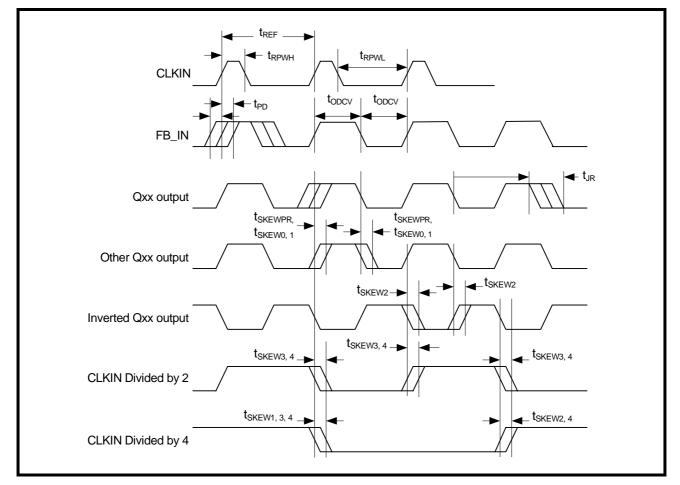

#### FIGURE 6. AC TIMING DIAGRAMS

**XP EXAR**

REV. 1.0.1

#### XRK49911 3.3V HIGH-SPEED (110 MHZ) PROGRAMMABLE SKEW CLOCK BUFFER

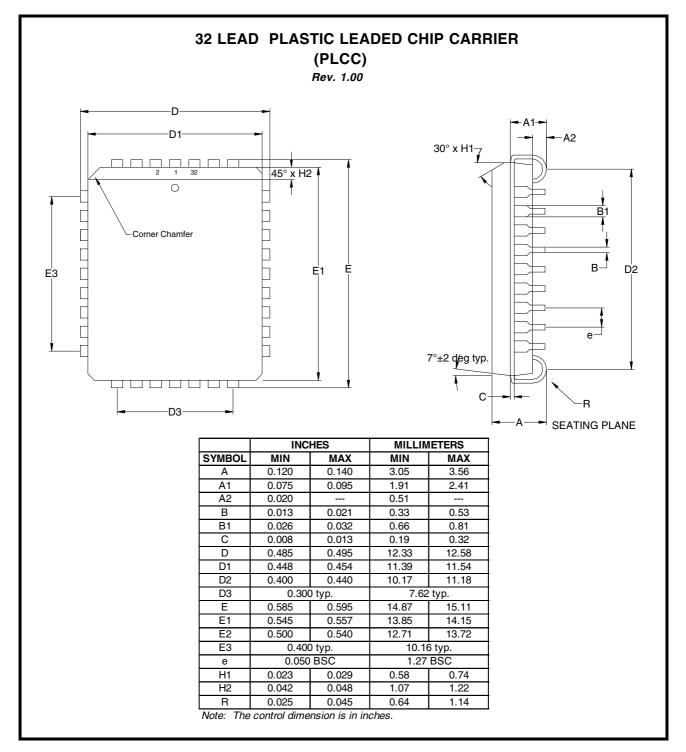

# **PACKAGE DIMENSIONS**

# **REVISION HISTORY**

| <b>REVISION #</b> | DATE            | DESCRIPTION                                                                    |

|-------------------|-----------------|--------------------------------------------------------------------------------|

| 1.0.0             | June 17, 2005   | Initial Production Release                                                     |

| 1.0.1             | October 5, 2005 | Product ordering information: Remove "F" product numbers and Lead Free column. |

|                   |                 |                                                                                |

|                   |                 |                                                                                |

|                   |                 |                                                                                |

|                   |                 |                                                                                |

|                   |                 |                                                                                |

|                   |                 |                                                                                |

|                   |                 |                                                                                |

#### NOTICE

EXAR Corporation reserves the right to make changes to the products contained in this publication in order to improve design, performance or reliability. EXAR Corporation assumes no responsibility for the use of any circuits described herein, conveys no license under any patent or other right, and makes no representation that the circuits are free of patent infringement. Charts and schedules contained here in are only for illustration purposes and may vary depending upon a user's specific application. While the information in this publication has been carefully checked; no responsibility, however, is assumed for inaccuracies.

EXAR Corporation does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless EXAR Corporation receives, in writing, assurances to its satisfaction that: (a) the risk of injury or damage has been minimized; (b) the user assumes all such risks; (c) potential liability of EXAR Corporation is adequately protected under the circumstances.

Copyright 2005 EXAR Corporation

Datasheet October 2005.

Reproduction, in part or whole, without the prior written consent of EXAR Corporation is prohibited.