Revision History Revision 0.1 (Jul. 2010)

- First release.

Revision 0.2 (Sep. 2010)

- Delete CL=2, page 2, 8, 17

- Add 166MHz@2.5-3-3; 200MHz@3-3-3, page 2

## 256Mb (4M×4Bank×16) Double DATA RATE SDRAM

#### **Features**

- Internal Double-Date-Rate architecture with twice accesses per clock cycle.

- Single 2.5V ±0.2V Power Supply

- 2.5V SSTL-2 compatible I/O

- Burst Length (B/L) of 2, 4, 8

- 2.5, 3 clock read latency

- Bi-directional, intermittent data strobe (DQS)

- All inputs except data and DM are sampled at the positive edge of the system clock.

- Data Mask (DM) for write data

- Sequential & Interleaved Burst type available

- Auto precharge option for each burst accesses

- DQS edge-aligned with data for Read cycles

- DQS center-aligned with data for Write cycles

- DLL aligns DQ & DQS transitions with CLK transition

- Auto Refresh and Self Refresh

- 8,192 Refresh Cycles / 64ms

### Description

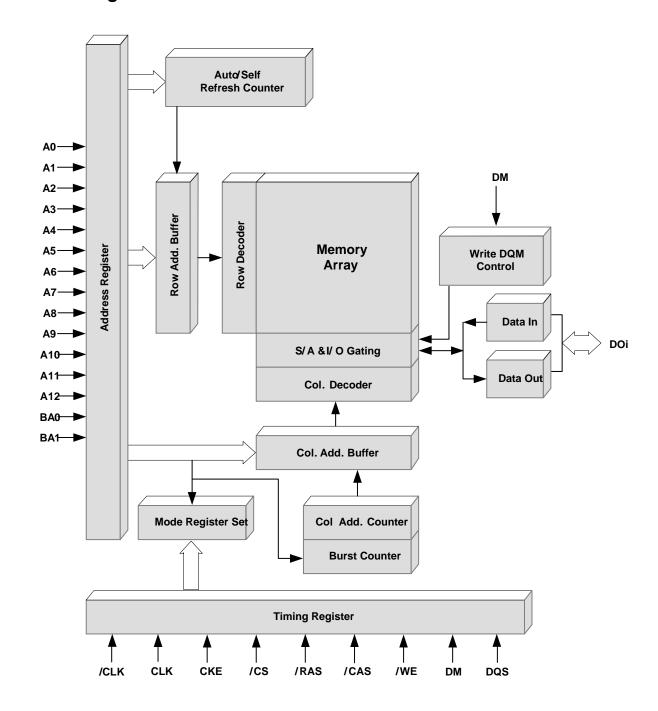

The EM42AM1684RTC is high speed Synchronous graphic RAM fabricated with ultra high performance CMOS process containing 268,435,456 bits which organized as 4Meg words x 4 banks by 16 bits.

The 256Mb DDR SDRAM uses a double data rate architecture to accomplish high-speed operation.

The data path internally prefetches multiple bits and transfers the data for both rising and falling edges of the system clock. It means the doubled data bandwidth can be achieved at the I/O pins.

Available package: TSOPII 66P 400mil.

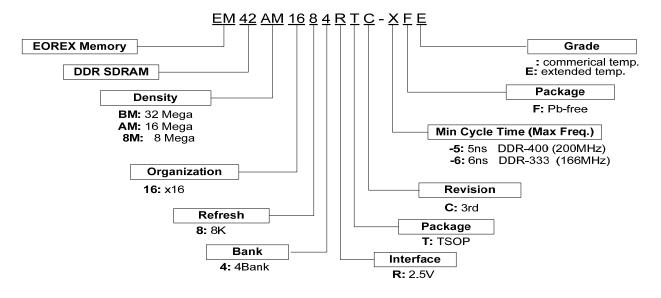

#### **Ordering Information**

| Part No           | Organization | Max. Freq         | Package        | Grade      | Pb   |

|-------------------|--------------|-------------------|----------------|------------|------|

| EM42AM1684RTC-6F  | 16M X 16     | 166MHz @CL2.5-3-3 | 66pin TSOP(II) | Commercial | Free |

| EM42AM1684RTC-5F  | 16M X 16     | 200MHz @CL3-3-3   | 66pin TSOP(II) | Commercial | Free |

| EM42AM1684RTC-6FE | 16M X 16     | 166MHz @CL2.5-3-3 | 66pin TSOP(II) | Extended   | Free |

| EM42AM1684RTC-5FE | 16M X 16     | 200MHz @CL3-3-3   | 66pin TSOP(II) | Extended   | Free |

<sup>\*</sup> EOREX reserves the right to change products or specification without notice.

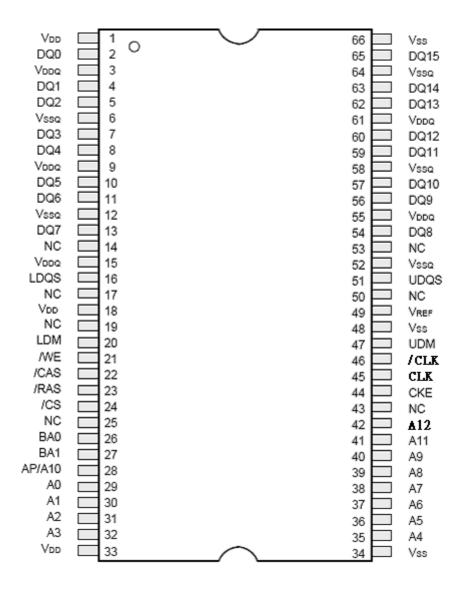

## Pin Assignment

66pin TSOP-II

## Pin Description (Simplified)

| Pin                                                             | Name                               | Function                                                                                                                                                                                                         |

|-----------------------------------------------------------------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 45,46                                                           | CLK,/CLK                           | (System Clock) Clock input active on the Positive rising edge except for DQ and DM are active on both edge of the DQS. CLK and /CLK are differential clock inputs.                                               |

| 24                                                              | /CS                                | (Chip Select) /CS enables the command decoder when"L" and disable the command decoder when "H". The new command are over-Looked when the command decoder is disabled but previous operation will still continue. |

| 44                                                              | CKE                                | (Clock Enable) Activates the CLK when "H" and deactivates when "L". When deactivate the clock, CKE low signifies the power down or self refresh mode.                                                            |

| 28~32,35~42                                                     | A0~A12                             | (Address) Row address (A0 to A12) and Column Address (CA0 to CA8) are multiplexed on the same pin. CA10 defines auto precharge at Column Address.                                                                |

| 26, 27                                                          | BA0, BA1                           | (Bank Address) Selects which bank is to be active.                                                                                                                                                               |

| 23                                                              | /RAS                               | (Row Address Strobe) Latches Row Addresses on the positive rising edge of the CLK with /RAS "L". Enables row access & pre-charge.                                                                                |

| 22                                                              | /CAS                               | (Column Address Strobe) Latches Column Addresses on the positive rising edge of the CLK with /CAS low. Enables column access.                                                                                    |

| 21                                                              | /WE                                | (Write Enable) Latches Column Addresses on the positive rising edge of the CLK with /CAS low. Enables column access.                                                                                             |

| 16/51                                                           | LDQS/UDQS                          | (Data Input/Output) Data Inputs and Outputs are synchronized with both edge of DQS.                                                                                                                              |

| 20/47                                                           | LDM/UDM                            | (Data Input/Output Mask) DM controls data inputs. LDM corresponds to the data on DQ0~DQ7.UDM corresponds to the data on DQ8~DQ15.                                                                                |

| 2, 4, 5, 7, 8, 10,<br>11, 13, 54, 56, 57,<br>59, 60, 62, 63, 65 | DQ0~DQ15                           | (Data Input/Output) Data inputs and outputs are multiplexed on the same pin.                                                                                                                                     |

| 1,18,33/<br>34,48,66                                            | V <sub>DD</sub> /V <sub>SS</sub>   | (Power Supply/Ground) V <sub>DD</sub> and V <sub>SS</sub> are power supply pins for internal circuits.                                                                                                           |

| 3, 9, 15, 55.61/<br>6, 12, 52, 58,64                            | V <sub>DDQ</sub> /V <sub>SSQ</sub> | (Power Supply/Ground) $V_{\text{DDQ}}$ and $V_{\text{SSQ}}$ are power supply pins for the output buffers.                                                                                                        |

| 14,17,19,25,43,<br>50,53                                        | NC/RFU                             | (No Connection/Reserved for Future Use) This pin is recommended to be left No Connection on the device.                                                                                                          |

| 49                                                              | VREF                               | (Input) SSTL-2 Reference voltage for input buffer.                                                                                                                                                               |

### **Absolute Maximum Rating**

| Symbol                             | Item                                        | Rat         | ting      | Units |

|------------------------------------|---------------------------------------------|-------------|-----------|-------|

| V <sub>IN</sub> , V <sub>OUT</sub> | Input, Output Voltage                       | -0.3 ~      | +3.6      | V     |

| $V_{DD}, V_{DDQ}$                  | Power Supply Voltage                        | -0.3 ~ +3.6 |           | V     |

| T <sub>OP</sub>                    | T <sub>OP</sub> Operating Temperature Range |             | 0 ~ +70   | °C    |

| I OP                               | Operating remperature Kange                 | Extended    | -25 ~ +85 | C     |

| T <sub>STG</sub>                   | Storage Temperature Range                   | -55 ~       | °C        |       |

| P <sub>D</sub>                     | Power Dissipation                           | 1.6         |           | W     |

| los                                | Short Circuit Current                       | 5           | 0         | mA    |

**Note:** Caution Exposing the device to stress above those listed in Absolute Maximum Ratings could cause permanent damage. The device is not meant to be operated under conditions outside the limits described in the operational section of this specification. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability.

### Capacitance ( $V_{CC}$ =2.5V, f=1MHz, $T_A$ =25 $^{\circ}C$ )

| Symbol           | Parameter                                                | Min. | Тур. | Max. | Units |

|------------------|----------------------------------------------------------|------|------|------|-------|

| C <sub>CLK</sub> | Clock Capacitance(CLK,/CLK)                              | 2.0  | -    | 3.0  | pF    |

| Cı               | Input Capacitance for CKE, Address, /CS, /RAS, /CAS, /WE | 2.0  | -    | 3.0  | pF    |

| Co               | DM & DQS Input/Output Capacitance                        | 4.0  | -    | 5.0  | рF    |

## Recommended DC Operating Conditions ( $T_A$ =-0°C ~+70°C)

| Symbol          | Parameter                             | Min.                   | Тур.          | Max.                   | Units |

|-----------------|---------------------------------------|------------------------|---------------|------------------------|-------|

| $V_{DD}$        | Power Supply Voltage                  | 2.3                    | 2.5           | 2.7                    | V     |

| $V_{DDQ}$       | Power Supply Voltage (for I/O Buffer) | 2.3                    | 2.5           | 2.7                    | V     |

| $V_{REF}$       | I/O Logic high Voltage                | $0.49*V_{DDQ}$         | $0.5*V_{DDQ}$ | 0.51*V <sub>DDQ</sub>  | V     |

| $V_{TT}$        | I/O Termination Voltage               | V <sub>REF</sub> -0.04 | -             | V <sub>REF</sub> +0.04 | V     |

| V <sub>IH</sub> | Input Logic High Voltage              | V <sub>REF</sub> +0.15 | •             | V <sub>DDQ</sub> +0.3  | V     |

| V <sub>IL</sub> | Input Logic Low Voltage               | -0.3                   | •             | V <sub>REF</sub> -0.15 | V     |

## **Recommended DC Operating Conditions**

$(V_{DD}=2.5V\pm0.2V, T_A=0^{\circ}C \sim 70^{\circ}C)$

| Cumbal            | Parameter                                                               | Test Conditions                                                                                                                                                | Max.     |     | Units |        |  |

|-------------------|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----|-------|--------|--|

| Symbol            | Parameter                                                               | rest Conditions                                                                                                                                                |          | -5  | -6    | Ullits |  |

| I <sub>DD1</sub>  | Operating Current (Note 1)                                              | Burst length=4,<br>t <sub>RC</sub> ≥t <sub>RC</sub> (min.), l <sub>OL</sub> =0mA,<br>One bank active                                                           |          | 150 | 145   | mA     |  |

| I <sub>DD2P</sub> | Precharge Standby Current in Power Down Mode                            | CKE≤V <sub>IL</sub> (max.), t <sub>CK</sub> =min                                                                                                               |          | 30  | 30    | mA     |  |

| I <sub>DD2N</sub> | Precharge Standby Current in<br>Non-power Down Mode<br>(All banks idle) | CKE≥V <sub>IH</sub> (min.), t <sub>CK</sub> =min,<br>/CS≥V <sub>IH</sub> (min.), V <sub>IN</sub> =V <sub>REF</sub><br>Input signals are changed<br>clock cycle | 65       | 65  | mA    |        |  |

| I <sub>DD3P</sub> | Active Standby Current in Power Down Mode                               | CKE≤V <sub>IL</sub> (max.), t <sub>CK</sub> =min<br>One bank active, V <sub>IN</sub> =V <sub>REF</sub>                                                         | 40       | 40  | mA    |        |  |

| I <sub>DD3N</sub> | Active Standby Current in Non-power Down Mode                           | CKE≥V <sub>IH</sub> (min.), t <sub>CK</sub> =min,<br>/CS≥V <sub>IH</sub> (min.)<br>Input signals are changed<br>clock cycle                                    | once per | 115 | 115   | mA     |  |

| ı                 | Operating Current (Note 2)                                              | $t_{CK} \ge t_{CK}(min.), I_{OL}=0mA,$                                                                                                                         | READ     | 180 | 165   | mA     |  |

| I <sub>DD4</sub>  | Operating Current · /                                                   | One banks active, BL=2                                                                                                                                         | WRITE    | 165 | 150   | ША     |  |

| I <sub>DD5</sub>  | Refresh Current (Note 3)                                                | t <sub>RC</sub> ≥ t <sub>RFC</sub> (min.), All banks a                                                                                                         | 150      | 145 | mA    |        |  |

| lan.              | Self Refresh Current                                                    | CKE≤0.2V, standard                                                                                                                                             | 5        | 5   | mA    |        |  |

| I <sub>DD6</sub>  | Och Kellesh Cullent                                                     | Low power                                                                                                                                                      | 2.5      | 2.5 | mA    |        |  |

| I <sub>DD7</sub>  | Operating current (Four Banks)                                          | Four Banks interleaving, B                                                                                                                                     | L=4      | 295 | 295   | mA     |  |

<sup>\*</sup>All voltages referenced to  $V_{\text{SS}}$ .

Note 1: I<sub>DD1</sub> depends on output loading and cycle rates.

Specified values are obtained with the output open.

Input signals are changed only one time during t<sub>CK</sub> (min.)

Note 2: I<sub>DD4</sub> depends on output loading and cycle rates.

Specified values are obtained with the output open.

Input signals are changed only one time during  $t_{CK}$  (min.)

Note 3: Min. of t<sub>RFC</sub> (Auto refresh Row Cycle Times) is shown at AC Characteristics.

## Recommended DC Operating Conditions (Continued)

| Symbol          | Parameter                 | Test Conditions                                                                    | Min. | Max. | Units |

|-----------------|---------------------------|------------------------------------------------------------------------------------|------|------|-------|

| I <sub>IL</sub> | Input Leakage Current     | $0 \le V_{I} \le V_{DDQ}$ , $V_{DDQ} = V_{DD}$<br>All other pins not under test=0V | -2   | +2   | uA    |

| I <sub>OL</sub> | Output Leakage Current    | $0 \le V_O \le V_{DDQ}$ , $D_{OUT}$ is disabled                                    | -5   | +5   | uA    |

| V <sub>OH</sub> | High Level Output Voltage | I <sub>O</sub> =-16.2mA                                                            | 1.95 | -    | V     |

| V <sub>OL</sub> | Low Level Output Voltage  | I <sub>O</sub> =+16.2mA                                                            | -    | 0.35 | V     |

## **Block Diagram**

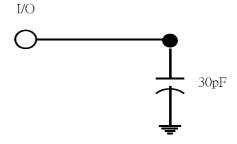

## **AC Operating Test Conditions**

$(V_{DD}=2.5V\pm0.2V, T_{A}=0^{\circ}C \sim 70^{\circ}C)$

| Item                             | Conditions                                     | Unit |

|----------------------------------|------------------------------------------------|------|

| Output Reference Level           | 1.25/1.25                                      | V    |

| Output Load                      | See diagram as below                           | V    |

| Input Signal Level               | V <sub>REF</sub> +0.31/ V <sub>REF</sub> -0.31 | V    |

| Transition Time of Input Signals | 1ns                                            | ns   |

| Input Reference Level            | V <sub>DDQ</sub> /2                            | V    |

## AC Operating Test Characteristics

$(V_{DD}=2.5V\pm0.2V, T_{A}=0^{\circ}C \sim 70^{\circ}C)$

| Symbol                             | Paramete                                       |                                 | -    | 5    | -6   |      | Units           |

|------------------------------------|------------------------------------------------|---------------------------------|------|------|------|------|-----------------|

| Symbol                             | Paramete                                       |                                 | Min. | Max. | Min. | Max. | Units           |

| $t_{DQCK}$                         | DQ output access from CL                       | -0.7                            | 0.7  | -0.7 | 0.7  | ns   |                 |

| t <sub>DQSCK</sub>                 | DQS output access from C                       | DQS output access from CLK,/CLK |      | 0.6  | -0.6 | 0.6  | ns              |

| $t_{CL}, t_{CH}$                   | CL low/high level width                        |                                 | 0.45 | 0.55 | 0.45 | 0.55 | t <sub>CK</sub> |

|                                    | Clock Cycle Time                               | CL=3                            | 5    | 12   | -    | -    | ns              |

| t <sub>CK</sub>                    | Clock Cycle Time                               | CL=2.5                          | -    | -    | 6    | 12   | ns              |

| t <sub>DH</sub> ,t <sub>DS</sub>   | DQ and DM hold/setup time                      | e                               | 0.4  | -    | 0.45 | -    | ns              |

| t <sub>DIPW</sub>                  | DQ and DM input pulse width for each input     |                                 | 1.75 | -    | 1.75 | -    | ns              |

| $t_{HZ},t_{LZ}$                    | Data out high/low impedance time from CLK,/CLK |                                 | -0.7 | 0.7  | -0.7 | 0.7  | ns              |

| t <sub>DQSQ</sub>                  | DQS-DQ skew for associated DQ signal           |                                 | 0.4  | -    | 0.45 | -    | ns              |

| t <sub>DQSS</sub>                  | Write command to first late transition         | hing DQS                        | 0.72 | 1.25 | 0.75 | 1.25 | t <sub>CK</sub> |

| t <sub>DSL</sub> ,t <sub>DSH</sub> | DQS input valid window                         |                                 | 0.35 | -    | 0.35 | -    | t <sub>CK</sub> |

| t <sub>MRD</sub>                   | Mode Register Set comma                        | nd cycle time                   | 2    | -    | 2    | -    | t <sub>CK</sub> |

| t <sub>WPRES</sub>                 | Write Preamble setup time                      |                                 | 0    | -    | 0    | -    | ns              |

| t <sub>WPST</sub>                  | Write Preamble                                 |                                 | 0.4  | 0.6  | 0.4  | 0.6  | t <sub>CK</sub> |

|                                    | Address/control input hold/                    | setup time (Slow)               | 0.7  | -    | 0.8  | -    | ns              |

| t <sub>IH</sub> ,t <sub>IS</sub>   | Address/control input hold/setup time (Fast)   |                                 | 0.6  | -    | 0.75 | -    | ns              |

| t <sub>RPRE</sub>                  | Read Preamble                                  |                                 | 0.9  | 1.1  | 0.9  | 1.1  | t <sub>CK</sub> |

| t <sub>DSH</sub>                   | DQS falling edge from CLK                      | rising, hold time               | 0.2  | -    | 0.2  | -    | t <sub>CK</sub> |

| t <sub>DSS</sub>                   | DQS falling edge to CLK ris                    | sing, setup time                | 0.2  | -    | 0.2  | -    | t <sub>CK</sub> |

## AC Operating Test Characteristics (Continued)

$(V_{DD}=2.5V\pm0.2V, T_{A}=0^{\circ}C \sim 70^{\circ}C)$

| Symbol            | Parameter                                  | _    | 5    | _    | 6    | Units           |

|-------------------|--------------------------------------------|------|------|------|------|-----------------|

| Symbol            | i alametei                                 | Min. | Max. | Min. | Max. | Office          |

| t <sub>RPST</sub> | Read Postamble                             | 0.4  | 0.6  | 0.4  | 0.6  | t <sub>CK</sub> |

| t <sub>RAS</sub>  | Active to Precharge command period         | 40   | 120k | 42   | 120k | ns              |

| t <sub>RC</sub>   | Active to Active command period            | 55   | -    | 60   | -    | ns              |

| t <sub>RFC</sub>  | Auto Refresh Row Cycle Time                | 70   | -    | 72   | -    | ns              |

| t <sub>RCD</sub>  | Active to Read or Write delay              | 15   | -    | 18   | -    | ns              |

| t <sub>RP</sub>   | Precharge command period                   | 15   | -    | 18   | -    | ns              |

| t <sub>RRD</sub>  | Active bank A to B command period          | 10   | -    | 12   | -    | ns              |

| t <sub>RAP</sub>  | Active to READ with Auto Precharge command | 15   | -    | 18   | -    | ns              |

| t <sub>WPRE</sub> | DQS write Preamble                         | 0.25 | -    | 0.25 | -    | t <sub>CK</sub> |

| t <sub>WR</sub>   | Write Recovery time                        | 15   | -    | 15   | -    | ns              |

| t <sub>WTR</sub>  | Internal WRITE to READ command delay       | 2    | -    | 2    | -    | t <sub>CK</sub> |

| t <sub>XSNR</sub> | Exit self Refresh to non-read command      | 75   | -    | 75   | -    | ns              |

| t <sub>XSRD</sub> | Exit self Refresh to read command          | 200  | -    | 200  | -    | ns              |

| t <sub>REFI</sub> | Average periodic refresh interval          | -    | 7.8  | -    | 7.8  | us              |

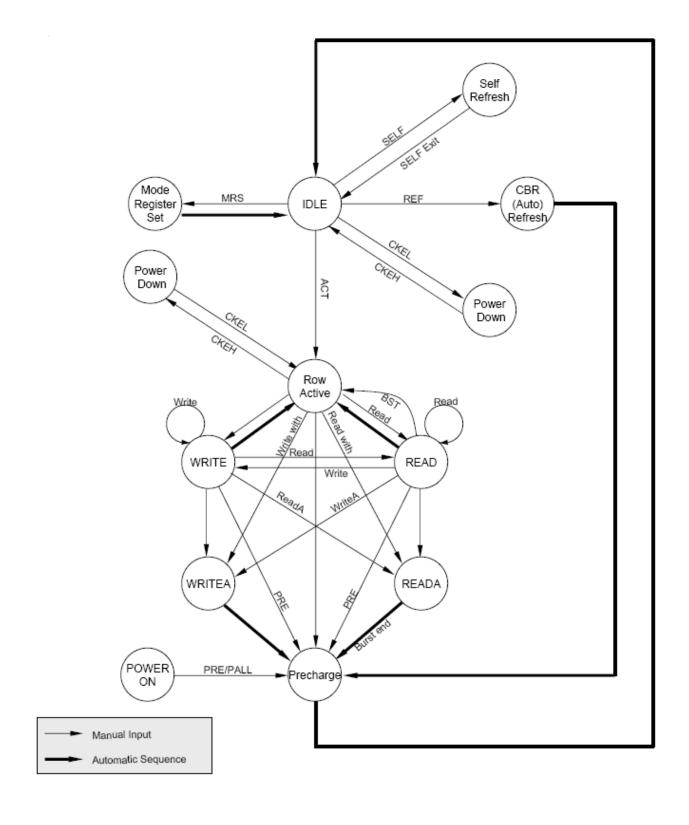

## Simplified State Diagram

### 1. Command Truth Table

|                   |        | Cł      | ΚE |     |       |      |    | BA0,    |         |        |

|-------------------|--------|---------|----|-----|-------|------|----|---------|---------|--------|

| Command           | Symbol | n-<br>1 | N  | /CS | /RAS  | /CAS | WE | BAU,    | A10     | A12~A0 |

| Ignore Command    | DESL   | Н       | Х  | Н   | Х     | Х    | Х  | Х       | Х       | Х      |

| No Operation      | NOP    | Н       | Х  | L   | Н     | Н    | Н  | Х       | Х       | Х      |

| Burst Stop        | BSTH   | Н       | Χ  | L   | Н     | Н    | L  | Х       | Х       | Х      |

| Read              | READ   | Н       | Χ  | L   | Н     | L    | Н  | V       | L       | V      |

| Read with Auto    | READ   | Н       | Х  | L   | Н     | L    | Н  | V       | Н       | V      |

| Pre-charge        | А      | П       | ^  | _   | П     | L    |    | V       | П       | V      |

| Write             | WRIT   | Н       | Х  | L   | Н     | L    | L  | V       | L       | V      |

| Write with Auto   | WRITA  | Н       | Х  | L   | Н     | L    | L  | V       | Н       | V      |

| Pre-charge        | WKITA  | 11      | ^  | L   | 11    | L    | L  | V       | 11      | V      |

| Bank Activate     | ACT    | Ι       | Χ  | L   | L     | Н    | Н  | V       | V       | V      |

| Pre-charge Select | PRE    | Η       | Х  | L   | L     | Н    | L  | V       | L       | Х      |

| Bank              | PRE    | Ε       | ^  | L   | L     | П    | L  | V       | L       | ^      |

| Pre-charge All    | PALL   | Н       | Х  | L   | L     | Н    | L  | Х       | Н       | Х      |

| Banks             | FALL   | П       | ^  | L   | L<br> |      | L  |         | П       | ^      |

| Mode Register Set | MRS    | Ι       | Χ  | L   | L     | L    | L  | OP Code |         |        |

| Extended MRS      | EMRS   | Н       | Χ  | L   | L     | L    | L  |         | OP Code |        |

H = High level, L = Low level, X = High or Low level (Don't care), V = Valid data input

#### 2. CKE Truth Table

| Item          | Command             | Cumbal | CKI | ≣  | /CS | /RAS | /CAS | /WE | Addr. |

|---------------|---------------------|--------|-----|----|-----|------|------|-----|-------|

| item          | Command             | Symbol | n-1 | n  | 703 | /KAS | /CAS | /VV | Addi. |

| Idle          | CBR Refresh Command | REF    | Ι   | Η  | L   | L    | L    | Τ   | X     |

| Idle          | Self Refresh Entry  | SELF   | Η   | L  | L   | L    | L    | Η   | Х     |

| Self Refresh  | Self Refresh Exit   | -      | L   | Н  | L   | Н    | Н    | Н   | Х     |

| Sell Kellesii | Sell Reliesh Exit   | _      | L   | Н  | Н   | Х    | Х    | Х   | Х     |

| Idle          | Power Down Entry    | _      | Н   | L  | Х   | Х    | Х    | Х   | Х     |

| Power         | Power Down Exit     | _      | L   | Н  | Х   | Х    | Х    | Х   | Х     |

| Down          | Fower Down Exit     |        | L   | 17 | ^   | ^    | ^    | ^   | ^     |

H = High level, L = Low level, X = High or Low level (Don't care)

## 3. Operative Command Table

| Current          |     |    |    |    |                      |              |                                                                                   |  |  |

|------------------|-----|----|----|----|----------------------|--------------|-----------------------------------------------------------------------------------|--|--|

| Current<br>State | /CS | /R | /C | /W | Addr.                | Command      | Action                                                                            |  |  |

|                  | Н   | Χ  | Χ  | Х  | X                    | DESL         | NOP                                                                               |  |  |

|                  | L   | Ι  | Н  | Н  | X                    | NOP          | NOP                                                                               |  |  |

|                  | L   | Н  | Н  | L  | X                    | TERM         | NOP                                                                               |  |  |

|                  | L   | Н  | L  | Х  | BA/CA/A10            | READ/WRIT/BW | ILLEGAL (Note 1)                                                                  |  |  |

| Idle             | L   | L  | Н  | Н  | BA/RA                | ACT          | Bank active,Latch RA                                                              |  |  |

|                  | L   | L  | Н  | L  | BA, A10              | PRE/PREA     | NOP(Note 3)                                                                       |  |  |

|                  | L   | L  | L  | Н  | Х                    | REFA         | Auto refresh(Note 4)                                                              |  |  |

|                  | L   | L  | L  | L  | Op-Code,<br>Mode-Add | MRS          | Mode register                                                                     |  |  |

|                  | Н   | Χ  | Χ  | Χ  | X                    | DESL         | NOP                                                                               |  |  |

|                  | L   | Н  | Н  | Н  | X                    | NOP          | NOP                                                                               |  |  |

|                  | L   | Н  | Н  | L  | BA/CA/A10            | READ/READA   | Begin read,Latch CA, Determine auto-precharge                                     |  |  |

| Row              | L   | Н  | L  | L  | BA/CA/A10            | WRIT/WRITA   | Begin write,Latch CA, Determine auto-precharge                                    |  |  |

| Active           | L   | L  | Н  | Н  | BA/RA                | ACT          | ILLEGAL (Note 1)                                                                  |  |  |

|                  | L   | L  | Н  | L  | BA/A10               | PRE/PREA     | Precharge/Precharge all                                                           |  |  |

|                  | L   | L  | L  | Н  | Х                    | REFA         | ILLEGAL                                                                           |  |  |

|                  | L   | L  | L  | L  | Op-Code,<br>Mode-Add | MRS          | ILLEGAL                                                                           |  |  |

|                  | Н   | Χ  | Х  | Χ  | X                    | DESL         | NOP(Continue burst to end)                                                        |  |  |

|                  | L   | Η  | Н  | Н  | X                    | NOP          | NOP(Continue burst to end)                                                        |  |  |

|                  | L   | Н  | Н  | L  | X                    | TERM         | Terminal burst                                                                    |  |  |

| Read             | L   | Н  | L  | Н  | BA/CA/A10            | READ/READA   | Terminate burst,Latch CA, Begin new read, Determine Auto-precharge                |  |  |

|                  | L   | L  | Н  | Н  | BA/RA                | ACT          | ILLEGAL (Note 1)                                                                  |  |  |

|                  | L   | L  | Н  | L  | BA, A10              | PRE/PREA     | Terminate burst, PrecharE                                                         |  |  |

|                  | L   | L  | L  | Н  | X                    | REFA         | ILLEGAL                                                                           |  |  |

|                  | L   | L  | L  | L  | Op-Code,<br>Mode-Add | MRS          | ILLEGAL                                                                           |  |  |

|                  | Н   | Χ  | Χ  | Χ  | X                    | DESL         | NOP(Continue burst to end)                                                        |  |  |

|                  | L   | Н  | Н  | Н  | X                    | NOP          | NOP(Continue burst to end)                                                        |  |  |

|                  | L   | Н  | Н  | L  | X                    | TERM         | ILLEGAL                                                                           |  |  |

|                  | L   | Н  | L  | Н  | BA/CA/A10            | READ/READA   | Terminate burst with DM="H",Latch CA,Begin read,Determine auto-precharge (Note 2) |  |  |

| Write            | L   | Н  | L  | L  | BA/CA/A10            | WRIT/WRITA   | Terminate burst,Latch CA,Begin new write, Determine auto-precharge (Note 2)       |  |  |

|                  | L   | L  | Н  | Н  | BA/RA                | ACT          | ILLEGAL (Note 1)                                                                  |  |  |

|                  | L   | L  | Н  | L  | BA, A10              | PRE/PREA     | Terminate burst with DM="H", Precharge                                            |  |  |

|                  | L   | L  | L  | Н  | Х                    | REFA         | ILLEGAL                                                                           |  |  |

|                  | L   | L  | L  | L  | Op-Code,             | MRS          | ILLEGAL                                                                           |  |  |

## 3. Operative Command Table (Continued)

| Current<br>State  | /CS | /R | /C | /W | Addr.                | Command    | Action                       |

|-------------------|-----|----|----|----|----------------------|------------|------------------------------|

|                   | Н   | Χ  | Χ  | Х  | Х                    | DESL       | NOP(Continue burst to end)   |

|                   | L   | Н  | Н  | Н  | Х                    | NOP        | NOP(Continue burst to end)   |

|                   | L   | Н  | Н  | L  | BA/CA/A10            | TERM       | ILLEGAL                      |

| Read with AP      | L   | Н  | L  | Х  | BA/RA                | READ/WRITE | ILLEGAL (Note 1)             |

|                   | L   | L  | Н  | Н  | BA/A10               | ACT        | ILLEGAL (Note 1)             |

|                   | L   | L  | Н  | L  | Х                    | PRE/PREA   | ILLEGAL (Note 1)             |

|                   | L   | L  | L  | Н  | X                    | REFA       | ILLEGAL                      |

|                   | L   | L  | L  | L  | Op-Code,<br>Mode-Add | MRS        | ILLEGAL                      |

|                   | Н   | Χ  | Х  | Χ  | X                    | DESL       | NOP(Continue burst to end)   |

|                   | L   | Н  | Н  | Н  | Х                    | NOP        | NOP(Continue burst to end)   |

|                   | L   | Н  | Н  | L  | Х                    | TERM       | ILLEGAL                      |

|                   | L   | Н  | L  | Χ  | BA/CA/A10            | READ/WRITE | ILLEGAL (Note 1)             |

| Write with AP     | L   | L  | Н  | Н  | BA/RA                | ACT        | ILLEGAL (Note 1)             |

|                   | L   | L  | Н  | L  | BA/A10               | PRE/PREA   | ILLEGAL (Note 1)             |

|                   | L   | L  | L  | Н  | Х                    | REFA       | ILLEGAL                      |

|                   | L   | L  | L  | L  | Op-Code,<br>Mode-Add | MRS        | ILLEGAL                      |

|                   | Н   | Χ  | Χ  | Χ  | Х                    | DESL       | NOP(idle after trp)          |

|                   | ┙   | Ι  | Н  | Ι  | X                    | NOP        | NOP(idle after trp)          |

|                   | L   | Н  | Н  | L  | X                    | TERM       | NOP                          |

|                   | L   | Н  | L  | Х  | BA/CA/A10            | READ/WRITE | ILLEGAL (Note 1)             |

| Pre-charging      | L   | L  | Η  | Н  | BA/RA                | ACT        | ILLEGAL (Note 1)             |

|                   | L   | L  | Н  | L  | BA/A10               | PRE/PREA   | NOP(idle after trp) (Note 3) |

|                   | L   | L  | L  | Η  | X                    | REFA       | ILLEGAL                      |

|                   | L   | L  | L  | L  | Op-Code,<br>Mode-Add | MRS        | ILLEGAL                      |

|                   | Ι   | Χ  | Χ  | Χ  | X                    | DESL       | NOP(Row active after tRCD)   |

|                   | L   | Н  | Н  | Н  | X                    | NOP        | NOP(Row active after trcd)   |

|                   | L   | Н  | Н  | L  | X                    | TERM       | NOP                          |

| Dow.              | L   | Н  | L  | Χ  | BA/CA/A10            | READ/WRITE | ILLEGAL (Note 1)             |

| Row<br>Activating | L   | L  | Н  | Н  | BA/RA                | ACT        | ILLEGAL (Note 1)             |

|                   | L   | L  | Н  | L  | BA/A10               | PRE/PREA   | ILLEGAL (Note 1)             |

|                   | L   | L  | L  | Н  | Х                    | REFA       | ILLEGAL                      |

|                   | L   | L  | L  | L  | Op-Code,<br>Mode-Add | MRS        | ILLEGAL                      |

H = High level, L = Low level, X = High or Low level (Don't care), AP = Auto Pre-charge

## 3. Operative Command Table (Continued)

| Current State | /CS | /R | /C | /W | Addr.                | Command    | Action                  |

|---------------|-----|----|----|----|----------------------|------------|-------------------------|

|               | Н   | Χ  | Χ  | Χ  | Х                    | DESL       | NOP                     |

|               | L   | Н  | Н  | Н  | Х                    | NOP        | NOP                     |

|               | L   | Н  | Н  | L  | Х                    | TERM       | NOP                     |

|               | L   | Н  | L  | Н  | BA/CA/A10            | READ       | ILLEGAL(Note 1)         |

| Write         | L   | Н  | L  | L  | BA/CA/A10            | WRIT/WRITA | New write, Determine AP |

| Recovering    | L   | L  | Н  | Н  | BA/RA                | ACT        | ILLEGAL (Note 1)        |

|               | L   | L  | Н  | L  | BA/A10               | PRE/PREA   | ILLEGAL (Note 1)        |

|               | L   | L  | L  | Н  | Х                    | REFA       | ILLEGAL                 |

|               | L   | L  | L  | L  | Op-Code,<br>Mode-Add | MRS        | ILLEGAL                 |

|               | Н   | Χ  | Χ  | Χ  | Χ                    | DESL       | NOP(idle after trp)     |

|               | L   | Ι  | Η  | Ι  | X                    | NOP        | NOP(idle after trp)     |

|               | L   | Ι  | Н  | L  | X                    | TERM       | NOP                     |

|               | L   | Ι  | L  | Χ  | BA/CA/A10            | READ/WRIT  | ILLEGAL                 |

| Refreshing    | L   | L  | Η  | Ι  | BA/RA                | ACT        | ILLEGAL                 |

|               | L   | L  | Н  | L  | BA/A10               | PRE/PREA   | NOP(idle after trp)     |

|               | L   | L  | L  | Н  | X                    | REFA       | ILLEGAL                 |

|               | L   | L  | L  | L  | Op-Code,<br>Mode-Add | MRS        | ILLEGAL                 |

H = High level, L = Low level, X = High or Low level (Don't care), AP = Auto Pre-charge

Note 1: ILLEGAL to bank in specified states;

Function may be legal in the bank indicated by Bank Address (BA), depending on the state of that bank.

Note 2: Must satisfy bus contention, bus turn around, and/or write recovery requirements.

Note 3: NOP to bank precharging or in idle state. May precharge bank indicated by BA.

Note 4: ILLEGAL of any bank is not idle.

#### 4. Command Truth Table for CKE

| Current State                     | Cł  | ΚE | /CS | /R | /C | /W    | Addr.   | Action                                 |

|-----------------------------------|-----|----|-----|----|----|-------|---------|----------------------------------------|

| Current State                     | n-1 | n  | 700 | /K |    | / ۷ ۷ | Addi.   | ACIIOII                                |

|                                   | Н   | Χ  | Χ   | Χ  | Χ  | Χ     | X       | INVALID                                |

|                                   | L   | Ι  | Н   | Χ  | Χ  | Χ     | X       | Exist Self-Refresh                     |

|                                   | L   | Н  | L   | Н  | Н  | Н     | Х       | Exist Self-Refresh                     |

| Self Refresh                      | L   | Н  | L   | Н  | Н  | L     | X       | ILLEGAL                                |

|                                   | L   | Н  | L   | Н  | L  | Χ     | Χ       | ILLEGAL                                |

|                                   | L   | Н  | L   | L  | Χ  | Χ     | X       | ILLEGAL                                |

|                                   | L   | L  | Χ   | Χ  | Χ  | Χ     | Х       | NOP(Maintain self refresh)             |

|                                   | Н   | Χ  | Х   | Χ  | Χ  | Χ     | X       | INVALID                                |

| Both bank                         | L   | Н  | Н   | Χ  | Χ  | Χ     | Χ       | Exist Power down                       |

| precharge                         | L   | Η  | L   | Н  | Н  | Η     | X       | Exist Power down                       |

| power down                        | L   | Н  | L   | Н  | Н  | L     | X       | ILLEGAL                                |

| power down                        | L   | Н  | L   | Н  | L  | Χ     | Χ       | ILLEGAL                                |

|                                   | L   | Н  | L   | L  | Χ  | Χ     | X       | ILLEGAL                                |

|                                   | L   | L  | Χ   | Χ  | Χ  | Χ     | X       | NOP(Maintain Power down)               |

|                                   | Н   | Н  | Х   | Χ  | Χ  | Χ     | X       | Refer to function true table           |

|                                   | Н   | L  | Н   | Х  | Χ  | Χ     | Χ       | Enter power down mode (Note 3)         |

|                                   | Н   | L  | L   | Н  | Н  | Н     | Х       | Enter power down mode (Note 3)         |

|                                   | Н   | L  | L   | Н  | Н  | L     | Х       | ILLEGAL                                |

| All Banks                         | Н   | L  | L   | Н  | L  | Χ     | Х       | ILLEGAL                                |

| Idle                              | Н   | L  | L   | L  | Η  | Ι     | RA      | Row active/Bank active                 |

|                                   | Н   | L  | L   | L  | L  | Η     | Х       | Enter self-refresh <sup>(Note 3)</sup> |

|                                   | Н   | L  | L   | L  | L  | L     | Op-Code | Mode register access                   |

|                                   | Н   | L  | L   | L  | L  | L     | Op-Code | Special mode register access           |

|                                   | L   | Х  | Х   | Χ  | Χ  | Χ     | Х       | Refer to current state                 |

| Any State Other than Listed above | Н   | Н  | Х   | Х  | Х  | Х     | Х       | Refer to command truth table           |

H = High level, L = Low level, X = High or Low level (Don't care)

**Notes 1:** After CKE's low to high transition to exist self refresh mode. And a time of tRC(min) has to be elapse after CKE's low to high transition to issue a new command.

Notes 2:CKE low to high transition is asynchronous as if restarts internal clock.

Notes 3: Power down and self refresh can be entered only from the idle state of all banks.

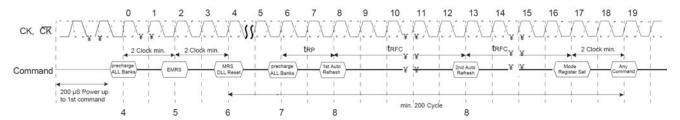

### The Sequence of Power-Up and Initialization

The following sequence is required for Power-Up and Initialization.

- 1. Apply power and attempt to maintain CKE at a low state (all other inputs may be undefined.)

- Apply VDD before or at the same time as VDDQ.

- Apply VDDQ before or at the same time as VTT & VREF.

- 2. Start clock and maintain stable condition for a minimum of 200us.

- 3. The minimum of 200us after stable power and clock (CLK, CLK), apply NOP & take CKE high.

- 4. Precharge all banks.

- 5. Issue EMRS to enable DLL.(To issue "DLL Enable" command, provide "Low" to A0, "High" to BA0 and "Low" to all of the rest address pins, A1~A11 and BA1)

- 6. Issue a mode register set command for "DLL reset". The additional 200 cycles of clock input is required to lock the DLL. (To issue DLL reset command, provide "High" to A8 and "Low" to BA0)

- 7. Issue precharge commands for all banks of the device.

- 8. Issue 2 or more auto-refresh commands.

- 9. Issue a mode register set command to initialize device operation.

#### Power up Sequence & Auto Refresh(CBR)

Note1 Every "DLL enable" command resets DLL. Therefore sequence 6 can be skipped during power up. Instead of it, the additional 200 cycles of clock input is required to lock the DLL after enabling DLL.

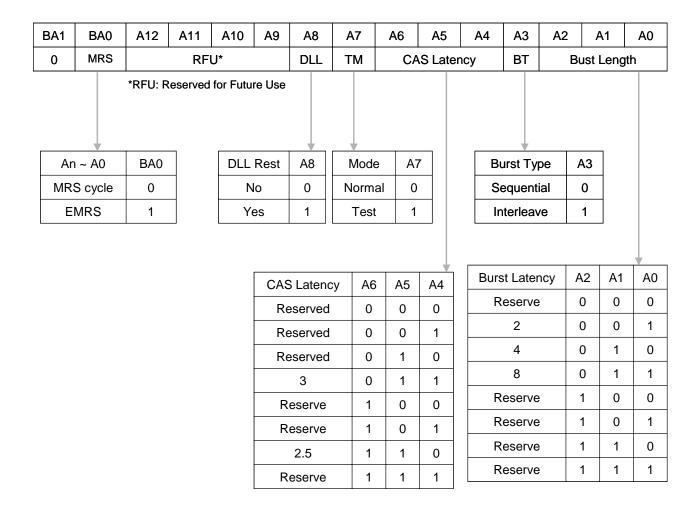

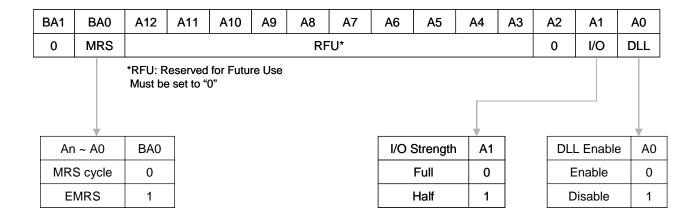

### **Mode Register Definition**

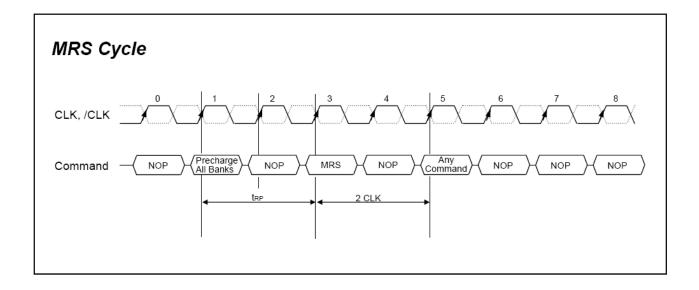

#### Mode Register Set

The mode register stores the data for controlling the various operating modes of DDR SDRAM which contains addressing mode, burst length, /CAS latency, test mode, DLL reset and various vendor's specific opinions. The defaults value of the register is not defined, so the mode register must be written after EMRS setting for proper DDR SDRAM operation. The mode register is written by asserting low on /CS, /RAS, /CAS, /WE and BA0 (The DDR SDRAM should be in all bank precharge with CKE already high prior to writing into the mode register.) The state of the address pins A0-A12 in the same cycle as /CS, /RAS, /CAS, /WE and BA0 going low is written in the mode register. Two clock cycles are requested to complete the write operation in the mode register. The mode register contents can be changed using the same command and clock cycle requirements during operating as long as all banks are in the idle state. The mode register is divided into various fields depending on functionality. The burst length uses A0-A2, addressing mode uses A3, /CAS latency (read latency from column address) uses A4-A6. A7 is used for test mode. A8 is used for DDR reset. A7 must be set to low for normal MRS operation.

## Address input for Mode Register Set

## Burst Type (A3)

| Burst Length | A2 | A1 | A0 | Sequential Addressing | Interleave Addressing |

|--------------|----|----|----|-----------------------|-----------------------|

| 2            | Х  | Х  | 0  | 0 1                   | 0 1                   |

| 2            | Х  | Х  | 0  | 10                    | 10                    |

|              | Χ  | 0  | 0  | 0123                  | 0123                  |

| 4            | Χ  | 0  | 1  | 1230                  | 1032                  |

| 4            | Х  | 1  | 0  | 2301                  | 2301                  |

|              | Χ  | 1  | 1  | 3012                  | 3210                  |

|              | 0  | 0  | 0  | 01234567              | 01234567              |

|              | 0  | 0  | 1  | 12345670              | 10325476              |

|              | 0  | 1  | 0  | 23456701              | 23016745              |

| 8            | 0  | 1  | 1  | 34567012              | 32107654              |

| 0            | 1  | 0  | 0  | 45670123              | 45670123              |

|              | 1  | 0  | 1  | 56701234              | 54761032              |

|              | 1  | 1  | 0  | 67012345              | 67452301              |

|              | 1  | 1  | 1  | 70123456              | 76543210              |

<sup>\*</sup>Page length is a function of I/O organization and column addressing

#### **DLL Enable / Disable**

The DLL must be enabled for normal operation. DLL enable is required during power-up initialization and upon returning to normal operation after having disable the DLL for the purpose of debug or evaluation (upon existing Self Refresh Mode, the DLL is enable automatically.) Any time the DLL is enabled, 200 clock cycles must occur before a READ command can be issued.

### **Output Drive Strength**

The normal drive strength got all outputs is specified to be SSTL-2, Class II. Some vendors might also support a weak drive strength option, intended for lighter load and/or point to point environments.

#### Extended Mode Register Set ( EMRS )

The Extended mode register stores the data enabling or disabling DLL. The value of the extended mode register is not defined, so the extended mode register must be written after power up for enabling or disabling DLL. The extended mode register is written by asserting low on /CS, /RAS, /CAS, /WE and high on BA0 (The DDR SDRAM should be in all bank precharge with CKE already prior to writing into the extended mode register.) The state of address pins A0-A10 and BA1 in the same cycle as /CS, /RAS, /CAS, and /WE going low is written in the extended mode register. The mode register contents can be changed using the same command and clock cycle requirements during operation as long as all banks are in the idle state. A0 is used for DLL enable or disable. High on BA0 is used for EMRS. All the other address pins except A0 and BA0 must be set to low for proper EMRS operation.

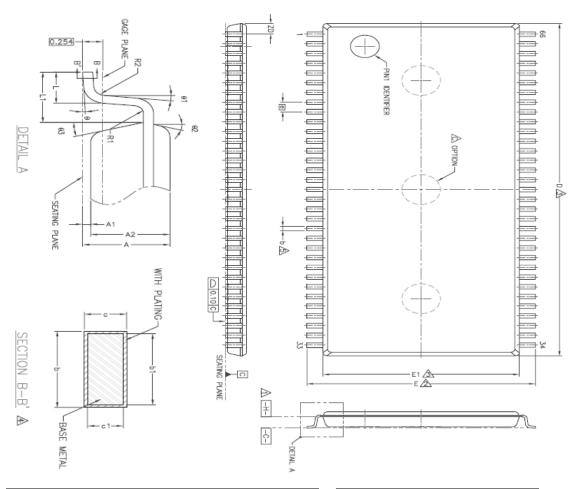

## Package Description

### 66-Pin Plastic TSOP-II (400mil)

| Complete | Dim     | nension(n | nm)  | Dim      | nension(ir | nch)  |

|----------|---------|-----------|------|----------|------------|-------|

| Symbol   | MIN NOM |           | MAX  | MIN      | NOM        | MAX   |

| Α        | -       | -         | 1.2  | -        | -          | 0.047 |

| A1       | 0.05    | 0.10      | 0.15 | 0.002    | 0.004      | 0.006 |

| A2       | 0.95    | 1.00      | 1.05 | 0.037    | 0.039      | 0.041 |

| b        | 0.22    | -         | 0.38 | 0.009    | -          | 0.015 |

| b1       | 0.22    | 0.30      | 0.33 | 0.009    | 0.012      | 0.013 |

| С        | 0.12    | -         | 0.21 | 0.005    | -          | 0.008 |

| c1       | 0.10    | 0.127     | 0.16 | 0.004    | 0.005      | 0.006 |

| D        | 2       | 22.22BS0  |      | 0.875BSC |            |       |

| ZD       |         | 0.71REF   |      | 0.028REF |            |       |

| E        | •       | 11.76BS0  | ;    | 0.463BSC |            |       |

| E1       | •       | 10.16BSC  | ;    | 0.400BSC |            |       |

| L        | 0.40    | 0.50      | 0.60 | 0.016    | 0.020      | 0.024 |

| L1       |         | 0.80REF   |      | 0.031REF |            |       |

| е        |         | 0.65BSC   |      | (        | 0.026BS0   |       |

| R1       | 0.12 -  |           | -    | 0.005    | -          | -     |

| R2       | 0.12    | -         | 0.25 | 0.005    | -          | 0.010 |

| S          | Symbol | MIN | NOM | MAX |

|------------|--------|-----|-----|-----|

| $\epsilon$ | 9      | 0   | -   | 8   |

| $\epsilon$ | 91     | 0   | i   | -   |

| $\epsilon$ | 92     | 10  | 15  | 20  |

| $\epsilon$ | 93     | 10  | 15  | 20  |

#### Note:

- 1. To be determined at seating plane -C- .

- 2. Datum plane H- coincident with bottom of lead, where lead exits body.

- 3. Dimension D and E1 are determined at datum H-

Dimension D does not include mold protrusions or gate burrs. Mold protrusions and gate burrs shall not exceed 0.15mm per side.

Dimension E1 does not include interlead mold protrusions. Interlead mold protrusions shall not exceed 0.25mm per side.

- These dimensions apply to the flat section of the lead between 0.10mm and 0.25mm from the lead tip.

- Dimension b does not include dambar protrusion/intrusion.

- 6. Controlling dimension: millimeter.

- 7. Pin pitch refer to JEDEC STD MS-024, FC.