## MC3480

## **Advance Specifications and Applications Information**

#### MEMORY CONTROLLER FOR 16 PIN 4K AND 16K DYNAMIC RAMs

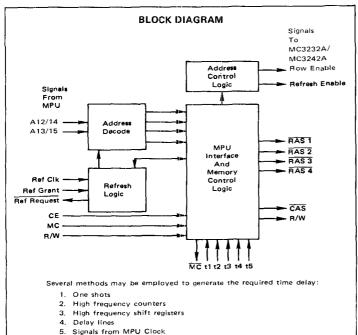

The memory controller chip is designed to greatly simplify the interface logic required to control the popular 16 pin 4K or 16K dynamic NMOS RAM in a microprocessor system such as the M6800. The controller will generate, on command from the microprocessor, the proper timing signals required to successfully transfer data between the microprocessor and the NMOS memories. The controller, in conjunction with an oscillator, will also generate the necessary www.DataSheet4U. signals required to insure that the dynamic memories are refreshed for the retention of data.

- Greatly Simplify the MPU-Dynamic Memory Interface

- Reduce Package Count and System Access/Cycle Times 30%

- Chip Enable for Expansion to Larger Word Capacity

- Generate 1 of 4 RAS Signals for an Optimum 16K/64K Memory System

- High Input Impedance for Minimum Loading of MPU Bus

- Schottky TTL Technology for High Performance

- Useful with 4K and 16K and Future Expanded Dynamic RAMs

### DYNAMIC MEMORY CONTROLLER

SCHOTTKY MONOLITHIC INTEGRATED CIRCUIT

This is advance information and specifications are subject to change without notice.

#### **ABSOLUTE MAXIMUM RATINGS (Note 1)**

| Rating                                            | Symbol           | Value        | Unit |

|---------------------------------------------------|------------------|--------------|------|

| Power Supply Voltage                              | Vcc              | 7,0          | Vdc  |

| Input Voltage                                     | VI               | ~0.5 to +7.0 | Vdc  |

| Output Voltage                                    | Vo               | -0.5 to +7.0 | Vdc  |

| Operating Ambient Temperature                     | TA               | 0 to +70     | °С   |

| Storage Temperature                               | T <sub>stg</sub> | -65 to +150  | °С   |

| Operating Junction Temperature<br>Ceramic Package | Тј               | 175          | °C   |

| Plastic Package                                   |                  | 150          |      |

Note 1: "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the devices should be operated at these limits. The table of "Electrical Characteristics" provides conditions for actual device operation.

Due to the advanced nature of this specification, final electrical limits are not yet given on all parameters. A final version may be obtained after October, 1978 by writing:

Motorola Linear IC Marketing — M250 P.O. Box 20912 Phoenix, AZ 85036

#### RECOMMENDED OPERATING CONDITIONS

| Rating                              | Symbol | Value          | Unit |  |

|-------------------------------------|--------|----------------|------|--|

| Power Supply Voltage                | vcc    | +4.75 to +5.25 | Vdc  |  |

| Operating Ambient Temperature Range | ŤΑ     | 0 to +70       | °С   |  |

ELECTRICAL CHARACTERISTICS (Unless otherwise noted specifications apply over recommended power supply and temperature ranges. Typical values measured at  $V_{CC} = 5.0 \text{ V}$  and  $T_A = 25^{\circ}\text{C.}$ )

| Characteristic                                                                                                                                                                                                      | Symbol           | Min               | Тур | Max        | Unit |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------|-----|------------|------|--|

| Input Voltage — Low Logic State                                                                                                                                                                                     | VIL              | _                 | -   | 0.8        | V    |  |

| Input Voltage — High Logic State                                                                                                                                                                                    | ViH              | 2.0               |     | _          | V    |  |

| Input Current — Low Logic State (VIL = 0.5 V)                                                                                                                                                                       | I <sub>I</sub> L |                   | -   | -250       | μА   |  |

| nput Current — High Logic State (V <sub>IH</sub> = 2.7 V)<br>(V <sub>IH</sub> = 5.5 V)                                                                                                                              | 1(Н              | _                 |     | 40<br>100  | μA   |  |

| nput Clamp Voltages<br>(I <sub>IC</sub> 18 mA)                                                                                                                                                                      | Уic              | -                 |     | -1.5       | V    |  |

| Dutput Voltage — Low Logic State  (I <sub>OL</sub> = 24 mA for RAS, CAS, and R/W)  (I <sub>OL</sub> = 8.0 mA for Row En, Ref En, MC, Ref Reg)                                                                       | VoL              |                   |     | 0.5<br>0.5 | V    |  |

| Dutput Voltage — High Logic State  {IOH = -1.0 mA for RAS, CAS, and R/W}  {IOH = -0.4 mA for Row En, Ref En, and MC}  IOH = -0.2 mA for Ref Req  {Note: Ref Req output has internal 5.0 k resistive pullup to VCC.} | Voн              | 3.0<br>2.4<br>2.4 |     | <br>       | V    |  |

| Power Supply Current                                                                                                                                                                                                | <sup>1</sup> cc  | -                 |     | 70         | m/   |  |

| Output Short-Circuit Current<br>(V <sub>OL</sub> = 0 V for Row En, Ref En, and MC)                                                                                                                                  | los              | -10               | -   | -55        | m/   |  |

**MOTOROLA** Semiconductor Products Inc. -

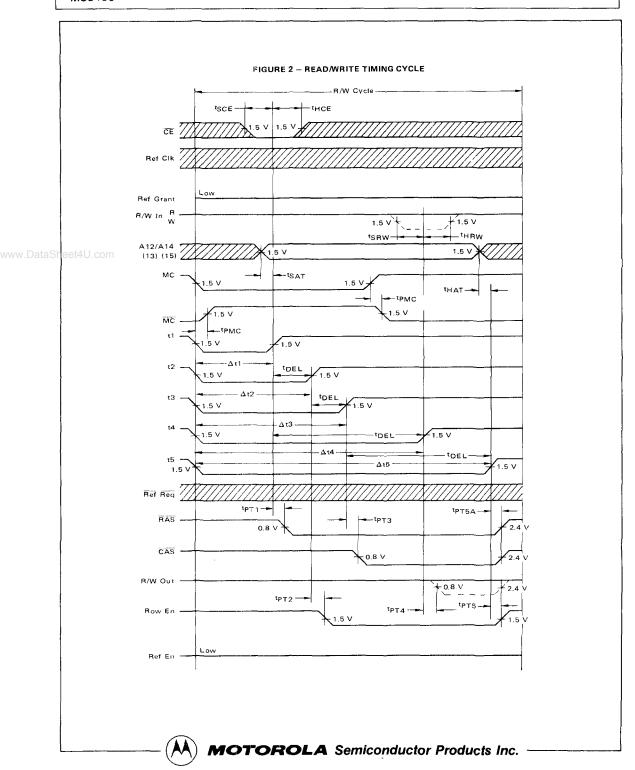

SWITCHING CHARACTERISTICS Typical values measured at V<sub>CC</sub> = 5.0 V, T<sub>A</sub> = 25°C

|             | Characteristic                     | Symbol | Min | Тур | Max | Unit |

|-------------|------------------------------------|--------|-----|-----|-----|------|

|             | Propagation Delay Times            |        |     |     |     | ns   |

| i           | MC to MC                           | tPMC   | -   | 8   |     | ĺ    |

|             | t1 to RAS                          | tPT1   | i - | 30  |     | Ì    |

| i i         | t2 to Row En                       | tPT2   |     | 30  | _   |      |

|             | t3 to CAS                          | tPT3   | l – | 30  | -   | l    |

| i           | t4 to R/W                          | tPT4   |     | 30  | _   | İ    |

|             | t5 to CAS, RAS                     | tPT5A  | _   | 30  | -   |      |

|             | t5 to R/W, Row En, Ref En          | tPT5   | _   | 45  | -   |      |

|             | Ref Clk to Ref Req                 | tPCQ   | _   | 45  | _   |      |

|             | Ref Grant to Row En or Ref En      | tPGR   | -   | 30  | -   |      |

|             | t1 to Ref Reg (Refresh Cycle only) | tPTQ   |     | 30  |     | İ    |

|             | Setup Times                        |        |     |     |     | ns   |

|             | Ref Clk before Ref Grant           | tSCG   | _   | 30  | -   |      |

|             | A12, A13 before t1                 | tSAT   | -   | -10 | -   | 1    |

|             | R/W Input before t4                | tSRW   | _   | 10  |     |      |

|             | CE before t1                       | tSCE   | -   | 15  |     |      |

|             | Hold Times                         |        |     |     |     | ns   |

| www.DataShe | A12, A13 after t5                  | tHAT   | _   | 10  |     |      |

| www.bataone | CE after t1                        | tHCE   | -   | 0   | ļ   | 1    |

|             | R/W after t4                       | tHRW   |     | 0   |     |      |

|             | Minimum Delay Times (see Note 2)   | tDEL   |     |     |     | ns   |

|             | t1 Low to High to t2 Low to High   | (1-2)  |     | 30  |     |      |

|             | t1 Low to High to t4 Low to High   | (1-4)  | _   | 30  | -   | 1    |

|             | t2 Low to High to t3 Low to High   | (2-3)  | _   | 30  | _   | I    |

| 1           | t3 Low to High to t5 Low to High   | (3-5)  | _   | 30  |     |      |

Note 2: If delays between pins are less than the minimum specified, the succeeding outputs may not switch.

AC Loads (Note 3)

| R/W and CAS Outputs                     | 450 pF to Gnd* |

|-----------------------------------------|----------------|

| RAS Outputs                             | 150 pF to Gnd* |

| MC, Row En, Ref En, and Ref Reg Outputs | 15 pF to Gnd*  |

<sup>\*</sup>Includes probe and jig capacitance.

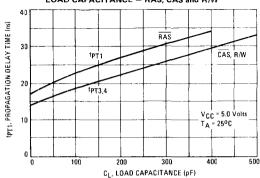

NOTE 3: All outputs can drive larger capacitive loads than those shown with a small decrease in speed. See Figure 1.

FIGURE 1 — TYPICAL tpT1,3,and4 (HIGH TO LOW) versus LOAD CAPACITANCE — RAS,  $\overline{\text{CAS}}$  and R/W

**MOTOROLA** Semiconductor Products Inc. -

| Г   | Name      | No. | PIN DESCRIPTION TABLE  Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----|-----------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1=  | RAS1 *    | 16  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     | AS2       | 15  | Row Address Strobe pins which connect to each of the dynamic RAMs to latch in Row Address on memory chips.  Decoded to 1 of 4 during R/W cycle. All 4 go low during refresh cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     | RAS3      | 14  | becode to 1 of 4 during n/w cycle. All 4 go low during refresh cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Ē   | RAS4      | 13  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Ĉ   | AS •      | 11  | Column Address Strobe pin which connects to each dynamic RAM to latch in column address.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| F   | R/W Out * | 10  | This pin signals the dynamic RAM whether the RAM is to be read from or written into.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| F   | Row En    | 9   | Row Enable output which goes to the MC3232A (MC3242A). It signals the Address Multiplexer that the lower half (Row Addresses) or the upper half (Column Addresses) of the address lines are to be multiplexed into the dynamic RAM address inputs. A Logic 1 on this output indicates the Row Addresses, and a Logic 0 indicates Column Addresses.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| L   | lef En    | 8   | Refresh Enable output. A Logic 1 signals the Address Multiplexer that a refresh cycle is to be done, and a Logic 0 indicates that address multiplexing should be done.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Ċ   | Ē         | 22  | Chip Enable Input. A Logic 1 on this pin disables all chip functions, except that of Refresh and the $\overline{MC}$ output. $\overline{CE}$ must be low during t1 low to high transition to initiate R/W cycle. Once t1 is initiated, the cycle is independent of $\overline{CE}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| F   | I/W In    | 7   | The Read/Write input pin receives information from the M6800 MPU as to the direction of data exchange in the dynamic RAM. It transmits a Logic 0 to the R/W output for a Write Cycle and a Logic 1 for a Read Cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     | 12 (A14)  | 17  | Upper Order Address lines from the M6800. These two inputs decode to four signals controlling the four RAS outputs,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| LA  | 13 (A15)  | 18  | A14 and A15 apply to 16K RAMs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| N   | 1C        | 23  | Memory Clock input which comes from the microprocessor clock generator. This input must rise after the rising edge of t1 to avoid a potential internal race condition.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| N   | 1C        | 1   | The complement of MC. It is a buffered output which may be used to drive the circuitry creating the time delays used on inputs 12 through t5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

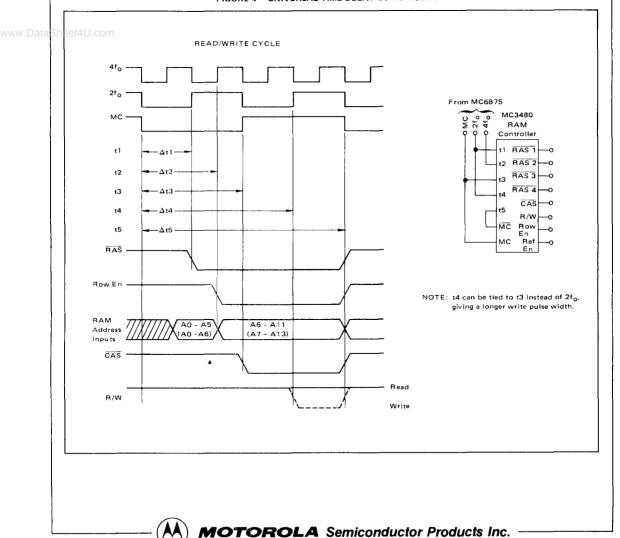

| She | et4U.ca   | m 2 | These pins use external timing delays to sequentially select the outputs to be enabled. They are positive-edge triggered                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| t?  | 2         | 3   | inputs. Assuming a Read/Write cycle is to be executed, a positive edge on t1 forces a logic 0 on one of the four RAS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| t:  | ١.        | 4   | outputs as determined by the A12/14, A13/15 inputs. After a delay, a positive edge on t2 causes Row En to go to a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| t4  |           | 5   | Logic 0, providing address-multiplexing information to the MC3232A or MC3242A. t3 enables the CAS output and it                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| t   | 9         | 6   | goes low. t4 enables the R/W output and it goes low, assuming the R/W input was low. t5 resets all the outputs to a Logic 1 (with the exception of MC, Ref En, and Ref Req). The inputs t1, t2, t3, and t5 are daisy-chained, so they mus be sequentially driven to obtain the desired output signals, t4 can be driven at any time after t1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

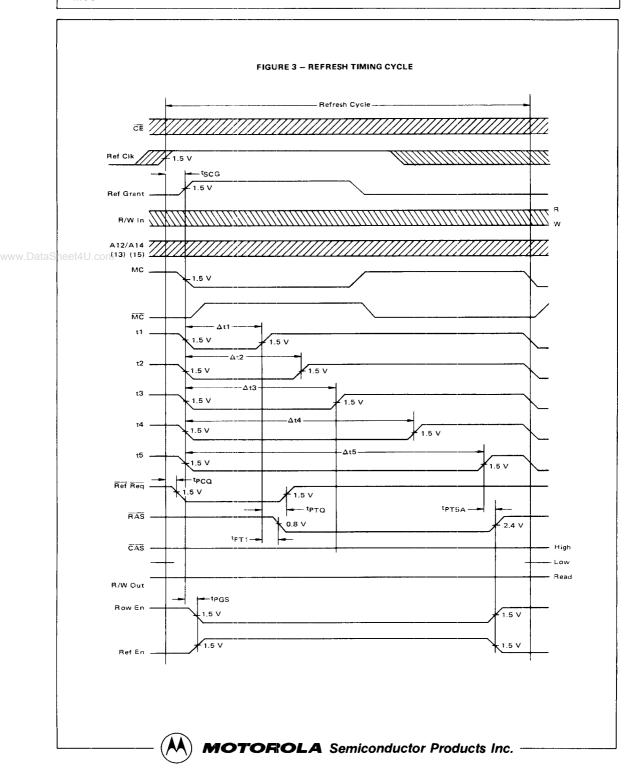

| R   | lef Clk   | 21  | The 32 kHz (64 kHz) Refresh Clock signals this pin that another refresh cycle is required. It is a positive-edge triggered input, and upon triggering, the Ref Req pin goes to a Logic 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Ā   | lef Req   | 20  | The Refresh Request output acts as an input to the MPU system, requesting a refresh cycle. This output has a 5 k $\Omega$ pullup resistor to the VCC supply to allow wire-ORing if desired.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| R   | lef Grant | 19  | Through the Refresh Grant input, the MC6875 initiates a refresh cycle. This input is positive-edge triggered and is enabled only after the Ref Req pin has gone low. This allows the MC3480 to discern between a Refresh Grant or a DMA Grant even though they appear on the same line. When employing both dynamic memory (refresh) and DMA in a microprocessor-based system with a combined Refresh/DMA Request control on the clock, provision must be made for holding off a DMA request during a refresh period (and visa versa). If this provision is not made, clock stretching (cycle stealing) will continue indefinitely and dynamic microprocessor data will be lost. The positive edge on Ref Grant causes Row En output to go low and Ref En output to go high. This signals the MC3232A (MC3242A) that a refresh address is required. The refresh cycle occurs with the succeeding pulses on t1-t5. A positive edge on t1 causes Ref Req to go high and all the RAS outputs to go low. A positive going edge on t2 causes no change in the outputs, since it controls the address multiplexing (Row En) during the Read/Write cycles. There is no output change when t5 and t4 go high because no CAS or R/W signal is needed during refresh. A positive edge on t5 resets the RAS to a Logic 1 state, and Ref En to a Logic 0 state, ready for the next Read/Write cycle. |

| V   | cc        | 24  | +5.0 V supply. A 0.1 μF capacitor is recommended to bypass pin 24 to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| _   | nd        | 12  | System Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

<sup>\*</sup>These outputs are designed to drive the highly capacitive inputs of multiple dynamic RAMS/(150 pF for RAS outputs, and 450 pF for CAS and R/W outputs). Consequently, these outputs have no short circuit limit and must be handled accordingly.

Note: All other outputs are LS TTL totem pole configuration unless otherwise noted. Good high capacitance load driving techniques usually include a 10th or greater series damping resistor. It is highly recommended that this be done on RAS, CAS and R/W outputs of the MC3480.

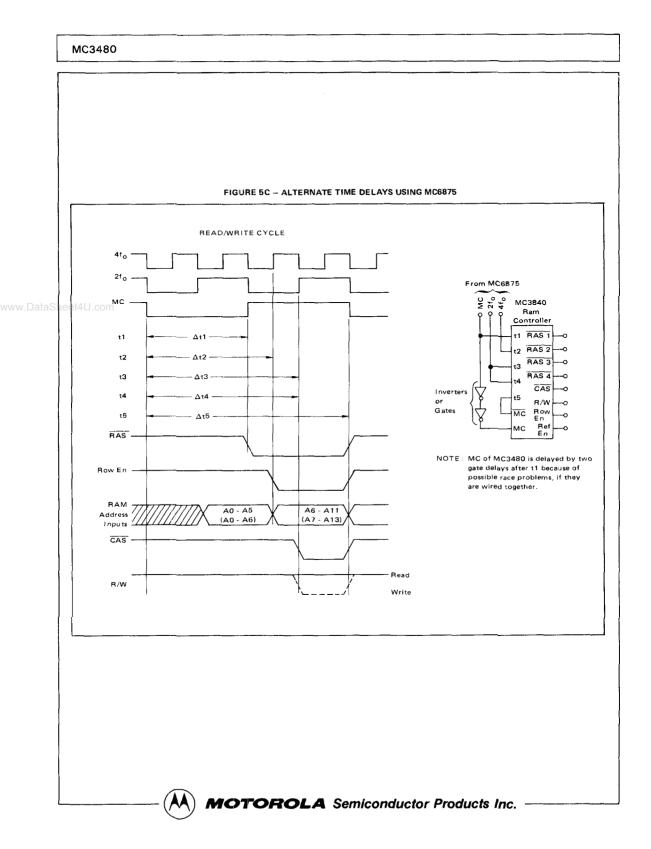

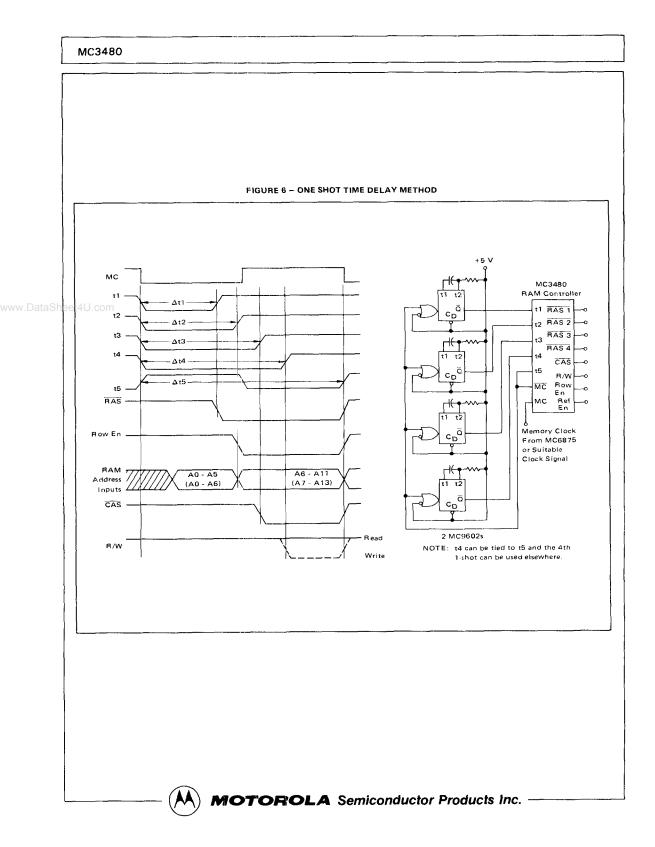

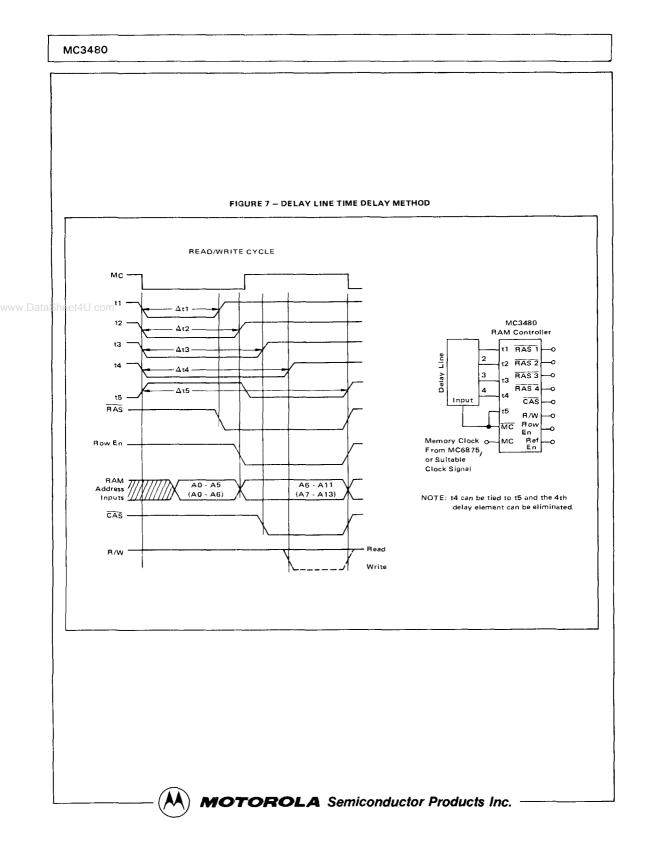

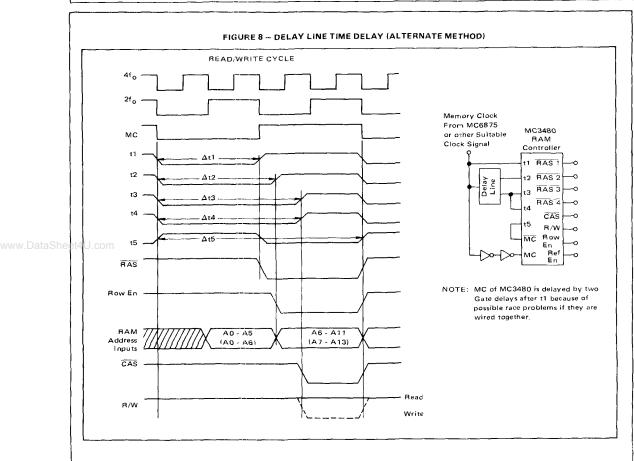

#### TIME DELAY INFORMATION

#### TIMING REQUIREMENT CONSTRAINTS

- $\Delta t1 \qquad \qquad \text{Minimum is determined by MPU Address Delay $$(t_{AD})$, plus RAM Row Address Set-Up Time $$(t_{ASR})$, minus MC3480 Propagation Delay $$(t_{PT1})$.}$

- Δt2 Δt1 Minimum is determined by RAM Row Address Hold Time (t<sub>RAH</sub>) minus the minimum MC3232A/3242A Row Enable to Output Delay (t<sub>00MIN</sub>).\*

- $\Delta t3 \Delta t2 \qquad \text{Minimum is determined by RAM Column Address Set-Up Time ($t_{ASC minimum}$) plus maximum MC3232A/3242A} \quad \text{Row Enable to Output Delay ($t_{001MAX}$).*}$

- Δt4 Δt3 No Minimum

- Δt5 Δt3 Minimum is determined by RAM minimum CAS Pulse Width (t<sub>CAS</sub>) or Access Time from CAS (t<sub>CAC</sub>) plus Data Set-Up Time of MPU (t<sub>DSR</sub>).

- Δt5 Δt4 Minimum is determined by the RAM minimum Write Pulse Width (t<sub>WP</sub>).

- \*The MC3480 has propagation delays also, but they cancel each other in these delay requirements.

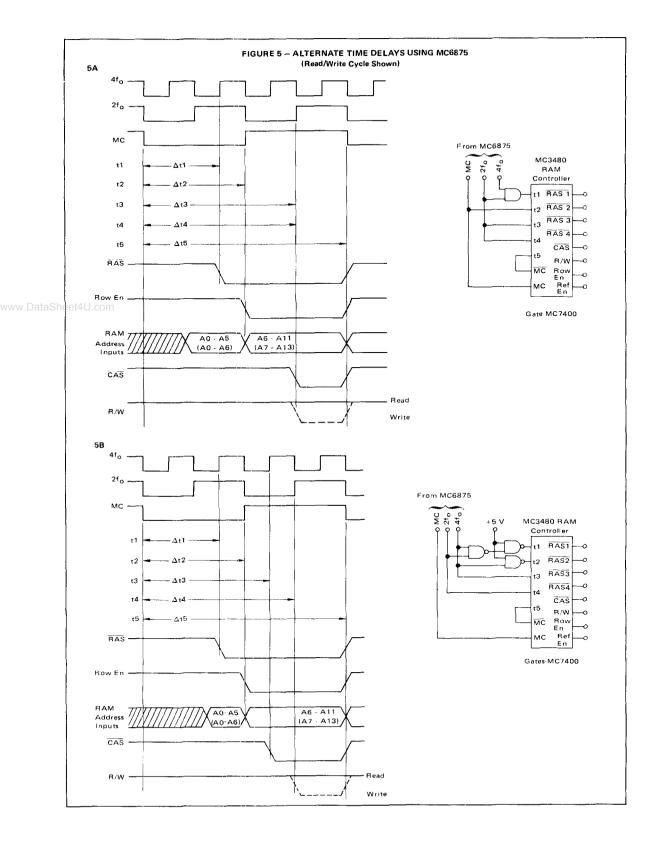

Note: Also required in computing time delays are the various delays incurred by the particular delay scheme used; i.e., delays between  $4 \times f_0$ ,  $2 \times f_0$ , and  $f_0$  from the MC6875 which are used as inputs or the gate delays of the gates used in Figures 4A through 4C.

**MOTOROLA** Semiconductor Products Inc. -

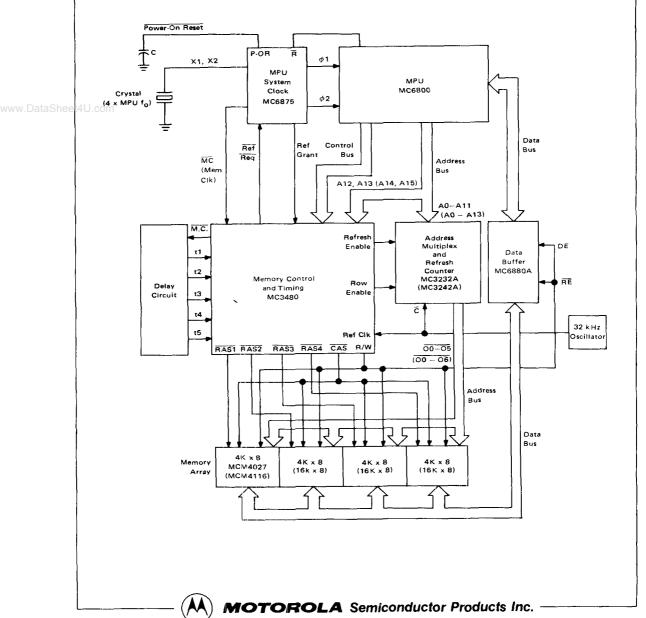

# TYPICAL APPLICATION 16K X 8-BIT MEMORY SYSTEM FOR M6800 MPU

Note: Numbers in parenthesis indicate part types or values for 16K x 1 RAMs

#### APPLICATIONS INFORMATION

#### GENERAL DESCRIPTION

The MC3480 uses five general timing inputs in place of a master clock with on-chip timing generation. This gives the system designer optimum flexibility in interfacing with the various microprocessor families and dynamic memories that are available. In simpler slow speed

systems, the timing signals required can be directly obtained from those available from the microprocessor. In systems requiring high speed memory/microprocessor cycle times, timing input t1-t5 can be obtained using delay lines or a range of techniques as shown in Figures 4 thru 8. It is only necessary to maintain the time delay relationships shown under time delay information.

#### FIGURE 4 -- UNIVERSAL TIME DELAY USING MC6875

#### REFRESH CONSIDERATIONS

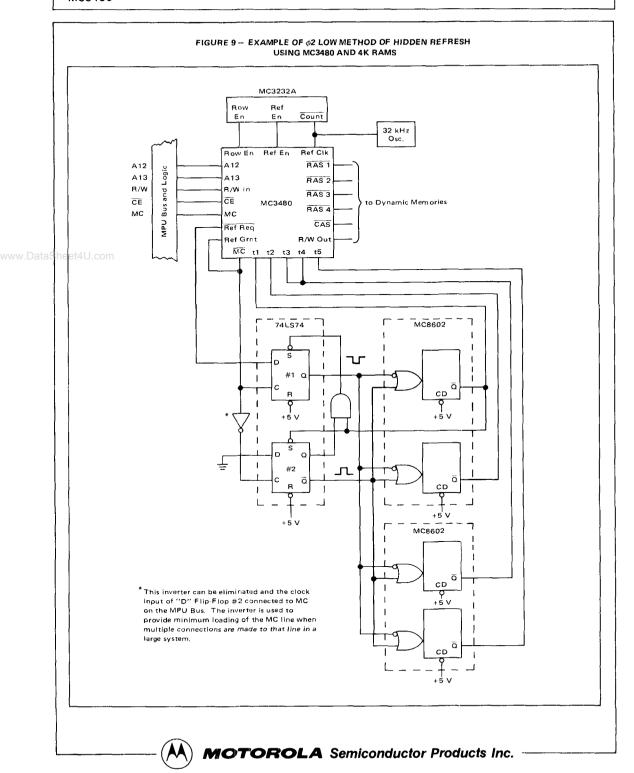

The MC3480/MC3232A (MC3242A) memory control system can be used with either cycle steal or transparent refresh methods. Figure 9 shows one transparent technique employing refresh during  $\phi 2$  low in an M6800 microprocessor-based system. Using this technique requires that the memory be capable of completing a Read/Write Cycle and a Refresh Cycle sequentially during the M6800 cycle. The minimum cycle time at the time of printing for dynamic multiplexed RAMs is 320 ns, therefore limiting the mciroprocessor to 1.56 MHz operation. The D flipflops of Figure 9 produce a trigger at the beginning of both  $\phi 1$  and  $\phi 2$ . For a 1.0 MHz system, the 11–t5 inputs should be adjusted so that the following conditions occur at the specified period after the beginning of a cycle:

RAS falls at 100 ns (triggered by t1)

Row In falls at 200 ns (triggered by t2)

CAS, R/W falls at 250 ns (triggered by t3)

t5 rises at 450 ns.

A delay line could be used to generate t1-t5 in place of

the four monostables. For the 1.0 MHz system, it would require either two 5 tap delay lines with 50 ns per tap or a 10 tap line with 50 ns/tap. For use with a 600 kHz system, a delay line with 5 taps of 150 ns each could be used. For this case:

RAS falls at 150 ns

Row En falls at 300 ns

CAS, R/W falls at 450 ns

t5 rises at 750 ns

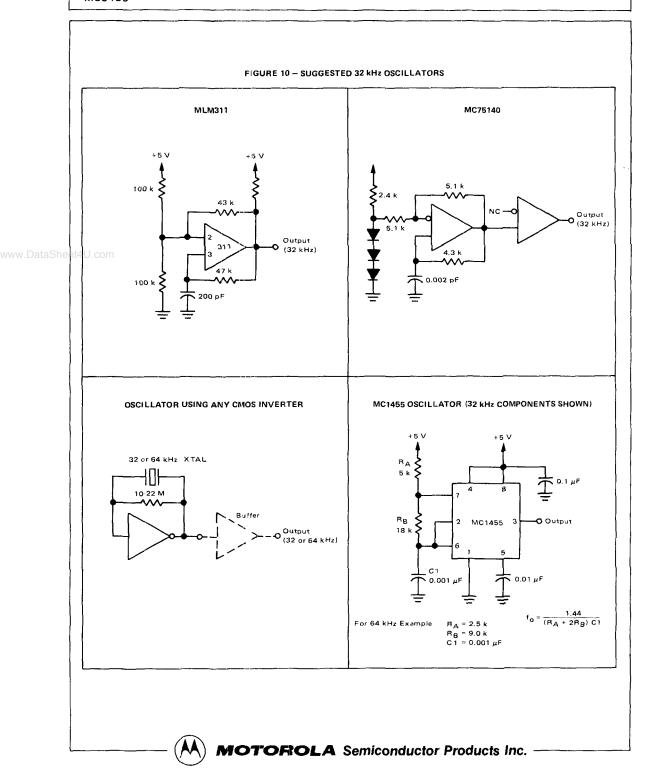

Figure 10 shows typical refresh oscillator configurations for both 32 kHz (fREFmin for 4K) and 64 kHz (fREFmin for 16K). In the case of transparent refresh, if the designer is not concerned with power consumption, the refresh oscillator may be eliminated and the Ref Clk input connected to the MC input yielding a refresh every  $\phi$ 1.

For DMA operation combined with cycle stealing refresh, care must be taken not to allow a DMA request during a Refresh Request/Grant period and to hold off a refresh during a DMA operation. See comments under pin descriptions, Pin 19.

**MOTOROLA** Semiconductor Products Inc.

www.DataSheet4U.com

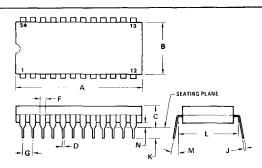

**L SUFFIX** CERAMIC PACKAGE CASE 623-03

DIM MIN MAX INCHES MIN | MAX A 31.24 32.26 1.230 1.270 B 12.70 13.72 0.500 0.540 C 4.06 5.59 0.160 0.220 D 0.41 0.51 0.016 0.020 | 0.51 | 0.50 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 | 0.060 G 1.27 0.020 0.050

NOTES:

- 1, DIM "L" TO CENTER OF LEADS WHEN FORMED

- PARALLEL.

2. LEADS WITHIN 0.13 mm (0.005) RADIUS OF TRUE POSITION AT SEATING PLANE AT MAXIMUM MATERIAL CONDITION. (WHEN FORMED PARALLEL)

**PSUFFIX** PLASTIC PACKAGE CASE 649-03

<u>ለ ሲ ሲ ሲ ሲ ሲ ሲ ሲ ሲ ሲ ሲ</u> В

|     | MILLIN   | ETERS | INCHES    |       |  |

|-----|----------|-------|-----------|-------|--|

| DIM | MIN      | MAX   | MIN       | MAX   |  |

| Α   | 31.50    | 32.13 | 1.240     | 1.265 |  |

| 8   | 13.21    | 13.72 | 0.520     | 0.540 |  |

| C   | 4.70     | 5.21  | 0.185     | 0.205 |  |

| D   | 0.38     | 0.51  | 0.015     | 0.020 |  |

| F   | 1.02     | 1.52  | 0.040     | 0.060 |  |

| G   | 2.54 BSC |       | 0.100 BSC |       |  |

| H   | 1.65     | 2.16  | 0.065     | 0.085 |  |

| J   | 0.20     | 0.30  | 0.008     | 0.012 |  |

| K   | 2.92     | 3.43  | 0.115     | 0.135 |  |

| L   | 14.99    | 15.49 | 0.590     | 0.610 |  |

| M   | _        | 100   | -         | 100   |  |

| N   | 0.51     | 1.02  | 0.020     | 0.040 |  |

| P   | 0.13     | 0.38  | 0.005     | 0.015 |  |

| Q   | 0.51     | 0.76  | 0.020     | 0.030 |  |

SEATING

- NOTES: 1. LEADS WITHIN 0.13 mm (0.005) RADIUS OF TRUE POSITION AT SEATING PLANE AT MAXIMUM

- MATERIAL CONDITION.

2. DIMENSION "L" TO CENTER OF LEADS WHEN FORMED PARALLEL.

Circuit diagrams utilizing Motorola products are included as a means of illustrating typical semiconductor applications; consequently, complete information sufficient for construction purposes is not necessarily given. The information has been carefully checked and

is believed to be entirely reliable. However, no responsibility is assumed for inaccuracies. Furthermore, such information does not convey to the purchaser of the semiconductor devices described any license under the patent rights of Motorola Inc. or others.

#### **MOTOROLA** Semiconductor Products Inc.

BOX 20912 • PHOENIX, ARIZONA 85036 • A SUBSIDIARY OF MOTOROLA INC.

11793 PRINTED IN USA 7-78 | IMPERIAL LITHO 672620

ADI 517